# **DSP56001A**

# Product Preview 24-BIT DIGITAL SIGNAL PROCESSOR

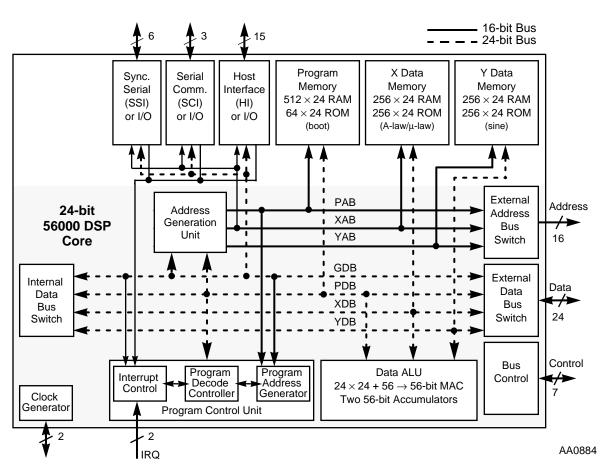

The DSP56001A is an MPU-style general purpose Digital Signal Processor (DSP) composed of an efficient 24-bit DSP core, program and data memories, various peripherals, and support circuitry. The DSP56000 core is fed by on-chip Program RAM, two independent data RAMs, and two data ROMs containing sine, A-law, and  $\mu$ -law tables. The DSP56001A contains a Serial Communication Interface (SCI), a Synchronous Serial Interface (SSI), and a parallel Host Interface (HI). This combination of features, illustrated in **Figure 1**, makes the DSP56001A a cost-effective, high-performance solution for high-precision general purpose digital signal processing. The DSP56001A is intended as a replacement for the DSP56001. The DSP56002 should be considered for new designs.

Figure 1 DSP56001A Block Diagram

# Freescale Semiconductor, Inc.

#### **TABLE OF CONTENTS**

| SECTION 1 | SIGNAL/PIN DESCRIPTIONS                                                              | I-1 |

|-----------|--------------------------------------------------------------------------------------|-----|

| SECTION 2 | SPECIFICATIONS2                                                                      | 2-1 |

| SECTION 3 | PACKAGING                                                                            | 3-1 |

| SECTION 4 | DESIGN CONSIDERATIONS (INCLUDES NOTES FOR DSP56001 TO DSP56001A DESIGN CONVERSION) 4 | 1-1 |

| SECTION 5 | ORDERING INFORMATION                                                                 | 5-1 |

| SECTION A | ROM TABLE LISTINGS                                                                   | ۱-۱ |

#### FOR TECHNICAL ASSISTANCE:

**Telephone:** 1 (800) 521-6274

Email: dsphelp@dsp.sps.mot.com

Internet: <a href="http://www.motorola-dsp.com">http://www.motorola-dsp.com</a>

# **Data Sheet Conventions**

This data sheet uses the following conventions:

| OVERBAR      | Used to indicate a signal that is active when pulled low; for example, the $\overline{\mbox{RESET}}$ pin is active when low |                                                                                                   |              |                                   |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------|-----------------------------------|--|

| "asserted"   | Means that a high tru<br>signal is low                                                                                      | Means that a high true (active high) signal is high or that a low true (active low) signal is low |              |                                   |  |

| "deasserted" | Means that a high tru<br>signal is high                                                                                     | Means that a high true (active high) signal is low or that a low true (active low) signal is high |              |                                   |  |

| Examples:    | Signal/Symbol                                                                                                               | <b>Logic State</b>                                                                                | Signal State | Voltage                           |  |

|              | $\overline{	ext{PIN}}$                                                                                                      | True                                                                                              | Asserted     | $V_{IL}/V_{OL}$                   |  |

|              | PIN                                                                                                                         | False                                                                                             | Deasserted   | $V_{IH}/V_{OH}$                   |  |

|              | PIN                                                                                                                         | True                                                                                              | Asserted     | $V_{\mathrm{IH}}/V_{\mathrm{OH}}$ |  |

|              | PIN                                                                                                                         | False                                                                                             | Deasserted   | $V_{IL}/V_{OL}$                   |  |

Note: Values for  $V_{IL}$ ,  $V_{OL}$ ,  $V_{IH}$ , and  $V_{OH}$  are defined by individual product specifications.

DSP56001A Features

#### **DSP56001A FEATURES**

# **Digital Signal Processing Core**

- Efficient, object code compatible, 24-bit 56000 family DSP engine

- Up to 16.5 Million Instructions Per Second (MIPS)—60.6 ns instruction cycle at 33 MHz

- Up to 99 Million Operations Per Second (MOPS) at 33 MHz

- Executes a 1024-point complex Fast Fourier Transform (FFT) in 59,898 clocks

- Highly parallel instruction set with unique DSP addressing modes

- Two 56-bit accumulators including extension byte

- Parallel 24 × 24-bit multiply-accumulate in 1 instruction cycle (2 clock cycles)

- Double precision  $48 \times 48$ -bit multiply with 96-bit result in 6 instruction cycles

- 56-bit addition/subtraction in 1 instruction cycle

- Fractional arithmetic with support for multiprecision arithmetic

- Hardware support for block-floating point FFT

- Hardware nested DO loops

- Zero-overhead fast interrupts (2 instruction cycles)

- Four 24-bit internal data buses and three 16-bit internal address buses for maximum information transfer on-chip

# **Memory**

- On-chip modified Harvard architecture permitting simultaneous accesses to program and two data memories

- 512  $\times$  24-bit on-chip Program RAM and 64  $\times$  24-bit bootstrap ROM

- Two 256 × 24-bit on-chip data RAMs

- Two  $256 \times 24$ -bit on-chip data ROMs containing sine, A-law and  $\mu$ -law tables

- · External memory expansion with 16-bit address and 24-bit data buses

- Bootstrap loading from external data bus or Host Interface

**Product Documentation**

# **Peripheral and Support Circuits**

- Byte-wide Host Interface (HI) with Direct Memory Access (DMA) support

- Synchronous Serial Interface (SSI) to communicate with codecs and synchronous serial devices

- 8-, 12-, 16-, and 24-bit word sizes

- Up to 32 software-selectable time slots in Network mode

- Serial Communication Interface (SCI) for full-duplex asynchronous communications

- On-chip peripheral registers memory mapped in data memory space

- Double-buffered peripherals

- Up to twenty-four General Purpose I/O (GPIO) pins

- Two external interrupt request pins

#### **Miscellaneous Features**

- Power-saving Wait and Stop modes

- Fully static, HCMOS design for operating frequencies from 33 MHz down to 4 MHz

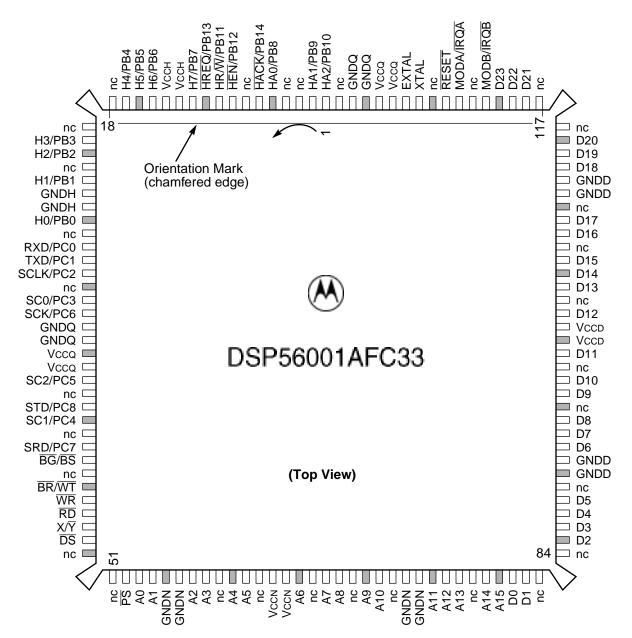

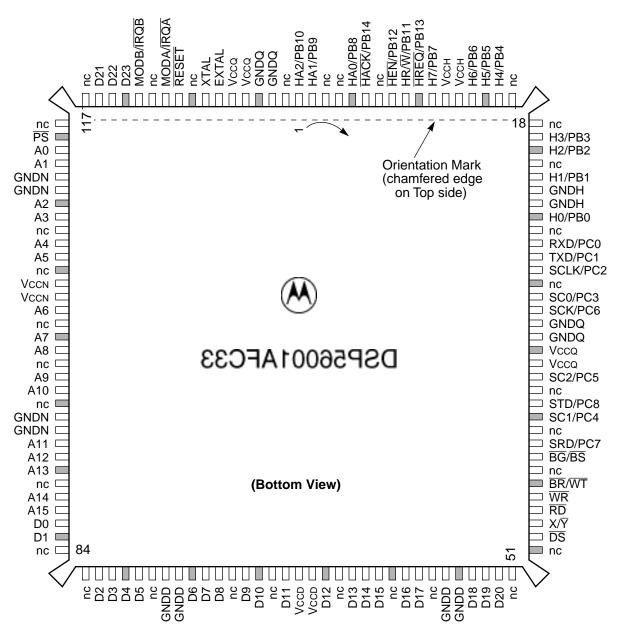

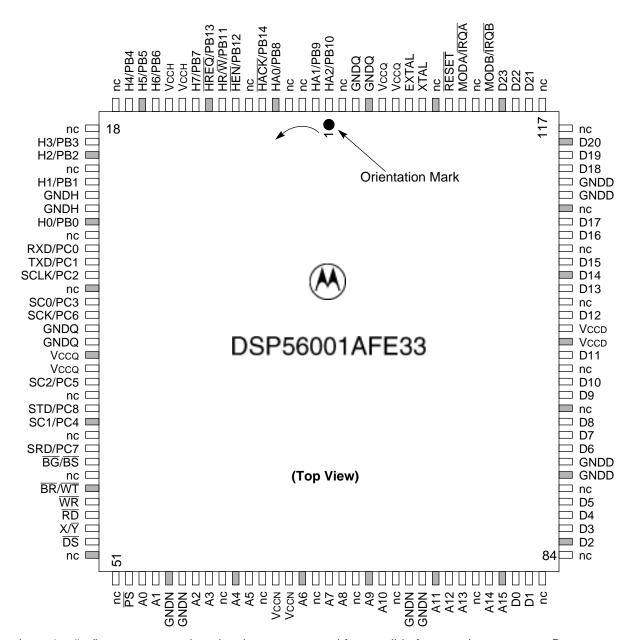

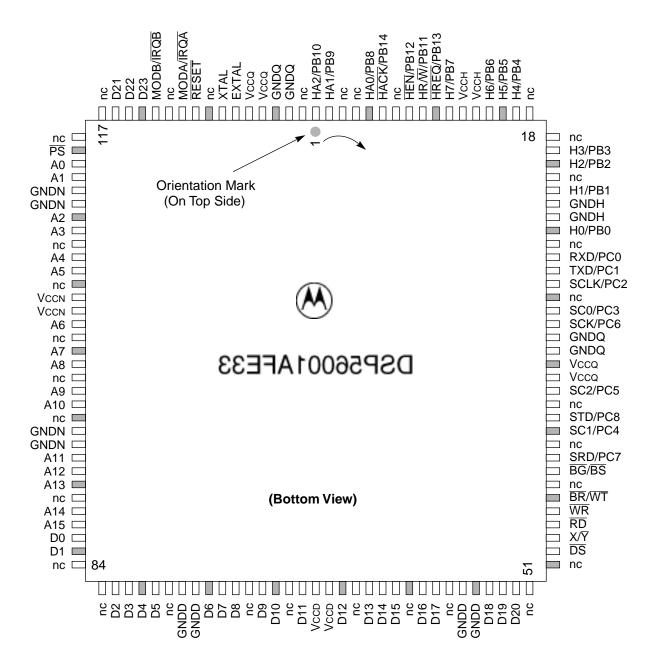

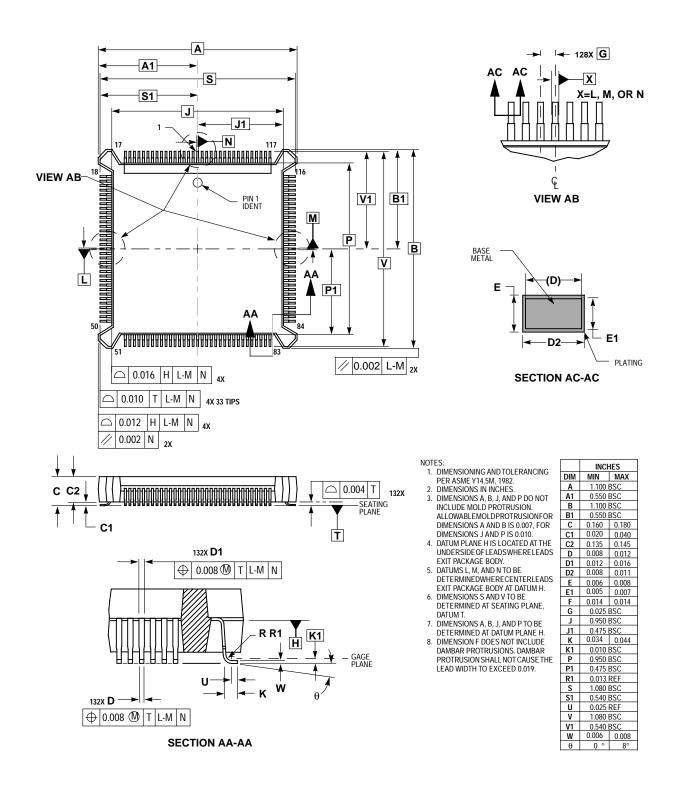

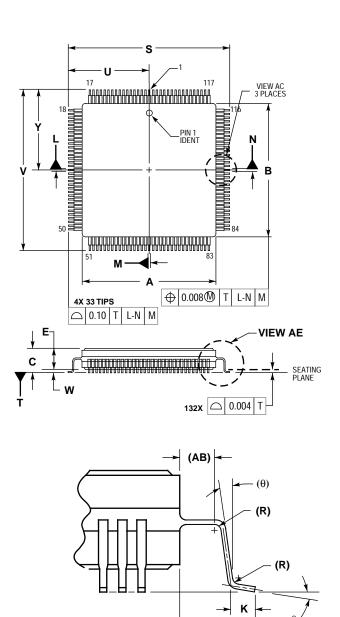

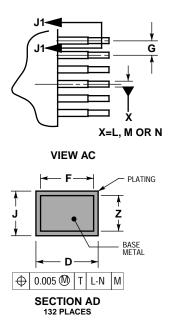

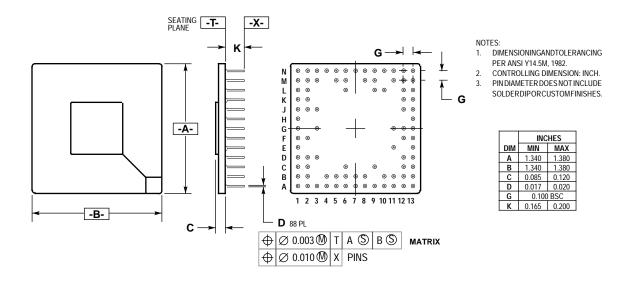

- 88-pin Ceramic Pin Grid Array (PGA) package; 13 × 13 array

- 132-pin Plastic Quad Flat Pack (PQFP) surface-mount package; 24 × 24 × 4 mm

- 132-pin Ceramic Quad Flat Pack (CQFP) surface-mount package; 22 × 22 × 4 mm

- 5 V power supply

#### PRODUCT DOCUMENTATION

The three documents listed in **Table 1** are required for a complete description of the DSP56001A and are necessary to design properly with the part. Documentation is available from one of the following locations (see back cover for detailed information):

- A local Motorola distributor

- A Motorola semiconductor sales office

- A Motorola Literature Distribution Center

- The World Wide Web (WWW)

**Product Documentation**

Table 1 DSP56001A Documentation

| Topic                     | Description                                                                                          | Order Number  |

|---------------------------|------------------------------------------------------------------------------------------------------|---------------|

| DSP56001<br>User's Manual | Detailed description of the 56001 architecture, 24-bit DSP, memory, peripherals, and instruction set | DSP56001UM/AD |

| DSP56001A<br>Data Sheet   | Pin and package descriptions, and electrical and timing specifications                               | DSP56001A/D   |

# **Related Documentation**

**Table 2** lists additional documentation relevant to the DSP56001A.

Table 2 DSP56001A Related Documentation

| Document Name                                                                       | Description                                                                                      | Order Number |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------|

| Digital Sine-Wave Synthesis                                                         | Application Report; uses the DSP56001 look-up table                                              | APR1/D       |

| Digital Stereo 10-band Graphic<br>Equalizer                                         | Application Report; includes code and circuitry; features the DSP56001                           | APR2/D       |

| Fractional and Integer Arithmetic                                                   | Application Report; includes code                                                                | APR3/D       |

| Implementation of Fast Fourier<br>Transforms                                        | Application Report; comprehensive FFT algorithms and code for DSP56001, DSP56156, and DSP96002   | APR4/D       |

| Implementation of PID Controllers                                                   | Application Report; PWM using the SCI timer and three phase output using modulo addressing       | APR5/D       |

| Convolutional Encoding and<br>Viterbi Decoding with a V.32<br>Modem Trellis Example | Application Report; theory and code; features the DSP56001                                       | APR6/D       |

| Implementing IIR/FIR Filters                                                        | Application Report; comprehensive example using the DSP56001                                     | APR7/D       |

| Principles of Sigma-Delta<br>Modulation for A-to-D Converters                       | Application Report; features the DSP56ADC16; improving resolution with half-band filters         | APR8/D       |

| Full-Duplex 32-kbit/s CCITT<br>ADPCM Speech Coding                                  | Application Report; features the DSP56001                                                        | APR9/D       |

| DSP56001 Interface Techniques and Examples                                          | Application Report; interfaces for pseudo<br>Static RAM, Dynamic RAM, ISA bus, Host<br>Interface | APR11/D      |

# **Product Documentation**

Table 2 DSP56001A Related Documentation (Continued)

| Document Name                                                                  | Description                                                                                                | Order Number                                   |

|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| Twin CODEC Expansion Board for<br>the DSP56000 ADS                             | Application Report; circuit, code, FIR filter design for two voice band codecs connecting to the SSI       | APR12/D                                        |

| Conference Bridging in the Digital<br>Telecommunications Environment           | Application Report; theory and code; features the DSP56001/002                                             | APR14/D                                        |

| Implementation of Adaptive<br>Controllers                                      | Application Report; adaptive control using reference models; generalized predictive control; includes code | APR15/D                                        |

| Calculating Timing Requirements of External SRAM                               | Application Report; determination of SRAM speed for optimum performance                                    | APR16/D                                        |

| Low Cost Controller for DSP56001                                               | Application Report; circuit and code to connect two DSP56001s to an MC68008                                | APR402/D                                       |

| G.722 Audio Processing                                                         | Application Report; theory and code using SB-ADPCM                                                         | APR404/D                                       |

| Minimal Logic DRAM Interface                                                   | Application Report; 1M x 480 ns DRAM, 1 PAL, code                                                          | APR405/D                                       |

| Logarithmic/Linear Conversion<br>Routines                                      | Application Report; μ-law and A-law companding routines for PCM monocircuits                               | ANE408/D                                       |

| Third Party Compendium                                                         | Brochures from companies selling hardware and software that supports Motorola DSPs                         | DSP3RDPTYPAK/D                                 |

| University Support Program                                                     | Flyer; Motorola's program supporting<br>Universities in DSP research and<br>education                      | BR382/D                                        |

| Technical Training Schedule                                                    | Technical Training Schedule                                                                                | BR348AD/D                                      |

| Audio Course Information                                                       | Audio Course Information                                                                                   | BR928/D                                        |

| Real Time Signal Processing<br>Applications with Motorola's<br>DSP56000 Family | Textbook by Mohamed El-Sharkawy;<br>398+ pages. (This is a charge item.)                                   | Prentice-Hall,<br>1990; ISBN 0-13-<br>767138-5 |

# **SECTION** SIGNAL/PIN DESCRIPTIONS

# **INTRODUCTION**

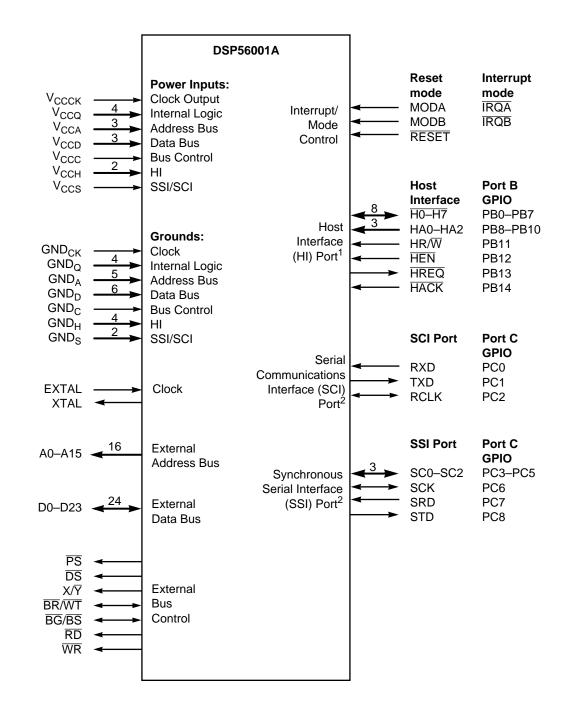

DSP56001A signals are organized into twelve functional groups as summarized in Table 1-1.

**Table 1-1** Signal Functional Group Allocations

| Functional Group                                                                                                                                                                                                                                                              | Number<br>of<br>Signals | Detailed<br>Description |           |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------|-----------|--|

| Power (V <sub>CCX</sub> )                                                                                                                                                                                                                                                     |                         | 5                       | Table 1-2 |  |

| Ground (GND <sub>X</sub> )                                                                                                                                                                                                                                                    |                         | 7                       | Table 1-3 |  |

| Clock                                                                                                                                                                                                                                                                         |                         | 2                       | Table 1-4 |  |

| Address Bus                                                                                                                                                                                                                                                                   |                         | 16                      | Table 1-5 |  |

| Data Bus                                                                                                                                                                                                                                                                      | 24                      | Table 1-6               |           |  |

| Bus Control                                                                                                                                                                                                                                                                   | 7                       | Table 1-7               |           |  |

| Interrupt and Mode Control                                                                                                                                                                                                                                                    | 3                       | Table 1-8               |           |  |

| Host Interface (HI) Port                                                                                                                                                                                                                                                      | 15                      | Table 1-9               |           |  |

| Serial Communications Interface (SCI) Port                                                                                                                                                                                                                                    | 3                       | Table 1-10              |           |  |

| Synchronous Serial Interface (SSI) Port                                                                                                                                                                                                                                       | 6                       | <b>Table 1-11</b>       |           |  |

| Note: 1. Port A signals define the External Memory Interface port. 2. Port B signals are GPIO signals multiplexed on the external pins also used with the HI signals. 3. Port C signals are GPIO signals multiplexed on the external pins also used by the SCI and SSI ports. |                         |                         |           |  |

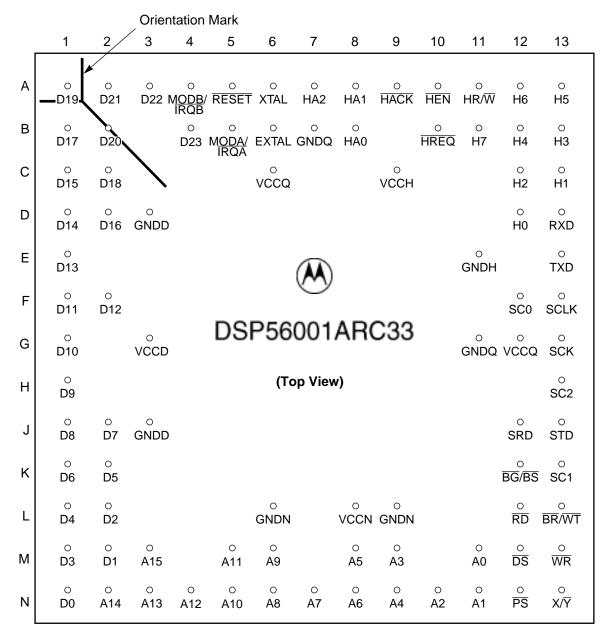

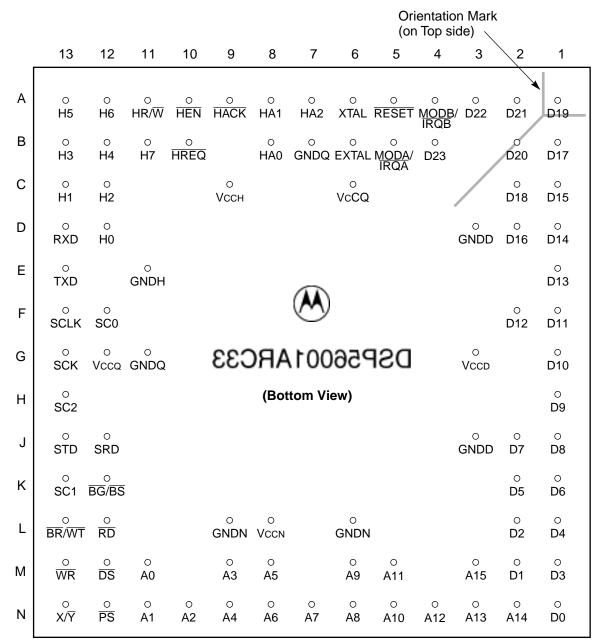

**Figure 1-1** is a diagram of DSP56001A signals by functional group.

#### Introduction

Note: 1. The H

- 1. The Host Interface port signals are multiplexed with the Port B GPIO signals (PB0-PB15).

- 2. The SCI and SSI signals are multiplexed with the Port C GPIO signals (PC0–PC8).

- 3. Power and ground lines are indicated for the 144-pin TQFP package.

AA0885

Figure 1-1 Signals Identified by Functional Group

# **POWER**

**Table 1-2** Power Connections

| Power Names          | Description                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CCQ</sub> (2) | Internal Logic Power—These lines supply a quiet power source to the oscillator circuits and the mode control and interrupt lines. Ensure that the input voltage to this line is well-regulated and uses an extremely low impedance path to tie to the $V_{CC}$ power rail. Use a 0.1 $\mu F$ bypass capacitor located as close as possible to the chip package to connect between the $V_{CCQ}$ lines and the $GND_Q$ lines. |

| V <sub>CCA</sub> (3) | Address Bus Power—These lines supply power to the address bus.                                                                                                                                                                                                                                                                                                                                                               |

| V <sub>CCD</sub> (3) | Data Bus Power—These lines supply power to the data bus.                                                                                                                                                                                                                                                                                                                                                                     |

| $V_{CCC}$            | Bus Control Power—This line supplies power to the bus control logic.                                                                                                                                                                                                                                                                                                                                                         |

| V <sub>CCH</sub> (2) | Host Interface Power—These lines supply power to the Host Interface logic.                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>CCS</sub>     | <b>Serial Interface Power</b> —This line supplies power to the serial interface logic (SCI and SSI).                                                                                                                                                                                                                                                                                                                         |

# **GROUND**

**Table 1-3** Ground Connections

| <b>Ground Names</b>  | Description                                                                                                                                                                                                                                                                                                                                                        |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND <sub>Q</sub> (2) | Internal Logic Ground—These lines supply a quiet ground connection for the oscillator circuits and the mode control and interrupt lines. Ensure that this line connects through an extremely low impedance path to ground. Use a 0.1 $\mu F$ bypass capacitor located as close as possible to the chip package to connect between the VCCQ line and the GNDQ line. |

| GND <sub>A</sub> (2) | Address Bus Ground—These lines connect system ground to the address bus.                                                                                                                                                                                                                                                                                           |

| GND <sub>D</sub> (2) | Data Bus Ground—These lines connect system ground to the data bus.                                                                                                                                                                                                                                                                                                 |

| GND <sub>H</sub> (1) | <b>Host Interface Ground</b> —These lines supply ground connections for the Host Interface logic.                                                                                                                                                                                                                                                                  |

Clock

# **CLOCK**

**Table 1-4** Clock Signals

| Signal<br>Name | Signal<br>Type | State<br>during<br>Reset | Signal Description                                                                                                                                                             |

|----------------|----------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

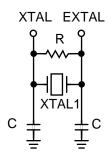

| EXTAL          | Input          | Input                    | <b>External Clock/Crystal Input</b> —This input should be connected to an external crystal or to an external oscillator.                                                       |

| XTAL           | Output         | Chip-<br>driven          | <b>Crystal Output</b> —This output connects the internal crystal oscillator output to an external crystal. If an external oscillator is used, XTAL should be left unconnected. |

# **ADDRESS BUS**

**Table 1-5** Address Bus Signals

| Signal<br>Names | Signal<br>Type | State<br>during<br>Reset | Signal Description                                                                                                                                                                                                                                                  |

|-----------------|----------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0-A15          | Output         | Tri-<br>stated           | Address Bus—These signals specify the address for external program and data memory accesses. If there is no external bus activity, A0–A15 remain at their previous values to reduce power consumption. A0–A15 are tri-stated when the bus grant signal is asserted. |

# **DATA BUS**

**Table 1-6** Data Bus Signals

| Signal<br>Names | Signal<br>Type   | State<br>during<br>Reset | Signal Description                                                                                                                                                                                                      |

|-----------------|------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0-D23          | Input/<br>Output | Tri-<br>stated           | <b>Data Bus</b> —These signals provide the bidirectional data bus for external program and data memory accesses. D0–D23 are tri-stated when the $\overline{\text{BG}}$ or $\overline{\text{RESET}}$ signal is asserted. |

**Bus Control**

# **BUS CONTROL**

**Table 1-7** Bus Control Signals

| Signal<br>Name   | Signal<br>Type   | State<br>during<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------|------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PS               | Output           | Tri-stated               | <b>Program Memory Select</b> — $\overline{PS}$ is asserted low for external program memory access. $\overline{PS}$ is tri-stated when the $\overline{BG}$ or $\overline{RESET}$ signal is asserted.                                                                                                                                                                                                                                                                                                                                                                                                              |

| DS               | Output           | Tri-stated               | <b>Data Memory Select</b> — $\overline{DS}$ is asserted low for external data memory access. $\overline{DS}$ is tri-stated when the $\overline{BG}$ or $\overline{RESET}$ signal is asserted.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $X/\overline{Y}$ | Output           | Tri-stated               | <b>X/<math>\overline{Y}</math> External Memory Select</b> —This output is driven low during external Y data memory accesses. It is also driven low during external exception vector fetches when operating in the Development mode. $X/\overline{Y}$ is tri-stated when the $\overline{BG}$ or $\overline{RESET}$ signal is asserted.                                                                                                                                                                                                                                                                            |

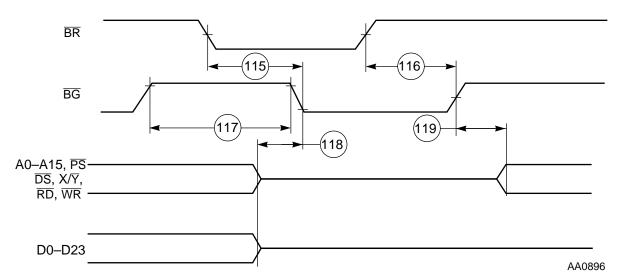

| BR               | Input/<br>Output | Tri-stated               | <b>Bus Request/Wait</b> —The bus request input $\overline{BR}$ allows another device such as a processor or DMA controller to become master of the external data bus D0–D23 and external address bus a0–a15. When operating mode register (OMR) bit 7 is clear and $\overline{BR}$ is asserted, the DSP56001A will always release the external data bus D0–D23, address bus A0–A15, and bus control signals $\overline{PS}$ , $\overline{DS}$ , $X/\overline{Y}$ , $\overline{RD}$ , and $\overline{WR}$ (i.e. Port A), by tri-stating these pins after execution of the current instruction has been completed. |

| WT               |                  |                          | If OMR bit 7 is set, this pin is an input that allows an external device to force wait states during an external Port A operation for as long as $\overline{\text{WT}}$ is asserted.  Note: To prevent erroneous operation, pull up the $\overline{\text{BR}}/\overline{\text{WT}}$ signal when it is not in use.                                                                                                                                                                                                                                                                                                |

| BG               | Input/<br>Output | Tri-stated               | Bus Grant/Bus Select—If OMR Bit 7 is clear, this output is asserted to acknowledge an external bus request after Port A has been released.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| BS               |                  |                          | If OMR Bit 7 is set, this signal is bus strobe, and is asserted when the DSP accesses Port A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| WR               | Output           | Tri-stated               | Write Enable— $\overline{WR}$ is asserted during external memory write cycles. $\overline{WR}$ is tri-stated when the $\overline{BG}$ or $\overline{RESET}$ signal is asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RD               | Output           | Tri-stated               | <b>Read Enable</b> — $\overline{RD}$ is asserted during external memory read cycles. $\overline{RD}$ is tri-stated when the $\overline{BG}$ or $\overline{RESET}$ signal is asserted.                                                                                                                                                                                                                                                                                                                                                                                                                            |

**Interrupt and Mode Control**

# INTERRUPT AND MODE CONTROL

Table 1-8

Interrupt and Mode Control Signals

| Signal Name | Signal<br>Type | State<br>during<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|----------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

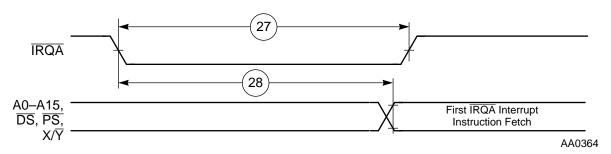

| MODA        | Input          | Input                    | Mode Select A/External Interrupt Request A—This input has two functions:  1. to select the initial chip operating mode, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ĪRQĀ        |                |                          | <ol><li>after synchronization, to allow an external device to<br/>request a DSP interrupt.</li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |                |                          | MODA is read and internally latched in the DSP on exit from Reset. MODA and MODB select the initial chip operating mode. After leaving the Reset state, the MODA signal changes to external interrupt request $\overline{IRQA}$ . The chip operating mode can be changed by software after reset. The $\overline{IRQA}$ input is a synchronized external interrupt request that indicates that an external device is requesting service. It may be programmed to be level-sensitive or negative-edge-triggered. If level-sensitive triggering is selected, an external pull up resistor is required for wired-OR operation. If the processor is in the Stop state and $\overline{IRQA}$ is asserted, the processor will exit the Stop state. |

| MODB        | Input          | Input                    | Mode Select B/External Interrupt Request B—This input has two functions:  1. to select the initial chip operating mode, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ĪRQB        |                |                          | 2. after internal synchronization, to allow an external device to request a DSP interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| шер         |                |                          | MODB is read and internally latched in the DSP on exit from Reset. MODA and MODB select the initial chip operating mode. After leaving the Reset state, the MODB signal changes to external interrupt request $\overline{IRQB}$ . After reset, the chip operating mode can be changed by software. The $\overline{IRQB}$ input is an external interrupt request that indicates that an external device is requesting service. It may be programmed to be level sensitive or negative-edgetriggered. If level-sensitive triggering is selected, an external pull up resistor is required for wired-OR operation.                                                                                                                              |

| RESET       | Input          | Input                    | $ \begin{array}{c} \textbf{Reset} - \textbf{This} \ input \ is \ a \ direct \ hardware \ reset \ on \ the \ processor. \\ When \ \overline{RESET} \ is \ asserted \ low, \ the \ DSP \ is \ initialized \ and \ placed \ in \\ the \ Reset \ state. \ A \ Schmitt \ trigger \ input \ is \ used \ for \ noise \ immunity. \\ When \ the \ \overline{RESET} \ signal \ is \ deasserted, \ the \ initial \ chip \ operating \\ mode \ is \ latched \ from \ MODA \ and \ MODB. \ The \ internal \ reset \ signal \\ is \ deasserted \ synchronously \ with \ the \ internal \ clocks. \\ \end{array} $                                                                                                                                         |

**Interrupt and Mode Control**

# **CAUTION**

DO NOT APPLY 10 VOLTS TO ANY PIN OF THE DSP56001A (including MODB)! Subjecting any pin of the DSP56001A to voltages in excess of the specified TTL/CMOS levels will permanently damage the device.

**Host Interface (HI) Port**

# **HOST INTERFACE (HI) PORT**

Table 1-9 HI Signals

| Signal<br>Name | Signal<br>Type     | State<br>during<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|----------------|--------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

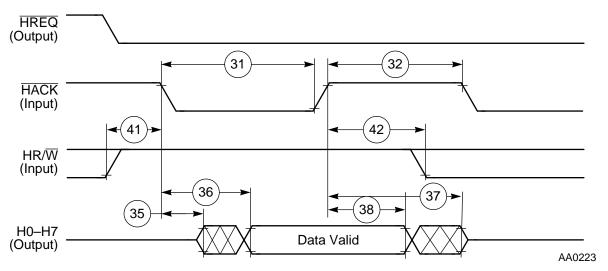

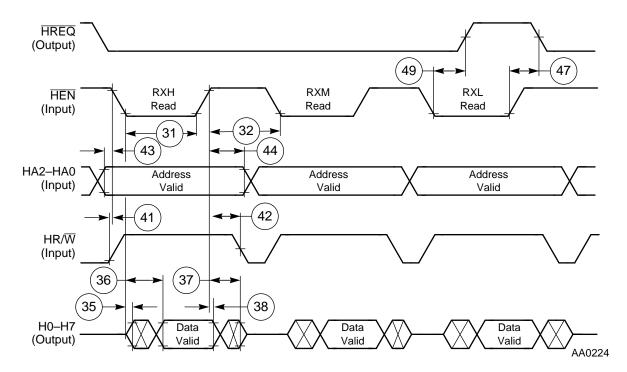

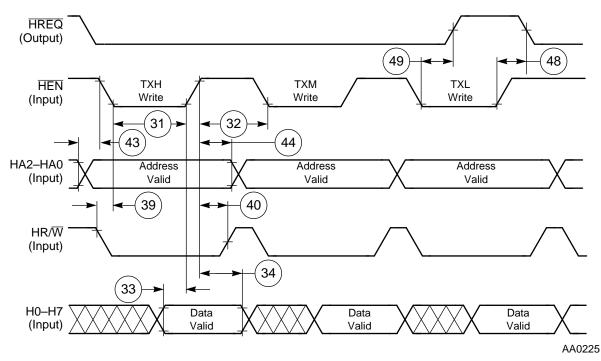

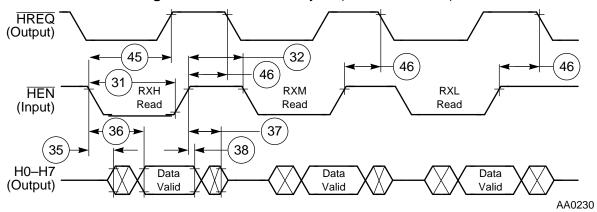

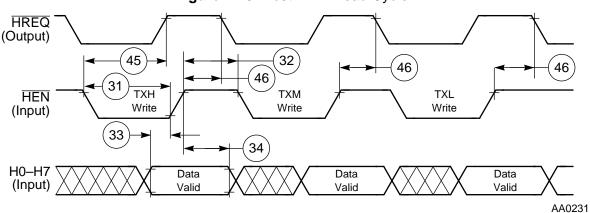

| Н0-Н7          | Input/<br>Output   | Tri-stated               | Host Data Bus (H0–H7)—This data bus transfers data between the host processor and the DSP56001A. When configured as a Host Interface port, the H0–H7 signals are tri-stated as long as $\overline{\text{HEN}}$ is deasserted. The signals are inputs unless $\overline{\text{HR}}/\overline{\text{W}}$ is high and $\overline{\text{HEN}}$ is asserted, in which case H0–H7 become outputs, allowing the host processor to read the DSP56001A data. H0–H7 become outputs when $\overline{\text{HACK}}$ is asserted during $\overline{\text{HREQ}}$ assertion. |  |

| PB0-PB7        | Input or<br>Output |                          | <b>Port B GPIO 0–7 (PB0–PB7)</b> —These signals are GPIO signals (PB0–PB7) when the Host Interface is not selected.                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                |                    |                          | After reset, the default state for these signals is GPIO input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| HA0-HA2        | Input              | Tri-stated               | <b>Host Address 0 – Host Address 2 (HA0–HA2)</b> —These inputs provide the address selection for each Host Interface register.                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| PB8-PB10       | Input or<br>Output |                          | <b>Port B GPIO 8–10 (PB8–PB10)</b> —These signals are GPIO signals (PB8–PB10) when the Host Interface is not selected.                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                |                    |                          | After reset, the default state for these signals is GPIO input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| HR/W           | Input              | Tri-stated               | <b>Host Read/Write</b> —This input selects the direction of data transfer for each host processor access. If $HR/\overline{W}$ is high and $\overline{HEN}$ is asserted, H0–H7 are outputs and DSP data is transferred to the host processor. If $HR/\overline{W}$ is low and $\overline{HEN}$ is asserted, H0–H7 are inputs and host data is transferred to the DSP. $HR/\overline{W}$ must be stable when $\overline{HEN}$ is asserted.                                                                                                                     |  |

| PB11           | Input or<br>Output |                          | <b>Port B GPIO 11 (PB11)</b> —This signal is a GPIO signal called PB11 when the Host Interface is not being used.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                |                    |                          | After reset, the default state for this signal is GPIO input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

Host Interface (HI) Port

Table 1-9 HI Signals (Continued)

| Signal<br>Name | Signal<br>Type          | State<br>during<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|----------------|-------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| HEN            | Input                   | Tri-stated               | <b>Host Enable</b> —This input enables a data transfer on the host data bus. When $\overline{\text{HEN}}$ is asserted and $\overline{\text{HR}}/\overline{\text{W}}$ is high, H0–H7 become outputs and the host processor may read DSP56001A data. When $\overline{\text{HEN}}$ is asserted and $\overline{\text{HR}}/\overline{\text{W}}$ is low, H0–H7 become inputs. Host data is latched in the DSP on the rising edge of $\overline{\text{HEN}}$ . Normally, a chip select signal derived from host address decoding and an enable strobe are used to generate $\overline{\text{HEN}}$ . |  |

| PB12           | Input or<br>Output      |                          | <b>Port B GPIO 12 (PB12)</b> —This signal is aGPIO signal called PB12 when the Host Interface is not being used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                |                         |                          | After reset, the default state for this signal is GPIO input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| HREQ           | Open<br>drain<br>Output | Tri-stated               | <b>Host Request</b> —This signal is used by the Host Interface to request service from the host processor, DMA controller, or a simple external controller.                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|                |                         |                          | Note: HREQ should always be pulled high when it is not in use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| PB13           | Input or<br>Output      |                          | <b>Port B GPIO 13 (PB13)</b> —This signal is a GPIO (not open-drain) signal (PB13) when the Host Interface is not selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|                |                         |                          | After reset, the default state for this signal is GPIO input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| HACK           | Input                   | Tri-stated               | <b>Host Acknowledge</b> —This input has two functions. It provides a host acknowledge handshake signal for DMA transfers and it receives a host interrupt acknowledge compatible with MC68000 family processors.                                                                                                                                                                                                                                                                                                                                                                              |  |

| PB14           |                         |                          | Note: HACK should always be pulled high when it is not in use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                | Input or<br>Output      |                          | <b>Port B GPIO 14 (PB14)</b> —This signal is a GPIO signal (PB14) when the Host Interface is not selected, and may be programmed as a GPIO signal when the Host Interface is selected.                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                |                         |                          | After reset, the default state for this signal is GPIO input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

**Serial Communications Interface Port**

# SERIAL COMMUNICATIONS INTERFACE PORT

Table 1-10

Serial Communications Interface (SCI) Signals

| Signal Name | Signal<br>Type     | State<br>during<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                     |  |

|-------------|--------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

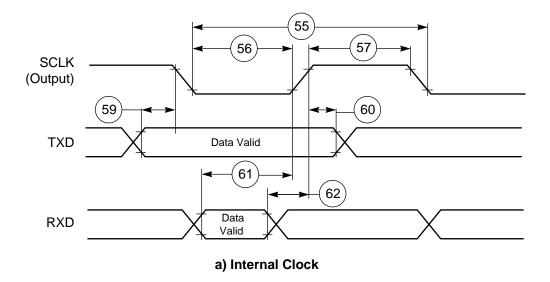

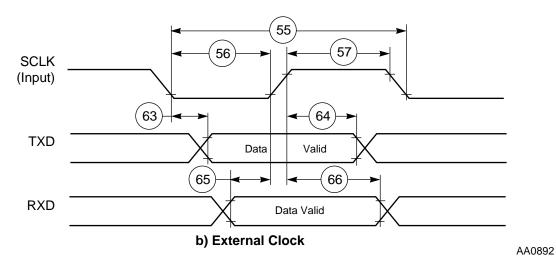

| RXD         | Input              | Tri-stated               | Receive Data (RXD)—This input receives byte-oriented data and transfers the data to the SCI receive shift register. Input data can be sampled on either the positive edge or on the negative edge of the receive clock, depending on how the SCI control register is programmed.                                       |  |

| PC0         | Input or<br>Output |                          | <b>Port C GPIO 0 (PC0)</b> —This signal is a GPIO signal called PC0 when the SCI RXD function is not being used.                                                                                                                                                                                                       |  |

|             |                    |                          | After reset, the default state is GPIO input.                                                                                                                                                                                                                                                                          |  |

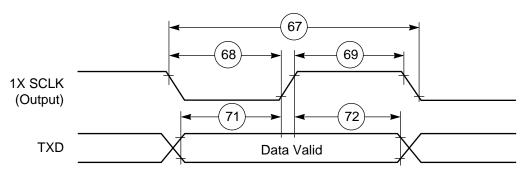

| TXD         | Output             | Tri-stated               | <b>Transmit Data (TXD)</b> —This output transmits serial data from the SCI transmit shift register. In the default configuration, the data changes on the positive clock edge and is valid on the negative clock edge. The user can reverse this clock polarity by programming the SCI control register appropriately. |  |

| PC1         | Input or<br>Output |                          | <b>Port C GPIO 1 (PC1)</b> —This signal is a GPIO signal called PC1 when the SCI TXD function is not being used.                                                                                                                                                                                                       |  |

|             |                    |                          | After reset, the default state is GPIO input.                                                                                                                                                                                                                                                                          |  |

| SCLK        | Input/<br>Output   | Tri-stated               | SCI Clock (SCLK)—This signal provides an input or output clock from which the transmit/receive baud rate is derived in the Asynchronous mode, and from which data is transferred in the Synchronous mode. The direction and function of the signal is defined by the RCM bit in the SCI Clock Control Register (SCCR). |  |

| PC2         | Input or<br>Output |                          | <b>Port C GPIO 2 (PC2)</b> —This signal is a GPIO signal called PC2 when the SCI TCLK function is not being used.                                                                                                                                                                                                      |  |

|             |                    |                          | After reset, the default state is GPIO input.                                                                                                                                                                                                                                                                          |  |

**Synchronous Serial Interface Port**

# SYNCHRONOUS SERIAL INTERFACE PORT

Table 1-11 Synchronous Serial Interface (SSI) Signals

| Signal Name | Signal<br>Type     | State<br>during<br>Reset | Signal Description                                                                                                                                                                                     |  |

|-------------|--------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SC0         | Input or<br>Output | Tri-stated               | <b>Serial Clock 0 (SC0)</b> —This signal's function is determined by whether the SCLK is in Synchronous or Asynchronous mode.                                                                          |  |

|             |                    |                          | • In Synchronous mode, this signal is used as a serial I/O flag.                                                                                                                                       |  |

| PC3         | Input or<br>Output |                          | • In Asynchronous mode, this signal receives clock I/O. <b>Port C GPIO 3 (PC3)</b> —This signal is GPIO signal PC3 when not configured as SCI signal SC0.                                              |  |

|             |                    |                          | After reset, the default state is GPIO input.                                                                                                                                                          |  |

| SC1         | Input or<br>Output | Tri-stated               | Serial Clock 1 (SC1)—The SSI uses this bidirectional signal to control flag or frame synchronization. This signal's function is determined by whether the SCLK is in Synchronous or Asynchronous mode. |  |

|             |                    |                          | <ul> <li>In Asynchronous mode, this signal is frame sync I/O.</li> </ul>                                                                                                                               |  |

|             |                    |                          | <ul> <li>For Synchronous mode with continuous clock, this signal is<br/>a serial I/O flag and operates like the SCO.</li> </ul>                                                                        |  |

|             |                    |                          | SC0 and SC1 are independent serial I/O flags, but may be used together for multiple serial device selection.                                                                                           |  |

| PC4         | Input or<br>Output |                          | <b>Port C GPIO 4 (PC4)</b> —This signal is GPIO signal PC4 when not configured as SSI function SC1.                                                                                                    |  |

|             |                    |                          | After reset, the default state is GPIO input.                                                                                                                                                          |  |

| SC2         | Input or<br>Output | Tri-stated               | <b>Serial Clock 2 (SC2)</b> —The SSI uses this bidirectional signal to control frame synchronization only. As with SC0 and SC1, its function is defined by the SSI operating mode.                     |  |

| PC5         | Input or<br>Output |                          | <b>Port C GPIO 5 (PC5)</b> —This signal is GPIO signal PC5 when not configured as SSI function SC1.                                                                                                    |  |

|             |                    |                          | After reset, the default state is GPIO input.                                                                                                                                                          |  |

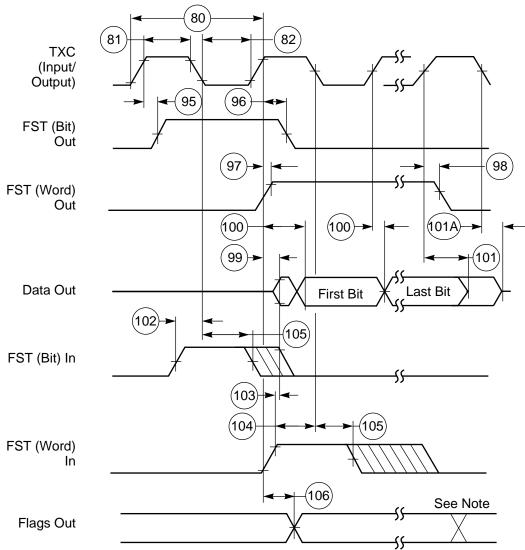

| SCK         | Input or<br>Output | Tri-stated               | SSI Serial Receive Clock—This bidirectional signal provides the serial bit rate clock for the SSI when only one clock is being used.                                                                   |  |

| PC6         | Input or<br>Output |                          | <b>Port C GPIO 6 (PC6)</b> —This signal is GPIO signal PC6 when the SSI function is not being used.                                                                                                    |  |

|             |                    |                          | After reset, the default state is GPIO input.                                                                                                                                                          |  |

#### **Synchronous Serial Interface Port**

**Table 1-11** Synchronous Serial Interface (SSI) Signals (Continued)

| Signal Name | Signal<br>Type     | State<br>during<br>Reset | Signal Description                                                                                                |

|-------------|--------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------|

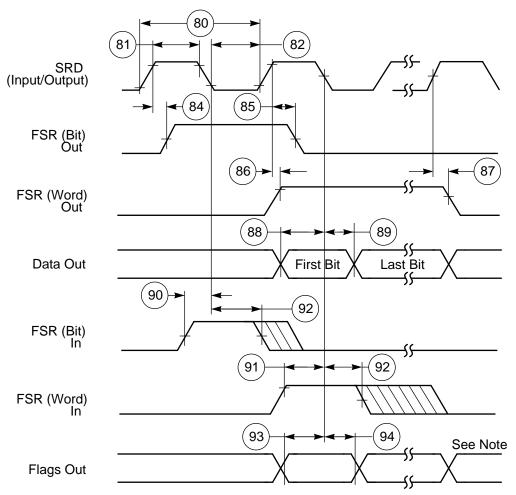

| SRD         | Input              | Tri-stated               | SSI Receive Data—This input signal receives serial data and transfers the data to the SSI Receive Shift Register. |

| PC7         | Input or<br>Output |                          | <b>Port C GPIO 7 (PC7)</b> —This signal is GPIO signal PC7 when the SSI SRD function is not being used.           |

|             |                    |                          | After reset, the default state is GPIO input.                                                                     |

| STD         | Output             | Tri-stated               | <b>SSI Transmit Data (STD)</b> —This output signal transmits serial data from the SSI Transmitter Shift Register. |

| PC8         | Input or<br>Output |                          | <b>Port C GPIO 8 (PC8)</b> —This signal is GPIO signal PC8 when the SSI STD function is not being used.           |

|             |                    |                          | After reset, the default state is GPIO input.                                                                     |

# SECTION 2 SPECIFICATIONS

#### GENERAL CHARACTERISTICS

The DSP56001A is fabricated in high-density HCMOS with TTL compatible inputs and outputs.

**Table 2-1** Absolute Maximum Ratings (GND = 0 V)

| Rating                                                  | Symbol           | Value                             | Unit |

|---------------------------------------------------------|------------------|-----------------------------------|------|

| Supply Voltage                                          | V <sub>CC</sub>  | -0.3 to +7.0                      | V    |

| All Input Voltages                                      | V <sub>IN</sub>  | $(GND - 0.5)$ to $(V_{CC} + 0.5)$ | V    |

| Current Drain per Pin excluding V <sub>CC</sub> and GND | I                | 10                                | mA   |

| Storage Temperature                                     | T <sub>stg</sub> | -55 to +150                       | °C   |

Note: This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g., either GND or  $V_{CC}$ ).

Table 2-2 Recommended Operating Conditions

| Rating                                   | Symbol          | Value       | Unit |

|------------------------------------------|-----------------|-------------|------|

| Supply Voltage                           | V <sub>CC</sub> | 4.5 to 5.5  | V    |

| Operating Temperature Range (See Note 1) | T <sub>A</sub>  | -40 to +105 | °C   |

**Table 2-3** Thermal Characteristics for 88-pin PGA Package

| Thermal Resistance                        | Symbol         | Value | Rating |

|-------------------------------------------|----------------|-------|--------|

| Junction to Ambient (See Note 2)          | $R_{	heta JA}$ | 27    | °C/W   |

| Junction to Case (estimated) (See Note 3) | $R_{	heta JC}$ | 6.5   | °C/W   |

#### **General Characteristics**

Table 2-4 Thermal Characteristics for 132-pin CQFP/PQFP Packages

| Thermal Resistance           | Symbol         | Value                     | Rating |

|------------------------------|----------------|---------------------------|--------|

| Junction to Ambient          | $R_{	heta JA}$ | 40 (CQFP)<br>47 (PQFP)    | °C/W   |

| Junction to Case (estimated) | $R_{	heta JC}$ | 7.0 (CQFP)<br>13.0 (PQFP) | °C/W   |

Note:

- 1. See discussion under **Design Considerations**, **Heat Dissipation**, **page 4-1**.

- Junction-to-ambient thermal resistance is based on measurements on a horizontal single-sided Printed Circuit Board per SEMI G38-87 in natural convection. SEMI is Semiconductor Equipment and Materials International, 805 East Middlefield Road, Mountain View, CA 94043, (415) 964-5111.

- Junction-to-case thermal resistance is based on measurements using a cold plate per SEMI G30-88 with the exception that the cold plate temperature is used for the case temperature.

**DC Electrical Characteristics**

# DC ELECTRICAL CHARACTERISTICS

Table 2-5

DC Electrical Characteristics

| Characteristics                                                                                                                | Symbol           | Min  | Тур | Max      | Units |

|--------------------------------------------------------------------------------------------------------------------------------|------------------|------|-----|----------|-------|

| Supply Voltage 27 MHz                                                                                                          | V <sub>CC</sub>  | 4.5  | 5.0 | 5.5      | V     |

| 33 MHz                                                                                                                         |                  | 4.75 | 5.0 | 5.25     | V     |

| Input High Voltage                                                                                                             |                  |      |     |          |       |

| •EXTAL                                                                                                                         | VIHC             | 4.0  | _   | $V_{CC}$ | V     |

| •RESET                                                                                                                         | VIHR             | 2.5  | _   | $V_{CC}$ | V     |

| • MODA, MODB                                                                                                                   | VIHM             | 3.5  | _   | $V_{CC}$ | V     |

| All other inputs                                                                                                               | VIH              | 2.0  | _   | $V_{CC}$ | V     |

| Input Low Voltage                                                                                                              |                  |      |     |          |       |

| • EXTAL                                                                                                                        | V <sub>ILC</sub> | -0.5 | _   | 0.6      | V     |

| • MODA, MODB                                                                                                                   | $V_{ILM}$        | -0.5 | _   | 2.0      | V     |

| All other inputs                                                                                                               | $V_{IL}$         | -0.5 | _   | 0.8      | V     |

| Input Leakage Current EXTAL, RESET, MODA/IRQA, MODB/IRQB, DR, BR/WT                                                            | I <sub>IN</sub>  | -1   | _   | 1        | μА    |

| Tri-state (Off-state) Input Current (@ 2.4 V/0.4 V)                                                                            | I <sub>TSI</sub> | -10  | _   | 10       | μА    |

| Output High Voltage (I <sub>OH</sub> = -0.4 mA)                                                                                | V <sub>OH</sub>  | 2.4  | _   | _        | V     |

| $\frac{\text{Output Low Voltage (I}_{OL} = 1.6 \text{ mA)}}{\text{HREQ I}_{OL} = 6.7 \text{ mA, TXD I}_{OL} = 6.7 \text{ mA}}$ | V <sub>OL</sub>  | _    | _   | 0.4      | V     |

| Internal Supply Current at 33 MHz (Note 1)                                                                                     | I <sub>CCI</sub> |      | 80  | 115      | mA    |

| • In Wait mode (Note 2)                                                                                                        | I <sub>CCW</sub> | _    | 10  | 25       | mA    |

| • In Stop mode (Note 2)                                                                                                        | I <sub>CCS</sub> |      | 2   | 2000     | μΑ    |

| Input Capacitance (Note 3)                                                                                                     | C <sub>IN</sub>  | _    | 10  | _        | pF    |

Note:

- 1. **Section 4 Design Considerations** describes how to calculate the external supply current.

- 2. In order to obtain these results all inputs must be terminated (i.e., not allowed to float).

- 3. Periodically sampled and not 100% tested

**AC Electrical Characteristics**

#### **AC ELECTRICAL CHARACTERISTICS**

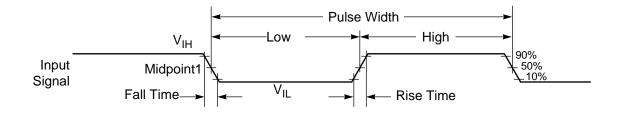

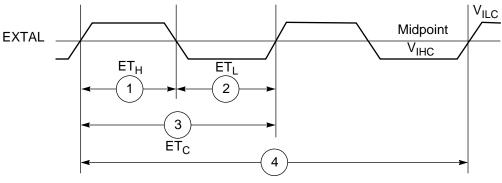

The midpoint is  $V_{IL} + (V_{IH} - V_{IL})/2$ .

The timing waveforms in the AC Electrical Characteristics are tested with a  $V_{IL}$  maximum of 0.5 V and a  $V_{IH}$  minimum of 2.4 V for all pins, except EXTAL,  $\overline{\text{RESET}},$  MODA, and MODB. These pins are tested using the input levels set forth in the DC electrical characteristics. AC timing specifications that are referenced to a device input signal are measured in production with respect to the 50% point of the respective input signal's transition. DSP56001A output levels are measured with the production test machine  $V_{OL}$  and  $V_{OH}$  reference levels set at 0.8 V and 2.0 V, respectively.

Figure 2-1 Signal Measurement Reference

#### **INTERNAL CLOCKS**

Note:

For each occurrence of  $T_H$ ,  $T_L$ ,  $T_C$  or  $I_{CYC}$ , substitute with the numbers in **Table 2-6**.

Table 2-6 Internal Clocks

| Characteristics              | Symbol           | Expression       |

|------------------------------|------------------|------------------|

| Internal Operation Frequency | f                |                  |

| Internal Clock High Period   | T <sub>H</sub>   | ET <sub>H</sub>  |

| Internal Clock Low Period    | $T_{ m L}$       | $ET_L$           |

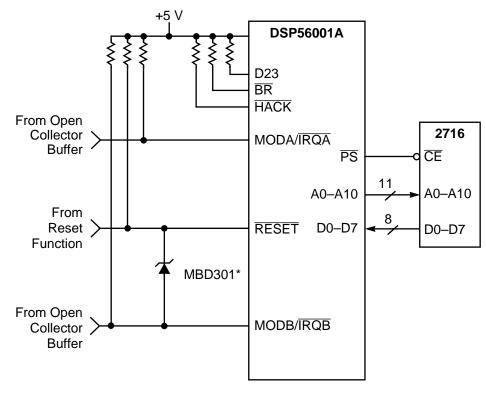

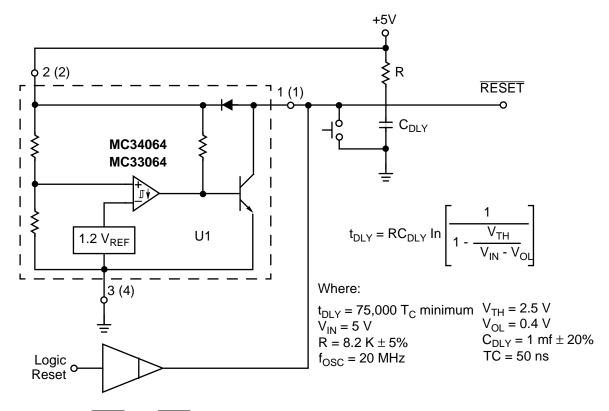

| Internal Clock Cycle Time    | T <sub>C</sub>   | ET <sub>C</sub>  |