# M62021L/P/FP

## System Reset IC with Switch for Memory Backup

REJ03D0784-0200 Rev.2.00 Jun 15, 2007

#### **Description**

The M62021 is a system IC that controls the memory backup function of microcomputer (internal RAM).

The IC outputs reset signals (RES/ $\overline{RES}$ ) to a microcomputer at power-down and power failure. It also shifts the power supply to RAM from main to backup, outputs a signal ( $\overline{CS}$ ) that invokes standby mode, and alters RAM to backup circuit mode.

The M62021 contains, in a single chip, power supply monitor and RAM backup functions needed for a microcomputer system, so that the IC makes it possible to construct a system easily and with fewer components compared with a conventional case that uses individual ICs and discrete components.

#### **Features**

- Built-in switch for selection between main power supply and backup power supply to RAM.

- Small difference between input and output voltage ( $I_{OUT}$  = 80 mA,  $V_{IN}$  = 5 V) 0.2 V Typ

- Detection voltage (power supply monitor voltage) 4.40 V  $\pm$  0.2 V

- Chip select signal output (CS)

- Two channels of reset outputs (RES/RES)

- Power on reset circuit built-in

- Delay time variable by an external capacitance connected to Ct pin

- · Facilitates to form backup function with a few number of components

## **Application**

Power supply control systems for memory backup of microcomputer system and SRAM boards with built-in backup function that require switching between external power supply and battery.

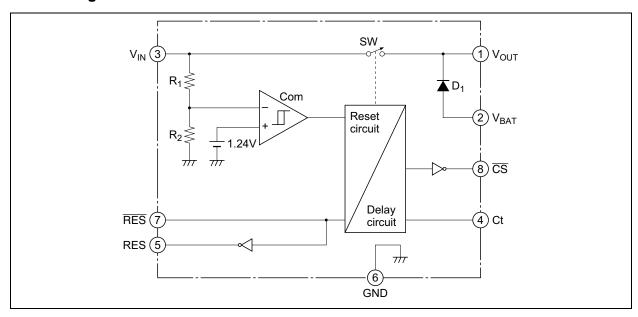

#### **Block Diagram**

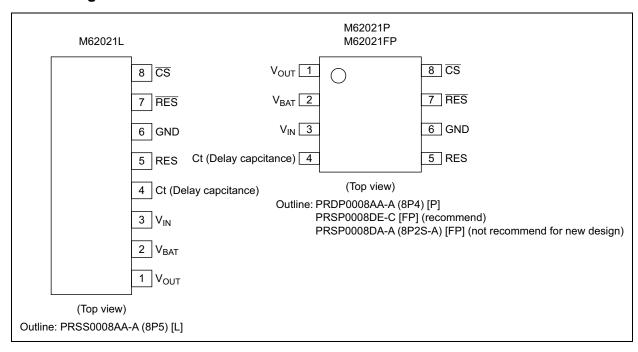

### **Pin Arrangement**

## **Absolute Maximum Ratings**

$(Ta = 25^{\circ}C, unless otherwise noted)$

| Item                  | Symbol           | Ratings     | Unit  | С         | onditions |

|-----------------------|------------------|-------------|-------|-----------|-----------|

| Input voltage         | V <sub>IN</sub>  | 7           | V     |           |           |

| Output current        | I <sub>OUT</sub> | 100         | mA    |           |           |

| Power dissipation     | Pd               | 800         | mW    | 8-pin SIP |           |

|                       |                  | 625         |       | 8-pin DIP |           |

|                       |                  | 440         |       | 8-pin SOP |           |

| Thermal derating      | Kθ               | 8           | mW/°C | Ta ≥ 25°C | 8-pin SIP |

|                       |                  | 6.25        |       |           | 8-pin DIP |

|                       |                  | 4.4         |       |           | 8-pin SOP |

| Operating temperature | Topr             | -20 to +75  | °C    |           |           |

| Storage temperature   | Tstg             | -40 to +125 | °C    |           |           |

#### **Electrical Characteristics**

(Ta = 25°C, unless otherwise noted)

| Item                                         | Symbol                    | Min  | Тур   | Max  | Unit | Test Conditions                          |                          |  |

|----------------------------------------------|---------------------------|------|-------|------|------|------------------------------------------|--------------------------|--|

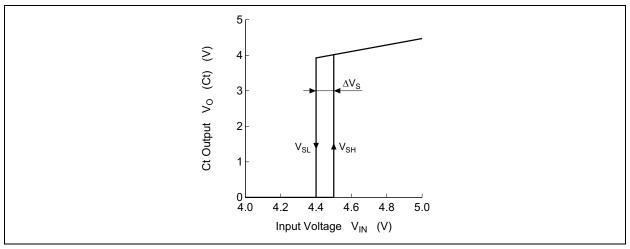

| Detection voltage                            | Vs                        | 4.2  | 4.4   | 4.6  | V    | V <sub>IN</sub> (at the change from H→L) |                          |  |

| Hysteresis voltage                           | ΔVs                       | 50   | 100   | 200  | mV   | $\Delta V_{S} = V_{SH} - V_{SL}$         |                          |  |

| Temperature coefficient of detection voltage | V <sub>S</sub> /∆T        | _    | 0.005 | _    | %/°C |                                          |                          |  |

|                                              |                           |      | 0.0   | 4.0  | A    | J 0 A                                    | 11/ 41/                  |  |

| Circuit current                              | Icc                       |      | 2.0   | 4.0  | mA   | $I_{OUT} = 0mA$                          | $V_{IN} = 4V$            |  |

|                                              |                           |      | 7.5   | 12.0 |      |                                          | V <sub>IN</sub> = 5V     |  |

| Difference between input and                 | $V_{DROP}$                |      | 0.125 | 0.25 | V    | $V_{IN} = 5V$                            | $I_{OUT} = 50mA$         |  |

| output voltage                               |                           |      | 0.2   | 0.4  |      |                                          | $I_{OUT} = 80 \text{mA}$ |  |

| Ct output voltage (high level)               | V <sub>OH(Ct)</sub>       | 4.5  | 5.0   | _    | V    | $V_{IN} = 5V^{*1}$                       |                          |  |

| Ct output voltage (low level)                | $V_{OL(Ct)}$              | _    | 0.02  | 0.1  | V    | $V_{IN} = 4V^{*1}$                       |                          |  |

| RES output voltage (high level)              | V <sub>OH(RES)</sub>      | 3.5  | 4.0   | _    | V    | $V_{IN} = 4V^{*1}$                       |                          |  |

| RES output voltage (low level)               | V <sub>OL(RES)</sub>      | _    | 0.02  | _    | V    | $V_{IN} = 5V$                            | *1                       |  |

|                                              |                           |      | 0.05  | 0.2  |      |                                          | Isink = 1mA              |  |

| RES output voltage (high level)              | V <sub>OH(RES)</sub>      | 4.5  | 5.0   | _    | V    | $V_{IN} = 5V^{*1}$                       |                          |  |

| RES output voltage (low level)               | V <sub>OL(RES)</sub>      |      | 0.02  | _    | V    | $V_{IN} = 4V$                            | *1                       |  |

|                                              |                           |      | 0.05  | 0.2  |      |                                          | Isink = 1mA              |  |

| CS output voltage (high level)               | $V_{OH(\overline{CS})}$   | 3.50 | 3.57  | _    | V    | $V_{IN} = 4V^{*2}$                       |                          |  |

|                                              |                           | 2.40 | 2.47  | _    |      | $V_{IN} = 0V$ , $V_{BAT} = 3$            | 3V * <sup>2</sup>        |  |

| CS output voltage (low level)                | V <sub>OL(CS)</sub>       | _    | 0.08  | _    | V    | $V_{IN} = 5V$                            | *1                       |  |

|                                              |                           | _    | 0.1   | 0.3  |      |                                          | Isink = 1mA              |  |

| Backup diode leakage current                 | I <sub>R</sub>            | _    | _     | ±0.5 | μΑ   | $V_{BAT} = 3V$                           | $V_{IN} = 5V$            |  |

|                                              |                           | _    | _     | ±0.5 |      |                                          | $V_{IN} = 0V$            |  |

| Backup diode forward direction               | V <sub>F</sub>            | _    | 0.54  | 0.6  | V    | $I_F = 10\mu A$                          |                          |  |

| voltage                                      |                           |      |       |      |      |                                          |                          |  |

| Delay time                                   | t <sub>pd</sub>           | 10   | 27    | 55   | ms   | $V_{IN} = 0V \rightarrow 5V$ , Ct        | = 4.7μF                  |  |

| Response time                                | t <sub>d</sub>            | _    | 5.0   | 25.0 | μS   | V <sub>IN</sub> = 5V→4V                  |                          |  |

| RES limit voltage of operation               | $V_{OPL(\overline{RES})}$ |      | 0.65  | _    | V    | *3                                       |                          |  |

Notes: 1. Regarding conditions to measure V<sub>OH</sub> and V<sub>OL</sub>, voltage values are to be generated by internal resistance only and no external resistor is used.

- 2. These values are produced inserting an external resistor,  $R_{\overline{CS}} = 1 \text{ M}\Omega$ , between the  $\overline{CS}$  pin and GND.

- 3. With no external resistor (10  $k\Omega$  internal resistance only)

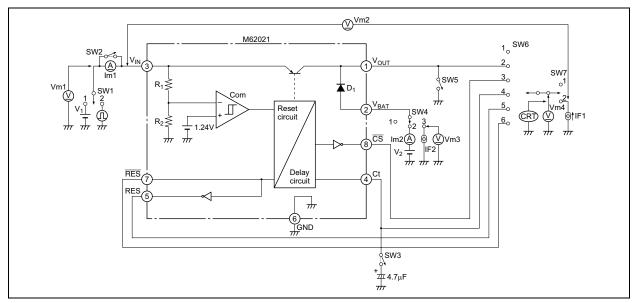

#### **Test Circuit**

Figure 1 Test Circuit

#### **Switch Matrix**

|                                                              |                                   |                     |    |                |      |         | SW |          |   |     | Measuring             |   |                   |

|--------------------------------------------------------------|-----------------------------------|---------------------|----|----------------|------|---------|----|----------|---|-----|-----------------------|---|-------------------|

| Item                                                         | Symbol                            | V1                  | V2 | IF1            | IF2  | 1       | 2  | 3        | 4 | 5   | 6                     | 7 | Instrument        |

| Circuit current                                              | I <sub>CC</sub>                   | 4V<br>5V            | _  | _              | _    | 1       | ON | OFF      | 1 | OFF | 1                     | 1 | lm1               |

| Detection voltage (V <sub>IN</sub> negative-going)           | V <sub>S</sub> (V <sub>SL</sub> ) | Decrease<br>from 5V | ı  | _              |      | 1       | ON | OFF      | 1 | OFF | 2<br>3<br>4<br>5<br>6 | 1 | vm4<br>CRT<br>Vm1 |

| Difference between input and output voltage                  | $V_{DROP}$                        | 5V                  | -  | -50mA<br>-80mA | -    | 1       | ON | OFF      | 1 | OFF | 2                     | 2 | Vm2               |

| Ct output voltage (high level) Ct output voltage (low level) | V <sub>OH(Ct)</sub>               | 5V<br>4V            | _  | _              | _    | 1       | ON | OFF      | 1 | OFF | 4                     | 1 | Vm4               |

| RES output voltage (high level)                              | V <sub>OH(RES)</sub>              | 4V                  |    |                |      |         |    |          |   |     |                       | 1 |                   |

| RES output voltage (low level)                               | V <sub>OL(RES)</sub>              | 5V                  | -  | 1mA            | _    | 1       | ON | OFF      | 1 | OFF | 5                     | 2 | Vm4               |

| RES output voltage (high level)                              | V <sub>OH(RES)</sub>              | 5V                  |    |                |      |         |    |          |   |     |                       | 1 |                   |

| RES output voltage (low level)                               | $V_{OL(\overline{RES})}$          | 4V                  | l  | 1mA            | ı    | 1       | ON | OFF      | 1 | OFF | 6                     | 2 | Vm4               |

| CS output voltage (high level) *1                            | $V_{OH(\overline{CS})}$           | 4V                  |    |                |      |         |    |          |   |     |                       |   |                   |

| Co output voltage (riight level)                             | V OH(CS)                          | 0V                  | 3V | _              | _    | 1       | ON | OFF      | 1 | OFF | 3                     | 1 | Vm4               |

| CS output voltage (low level)                                | $V_{OL(\overline{CS})}$           | 5V                  | 1  | 1mA            |      | ·       | ON | OIT      | · | OIT | ,                     | 2 | VIII-             |

| Backup diode leakage current                                 | I <sub>R</sub>                    | 5V<br>0V            | 3V | _              | _    | 1       | ON | OFF      | 2 | OFF | 1                     | 1 | lm2               |

| Backup diode forward direction voltage                       | V <sub>F</sub>                    | 0V                  |    | _              | 10μΑ | 1       | ON | OFF      | 3 | ON  | 1                     | 1 | Vm3               |

| Vout   CS   Response time   RES   RES                        | t <sub>pd</sub>                   | _                   | _  |                | _    | 2<br>*3 | ON | ON<br>*4 | 1 | OFF | 2<br>3<br>5<br>6      | 1 | CRT               |

Notes: 1. To measure  $V_{OH(\overline{CS})}$ , insert a 1 M $\Omega$  resistor between the  $\overline{CS}$  pin and GND.

- 2. While monitoring each output by Vm4 or CRT, measure the input voltage Vm1 when the output goes from H to L and L to H. Regarding  $V_{SH}$ , raise  $V_{IN}$  from 4 V and measure the input voltage Vm1 when the output goes from H to L and L to H.  $\Delta V_S$  is  $V_{SH} V_{SL}$ .

- 3. To measure delay time, change VIN from 0 V to 5 V and compare, with respect to each pin, the positive-going edge observed on a monitor with that of  $V_{IN}$ . To measure response time, change  $V_{IN}$  from 5 V to 4 V and compare, with respect to each pin, the negative-going edge observed on a monitor with that of  $V_{IN}$ .

- 4. Set the switch to OFF when measuring response time.

### **Pin Description**

| Pin No. | Pin Name                       | Symbol           | Function                                                                                                                                                                                                                                                                                               |

|---------|--------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | Power supply output            | V <sub>оит</sub> | VIN and VBAT are controlled by means of an internal switch and output through VOUT.  The pin is capable of outputting up to 100 mA. Use it as VDD of CMOS RAM and the like.                                                                                                                            |

| 2       | Backup power supply input      | $V_{BAT}$        | Backup power supply is connected to this pin.  If a lithium battery is used, insert a resistor in series for safety purposes.                                                                                                                                                                          |

| 3       | Power supply input             | V <sub>IN</sub>  | +5 V input pin. Connect to a logic power supply.                                                                                                                                                                                                                                                       |

| 4       | Delay capacitor connection pin | Ct               | A delay capacitor is connected to this pin. By connecting a capacitor, it is possible to delay each output.                                                                                                                                                                                            |

| 5       | Positive reset output          | RES              | Connect to the positive reset input of a microcomputer. The pin is capable of flowing 1 mA sink current.                                                                                                                                                                                               |

| 6       | Ground                         | GND              | Reference for all signals.                                                                                                                                                                                                                                                                             |

| 7       | Negative reset output          | RES              | Connect to the negative reset input of a microcomputer. The pin is capable of flowing 1 mA sink current.                                                                                                                                                                                               |

| 8       | Chip select output             | CS               | Connect to the chip select of RAM. The CS output is at low level in normal state thereby letting RAM be active. Under failure or backup condition, the CS output is set to high level, then RAM enters standby state disabling read/write function. The pin is capable of flowing a 1 mA sink current. |

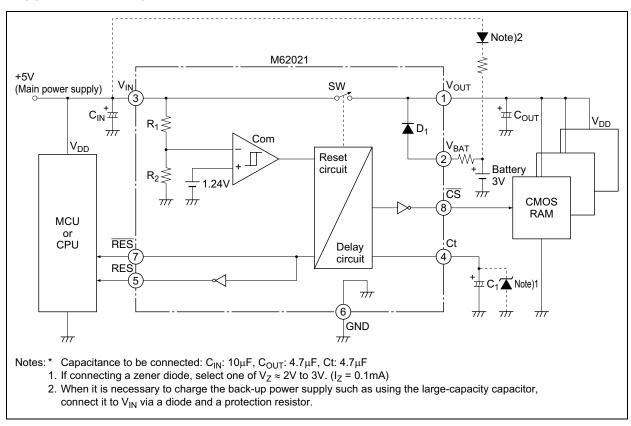

#### **Application Example**

Figure 2 Application Example

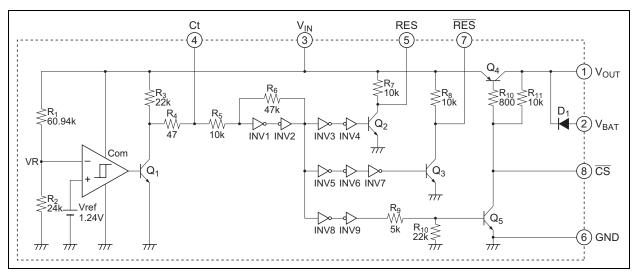

#### Configuration

#### **Power Supply Detection**

The internal reference voltage Vref is compare by means of a comparator with resistor-divided voltage  $V_R$  (resistor-divided voltage produced by  $R_1$  and  $R_2$  from  $V_{IN}$ ).

If the input voltage is 5 V,  $V_R$  is set to 1.24 V or higher, so the comparator output is at low level and the Ct output ( $Q_1$  collector output) is set to high level. If the input voltage drops to below 4.4 V in an abnormal condition,  $V_R$  becomes below 1.24 V, so the comparator output goes from low to high level and the Ct output, from high to low. The input voltage at this point is called  $V_{SL}$ . Next, when the input voltage, restored from abnormal state, has a rise, the comparator output goes from high to low level and the Ct output, from low to high.

The comparator used for detection has 100 mV hysteresis ( $\Delta V_S$ ), so that malfunctioning is prevented in case that the input voltage slowly drops or  $V_R$  nearly equals Vref.

Figure 3

#### **Delay Circuit**

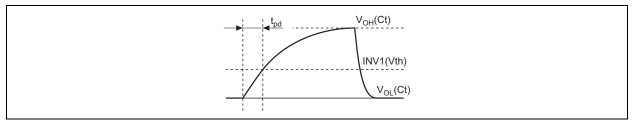

Connecting an external capacitor to the Ct pin lets RES,  $\overline{RES}$ ,  $\overline{CS}$ , and  $V_{OUT}$  be delayed due to RC transient phenomenon (electric charge).

Delay time is determined as follows.

Delay time (t<sub>pd</sub>) = C<sub>1</sub> × (R<sub>3</sub> + R<sub>4</sub>) × 1n

$$\frac{[V_{OH}(Ct) - V_{OL}(Ct)]}{[V_{OH}(Ct) - INV1(V_{TH})]}$$

= C<sub>1</sub> × 22k $\Omega$  × 0.2614

≈ 5.75 × 10<sup>3</sup> × C<sub>1</sub>

\* C is an external capacitance.

Taking into consideration the time taken by the oscillator of microcomputer to be stable, connect a 4.7  $\mu$ F capacitor to the Ct pin. (As the response time of detection can be slowed due to internal structure depending in the rising rate of power supply, avoid connecting a too large capacitance.)

Figure 4 Delayed Output Waveforms of Ct

#### **Schmitt Trigger Circuit**

Since waveforms show a gentle rise due to the RC delay circuit, INV1, INV2, R5, and R6 constitute a Schmitt trigger circuit to produce hysteresis so as to prevent each output from chattering.

### **Internal Circuit**

Figure 5 Internal Circuit

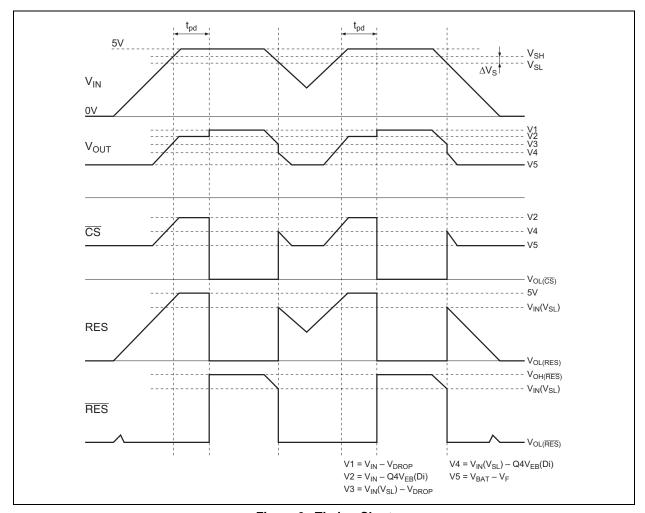

## **Timing Chart**

Figure 6 Timing Chart

| Input<br>Voltage | In Normal Operation                                                                 | In Failure (Instantaneous Drop)                                                                                                    | Restoration from Failure (Instantaneous Drop)                                                                                          | In Backup State                                                                      |

|------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Output<br>Pin    | Input voltage: 5V                                                                   | Input voltage: 5V—>4V Each output varies if the input voltage drops to V <sub>SL</sub> or under                                    | Input voltage: 4V→5V  If the input voltage goes higher than VSL by 100mV, each output varies after delay produced by the delay circuit | Input voltage: 0V<br>Backup voltage: 3V                                              |

| V <sub>OUT</sub> | With Q4 set to ON,<br>a voltage (V <sub>IN</sub> – V <sub>DROP</sub> )<br>is output | Q4 is turned OFF. A voltage $(V_{IN}-Q4V_{EB}(Di))$ is output by the diode between E and B of Q4.                                  | Q4 is turned ON after delay and a voltage ( $V_{\text{IN}} - V_{\text{DROP}}$ ) is output.                                             | $V_{BAT} - V_{F}$                                                                    |

| RES              | The output level is V <sub>OL</sub> (RES) with a logic low                          | As the state shifts from a logic low to logic high, the output level becomes approximately equal to the input voltage.             | A logic high is maintained, and than shifts to a logic high.                                                                           | _                                                                                    |

| RES              | The output level is V <sub>OH</sub> (RES) with a logic low                          | As the state shifts from a logic high to logic low, the output level becomes V <sub>OL</sub> (RES).                                | A logic low is held, and than shifts to a logic high.                                                                                  | _                                                                                    |

| <u>CS</u>        | The output level is V <sub>OL</sub> (CS) with a logic low                           | As the state shifts from a logic low to logic high, the output level becomes the voltage $V_{\text{IN}}$ – Q4V <sub>EB</sub> (Di). | A logic high is maintained, and than shifts to a logic high.                                                                           | The output is a logic high and the output level is V <sub>BAT</sub> – V <sub>F</sub> |

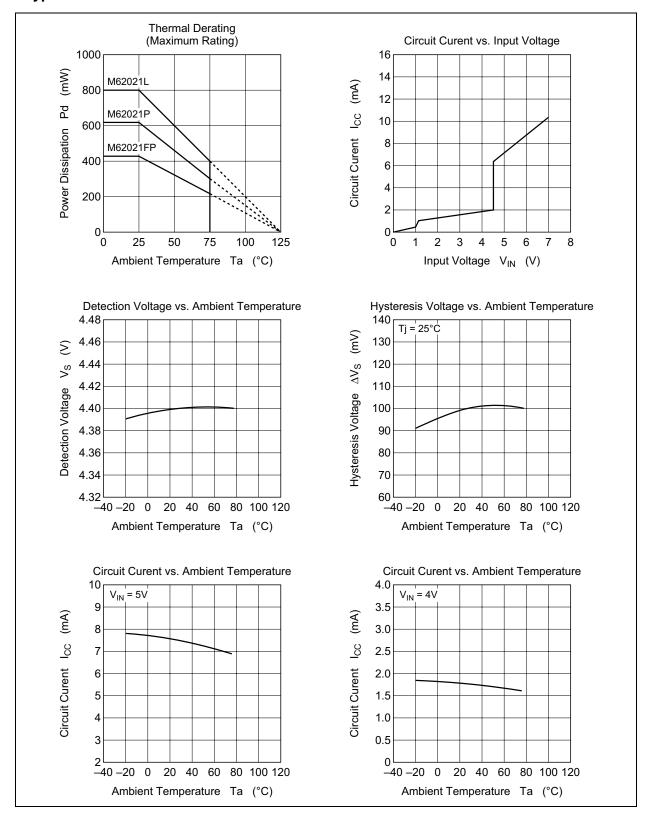

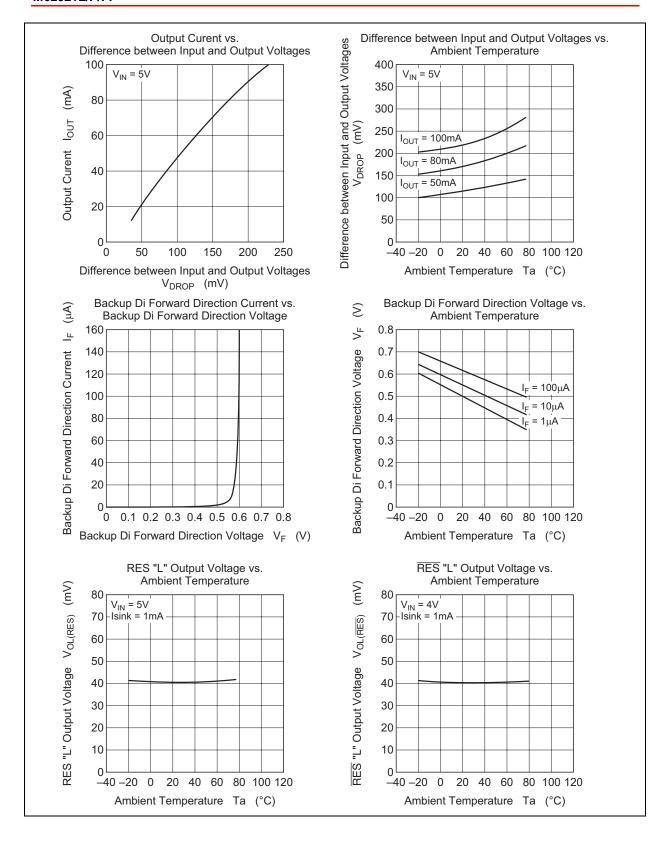

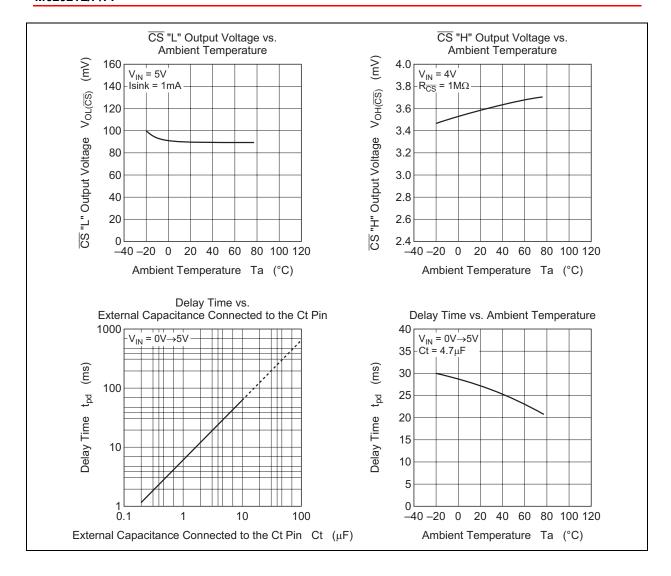

## **Typical Characteristics**

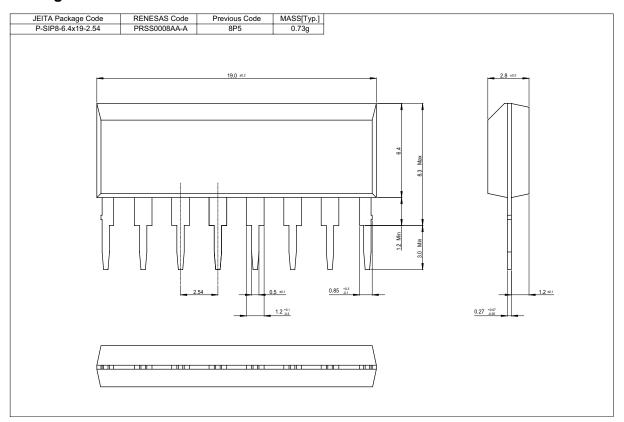

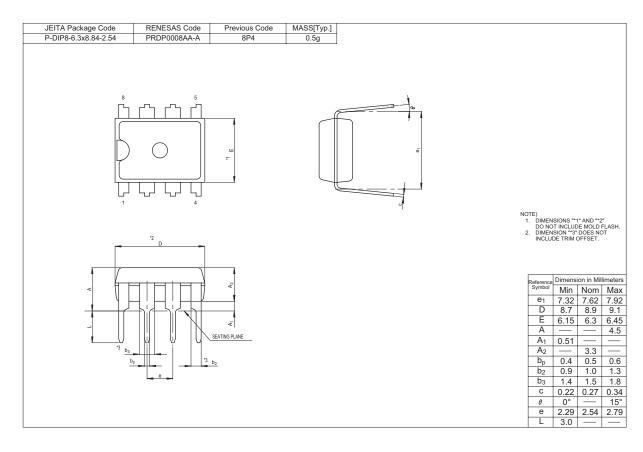

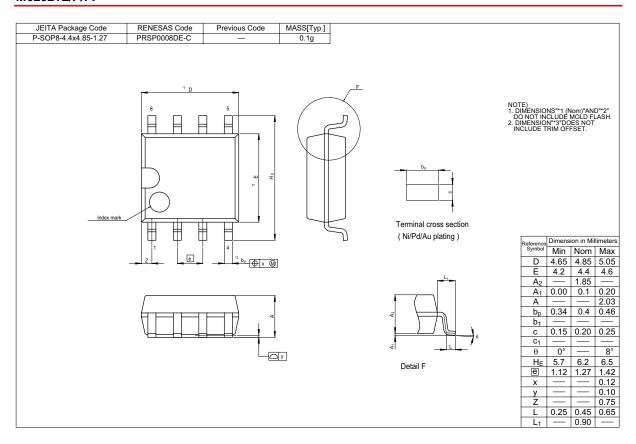

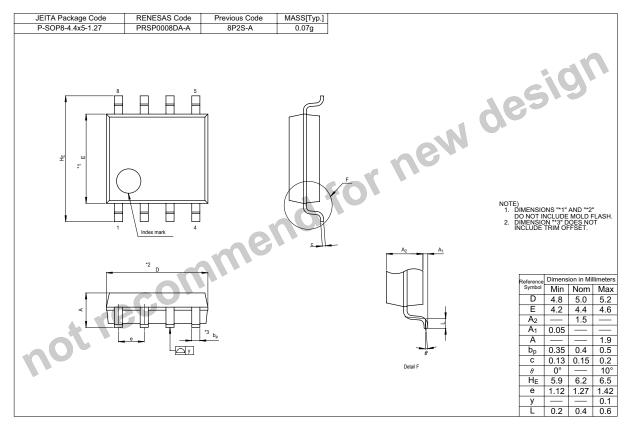

### **Package Dimensions**

#### Renesas Technology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

- Renesas Technology Corp. Sales Strategic Planning Div. Nippon Bidg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

Notes:

1. Whis document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas groducts for their use. Renesas neither makes may not be rights or any other rights of rany other rights of ranges or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, algorithms, and application circuit examples.

3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws destruction to for the purpose of any other military such as a product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information however, is subject to change without any prior notice. Before purchasign or using any Renease spructus isled in this document, pleases confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to develope the information in light of the total system before deciding about the applicable of years as such as a such a

#### **RENESAS SALES OFFICES**

http://www.renesas.com

Refer to "http://www.renesas.com/en/network" for the latest and detailed information

Renesas Technology America, Inc. 450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K.

Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd.

Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7898

Renesas Technology Hong Kong Ltd.

7th Floor, North Tower, World Finance Centre, Harbour City, 1 Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2730-6071

**Renesas Technology Taiwan Co., Ltd.** 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999

Renesas Technology Singapore Pte. Ltd. 1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd

Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jalan Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510