# Advance Information

# Color SXGA Digital Image Sensor 1280 x 1024 pixel progressive scan solid state image sensor with integrated CDS/PGA/ADC, digital programming, control, timing, and pixel correction features

#### Features:

- SXGA resolution, active CMOS image sensor with square pixel unit cells

- 6.0µm pitch pixels with patented pinned photodiode architecture

- Bayer-RGB color filter array with optional micro lenses

- High sensitivity, quantum efficiency, and charge conversion efficiency

- · Low fixed pattern noise / Wide dynamic range

- Antiblooming and continuous variable speed shutter

- Single master clock operation

- Digitally programmable via I<sup>2</sup>C interface

- Integrated on-chip timing/logic circuitry

- CDS sample and hold for suppression of low frequency and correlated reset noise

- 20X programmable variable gain to optimize dynamic range and facilitate white balance and iris adjustment

- 10-bit, pipelined algorithmic RSD ADC (DNL ±0.5 LSB, INL ±1.0 LSB)

- Automatic column offset correction for noise suppression

- Pixel addressability to support 'Window of Interest' windowing, resolution, and subsampling

- Encoded data stream

- 10 fps full SXGA at 13.5MHz Master Clock Rate

- Single 3.3V power supply

- 48 pin CLCC package

| MCM20027      |

|---------------|

| 1.3 Megapixel |

| Part Number  | Description                              | Package     |

|--------------|------------------------------------------|-------------|

| MCM20027IBBL | Color RGB sensor with Lenslets           | 48 Pin CLCC |

| MCM20027IBMN | Monochrome<br>sensor without<br>Lenslets | 48 Pin CLCC |

The MCM20027 is a fully integrated, high performance CMOS image sensor with features such as integrated timing, control, and analog signal processing for digital imaging applications. The part provides designers a complete imaging solution with a monolithic image capture and processing engine thus making it a true "camera on a chip". System benefits enable design of smaller, portable, low cost and low power systems. Thereby making the product suitable for a variety of consumer applications including still/full motion imaging, security/surveillance, and automotive among others.

The imaging pixels are based on active CMOS pixels using pinned photodiodes that are realized using Motorola's sub-micron ImageMOS<sup>TM</sup> technology. A maximum frame rate of 10 FPS at full resolution can be achieved, further the frame rate is completely adjustable without adjusting the system clock. Each pixel on the sensor is individually addressable allowing the user to control "Window of Interest" (WOI) panning and zooming. Control of sub-sampling, resolution, exposure, gain, and other image processing features is accomplished via a two pin I<sup>2</sup>C interface. The sensor is run by supplying a single Master Clock. The sensor output is 10 digital bits providing wide dynamic range images.

#### **ELECTRO STATIC DISCHARGE WARNING:**

This device is sensitive to electrostatic discharge (ESD).ESD immunity meets Human Body Model (HBM)  $\leq$  1500 V and Machine Model (MM)  $\leq$  150 V Additional ESD data upon request. When handling this part, proper ESD precautions should be followed to avoid exposing the device to discharges which may be detrimental to its immediate performance and/or reduce the parts expected lifetime..

out notice

This document contains information on a new product. Specifications and information herein are subject to change with-

© MOTOROLA, INC. 2001 Revision 8.0 - 28 November 2001 : MCM20027

# **Specifications**

Image Size: 7.7mm x 6.1mm (9.82mm Diagonal, 1/2" Optic)

Resolution:1280 x 1024 pixels, available digital zoom and region of interest (ROI) windowing

Pixel Size: 6μm x 6μm

Monochrome Sensitivity: 1.8 V/Lux-sec

Min. Detectable Light Level: 3 Lux at 10FPS/F2 lens

Scan Modes: Progressive

Shutter Modes: Continuous Frame and Single Frame Rolling Shutter modes available

Readout Rate: 13.5MSPS

Frame Rate: 0-10 Full frames (1280x1024) per second

Max Master Clock Frequency: 13.5MHz

System Dynamic Range: 50dB

On Chip programmable gain: -9.5dB to 26dB

On Chip Image Correction: Column Fixed Pattern Correction

Analog to Digital Converter: 10-bit, RSD ADC (DNL +/-0.5 LSB, INL +/-1.0 LSB)

Power Dissipation: 250mW RMS, operating @13.5Mhz

Package: 48 pin ceramic LCC

**Temperature Operating Range:** 0-40°C

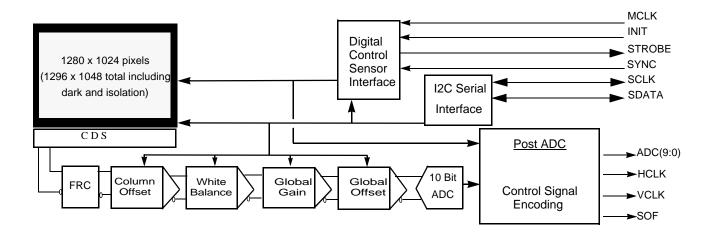

Figure 1. MCM20027 Simplified Block Diagram

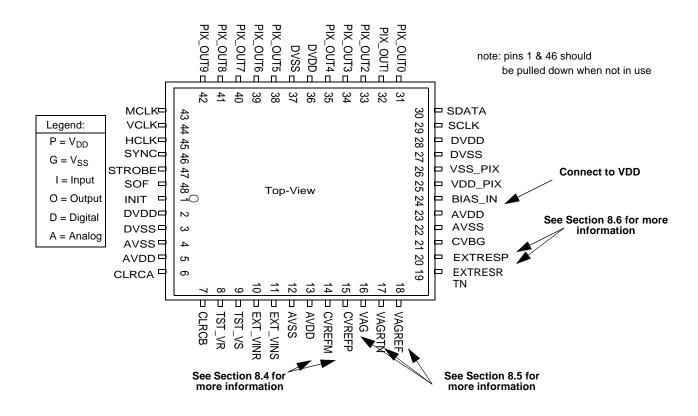

See "MCM20027 Pin Definitions" on page 67 for more information

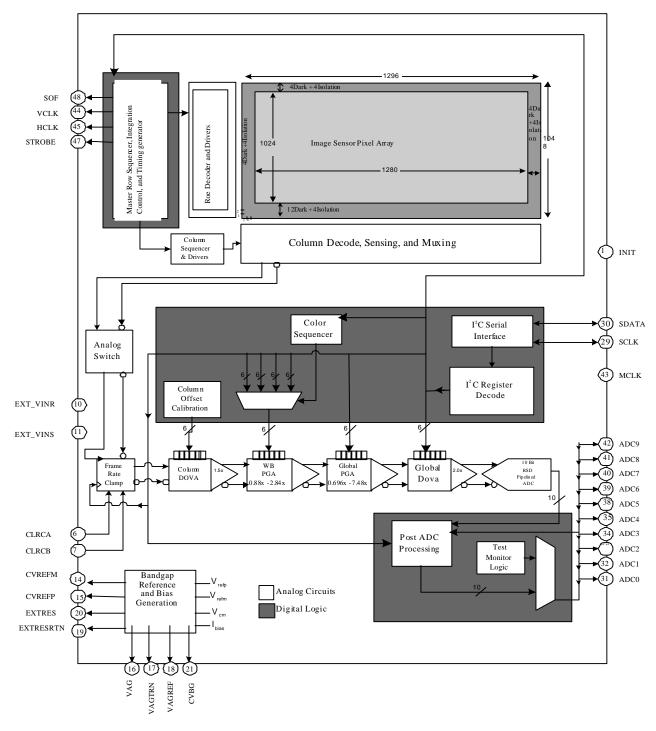

Figure 2. MCM20027 Detailed Block Diagram

# **MOTOROLA**

# SEMICONDUCTOR TECHNICAL DATA

# **Table Of Contents**

| 1.0 |     |       | MCM20027 Overview                                                                 | 7  |

|-----|-----|-------|-----------------------------------------------------------------------------------|----|

| 2.0 |     |       | MCM20027 Architecture                                                             | 7  |

|     | 2.1 |       | Pixel Architecture                                                                | 7  |

|     | 2.2 |       | Color Separation and Fill Factor Enhancement                                      | 9  |

| 3.0 |     |       | Frame Capture Modes                                                               | 10 |

|     | 3.1 |       | Continuous Frame Rolling Shutter capture mode (Default)                           | 10 |

|     | 3.2 |       | Single Frame Rolling Shutter capture mode (SFRS)                                  | 11 |

| 4.0 |     |       | Active Window of Interest Control                                                 | 12 |

| 5.0 |     |       | Active Window Sub-sampling Control                                                | 12 |

| 6.0 |     |       | Frame Rate and Integration Time Control                                           | 13 |

|     | 6.1 |       | CFRS Frame Time/Rate:                                                             | 13 |

|     | 6.2 |       | Integration Time in CFRS mode:                                                    | 13 |

|     | 6.3 |       | SFRS Frame Time/Rate:                                                             | 14 |

|     | 6.4 |       | Integration Time in SFRS mode                                                     | 14 |

|     | 6.5 |       | Example of Frame time/rate and Integration Time in CFRS and SFRS modes            |    |

| 7.0 |     |       | Analog Signal Processing Chain Overview                                           | 15 |

|     | 7.1 |       | Correlated Double Sampling (CDS)                                                  | 15 |

|     | 7.2 |       | Frame Rate Clamp (FRC)                                                            | 15 |

|     | 7.3 |       | Programmable Per-Column Offset                                                    | 16 |

|     | 7.4 |       | Digitally Programmable Gain Amplifiers (DPGA) for White Balance and Exposure Gain | 16 |

|     |     | 7.4.1 | White Balance Control PGA                                                         | 16 |

|     |     | 7.4.2 | Exposure Global Gain PGA                                                          | 16 |

|     |     | 7.4.3 | Gain Modes                                                                        | 17 |

|     | 7.5 |       | Global Digital Offset Voltage Adjust (DOVA)                                       | 19 |

|     | 7.6 |       | Analog to Digital Converter (ADC)                                                 | 19 |

| 8.0 |     |       | MCM20027 Sensor External Controls                                                 | 20 |

|     | 8.1 |       | Initialization                                                                    | 20 |

|     | 8.2 |       | Standby Mode                                                                      | 20 |

# **MOTOROLA**

# SEMICONDUCTOR TECHNICAL DATA

# **Table Of Contents**

|      | 8.3   | Tristate Mode                                      | 20 |

|------|-------|----------------------------------------------------|----|

|      | 8.4   | References CVREFP, CVREFM                          | 20 |

|      | 8.5   | Common Mode References: VAG, VAGREF and VAGRETURN. | 20 |

|      | 8.6   | Internal Bias Current Control                      | 21 |

| 9.0  |       | Sensor Output/Input Signals                        | 22 |

|      | 9.1   | Start Of Data Capture (SYNC)                       | 22 |

|      | 9.2   | Start Of Row Readout (SOF)                         | 22 |

|      | 9.3   | Horizontal Data SYNC (VCLK)                        | 22 |

|      | 9.4   | Data Valid (HCLK)                                  | 22 |

|      | 9.5   | Strobe Signal                                      | 24 |

| 10.0 |       | I <sup>2</sup> C Serial Interface                  | 26 |

|      | 10.1  | MCM20027 I <sup>2</sup> C Bus Protocol             | 26 |

|      | 10.2  | START Signal                                       | 26 |

|      | 10.3  | Slave Address Transmission                         | 26 |

|      | 10.4  | Acknowledgment                                     | 26 |

|      | 10.5  | Data Transfer                                      | 26 |

|      | 10.6  | Stop Signal                                        | 27 |

|      | 10.7  | Repeated START Signal                              | 27 |

|      | 10.8  | I <sup>2</sup> C Bus Clocking and Synchronization  | 27 |

|      | 10.9  | Register Write                                     | 28 |

|      | 10.10 | Register Read                                      | 28 |

| 11.0 |       | Suggested Software Register Changes                | 31 |

| 12.0 |       | MCM20027 Utility Programming Registers             | 32 |

|      | 12.1  | Register Reference Map                             | 32 |

| 13.0 |       | Detailed Register Block Assignments                | 35 |

| 14.0 |       | Electrical Characteristics                         | 64 |

| 15.0 |       | MCM20027 Pin Definitions                           | 67 |

| 16.0 |       | MCM20027 Packaging Information                     | 69 |

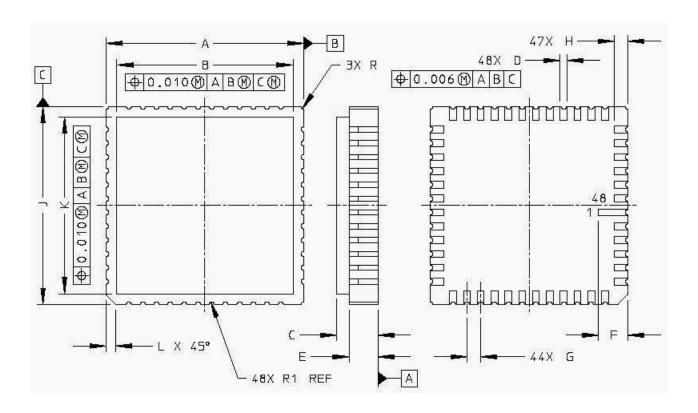

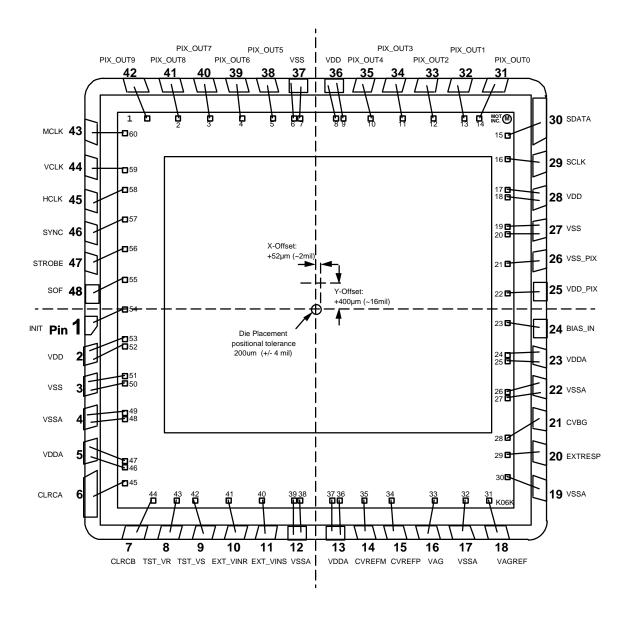

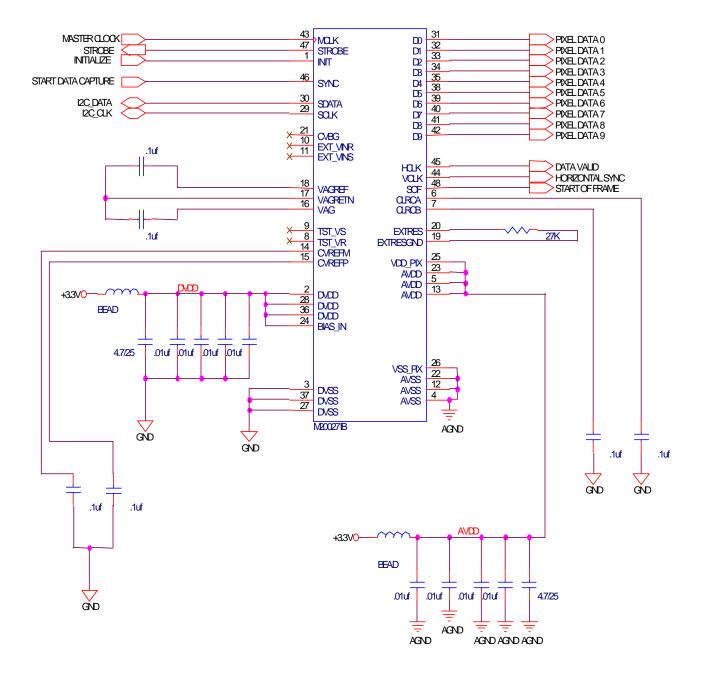

| 17.0 |       | MCM20027 Typical electrical connection             | 72 |

# **Reference Documentation**

| No | Description                                            | Name of Document                  | Release<br>Date | Contact/Location of Info            |

|----|--------------------------------------------------------|-----------------------------------|-----------------|-------------------------------------|

| 1  | Digital Camera Reference Design utilizing the MCM20027 | Roadrunner<br>Application Note    | May 4 2001      | http://www.motorola.com/adc/imaging |

| 2  | Information on MCM20027<br>Optics                      | Optic Application note            | Feb 7 2001      | http://www.motorola.com/adc/imaging |

| 3  | Information on Strobe Timing                           | Strobe Timing<br>Application Note | May 30 2001     | http://www.motorola.com/adc/imaging |

|    |                                                        |                                   | _               |                                     |

**Table 1. Reference Documentation**

#### 1.0 MCM20027 Overview

The MCM20027 is a solid state CMOS Active CMOS Imager (ACI<sup>TM</sup>) that integrates the functionality of a complete analog image acquisition, digitizer, and digital signal processing system on a single chip. The image sensor comprises a format pixel array with 1280x1024 active elements. The image size is fully programmable to user defined windows of interest. The pixels are on a 6.0µm pitch. High sensitivity and low noise are a characteristic of the pinned "shared diffusion" photodiode architecture utilized in the pixels. Standard microlenses further enhance the sensitivity. The sensor is available with Bayer patterned Color Filter Arrays (CFAs) for color output or as a monochrome imager.

Integrated timing and programming controls allow video or still image capture modes. Frame rates are programmable while keeping Master Clock frequency constant. User programmable row and column start/stop allow windowing to a minimum 1x1 pixel window (see "Active Window of Interest Control" on page 12). Windowing can also be performed by subsampling in multiple pixel increments to allow digital zoom (see "Active Window Sub-sampling Control" on page 12).

The analog video output of the pixel array is processed by an on chip analog signal processing pipeline. Correlated Double Sampling (see "Correlated Double Sampling (CDS)" on page 15) eliminates the sensor reset noise without the need to capture and subtract a reset frame per live video frame. The Frame Rate Clamp (FRC) enables real time optical black level calibration and offset correction (see "Frame Rate Clamp (FRC)" on page 15). The programmable analog gain consists of exposure or global gain to map the signal swing to the ADC input range, and white balance gain to perform color white balance in the analog domain. The ASP signal chain consists of :

- (1) Column op-amp(1.5X fixed gain)

- (2) Column DOVA (1.5X fixed gain)

- (3) White Balance PGA (0.88-2.82X)

- (4) Global PGA (0.67X 5.92X)

- (5) Global DOVA (2.0X fixed gain)

These Digitally Programmable Amplifiers (DPGAs) allow real time color gain correction for Auto White Balance (see "White Balance Control PGA" on page 16) as well as global gain adjustment (see "Exposure Global Gain PGA" on page 16); offset calibration (see "Pro-

grammable Per-Column Offset" on page 16 and "Global Digital Offset Voltage Adjust (DOVA)" on page 19) can be done on a per column basis and globally. This percolumn offset correction can be applied by using stored values in the on chip registers. A 10-bit Redundant Signed Digit (RSD) ADC converts the analog data to a 10-bit digital word stream. The fully differential analog signal processing pipeline serves to improve noise immunity, signal to noise ratio, and system dynamic range.

The sensor uses an industry standard two line I<sup>2</sup>C complaint serial interface. (see page 26). The MCM20027 operates with a single 3.3V power supply (see "Electrical Characteristics" on page 53) with no additional biases and requires only a single Master Clock for operation upto 13.5MHz. It is housed in a 48 pin ceramic LCC package (see "MCM20027 Packaging Information" on page 69).

The MCM20027 is designed taking into consideration interfacing requirements to standard video encoders. In addition to the 10 bit bayer encoded data stream, the sensor outputs the valid frame, line and pixel sync signals needed for encoding. The sensor interfaces with a variety of commercially available video image processors to allow encoding into various standard video formats.

The MCM20027 is an elegant and extremely flexible single chip solution that simplifies a system designer's tasks of image sensing, processing, digital conversion, and digital signal processing to a high performance, low cost, low power IC. One that supports among others a wide range of low power, portable consumer digital imaging applications.

#### 2.0 MCM20027 Architecture

#### 2.1 Pixel Architecture

The MCM20027 ImageMOS<sup>TM</sup> (1) sensor comprises of a 1280 x 1024 active pixel array and supports progressive scan mode.

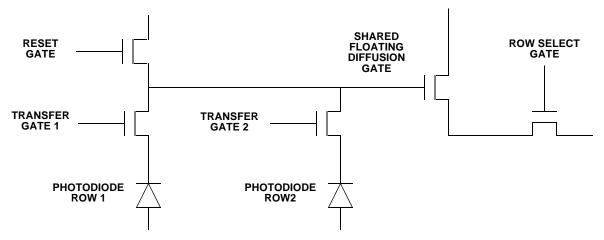

The MCM20027 utilizes the Kodak patented "Shared Floating Diffusion" pixel design <sup>3</sup>. This design enables two adjacent Row pixels' photodiodes to share the same floating diffusion transistor. (see Figure 2, on page 8).

- 1. ImageMOS is a Motorola trademark

- 2. Patents held jointly by Motorola and Kodak

- 3. Kodak Patent pending

The basic operation of the pixel relies on the photoelectric effect where due to its physical properties silicon is able to detect photons of light. The photons generate electron-hole pairs in direct proportion to the intensity and wavelength of the incident illumination. The application of an appropriate bias allows the user to collect the electrons and meter the charge in the form of a useful parameter such as voltage.

The pixel architecture also requires all pixels in a row to have common Reset, Transfer 1 and 2, Floating diffu-

sion and Row Select gate controls. In addition all pixels have common supply  $(V_{DD})$  and ground  $(V_{SS})$  connections. An optimized cell architecture provides enhancements such as noise reduction, fill factor maximizations, and antiblooming. The use of pinned photodiodes (2) and proprietary transfer gate devices in the photoelements enables enhanced sensitivity in the entire visual spectral range and a lag free operation.

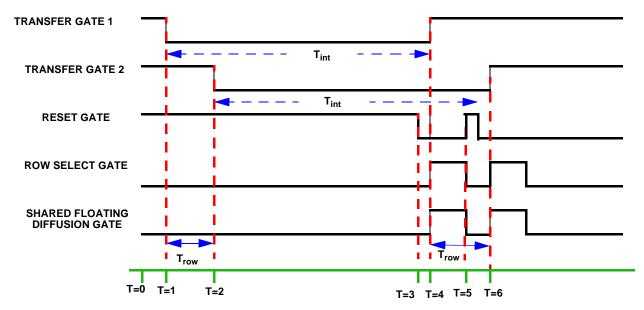

Figure 2. Shared Floating Diffusion Pixel Architecture

### How it works?

In brief, initially during Integration @T=0, both Transfer Gates 1 and 2 and the Reset Gate is Open (On-Active High). Transfer Gate 1 then Closes (Off) @ T=1, thereby allowing Photodiode 1 to charge its well capacitance.

At this time Photodiode 2 is held at Reset level by having Transfer Gate 2 and the Reset Gate open (On). After 1 Row Period [T<sub>row</sub>], @T=2 ,Transfer Gate 2 closes (Off). This action causes Photodiode 2 to start charging. When the integration (charging) of Photdiode 1 has

# SEMICONDUCTOR TECHNICAL DATA

neared completion, @ T=3, the Reset Gate closes (Off). The charge off the well capacitance of Photodiode 1 is then transfered to the Shared Floating Diffusion Gate @ T=4 when Transfer Gate 1 opens (On). Also @ T=4 the Shared Diffusion gate and the Row Select gate opens (On). This action causes charge from the floating diffusion to be read out as a Voltage value for that pixel on Row 1. @T=5 the Row Select gate and the Floating diffusion close (Off) while the Reset gate opens (On). This is occurs in preparation of readout of Row 2.

When the integration (charging) of Photodiode 2 has neared completion, the Reset Gate closes (Off) again. The charge off the Well Capacitance of Photodiode 2 is then transfered to the Shared Floating Diffusion Gate @ T=6 when Transfer Gate 2 opens (On) and then the same readout procedure as before occurs.

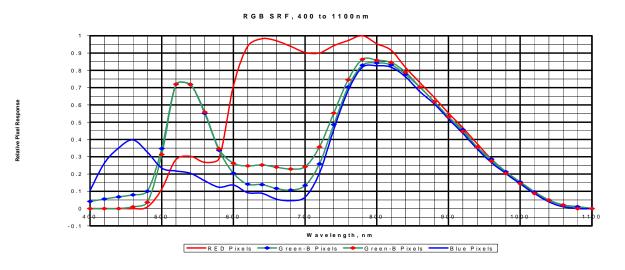

The nominal photoresponse of the MCM20027 is shown in Figure 3

Figure 3. MCM20027 Nominal spectral response

In addition to the imaging pixels, there are additional pixels called dark and dummy pixels at the periphery of the imaging section (see Figure 2). The dark pixels are covered by a light blocking shield rendering the pixels underneath insensitive to photons. These pixels provide the sensor means to measure the dark level offset which is used downstream in the signal processing chain to perform auto black level calibration. The dummy pixels are provided at the array's periphery to eliminate inexact measurements due to light piping into the dark pixels adjacent to active pixels. The output of these pixels should be discarded.

Electronic shuttering, also known as electronic exposure timing in photographic terms, is a standard feature. The pixel integration time can be widely varied from a small fraction of a given frame readout time to the entire frame time.

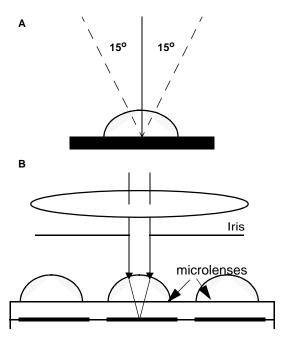

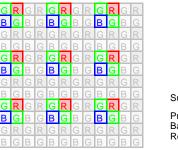

**2.2 Color Separation and Fill Factor Enhancement** The MCM20027 family is offered with the option of monolithic polymer color filter arrays (CFAs). The combination of an extremely planarized process and propri-

atary color filter technology result in CFAs with superior spectral and transmission properties. The standard option is a primary (RGB) "Bayer" pattern (see Figure 4), however, facility to produce customized CFAs including complementary (CMYG) mosaics also exists.

Applications requiring higher sensitivity can benefit from the optional micro-lens arrays shown in Figure 5. The lenslet arrays can improve the fill factor (aperture ratio) of the sensor by 1.5-2x depending on the F number of the main lens used in the camera system. Microlenses yield greatest benefits when the main lens has a high F number. As a caution, telecentric optical design is a requirement due to the limited optical acceptance angle of the lenslit. The optical acceptance angle is approximately 15 degrees (see figure 5a). Due to the lenslits being placed in the same area/position over all the photodiodes on the sensor, hence, care should be taken when taking into consideration the telecentric design for especially the outermost pixels. The fill factor of the pixels without microlenses is 32%. With Microlens the fill factor improves to approximately 45% to 50%.

Revision 8.0 - 28 November 2001 : MCM20027 MOTOROLA

| G1 | R  | G1 | R  |

|----|----|----|----|

| В  | G2 | В  | G2 |

| G1 | R  | G1 | R  |

| В  | G2 | В  | G2 |

Figure 4. On-chip Bayer CFA

Figure 5. a) 15 degrees acceptance angle b)Improvement in pixel sensitivity results from focusing incident light on photo sensitive portions of the pixel by using microlenses

# 3.0 Frame Capture Modes

There exists two frame capture modes:

- 1) Continuous Frame Rolling Shutter mode (CFRS)

- 2) Single Frame Rolling Shutter mode (SFRS)

The sensor can be put into either one of the aforementioned modes by writing either "1" or "0" to Bit 6 of Capture Mode Control Register, (Table 29), on page 48.

# 3.1 Continuous Frame Rolling Shutter capture (CFRS) [Default]

The default mode of image capture is the "Continuous Frame Rolling Shutter" capture mode (CFRS). This mode will yield frame rates up to 10fps at 13.5 MHz MCLK. In this mode the image integration and row readout take place in parallel. While a row of pixels is being read out, another row(s) are being integrated. Readout of each row follows the Integration of that row. Therefore the Integration of the rows are staggered out due to the Readout of sequential rows occurring one after the other (see "Integration Time in CFRS mode:" on page 13).

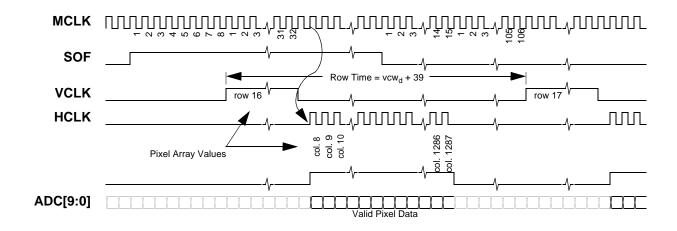

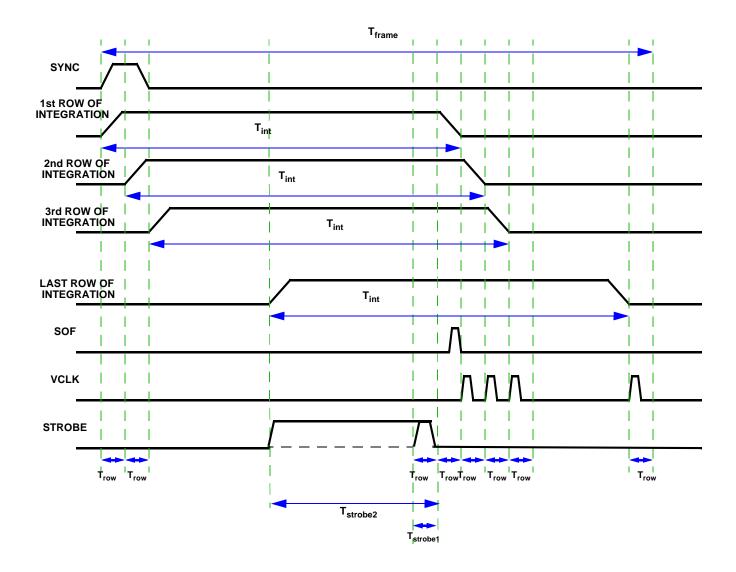

In CFRS, after one frame has completed integrating, the first row of the second frame automatically begins integrating. The readout of the rows also follow the same routine. The waveforms depicting the CFRS output data stream refer to Figure 6, on page 11 and Figure 7, on page 12.

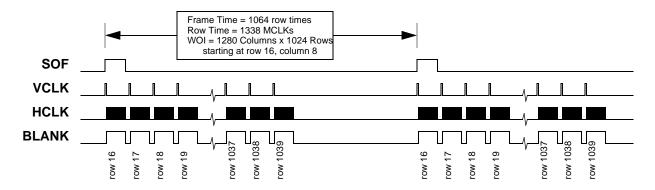

#### 3.1.1 CFRS Video Encoded Data stream

The Pixel Data Stream Signal Control Register, (Table 53), on page 62 allows the user to select how the output pixel data stream in Continuous Frame Rolling Shutter mode is encoded/formatted. In default mode, internally generated signals SOF, VCLK, HCLK etc. drive the integration and readout of the pixel data frames but only the valid pixel data is readout of the sensor. When a "1" is written to bit 5 of the Pixel Data Stream Signal Control Register, (Table 53), on page 62, it causes the output pixel data to be encoded with SOF, VCLK and End Of Frame signals. It accomplishes this by attaching the pixel data with certain predefined signal data. The Video Encoded Signal Definitions, (Table 2), on page 10 defines the data that represents the SOF, VCLK and End of Frame signals.

| Signal          | Description                                         | Data         |

|-----------------|-----------------------------------------------------|--------------|

| SOF             | Start of Row read-<br>out (i.e Readout of<br>Row 1) | 3FF3FF3FF    |

| VCLK            | Start of Row read-<br>out of Rows 2+                | 3FF3FF000000 |

| End Of<br>Frame | Readout of last Row complete                        | 00000000000  |

**Table 2. Video Encoded Signal Definitions**

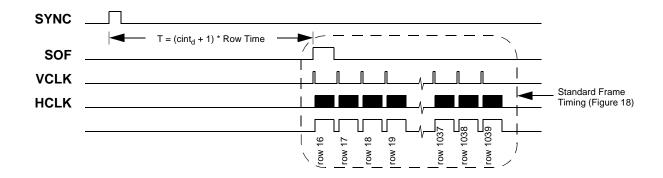

# 3.2 Single Frame Rolling Shutter capture mode (SFRS)

This mode of capture refers to non-interlaced or sequential row by row scanning of the entire sensor in a single pass for the purpose of capturing a single frame. The start of Integration in this mode is triggered by the SYNC signal. Similar to the CFRS capture mode, Readout of each row follows the Integration of that row.

Therefore the Integration of the rows are staggered out as well due to the Readout of the sequential rows occurring one after the other (see "Integration Time in SFRS"

mode" on page 14). This process continues until all Rows have been integrated and readout. Once readout of the entire frame is complete, the sensor awaits a new SYNC signal before it starts integration and readout of another frame.

The waveforms depicting the SFRS output data stream refer to Figure 8, on page 12

NOTE!! The faster the clock speed, the closer the sequential Integration start times are.

Figure 6. CFRS Default Frame Waveform

Figure 7. CFRS Default Line Waveform

Figure 8. SFRS Waveform

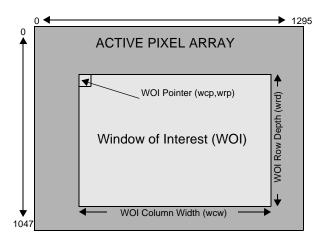

#### 4.0 Active Window of Interest Control

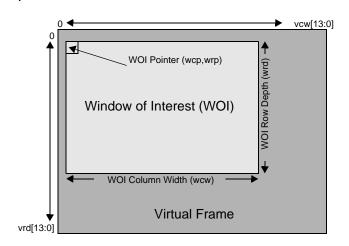

The pixel data to be read out of the device is defined as a 'Window of Interest' (WOI). The window of interest can be defined anywhere on the pixel array at any size. The user provides the upper-left pixel location and the size in both row and column depth to define the WOI. The WOI is defined using the WOI Pointer, WOI Depth, and WOI Width registers, (Table 32 on page 51 through Table 39 on page 53). Please refer to Figure 9 for a pictorial representation of the WOI within the active pixel array.

Figure 9. WOI Definition

## 5.0 Active Window Sub-sampling Control

The user can further control the size of the Active Window that is read out by sub sampling the already defined Active Window Of Interest (See "Active Window of Interest Control" on page 12). Subsampling enables the pixel data to be readout in 1 pixel or 2 pixel increments depending if you are subsampling in either monochrome (1 pixel) or bayer pixel (2 pixel) space in four different sampling rates in each direction: full, 1/2, 1/4, or 1/8. The user controls the subsampling via the Subsample Control Register, (Table 30), on page 49.

An example of Bayer space sub-sampling is shown in Figure 10.

Sub-sample Control Register = x0010101<sub>b</sub> = Progressive Scan

Bayer Pattern

Read 1 Pattern, Skip 1 Pattern

in both directions

Figure 10. Bayer Space Sub-sampling Example

#### 6.0 Frame Rate and Integration Time Control

In addition to the minimum time required to readout the selected resolution and WOI, the user has the ability to control the frame rates while operating in either Continuous Frame Rolling Shutter capture mode (CFRS) and Single Frame Rolling Shutter (SFRS).

The **frame rate** can be defined as the time required to readout an entire frame of data plus the required boundary timing. This is done by varying the size of a number of parameters identified in later sections, the main one being the Virtual Frame surrounding the WOI.

Please refer to Figure 11 for a pictorial description of the Virtual Frame and its relationship to the WOI

Figure 11. Virtual Frame Definition

#### 6.1 CFRS Frame Time/Rate:

In Continuous Frame Rolling Shutter capture mode, the Frame time is completely defined by the size of the Virtual Frame and can be expressed as:

Frame Time =

$$T_{frame}$$

=  $(vrd_d + 1) * T_{row}$

where  $\mathbf{vrd_d}$  defines the number of rows in the virtual frame. The user controls  $\mathbf{vrd_d}$  via the Virtual Frame Row Depth registers (Table 42 on page 55 and Table 43 on page 55).

Frame Rate = (Frame time)<sup>-1</sup>

#### 6.2 Integration Time in CFRS mode:

In Continuous Frame Rolling Shutter capture mode, the Integration time is defined as:

Integration Time=

$$T_{int} = (cint_d + 1) * T_{row}$$

where  $\mathbf{cint_d}$  is the number of virtual row times desired for integration time. Therefore, the integration time in CFRS mode can be adjusted in steps of virtual frame row times. The user controls  $\mathbf{cint_d}$  via the Integration Time MSB Register, (Table 40), on page 54 and Integration Time LSB Register, (Table 41), on page 55.

Row Time (T<sub>row</sub>) is the length of time required to read one row of the virtual frame and can be defined as:

$$T_{row} = (vcw_d + shs_d + shr_d + 19) * MCLK_{period}$$

where  $\mathbf{vcw_d}$  defines the number of columns in the virtual frame and  $\mathbf{shs_d}$  and  $\mathbf{shr_d}$  are internal timing control registers.

The user controls **vcw**<sub>d</sub> via the CFRS Virtual Frame Column Width registers (Table 44 on page 56 and Table 45 on page 56).

The user controls the  $\mathbf{shs_d}$  and  $\mathbf{shr_d}$  values via the Internal Timing Control Register 1 (shs time definition); Table 50 and Table 51, "Internal Timing Control Register 2 (shr time definition)," on page 60.

NOTE!! In Continuous Frame Rolling Shutter (CFRS) capture mode, the Integration time upper limit is bounded by the Frame time (see "CFRS Frame Time/Rate:" on page 13).

i.e..

$$T_{int} < T_{frame}$$

Revision 8.0 - 28 November 2001 : MCM20027

# SEMICONDUCTOR TECHNICAL DATA

#### 6.3 SFRS Frame Time/Rate:

In Single Frame Rolling Shutter capture mode the Frame time is defined as:

# Frame time = T<sub>frame</sub>= Integration time+Readout time

Readout time is the amount of time to readout the data after integration of the row has been completed. It is defined as follows:

Readout time =

$$(vrd_d + 1) * T_{row}$$

where  $\mathbf{vrd_d}$  defines the number of rows in the virtual frame. The user controls  $\mathbf{vrd_d}$  via the CFRS Virtual Frame Row Depth registers (Table 42 on page 55 and Table 43 on page 55).

$$T_{row} = (vcw_d + shs_d + shr_d + 19) * MCLK_{period}$$

For **Integration time** see "Integration Time in SFRS mode" on page 14

# 6.3.1 Integration Time in SFRS mode

The Integration time in Single Frame Rolling Shutter capture mode is the same as in Rolling Shutter Capture Mode. For further information, see "Integration Time in CFRS mode:" on page 13. The only difference is that in this mode the Integration time is NOT bounded by the Frame time

# 6.4 Example of Frame time/rate and Integration Time in CFRS and SFRS modes

The following illustrates how to determine the Frame time/rate and Integration time in both capture modes:

## **Assumptions:**

1) Active Window of Interest = 1280 x 1024

i.e..

$$(wcw_d)$$

=1279  $(wrd_d)$ =1023

- 2) Virtual Column Width (vcw<sub>d</sub>)= 1290

- 3) Virtual Row Depth ( $vrd_d$ ) = 1034

- 4) Sample & hold time (shs<sub>d</sub>) = 10

5) Sample & hold time (shr<sub>d</sub>) = 10

- 6) Integration Time (cint<sub>d</sub>)= 350

- 7) MCLK = 13.5 Mhz

NOTE!! vcw<sub>d</sub> and cint<sub>d</sub> are typically varied frame to frame

# **Calculations:**

Row Time =Trow =

$$(vcwd + shsd + shrd + 19)$$

$$= (1290 + 10 + 10 + 19) / 13.5e6$$

$$= 98.44 \mu s$$

$$=(350+1)*98.44 \mu s$$

$$=34.5 ms$$

$$T_{frame} = (1034 + 1)^* 98.44$$

$$= 101.34 \text{ ms}$$

Frame Time in SFRS mode =

$$= 34.5 ms + 101.34 ms$$

$$= 135.84 ms$$

#### **Results**

| Capture Mode | T <sub>int</sub> | T <sub>frame</sub> |

|--------------|------------------|--------------------|

| CFRS         | 34.5ms           | 101.34 ms          |

| SFRS         | 34.5ms           | 135.84ms           |

NOTE!! CFRS Integration time = 34.5ms because:

$$T_{int} < T_{frame} = (vrd_d + 1) * T_{row}$$

(see "Integration Time in CFRS mode:" on page 13)

### 7.0 Analog Signal Processing Chain Overview

The MCM20027's analog signal processing (ASP) chain incorporates Correlated Double Sampling (CDS), Frame Rate Clamp (FRC), two Digitally Programmable Gain Amplifiers (DPGA), Offset Correction (DOVA), and a 10-bit Analog to Digital Converter (ADC).

To see a pictorial depiction of this chain refer to "Specifications" on page 2

# 7.1 Correlated Double Sampling (CDS)

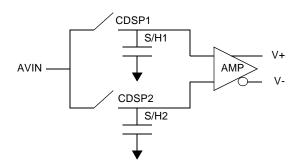

The uncertainty associated with the reset action of a capacitive node results in a reset noise which is equal to kTC; C being the capacitance of the node, T the temperature and k the Boltzmann constant. A common way of eliminating this noise source in all image sensors is to use Correlated Double Sampling. The output signal is sampled twice, once for its reset (reference) level and once for the actual video signal. These values are sampled and held while a difference amplifier subtracts the reference level from the signal output. Double sampling of the signal eliminates correlated noise sources (see ."Conceptual block diagram of CDS implementation." on page 15)

Figure 12. Conceptual block diagram of CDS implementation.

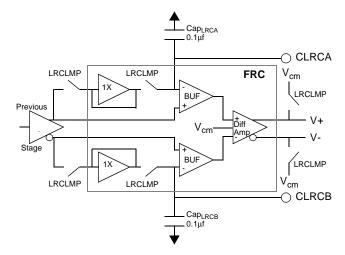

### 7.2 Frame Rate Clamp (FRC)

The FRC (Figure 13) is designed to provide a feed forward dark level subtract reference level measurement. In the automatic FRC mode, the optical black level reference is re-established each time the image sensor

begins a new frame. The MCM20027 uses optical black (dark) pixels to aid in establishing this reference.

Figure 13. FRC Conceptual Block Diagram

On the MCM20027, dark pixel input signals should be sampled for a minimum of 137µs to allow the two 0.1µF capacitors at the CLRCA and CLRCB pins sufficient time to charge for 10-bit accuracy. This guarantees that the FRC's "droop" will be maintained at <750 μV, thus assuring the specified ADC 10-bit accuracy at +0.5 LSB. Therefore, at maximum operational frequency (13.5 MHz), the imager would require a number of frames to establish the dark pixel reference for subsequent active pixel processing. The dark pixel sample period is automatically controlled internally and it is set to skip the first 3 dark rows and then sample the next 2 dark rows. When "dark clamping" is active, each dark pixel is processed and held to establish pixel reference level at the CLRCA and CLRCB pins. During this period, the FRC's differential outputs (V+ and V- on the Diff Amp, Figure 13) are clamped to V<sub>cm</sub>. Together, these actions help to eliminate the dark level offset, simultaneously establishing the desired zero code at the ADC output.

Care should be exercised in choosing the capacitors for the CLRCA, B pins to reflect different frame rates.

The user can disable this function via the FRC Definition Register; Table 54 and the Power Configuration Register, (Table 19), on page 41 (Check this - should be referring o FRC clamp ON/OFF) which will allow the ASP

chain to drift in offset Per-Column Digital Offset Voltage Adjust (DOVA), and controls the number of rows to clamp on.

Revision 8.0 - 28 November 2001: MCM20027 MOTOROLA

#### 7.3 Programmable Per-Column Offset

A programmable per-column offset adjustment is available on the MCM20027. In order to reduce the risk and have the ability to cover any mode of repetitive column Fixed Pattern Noise (FPN), there exists 64 registers that can be programmed with a DC offset that is added to all columns. (Mod64 Column Offset registers; Table 27). Each register is 6 bits, (5 bits plus 1 sign bit), providing+/-32 register values. The DC register values is added to each of the 64 columns registers to provide the total offset value. This set of 64 values is then repeatedly applied to each bank of 64 in the sensor via the column DOVA stage of the ASP chain.

The Column DOVA DC Register; Table 26, is used to set the initial offset of the pixel output in a range that will facilitate per-column offset data generation for varying operational conditions. In most operational scenarios, this register can be left in its default state of 00<sub>h</sub>. This is a pre-image processing gain in comparison to the Global DOVA Register (see section )which is a post image processing chain gain (pre A2D gain)

# 7.4 Digitally Programmable Gain Amplifiers (DPGA) for White Balance and Exposure Gain

Two DPGAs are available in the analog signal processing chain. These are used to perform white balance and exposure gain functions.

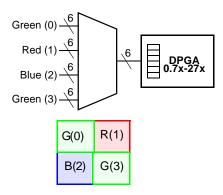

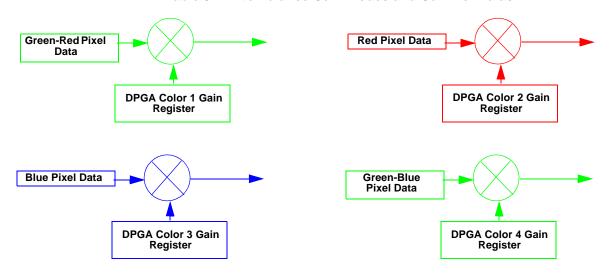

### 7.4.1 White Balance Control PGA

The sensor produces three primary color outputs, Red, Green and Blue. These are monochrome signals that represent luminance values in each of the primary colors. When added in equal amounts they mix to make neutral color. White balancing is a technique where the gain coefficients of the green(0), red, blue, and green(3) pixels comprising the Bayer pattern (see Figure 14.) are set so as to equalize their outputs for neutral color scenes. Since the sensitivity of the two green pixels in the Bayer pattern may not be equal, an individual color gain register is provided for each component of the Bayer pattern.

Once all color gain registers are loaded with the desired gain coefficients, according to which gain mode (see "Gain Modes" on page 17) has been set, white balance is then achieved in real time and in analog space. These gain coefficient values are then selected and applied to the pixel output via a high speed path, the delay of which is much shorter than the pixel clock rate. Real time updates can be performed to any of the gain registers. However, latency associated with the I<sup>2</sup>C interface should be taken into consideration before changes occur. In most applications, users will be able to assign predefined settings such as daylight, fluorescent, tung-

sten, and halogen to cover a wide gamut of illumination conditions.

Both DPGA designs use switched capacitors to minimize accumulated offset and improve measurement accuracy and dynamic range. The white balance gain registers are 6-bits and can be programmed to allow gain of 0.696x to 2.74x in varying steps.

The user programs the individual gain coefficients into the MCM20027 via the Color Gain Registers (Table 8 through Table 11). For the default Bayer configuration of the color filter array; Figure 4, the Color Gain Register addresses are as follows: Reg (00h): green pixel of a green-red row; Reg (01h): red pixel; Reg (02h): blue pixel; and Reg (03h): green pixel of a blue-green row.

The MCM20027 is presently available with only a Bayer CFA, however, it is designed to support other novel color configurations. This is accomplished via the Color Tile Configuration Register, (Table 12), on page 37 and the Color Tile Row Definition registers (Table 13 through Table 16).

Figure 14. Color Gain Register Selection

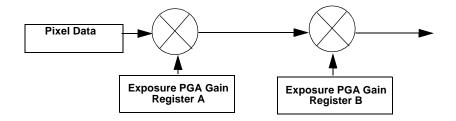

#### 7.4.2 Exposure Global Gain PGA

The global gain DPGA provides a 0.67x to 7.5x (approx) programmable gain adjustment for dynamic range. The gain of the amplifier is linearly programmable using a six bit gain coefficients on 2 6-bit PGA gain registers in varying steps depending on which exposure gain mode it is set at i.e. RAW or LIN or LIN2 (PGA Gain Mode, (Table 25), on page 45). The user programs the global gain via the Exposure PGA Global Gain Register A, (Table 23), on page 44.

#### 7.4.3 Gain Modes

There exists different gain modes that are available when the sensor is performing White Balance and Exposure gain. The Gain mode utilized for White balance and Exposure gain can be selected by the user writing different values to the register described in Table 25, "PGA Gain Mode," on page 45.

There are two different Gain modes for White Balance and there are three different Gain modes for the Exposure gain refer to White Balance Gain modes and Gain Formulas; Table 3 and Exposure Gain modes and Gain Formulas; Table 4 for more info.

| Register<br>No | Register Name                           | Variable           | Gain<br>Modes | Gain<br>Steps | Gain Formula                           | Gain<br>Range                          |           |

|----------------|-----------------------------------------|--------------------|---------------|---------------|----------------------------------------|----------------------------------------|-----------|

| 00h            | DPGA Color 1 Gain                       | cg1                | RAW           | 0-32          | 0.6956 + (0.02174* cg1 <sub>d</sub> )  | 0.69-1.39                              |           |

|                | Register; Table 8                       |                    |               | 33-63         | 1.391+ (0.0434* (cg1 <sub>d</sub> -32) | 1.39-2.74                              |           |

|                |                                         |                    | LINEAR        | 0-47          | 0.6956 +(0.0434 x cg1 <sub>d</sub> )   | 0.69-2.74                              |           |

| 01h            | DPGA Color 2 Gain                       | cg2                | RAW           | 0-32          | 0.6956 + (0.02174* cg2 <sub>d</sub> )  | 0.69-1.39                              |           |

|                | Register; Table 9                       |                    |               | 33-63         | 1.391+ (0.0434* (cg2 <sub>d</sub> -32) | 1.39-2.74                              |           |

|                |                                         |                    | LINEAR        | 0-47          | 0.6956 +(0.0434 x cg2 <sub>d</sub> )   | 0.69-2.74                              |           |

| 02h            | DPGA Color 3 Gain<br>Register; Table 10 | cg3                | RAW           | 0-32          | 0.6956 + (0.02174* cg3 <sub>d</sub> )  | 0.69-1.39                              |           |

|                |                                         | Register, Table 10 |               |               | 33-63                                  | 1.391+ (0.0434* (cg3 <sub>d</sub> -32) | 1.39-2.74 |

|                |                                         |                    | LINEAR        | 0-47          | 0.6956 +(0.0434 x cg3 <sub>d</sub> )   | 0.69-2.74                              |           |

| 03h            |                                         |                    |               |               | 0-32                                   | 0.6956 + (0.02174* cg4 <sub>d</sub> )  | 0.69-1.39 |

|                | Register; Table 11                      | Register; Table 11 |               | 33-63         | 1.391+ (0.0434* (cg4 <sub>d</sub> -32) | 1.39-2.74                              |           |

|                |                                         |                    | LINEAR        | 0-47          | 0.6956 +(0.0434 x cg4 <sub>d</sub> )   | 0.69-2.74                              |           |

Table 3. White Balance Gain modes and Gain Formulas

NOTE!! The Diagrams above illustrates how the Color Gain Registers apply the gain onto each individual color pixel data:

Revision 8.0 - 28 November 2001 : MCM20027 MOTOROLA

| Register<br>No | Register Name                | Variable | Gain<br>Modes | Gain<br>Steps | Gain Formula                           | Gain<br>Range |

|----------------|------------------------------|----------|---------------|---------------|----------------------------------------|---------------|

| 10h            | Exposure PGA Global          | gg1      | RAW           | 0-32          | 0.6956 + (0.02174* gg1 <sub>d</sub> )  | 0.69-1.39     |

|                | Gain Register A; Table<br>23 |          |               | 33-63         | 1.391+ (0.0434* (gg1 <sub>d</sub> -32) | 1.39-2.74     |

|                |                              |          | LINEAR        | 0-47          | 0.6956 +(0.0434 x gg1 <sub>d</sub> )   | 0.69-2.74     |

|                |                              |          | LINEAR 2      | 0-67          | 0.6956 + (0.0434 * gg2 <sub>d</sub> )  | 0.69-3.60     |

| 21h            | Exposure PGA Global          | gg2      | RAW           | 0-32          | 0.6956 + (0.02174* cg2 <sub>d</sub> )  | 0.69-1.39     |

|                | Gain Register B; Table<br>24 | _        |               | 33-63         | 1.391+ (0.0434* (cg2 <sub>d</sub> -32) | 1.39-2.74     |

|                |                              |          | LINEAR        | 0-47          | 0.6956 +(0.0434 x cg2 <sub>d</sub> )   | 0.69-2.74     |

|                |                              |          | LINEAR 2      | 0-67          | 0.6956 + (0.0434 * gg2 <sub>d</sub> )  | 0.69-3.60     |

**Table 4. Exposure Gain modes and Gain Formulas**

The Diagram below illustrates how the Exposure Gain Registers apply the gain onto the pixel data:

# **MOTOROLA**

# SEMICONDUCTOR TECHNICAL DATA

## 7.5 Global Digital Offset Voltage Adjust (DOVA)

A programmable global offset adjustment is available on the MCM20027. A user defined offset value is loaded via a 6-bit signed magnitude programming code via the Global DOVA Register, (Table 28), on page 47.

Offset correction allows fine-tuning of the signal to remove any additional residual error which may have accumulated in the analog signal path. This function is performed directly before analog to digital conversion and introduces a fixed gain of 2.0X. This feature is useful in applications that need to insert a desired offset to adjust for a known system noise floor relative to AVSS and offsets of amplifiers in the analog chain.

## 7.6 Analog to Digital Converter (ADC)

The ADC is a fully differential, low power circuit. A pipelined, Redundant Signed Digit (RSD) algorithmic technique is used to yield an ADC with superior characteristics for imaging applications.

Integral Noise Linearity (INL) and Differential Noise Linearity (DNL) performance is specified at +1.0 and +0.5. respectively, with no missing codes. The input voltage resolution is 2.44 mV with a full-scale 2.5 V<sub>pp</sub> input (2.5  $V_{pp}/2^{10}$ ). The input dynamic range of the ADC is programmed via a Programmable Voltage Reference Generator. The positive reference voltage (VREFP) and negative reference voltages (VREFM) can be programmed from 2.5V to 1.25V and 0V to 1.25V respectively in steps of 5mV via the Reference Voltage Registers (Table 17 and Table 18). This feature is used independently or in conjunction with the DPGAs to maximize the system dynamic range based on incident illumination. The default input range for the ADC is 1.9V for VREFP and 0.6V for VREFM hence allowing a 10 bit digitization of a 1.3V peak to peak signal.

Revision 8.0 - 28 November 2001 : MCM20027 MOTOROLA

# 8.0 Sensor External Controls (Additional Operational Conditions)

The MCM20027 includes initialization, standby modes, and external reference voltage outputs to afford the user additional applications flexibility.

#### 8.1 Initialization

The INIT input pin (#42) controls reinitialization of the MCM20027. This serves to assure controlled chip and system startup. Control is asserted via a logic high input. (i.e.. Asserting a Logic high "1" initializes all the Registers, while asserting a Logic low "0" returns the sensor to normal operation). This state must be held a minimum of 1 ms and a 1 ms "wait period" should be allowed before chip processing to ensure that the start-up routines within the MCM20027 have run to completion, and to guarantee that all holding and bypass capacitors, etc. have achieved their required steady state values.

Tasks which are accomplished during startup include: reset of the utility programming registers and initialization to their default values (please refer to previous section for settings), reset of all internal counters and latches, and setup of the analog signal processing chain.

Another method of saving power consumption is to applying an active high signal to the INIT pin (#42) but Note - Doing this will also cause initialization of the chip

# 8.2 Standby Mode

The standby mode option is implemented to allow the user to reduce system power consumption during periods which do not require operation of the MCM20027. This feature allows the user to extend battery life in low power applications.

By utilizing this mode, the user may reduce dynamic power consumption from 250mW RMS nominal @13.5MHz to ≤100 uW in the standby mode.

The standby mode is activated by writing a "1" to bit 0 of "Power Configuration Register" on page 41. Writing a "0" restores normal operation.

#### 8.3 Tristate Mode

The sensors HCLK, SOF, VCLK, SYNC and STROBE output signals as well as the pixel output data can be tristated via the Tristate Control Register, (Table 21), on page 42.

#### 8.4 References CVREFP, CVREFM

The MCM20027 contains all internally generated references and biases on-chip for system simplification. An internally generated differential bandgap regulator derives all the ADC and other analog signal processing required references. The user should connect  $0.1\mu F$  capacitors to the CVREFP and CVREFM pins (#15 and #14 respectively) to accurately hold the biases.

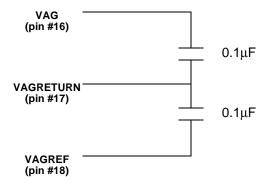

# 8.5 Common Mode References: VAG, VAGREF and VAGRETURN

The MCM20027 holds the Common Mode Reference Voltages on the chip to a stable value. In order to achieve this stable value, the VAG (pin #16), VAGREF(pin #18 ) and VAGRETURN (pin #17) have to be connected to two  $0.1\mu F$  capacitors in the manner described in the diagram below:

# **MOTOROLA**

# SEMICONDUCTOR TECHNICAL DATA

# **8.6 Internal Bias Current Control**

The ASP chain has internally generated bias currents that result in an operating power consumption of nearly 400mW approx. (Accurate value will be given upon sensor testing). By attaching a resistor between pin 20, EXTRES; and Pin19, the user can reduce the power consumption of the device. This feature is enabled by writing a 1<sub>b</sub> to bit **res** of the Power Configuration Register. Additional power savings can be achieved at lower clock rates. Note - The External Bias resistor Input pin (EXTRESP - pin #20) should be connected to the

ETRESRTN (pin#19) in the manner described in the diagram below.

Revision 8.0 - 28 November 2001 : MCM20027 MOTOROLA

## 9.0 Sensor Output/Input Signals

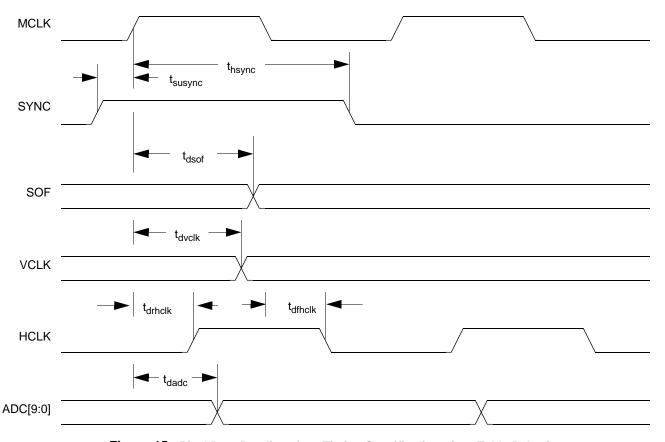

# 9.1 Start Of Data Capture (SYNC)

This signal is utilized by the sensor to indicate the start of integration (data capture) in Single Frame Rolling Shutter capture mode (SFRS). For more info refer to Figure 15, on page 22, Figure 8, on page 12 and Figure 16, on page 24. This signal can be generated internally by the sensor or be driven via Pin # 46 of the sensor (see Figure 20, on page 67). To set whether the signal is generated internally or externally, as well as other settings to this signal, refer to Sync and Strobe Control register, (Table 31), on page 50.

# 9.2 Start Of Row Readout (SOF)

This signal triggers/indicates the start of Row Readout of the frame. This signal is an Output and can be read via Pin # 48 of the sensor (see Figure 20, on page 67). The SOF signal delay as well as its length can be set by the user via SOF Delay Register, (Table 46), on page 57 and SOF & VCLK Signal Length Control Register, (Table 48), on page 57. For timing diagrams depicting the use of the SOF signal refer to Figure 15, on page 22, Figure 6, on page 11, Figure 7, on page 12, Figure 8, on page 12 and Figure 16, on page 24.

## 9.3 Horizontal Data SYNC (VCLK)

This signal triggers the Readout of the sequential rows of the frame. This signal is an Output and can be read via Pin # 44 of the sensor (see Figure 20, on page 67). The VCLK signal delay in relation to SOF, as well as its length can be set by the user via VCLK Delay Register, (Table 47), on page 57 and SOF & VCLK Signal Length Control Register, (Table 48), on page 57. For timing diagrams depicting the use of the VCLK signal refer to Figure 15, on page 22, Figure 6, on page 11, Figure 7, on page 12, Figure 8, on page 12 and Figure 16, on page 24.

# 9.4 Data Valid (HCLK)

This signal triggers/indicates a single active pixel data has been readout (eg Column 5 of Row 10 data has been read out). This signal is an Output and can be read via Pin # 45 of the sensor (see Figure 20, on page 67). The HCLK signal delay can be set by the user via HCLK Delay Register, (Table 52), on page 60. For timing diagrams depicting the use of the HCLK signal refer to Figure 15, on page 22, Figure 6, on page 11, Figure 7, on page 12 ,and Figure 8, on page 12.

Figure 15. Pixel Data Bus linterface Timing Specifications (see Table Below)

# **MOTOROLA**

# SEMICONDUCTOR TECHNICAL DATA

# PIXEL DATA BUS INTERFACE TIMING SPECIFICATIONS (see Figure 15)

| Symbol              | Characteristic                                          | Min | Тур  | Max  | Unit |

|---------------------|---------------------------------------------------------|-----|------|------|------|

| f <sub>max</sub>    | MCLK maximum frequency                                  | 1   | 11.5 | 13.5 | MHz  |

| t <sub>hsync</sub>  | SYNC hold time w.r.t MCLK                               | 3.5 | -    | 9    | ns   |

| t <sub>susync</sub> | SYNC setup time w.r.t MCLK                              | 3.0 | -    | 8.5  | ns   |

| t <sub>dsof</sub>   | MCLK to SOF delay time                                  | 8   | 13   | 21.5 | ns   |

| t <sub>dvclk</sub>  | MCLK to VCLK delay time                                 | 8.5 | 13.5 | 22   | ns   |

| t <sub>drhclk</sub> | Rising edge of MCLK to rising edge of HCLK delay time   | 7.5 | 13   | 22   | ns   |

| t <sub>dfhclk</sub> | Falling edge of MCLK to falling edge of HCLK delay time | 3   | 5    | 10.5 | ns   |

| t <sub>dadc</sub>   | MCLK to ADC[9:0] delay time                             | 8   | 13   | 21.5 | ns   |

| t <sub>strobe</sub> | MCLK to STROBE delay time                               | 8   | 13   | 21.5 | ns   |

#### 9.5 Strobe Signal

The Strobe signal is a output pin on the MCM20027 sensor that can be used to activate 'Flash/Strobe illumination modules". It can be activated by writing a "1" to bit 3 of "Sync and Strobe Control register" on page 50 while in SFRS mode. When activated, the Strobe signal goes high (Active) when all Rows are Integrating simultaneously, and ends one Row period ( $T_{row}$ ) before the

last Row begins to Integrate. (see 3"Frame Rate and Integration Time Control" on page 13). The start of the strobe signal can also be set by the user. In default mode, when the strobe is activated, the signal fires 2 Row Periods ( $T_{row}$ ) before the first Row begins to Readout and last for a length of 1  $T_{row}$ . A sample timing diagram for the Strobe signal can be seen in Figure 16, on page 24:

Figure 16. Strobe Timing Diagram in SFRS capture mode

# SEMICONDUCTOR TECHNICAL DATA

To ensure that Strobe signal fires, the integration time must be large enough to ensure that all rows are integrating simulanteously for at least 2 Row periods ( $T_{row}$ )

(see "Frame Rate and Integration Time Control" on page 13)

where

$$T_{row} = (vcw_d + shs_d + shr_d + 19)$$

To accomplish this - ensure that the Integration time  $(cint_d)$  greater than 2 Row periods  $(T_{row})$  larger than the active Window of Interest Row depth.

Min. Integration time

$$=T_{intmin}=(cint_{min}+1)*T_{row}$$

$$cint_{min}=wrd_d+x$$

where  $x > 2$

where wrdd is the Window Of Interest Row depth.

$$T_{\text{strobe1}} = T_{\text{row}}$$

$$T_{\text{strobe2}} = T_{\text{intmin}} - (\text{wrd}_d + 1) * T_{\text{row}}$$

**EXAMPLE:** Below you will find an example of how to ensure that the strobe signal will fire and to determine the length of the STROBE signal in default mode:

(Refer to Figure 16, on page 24 for timing analysis)

# Goal (For example purpose):

Strobe Signal that lasts for at least 250us, which is the length of a typical strobe/flash event.

# **Assumptions:**

1) Active Window of Interest = 1280 x 1024

$$(wrd_d) = 1023$$

- 2) Virtual Column Width (vcw<sub>d</sub>)= 1290

- 3) Virtual Row Depth (vrd<sub>d</sub>) = 1034

- 4) Sample & hold time (shs<sub>d</sub>) = 10

- 5) Sample & hold time  $(\mathbf{shr_d}) = 10$

- 6) MCLK = 13 Mhz

#### Variables:

Integration Time  $(cint_{min})$  is the main variable used to control the time of the Strobe signals.

$$T_{intmin} = (cint_{min} + 1) * T_{row}$$

# **Calculations:**

$$cint_{min} = wrd_d + x$$

where  $x > 2$

Let

$$cint_{min} = wrd_d + x$$

where  $x > 2$

Therefore,

$$T_{intmin} = 101.39$$

$$T_{\text{strobe1}} = 98.44 \mu s$$

$$T_{\text{strobe2}} = T_{\text{intmin}} - (\text{wrd}_d + 2) * T_{\text{row}}$$

$$= 3 * T_{row}$$

$$= 295us$$

# Results:

| Signal               | Value |

|----------------------|-------|

| T <sub>row</sub>     | 98us  |

| T <sub>int</sub>     | 101ms |

| T <sub>strobe1</sub> | 98us  |

| T <sub>strobe2</sub> | 295us |

| T <sub>frame</sub>   | 202ms |

**NOTE!!** Refer to Figure 16, on page 24 for timing analysis

#### 10.0 I<sup>2</sup>C Serial Interface

The I $^2$ C is an industry standard which is also compatible with the Motorola bus (called M-Bus) that is available on many microprocessor products. The I $^2$ C contains a serial two-wire half-duplex interface that features bidirectional operation, master or slave modes, and multimaster environment support. The clock frequency on the system is governed by the slowest device on the board. The SDATA and SCLK are the bidirectional data and clock pins, respectively. These pins are open drain and will require a pull-up resistor to VDD of 1.5 k $\Omega$  to 10 k $\Omega$  (see page 66).

The I<sup>2</sup>C is used to write the required user system data into the Program Control Registers in the MCM20027. The I<sup>2</sup>C bus can also read the data in the Program Control Register for verification or test considerations. The MCM20027 is a slave only device that supports a maximum clock rate (SCLK) of 100 kHz while reading or writing only one register address per I<sup>2</sup>C start/stop cycle. The following sections will be limited to the methods for writing and reading data into the MCM20027 register.

For a complete reference to I<sup>2</sup>C, see "The I<sup>2</sup>C Bus from Theory to Practice" by Dominique Paret and Carll-Fenger, published by John Wiley & Sons, ISBN 0471962686.

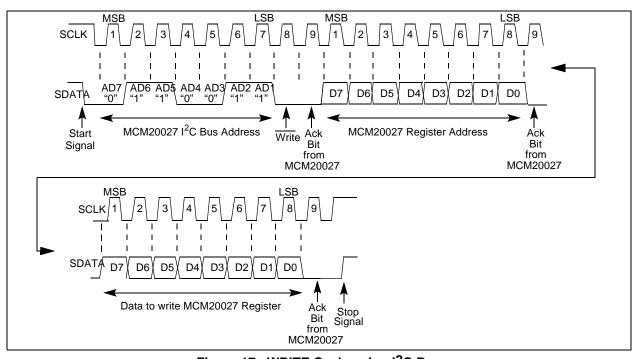

# 10.1 MCM20027 I<sup>2</sup>C Bus Protocol

The MCM20027 uses the I<sup>2</sup>C bus to write or read one register byte per start/stop I<sup>2</sup>C cycle as shown in Figure 17 and Figure 18. These figures will be used to describe the various parts of the I<sup>2</sup>C protocol communications as it applies to the MCM20027.

MCM20027 I<sup>2</sup>C bus communication is basically composed of following parts: START signal, MCM20027 slave address (0110011 $_{\rm b}$ ) transmission followed by a R/ $\overline{\rm W}$  bit, an acknowledgment signal from the slave, 8 bit data transfer followed by another acknowledgment signal, STOP signal, Repeated START signal, and clock synchronization.

#### 10.2 START Signal

When the bus is free, i.e. no master device is engaging the bus (both SCLK and SDATA lines are at logical "1"), a master may initiate communication by sending a START signal. As shown in Figure 17, a START signal is defined as a high-to-low transition of SDATA while SCLK is high. This signal denotes the beginning of a new data transfer and wakes up all the slaves on the bus.

#### 10.3 Slave Address Transmission

The first byte of a data transfer, immediately after the START signal, is the slave address transmitted by the master. This is a 7-bit calling address followed by a R/W bit. The seven-bit address for the MCM20027, starting with the MSB (AD7) is 0110011 $_{\rm b}$ . The transmitted calling address on the SDATA line may only be changed while SCLK is low as shown in Figure 17. The data on the SDATA line is valid on the High to Low signal transition on the SCLK line. The R/W bit following the 7-bit tells the slave the desired direction of data transfer:

- 1 = Read transfer, the slave transitions to a slave transmitter and sends the data to the master

- 0 = Write transfer, the master transmits data to the slave

# 10.4 Acknowledgment

Only the slave with a calling address that matches the one transmitted by the master will respond by sending back an acknowledge bit. This is done by pulling the SDATA line low at the 9th clock (see Figure 17). If a transmitted slave address is acknowledged, successful slave addressing is said to have been achieved. No two slaves in the system may have the same address. The MCM20027 is configured to be a slave only.

#### 10.5 Data Transfer

Once successful slave addressing is achieved, data transfer can proceed between the master and the selected slave in a direction specified by the R/W bit sent by the calling master. Note that for the first byte after a start signal (in Figure 17 and Figure 18), the R/W bit is always a "0" designating a write transfer. This is required since the next data transfer will contain the register address to be read or written.

All transfers that come after a calling address cycle are referred to as data transfers, even if they carry sub-address information for the slave device.

Each data byte is 8 bits long. Data may be changed only while SCLK is low and must be held stable while SCLK is high as shown in Figure 17. There is one clock pulse on SCLK for each data bit, the MSB being transferred first.

Each data byte has to be followed by an acknowledge bit, which is signalled from the receiving device by pulling the SDATA low at the ninth clock. So one complete data byte transfer needs nine clock pulses. If the slave receiver does not acknowledge the master, the SDATA line must be left high by the slave. The master can then generate a stop signal to abort the data transfer or a start signal (repeated start) to commence a new calling.

# SEMICONDUCTOR TECHNICAL DATA

If the master receiver does not acknowledge the slave transmitter after a byte transmission, it means 'end of data' to the slave, so the slave releases the SDATA line for the master to generate STOP or START signal.

#### 10.6 Stop Signal

The master can terminate the communication by generating a STOP signal to free the bus. However, the master may generate a START signal followed by a calling command without generating a STOP signal first. This is called a Repeated START. A STOP signal is defined as a low-to-high transition of SDATA while SCLK is at logical "1" (see Figure 17).

The master can generate a STOP even if the slave has generated an acknowledge bit at which point the slave must release the bus.

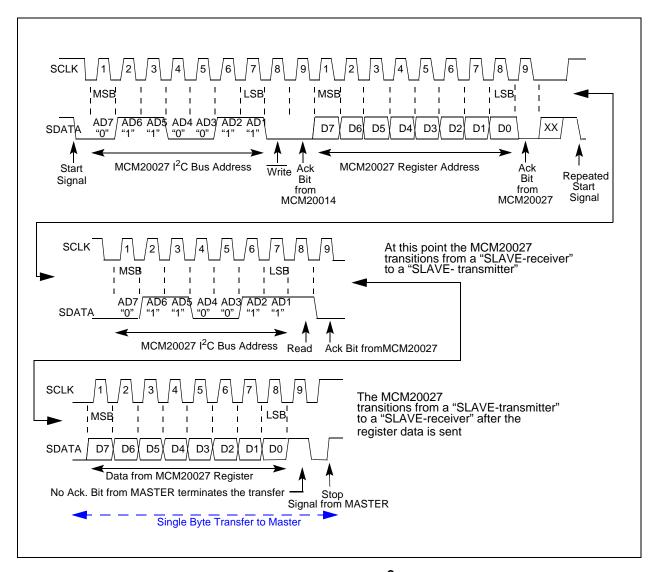

# 10.7 Repeated START Signal

A Repeated START signal is a START signal generated without first generating a STOP signal to terminate the communication. This is used by the master to communicate with another slave or with the same slave in a different mode (transmit/receive mode) without releasing the bus.

As shown in Figure 18, a Repeated START signal is being used during the read cycle and to redirect the data transfer from a write cycle (master transmits the register address to the slave) to a read cycle (slave transmits the data from the designated register to the slave).

Figure 17. WRITE Cycle using I<sup>2</sup>C Bus

#### 10.8 I<sup>2</sup>C Bus Clocking and Synchronization

Open drain outputs are used on the SCLK outputs of all master and slave devices so that the clock can be synchronized and stretched using wire-AND logic. This means that the slowest device will keep the bus from going faster than it is capable of receiving or transmitting data.

After the master has driven SCLK from High to Low, all the slaves drive SCLK Low for the required period that is needed by each slave device and then releases the SCLK bus. If the slave SCLK Low period is greater than the master SCLK Low period, the resulting SCLK bus

signal Low period is stretched. Therefore, synchronized clocking occurs since the SCLK is held low by the device with the longest Low period. Also, this method can be used by the slaves to slow down the bit rate of a transfer. The master controls the length of time that the SCLK line is in the High state. The data on the SDATline is valid when the master switches the SCLK line from a High to a Low.

Slave devices may hold the SCLK low after completion of one byte transfer (9 bits). In such case, it halts the bus clock and forces the master clock into wait states until the slave releases the SCLK line.

# **MOTOROLA**

# SEMICONDUCTOR TECHNICAL DATA

# 10.9 Register Write

Writing the MCM20027 registers is accomplished with the following I<sup>2</sup>C transactions (see Figure 17):

- Master transmits a START

- Master transmits the MCM20027 Slave Calling Address with "WRITE" indicated (BYTE=66<sub>h</sub>, 102<sub>d</sub>, 01100110<sub>h</sub>)

- MCM20027 slave sends acknowledgment by forcing the SDATA Low during the 9th clock, if the Calling Address was received

- Master transmits the MCM20027 Register Address

- MCM20027 slave sends acknowledgment by forcing the SDATA Low during the 9th clock after receiving the Register Address

- Master transmits the data to be written into the register at the previously received Register Address

- MCM20027 slave sends acknowledgment by forcing the SDATA Low during the 9th clock after receiving the data to be written into the Register Address

- Master transmits STOP to end the write cycle

# 10.10 Register Read

Reading the MCM20027 registers is accomplished with the following I<sup>2</sup>C transactions (see Figure 18):

- Master transmits a START

- Master transmits the MCM20027 Slave Calling Address with "WRITE" indicated (BYTE=66<sub>h</sub>, 102<sub>d</sub>, 01100110<sub>b</sub>)

- MCM20027 slave sends acknowledgment by forcing the SData Low during the 9th clock, if the Calling Address was received

- Master transmits the MCM20027 Register Address

- MCM20027 slave sends acknowledgment by forcing the SData Low during the 9th clock after receiving the Register Address

- Master transmits a Repeated START

- Master transmits the MCM20027 Slave Calling Address with "READ" indicated (BYTE = 67<sub>h</sub>, 103<sub>d</sub>, 01100111<sub>b</sub>)

- MCM20027 slave sends acknowledgment by forcing the SDATA Low during the 9th clock, if the Calling Address was received

- At this point, the MCM20027 transitions from a "Slave-Receiver" to a "Slave-Transmitter"

- MCM20027 sends the SCLK and the Register Data contained in the Register Address that was previ-

ously received from the master; MCM20027 transitions to slave-receiver

- Master does not send an acknowledgment (NAK)

- · Master transmits STOP to end the read cycle

Figure 18. READ Cycle using I<sup>2</sup>C Bus

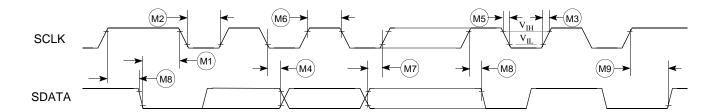

| I <sup>2</sup> C SERIAL INTERFACE <sup>6</sup> TIMING SPECIFICATIONS (see Figure 19) |                                                                          |     |     |                                |  |  |  |  |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----|-----|--------------------------------|--|--|--|--|

| Symbol                                                                               | Characteristic                                                           | Min | Max | Unit                           |  |  |  |  |

| f <sub>max</sub>                                                                     | SCLK maximum frequency                                                   | 50  | 400 | KHz                            |  |  |  |  |

| M1                                                                                   | Start condition SCLK hold time                                           | 4   | -   | T <sub>MCLK</sub> <sup>7</sup> |  |  |  |  |

| M2                                                                                   | SCLK low period                                                          | 8   | -   | T <sub>MCLK</sub>              |  |  |  |  |

| М3                                                                                   | SCLK/SDATA rise time [from $V_{IL} = (0.2)*VDD$ to $V_{IH} = (.8)*VDD$ ] | -   | .3  | μs <sup>8</sup>                |  |  |  |  |

| M4                                                                                   | SDATA hold time                                                          | 4   | -   | T <sub>MCLK</sub> <sup>7</sup> |  |  |  |  |

| M5                                                                                   | SCLK/SDATA fall time (from Vh = 2.4V to VI = 0.5V)                       | -   | .3  | μs <sup>8</sup>                |  |  |  |  |

| M6                                                                                   | SCLK high period                                                         | 4   | -   | T <sub>MCLK</sub>              |  |  |  |  |

| M7                                                                                   | SDATA setup time                                                         | 4   | -   | T <sub>MCLK</sub> <sup>7</sup> |  |  |  |  |

| M8                                                                                   | Start / Repeated Start condition SCLK setup time                         | 4   | -   | T <sub>MCLK</sub>              |  |  |  |  |

| M9                                                                                   | Stop condition SCLK setup time                                           | 4   | -   | T <sub>MCLK</sub>              |  |  |  |  |

| C <sub>I</sub>                                                                       | Capacitive for each I/O pin                                              | -   | 10  | pF                             |  |  |  |  |

| Cbus                                                                                 | Capacitive bus load for SCLK and SDATA                                   | -   | 200 | pF                             |  |  |  |  |

| Rp                                                                                   | Pull-up Resistor on SCLK and SDATA                                       | 1.5 | 10  | kΩ <sup>9</sup>                |  |  |  |  |

<sup>&</sup>lt;sup>6</sup> I<sup>2</sup>C is a proprietary Phillips interface bus

Figure 19. I<sup>2</sup>C SERIAL INTERFACE<sup>6</sup> TIMING SPECIFICATIONS

The unit T<sub>MCLK</sub> is the period of the input master clock; The frequency of MCLK is assumed 13.5 MHz

The capacitive load is 200 pF

A pull-up resistor to VDD is required on each of the SCLK and SDATA lines; for a maximum bus capacitive load of 200 pf, the minimum value of Rp should be selected in order to meet specifications

# 11.0 Suggested Software Register Programming Reference

There are number of registers whose default values we have been changed to make the sensor operational with a Digital Still Camera. The registers, there suggested new values (changes) and reason for there change are detailed in Suggested Register Default Value Changes, (Table 5), on page 31

NOTE!! These are only suggested value changes. Depending on the application, there might exist more or less registers whose default values require modifications.

| Register<br>No         | Register Name                                                              | Default<br>Values      | New<br>Values          | Comment                                                                                                     |

|------------------------|----------------------------------------------------------------------------|------------------------|------------------------|-------------------------------------------------------------------------------------------------------------|

| 0C <sub>h</sub>        | Power Configuration<br>Register; Table 19                                  | <b>00</b> <sub>h</sub> | <b>08</b> <sub>h</sub> | Switching External Resistor On for Lower active power consumption                                           |

| <b>22</b> <sub>h</sub> | PGA Gain Mode; Table 25                                                    | <b>00</b> <sub>h</sub> | <b>06</b> <sub>h</sub> | White Balance switched from Raw to Linear gain mode . Exposure Gain switched from Raw to Linear 2 gain mode |

| <b>23</b> <sub>h</sub> | Global DOVA Register;<br>Table 28                                          | <b>00</b> <sub>h</sub> | <b>27</b> <sub>h</sub> | Negative Offset for Analog Signal Processing chain                                                          |

| <b>42</b> <sub>h</sub> | Sync and Strobe Control register; Table 31                                 | <b>02</b> <sub>h</sub> | <b>00</b> <sub>h</sub> | Necessary for switch to SFRS capture mode in addition to Capture Mode Control Register                      |

| <b>56</b> <sub>h</sub> | SOF & VCLK Signal<br>Length Control Register;<br>Table 48                  | 0E <sub>h</sub>        | <b>09</b> <sub>h</sub> | new SOF = 64 MCLKs<br>new VCLK = 8 MCLKs                                                                    |

| 5F <sub>h</sub>        | Internal Timing Control<br>Register 1 (shs time defi-<br>nition); Table 50 | <b>0A</b> <sub>h</sub> | <b>00</b> <sub>h</sub> | new shs=64 MCLKs<br>increase sample time to sweep all available<br>charge from pixel                        |

| <b>60</b> <sub>h</sub> | Internal Timing Control<br>Register 2 (shr time defini-<br>tion); Table 51 | <b>0A</b> <sub>h</sub> | <b>00</b> <sub>h</sub> | new shr=64 MCLKs<br>increased reset timesweep all available<br>charge from pixel                            |

**Table 5. Suggested Register Default Value Changes**

# 12.0 MCM20027 Utility Programming Registers

# 12.1 Register Reference Map

The I<sup>2</sup>C addressing is broken up into groups of 16 and assigned to a specific digital block. The designated block is responsible for driving the internal control bus, when the assigned range of addresses are present on the internal address bus. The grouping designation and assigned range are listed in Table 6. Each block contains registers which are loaded and read by the digital and analog blocks to provide configuration control via the I<sup>2</sup>C serial interface.

Table 7 contains all the I<sup>2</sup>C address assignments. The table includes a column indicating whether the register values are shadowed with respect to the sensor inter-

| Address Range                     | Block Name                |

|-----------------------------------|---------------------------|

| 00 <sub>h</sub> - 2F <sub>h</sub> | Analog Register Interface |

| 40 <sub>h</sub> - 7F <sub>h</sub> | Sensor Interface          |

| 80 <sub>h</sub> - BF <sub>h</sub> | Column Offset coeff.      |

Table 6. I<sup>2</sup>C Address Range Assignments

face. If the register is shadowed, the sensor interface will only be updated upon frame boundaries, thereby eliminating intraframe artifacts resulting from register changes.

| Hex<br>Address  | Register Function                                    |                 | Ref.<br>Table     | Shadow ed? |

|-----------------|------------------------------------------------------|-----------------|-------------------|------------|

| 00 <sub>h</sub> | DPGA Color 1 Gain Register (Green of Green-Red Row)  | 0E <sub>h</sub> | Table 8, page 35  | Yes        |

| 01 <sub>h</sub> | DPGA Color 2 Gain Register (Red)                     | 0E <sub>h</sub> | Table 9, page 35  | Yes        |

| 02 <sub>h</sub> | DPGA Color 3 Gain Register (Blue)                    | 0E <sub>h</sub> | Table 10, page 36 | Yes        |

| 03 <sub>h</sub> | DPGA Color 4 Gain Register (Green of Blue-Green Row) | 0E <sub>h</sub> | Table 11, page 36 | Yes        |

| 04 <sub>h</sub> | Unused                                               |                 |                   |            |

| 05 <sub>h</sub> | Color Tile Configuration Register                    |                 | Table 12, page 37 | No         |

| 06 <sub>h</sub> | Color Tile Row 1 Definition Register                 | 44 <sub>h</sub> | Table 13, page 38 | No         |

| 07 <sub>h</sub> | Color Tile Row 2 Definition Register                 | EE <sub>h</sub> | Table 14, page 38 | No         |

| 08 <sub>h</sub> | Color Tile Row 3 Definition Register                 | 00 <sub>h</sub> | Table 15, page 39 | No         |

| 09 <sub>h</sub> | Color Tile Row 4 Definition Register                 | 00 <sub>h</sub> | Table 16, page 39 | No         |

| 0A <sub>h</sub> | Negative Voltage Reference Code Register             | 76 <sub>h</sub> | Table 17, page 40 | No         |

| 0B <sub>h</sub> | Positive Voltage Reference Code Register             | 80 <sub>h</sub> | Table 18, page 40 | No         |

| 0C <sub>h</sub> | Power Configuration Register                         | 00 <sub>h</sub> | Table 19, page 41 | No         |

| 0D <sub>h</sub> | Factory Use Only                                     | FUO             | FUO               | FUO        |

| 0E <sub>h</sub> | Reset Control Register                               | 00 <sub>h</sub> | Table 20, page 42 | No         |

| 0F <sub>h</sub> | Device Identification (read only)                    | 50 <sub>h</sub> |                   | No         |

Table 7. I<sup>2</sup>C Address Assignments

# SEMICONDUCTOR TECHNICAL DATA

| Hex<br>Address                    | Register Function                           | Defa<br>ult     | Ref.<br>Table     | Shadow ed? |

|-----------------------------------|---------------------------------------------|-----------------|-------------------|------------|

| 10 <sub>h</sub>                   | Exposure PGA Global Gain Register A         | 0E <sub>h</sub> | Table 23, page 44 | Yes        |

| 11 <sub>h</sub>                   | Unused                                      |                 |                   |            |

| 12h                               | Tristate Control Register; Table 21         | 03 <sub>h</sub> | Table 21, page 42 |            |

| 13h                               | Programable Bias Generator Control register | 00 <sub>h</sub> | Table 22, page 43 |            |

| 14-1F                             | Unused                                      |                 |                   |            |