# DATA SHEET

# MOS INTEGRATED CIRCUIT Phase-out/Discontinued μ**PD70741**

# V821™ 32-/16-BIT MICROPROCESSOR

The  $\mu$ PD70741 (V821) is a 32/16-bit RISC microprocessor that uses, as its processor core, the highperformance 32-bit microprocessor  $\mu$ PD70732 (V810<sup>TM</sup>) designed for built-in control applications. It incorporates peripheral functions such as a DRAM/ROM controller, 2-channel DMA controller, real-time pulse unit, serial interface, and interrupt controller.

The V821, which offers quick real-time response, high-speed integer instructions, bit string instructions, and floating-point instructions, is ideally suited to use in OA equipment such as printers and facsimiles, image processing devices such as those used in navigation units, portable devices, and other devices demanding excellent cost performance.

The functions are described in detail in the following User's Manuals, which should be read before starting design work.

- V821 User's Manual Hardware

- V810 Family<sup>™</sup> User's Manual Architecture : U10082E

# **FEATURES**

NEC

○ The V810 32-bit microprocessor is used as the CPU core ○ Memory access control functions

- Separate address/data bus Address bus: 24 bits Data bus : 16 bits

- Built-in 1-Kbyte instruction cache memory

- Pipeline structure of 1-clock pitch

- Internal 4-Gbyte linear address space

- 32-bit general-purpose registers: 32

○ Instructions ideal for various application fields

- Floating-point operation instructions and bit string instructions

- Interrupts controller

- Nonmaskable : 1 external input

- Maskable : 8 external inputs and 11 types of internal sources

- Priorities can be specified in units of four groups.

- Wait control unit

- Capable of CS control over four blocks in both memory and I/O spaces.

- Linear address space of each block: 16M bytes

- - Supports DRAM high-speed page mode.

: U10077E

- Supports page-ROM page mode.

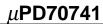

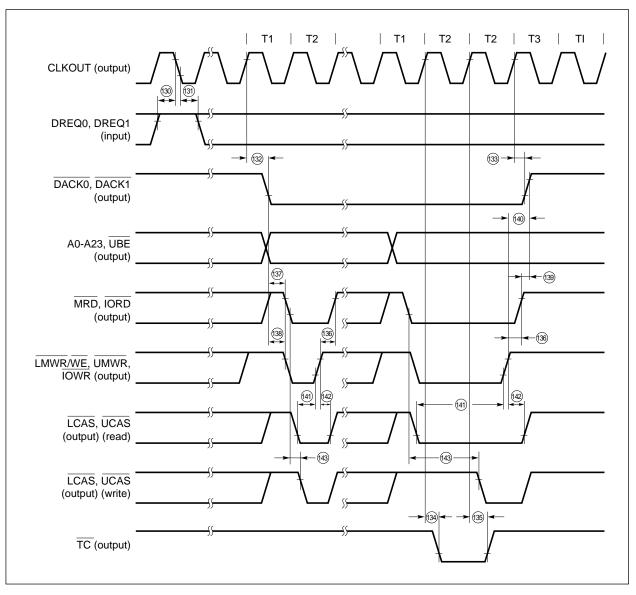

- O DMA controller (DMAC): 2 channels

- Maximum transfer count: 65 536

- Two transfer types (fly-by (1-cycle) transfer and 2-cycle transfer)

- · Three transfer modes (single transfer, singlestep transfer, and block transfer)

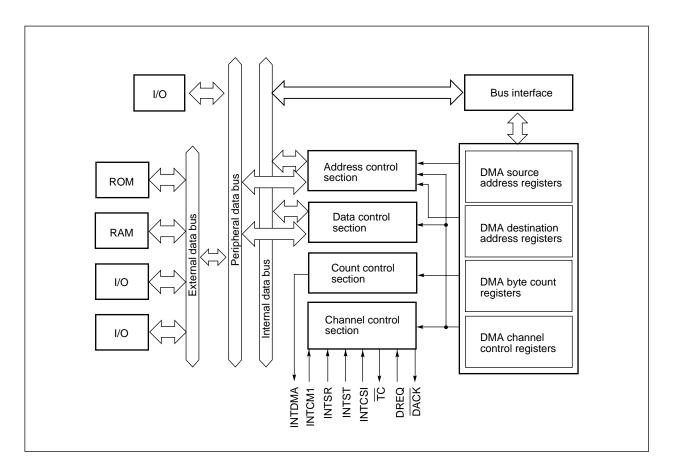

- Serial interfaces : 2 channels

- Asynchronous serial interface (UART): 1 channel

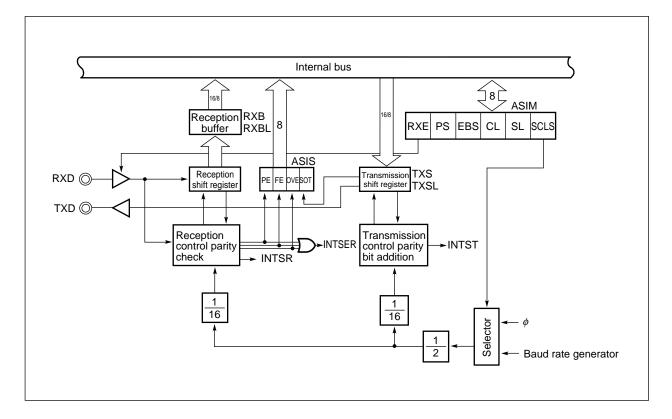

- Synchronous serial interface (CSI): 1 channel

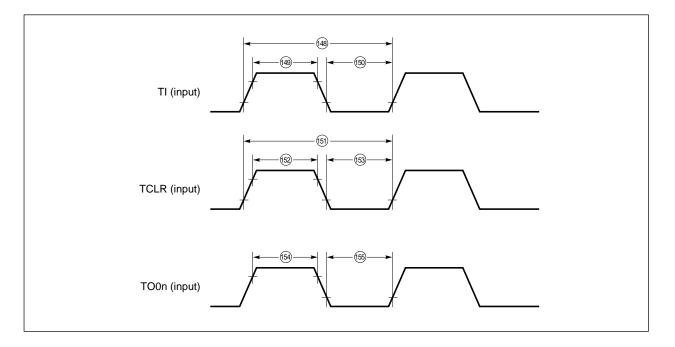

- Real-time pulse unit

- 16-bit timer/event counter : 1 channel

- : 1 channel • 16-bit interval timer

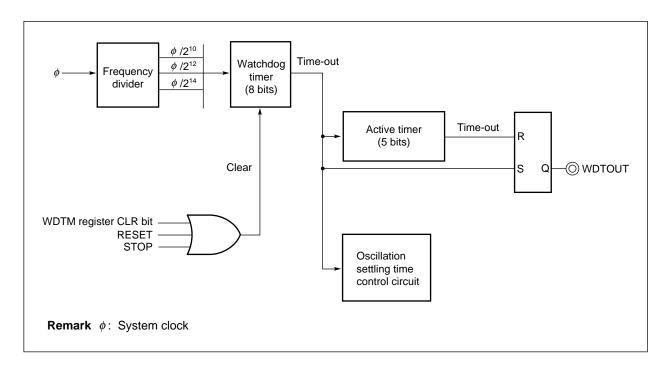

- Watchdog timer functions

- Clock generator functions

- Standby functions (HALT, IDLE, and STOP modes)

The information in this document is subject to change without notice.

# **\*** ORDERING INFORMATION

Part number

Package

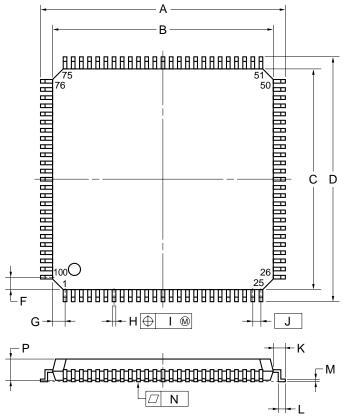

$\mu$ PD70741GC-25-8EU 100-pin plastic LQFP (fine pitch) (14  $\times$  14  $\times$  1.40 mm)

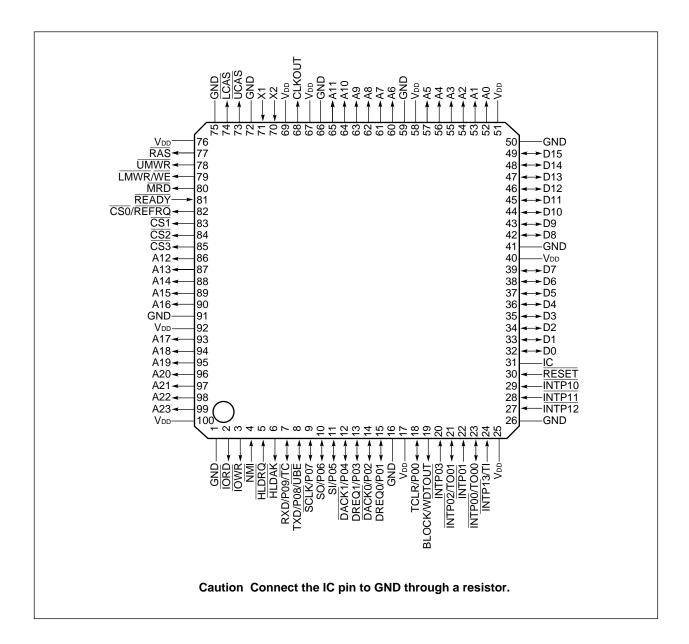

# ★ PIN CONFIGURATION (TOP VIEW)

100-pin plastic LQFP (fine pitch) (14  $\times$  14 mm)  $\mu$ PD70741GC-25-8EU

μ**PD70741**

# PIN NAMES

| A0-A23                       | : Address Bus                    |

|------------------------------|----------------------------------|

| BLOCK                        | : Bus Lock                       |

| CLKOUT                       | : System Clock Out               |

| CS0-CS3                      | : Chip Select                    |

| D0-D15                       | : Data Bus                       |

| DACK0, DACK1                 | : DMA Acknowledge                |

| DREQ0, DREQ1                 | : DMA Request                    |

| HLDAK                        | : Hold Acknowledge               |

| HLDRQ                        | : Hold Request                   |

| INTPO0-INTPO3, INTP10-INTP13 | : Interrupt Request              |

| IORD                         | : I/O Read                       |

| IOWR                         | : I/O Write                      |

| LCAS                         | : Lower Column Address Strobe    |

| LMWR                         | : Lower Memory Write             |

| MRD                          | : Memory Read                    |

| NMI                          | : Non-maskable Interrupt Request |

| P00-P09                      | : Port                           |

| RAS                          | : Row Address Strobe             |

| READY                        | : Ready                          |

| REFRQ                        | : Refresh Request                |

| RESET                        | : Reset                          |

| RXD                          | : Receive Data                   |

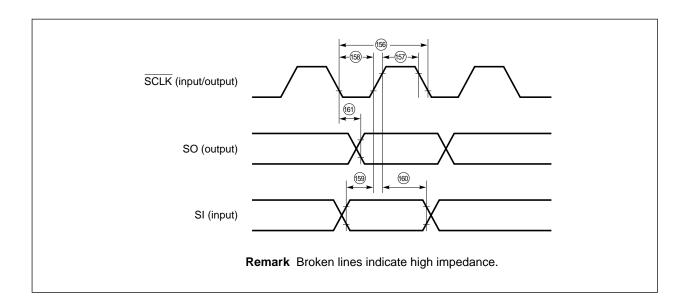

| SCLK                         | : Serial Clock                   |

| SI                           | : Serial Input                   |

| SO                           | : Serial Output                  |

| TC                           | : Terminal Count                 |

| TCLR                         | : Timer Clear                    |

| ті                           | : Timer Input                    |

| TO00, TO01                   | : Timer Output                   |

| TXD                          | : Transmit Data                  |

| UBE                          | : Upper Byte Enable              |

| UCAS                         | : Upper Column Address Strobe    |

| UMWR                         | : Upper Memory Write             |

| WDTOUT                       | : Watchdog Timer Output          |

| WE                           | : Write Enable                   |

| X1, X2                       | : Crystal Oscillator             |

|                              |                                  |

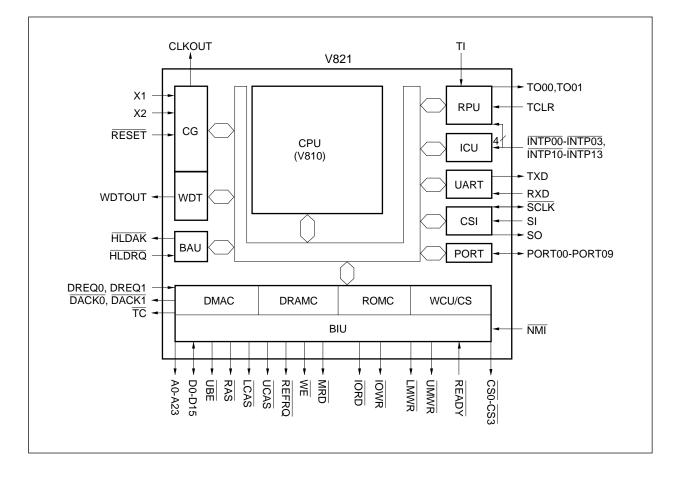

# **\*** INTERNAL BLOCK DIAGRAM

# CONTENTS

| 1. | PIN F | UNCTIC   | DNS                                    | 8  |

|----|-------|----------|----------------------------------------|----|

|    | 1.1   | Port Pi  | ns                                     | 8  |

|    | 1.2   | Non-Po   | ort Pins                               | 8  |

|    | 1.3   | Pin I/O  | Circuits and Processing of Unused Pins | 10 |

| 2. | INTE  | RNAL U   | NITS                                   | 12 |

|    | 2.1   | Bus Int  | erface Unit (BIU)                      | 12 |

|    | 2.2   | Wait Co  | ontrol Unit (WCU)                      | 12 |

|    | 2.3   | DRAM     | Controller (DRAMC)                     | 12 |

|    | 2.4   | ROM C    | ontroller (ROMC)                       | 12 |

|    | 2.5   | Interrup | pt Controller                          | 12 |

|    | 2.6   | DMA C    | ontroller (DMAC)                       | 12 |

|    | 2.7   | Serial I | nterfaces (UART/CSI)                   | 12 |

|    | 2.8   | Real-Ti  | me Pulse Unit (RPU)                    | 12 |

|    | 2.9   | Watchd   | dog Timer (WDT)                        | 13 |

|    | 2.10  | Clock C  | Generator (CG)                         | 13 |

|    | 2.11  | Bus Ar   | bitration Unit (BAU)                   | 13 |

|    | 2.12  | Port     |                                        | 13 |

| 3. | CPU   | FUNCTI   | ONS                                    | 14 |

|    | 3.1   |          | 9S                                     | 14 |

|    | 3.2   | Addres   | s Space                                | 14 |

|    |       | 3.2.1    | Memory map                             | 15 |

|    |       | 3.2.2    | I/O map                                | 16 |

|    | 3.3   | CPU Re   | egister Set                            | 17 |

|    |       | 3.3.1    | Program register set                   | 18 |

|    |       | 3.3.2    | System register set                    | 19 |

|    | 3.4   | Built-in | Peripheral I/O Registers               | 20 |

|    | 3.5   | Data Ty  | /pes                                   | 23 |

|    |       | 3.5.1    | Data types                             | 23 |

|    |       | 3.5.2    | Data alignment                         | 25 |

|    | 3.6   | Cache.   |                                        | 26 |

| 4. | INTE  | RRUPT/   | EXCEPTION HANDLING FUNCTIONS           | 27 |

|    | 4.1   |          | <br>PS                                 | 27 |

|    | -     |          |                                        |    |

| 5. | WAIT  |          | ROL FUNCTIONS                          | 30 |

|    | 5.1   | Feature  | 9S                                     | 30 |

# μ**ΡD70741**

| 6.  | MEM                                                                                 | DRY ACCESS CONTROL FUNCTIONS                           | 32       |

|-----|-------------------------------------------------------------------------------------|--------------------------------------------------------|----------|

|     | 6.1                                                                                 | DRAM Controller (DRAMC)                                | 32       |

|     |                                                                                     | 6.1.1 Features                                         | 32       |

|     |                                                                                     | 6.1.2 Address multiplexing function                    | 32       |

|     |                                                                                     | 6.1.3 Refresh function                                 | 33       |

|     |                                                                                     | 6.1.4 Self-refresh function                            | 33       |

|     | 6.2                                                                                 | ROM Controller (ROMC)                                  | 33       |

|     |                                                                                     | 6.2.1 on-page/off-page decision                        | 33       |

| 7.  | ПΜΔ                                                                                 | FUNCTIONS (DMA CONTROLLER)                             | 35       |

| ••  | DMA FONCTIONS (DMA CONTROLLER)         35           7.1         Features         35 |                                                        |          |

|     |                                                                                     |                                                        |          |

| 8.  | SERI                                                                                | AL INTERFACE FUNCTION                                  | 37       |

|     | 8.1                                                                                 | Features                                               | 37       |

|     | 8.2                                                                                 | Asynchronous Serial Interface (UART)                   | 37       |

|     |                                                                                     | 8.2.1 Features                                         | 37       |

|     | 8.3                                                                                 | Synchronous Serial Interface (CSI)                     | 39       |

|     |                                                                                     | 8.3.1 Features                                         | 39       |

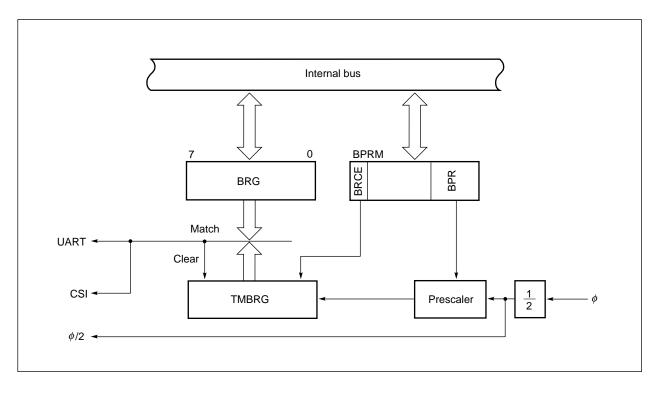

|     | 8.4                                                                                 | Baud Rate Generator (BRG)                              | 40       |

|     |                                                                                     | 8.4.1 Configuration and function                       | 40       |

| 9.  | TIME<br>9.1                                                                         | R/COUNTER FUNCTIONS (REAL-TIME PULSE UNIT)<br>Features | 41<br>41 |

| 10. | WAT                                                                                 | CHDOG TIMER FUNCTIONS                                  | 43       |

|     | 10.1                                                                                | Features                                               | 43       |

|     | 10.2                                                                                | Operation                                              | 44       |

| 44  |                                                                                     |                                                        | 45       |

|     | 11.1                                                                                | Fond nons                                              | 45<br>45 |

|     | 11.1                                                                                |                                                        | 45       |

| 12. | CLOC                                                                                | K GENERATION FUNCTIONS                                 | 46       |

|     | 12.1                                                                                | Features                                               | 46       |

| 12  | <b>CTAN</b>                                                                         | IDBY FUNCTIONS                                         | 47       |

| 15. | 13.1                                                                                | Features                                               | 47       |

|     | 13.1                                                                                | Standby Mode                                           | 47       |

|     | 13.2                                                                                |                                                        | -1       |

| 14. | RESE                                                                                | T FUNCTIONS                                            | 49       |

|     | 14.1                                                                                | Features                                               | 49       |

|     | 14.2                                                                                | Pin Functions                                          | 49       |

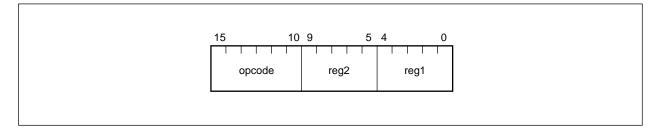

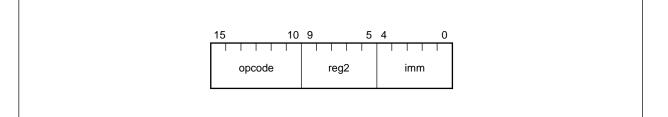

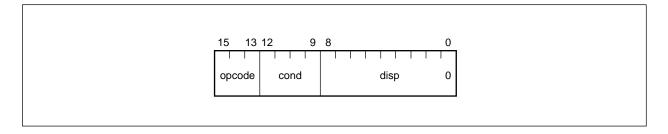

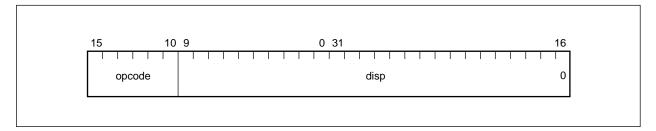

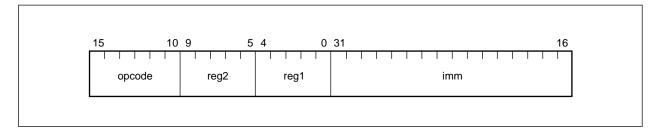

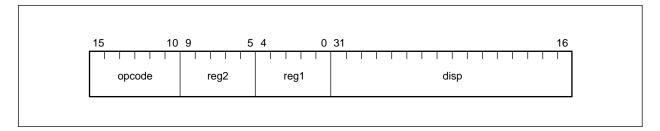

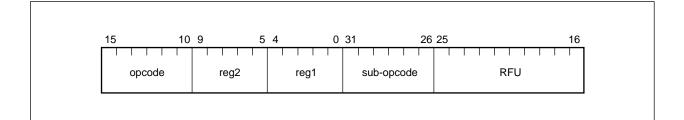

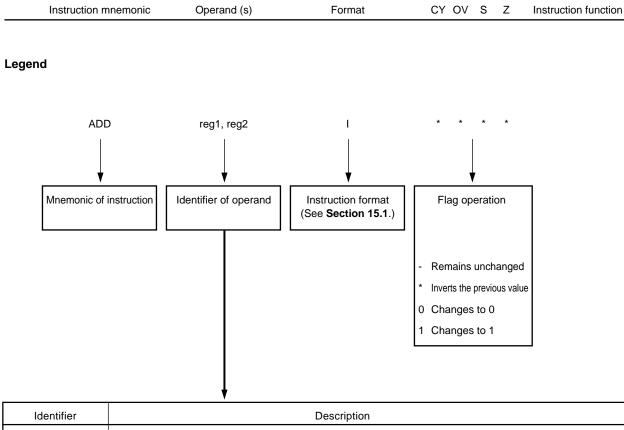

| 15  | INST                                                                                |                                                        | 50       |

|     | 15.1                                                                                | Instruction Format                                     | 50       |

|     | 15.2                                                                                | Instruction Mnemonic (In Alphabetical Order)           | 52       |

|     |                                                                                     | · · · · · · · · · · · · · · · · · ·                    |          |

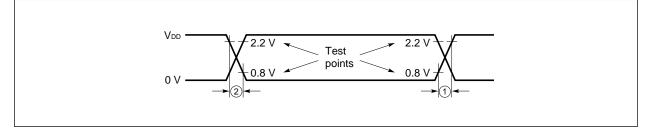

| 16. | ELECTRICAL SPECIFICATIONS        | 62  |

|-----|----------------------------------|-----|

| 17. | PACKAGE DRAWINGS                 | 107 |

| 18. | RECOMMENDED SOLDERING CONDITIONS | 108 |

(1/2)

# **1. PIN FUNCTIONS**

# 1.1 Port Pins

| Pin name | Input/output | Function                         | Dual-function pin |

|----------|--------------|----------------------------------|-------------------|

| P00      | Input/output | Port 0                           | TCLR              |

| P01      |              | 10-bit input/output port         | DREQ0             |

| P02      |              | Can be set for input/output bit. | DACK0             |

| P03      |              |                                  | DREQ1             |

| P04      |              |                                  | DACK1             |

| P05      |              |                                  | SI                |

| P06      |              |                                  | SO                |

| P07      |              |                                  | SCLK              |

| P08      | 1            |                                  | TXD/UBE           |

| P09      |              |                                  | RXD/TC            |

Remark After a reset is released, each port pin is set as an input port pin.

# 1.2 Non-Port Pins

|          |                       |                                             | (1/2)             |

|----------|-----------------------|---------------------------------------------|-------------------|

| Pin name | Input/output          | Function                                    | Dual-function pin |

| A0-A23   | Tristate output       | Address bus signal                          | -                 |

| D0-D15   | Tristate input/output | Bidirectional data bus signal               | -                 |

| READY    | Input                 | Bus cycle termination permit signal         | -                 |

| HLDRQ    | Input                 | Bus mastership request signal               | -                 |

| HLDAK    | Output                | Bus mastership permit signal                | -                 |

| BLOCK    | Output                | Bus mastership prohibit signal              | WDTOUT            |

| MRD      | Tristate output       | Read strobe signal to memory                | -                 |

| LMWR     | Tristate output       | Write strobe signal to lower data in memory | WE                |

| UMWR     | Tristate output       | Write strobe signal to upper data in memory | -                 |

| IORD     | Tristate output       | Read strobe signal to I/O data              | -                 |

| IOWR     | Tristate output       | Write strobe signal to I/O data             | -                 |

| UBE      | Tristate output       | Data bus upper data enable signal           | TXD/P08           |

| RESET    | Input                 | System reset input                          | -                 |

| X1, X2   | Input                 | Crystal connection/external clock input     | -                 |

# μ**ΡD70741**

(2/2)

| Pin name | Input/output    | Function                                                          | Dual-function pir |

|----------|-----------------|-------------------------------------------------------------------|-------------------|

| CLKOUT   | Output          | System clock output                                               | -                 |

| CS0      | Tristate output | Chip select signal                                                | REFRQ             |

| CS1      |                 |                                                                   | -                 |

| CS2      |                 |                                                                   | -                 |

| CS3      |                 |                                                                   | -                 |

| INTP00   | Input           | Interrupt request input                                           | ТО00              |

| INTP01   |                 |                                                                   | -                 |

| INTP02   |                 |                                                                   | TO01              |

| INTP03   |                 |                                                                   | -                 |

| INTP10   | -               |                                                                   | -                 |

| INTP11   |                 |                                                                   | -                 |

| INTP12   |                 |                                                                   | -                 |

| INTP13   | -               |                                                                   | ті                |

| NMI      | Input           | Nonmaskable interrupt request input                               | -                 |

| REFRQ    | Tristate output | Refresh request signal to DRAM                                    | CS0               |

| RAS      | Tristate output | Row address strobe signal to DRAM                                 | -                 |

| LCAS     | Tristate output | Column address strobe signal to lower data in DRAM                | -                 |

| UCAS     | Tristate output | Column address strobe signal to upper data in DRAM                | -                 |

| WE       | Tristate output | Write strobe signal to DRAM                                       | LMWR              |

| DREQ0    | Input           | DMA request signal (channel 0)                                    | P01               |

| DREQ1    | Input           | DMA request signal (channel 1)                                    | P03               |

| DACK0    | Output          | DMA permit signal (channel 0)                                     | P02               |

| DACK1    | Output          | DMA permit signal (channel 1)                                     | P04               |

| TC       | Output          | DMA end signal                                                    | RXD/P09           |

| TO00     | Output          | RPU pulse output                                                  | INTP00            |

| TO01     | -               |                                                                   | INTP02            |

| TCLR     | Input           | External clear or start signal input to timer 0                   | P00               |

| ТІ       | Input           | External count clock input to timer 0                             | INTP13            |

| TXD      | Output          | UART serial data output                                           | UBE/P08           |

| RXD      | Input           | UART serial data input                                            | TC/P09            |

| SCLK     | Input/output    | CSI serial clock input/output                                     | P07               |

| SO       | Output          | CSI serial data output                                            | P06               |

| SI       | Input           | CSI serial data input                                             | P05               |

| WDTOUT   | Output          | WDT overflow signal                                               | BLOCK             |

| IC       | -               | Internal connection (must be connected to GND through a resistor) | -                 |

| Vdd      | -               | Supplies positive power.                                          | -                 |

| GND      | -               | Ground potential                                                  | _                 |

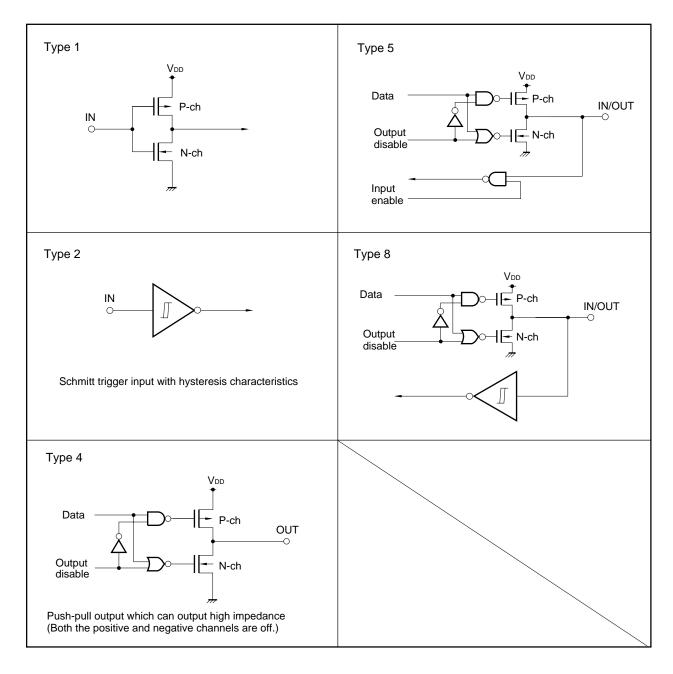

# 1.3 Pin I/O Circuits and Processing of Unused Pins

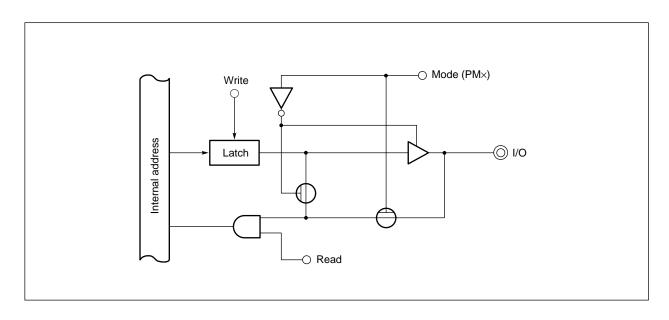

Table 1-1 shows the I/O circuit type of each pin and the processing for unused pins. Figure 1-1 shows the I/O circuit of each type.

| Pin             | I/O circuit type | Recommended connection                                                 |

|-----------------|------------------|------------------------------------------------------------------------|

| P00/TCLR        | 5                | Input status: Individually connected to VDD or GND through a resistor. |

| P01/DREQ0       |                  | Output status: Open                                                    |

| P02/DACK0       |                  |                                                                        |

| P03/DREQ1       |                  |                                                                        |

| P04/DACK1       | _                |                                                                        |

| P05/SI          |                  |                                                                        |

| P06/SO          | -                |                                                                        |

| P07/SCLK        |                  |                                                                        |

| P08/TXD/UBE     | -                |                                                                        |

| P09/RXD/TC      |                  |                                                                        |

| D0-D15          | 5                | Open                                                                   |

| A0-A7, A16-A18  | _                |                                                                        |

| A8-A15, A19-A23 | 4                | Open                                                                   |

| READY           | 1                | Connected to GND through a resistor.                                   |

| HLDRQ           |                  | Connected to VDD through a resistor.                                   |

| HLDAK           | 4                | Open                                                                   |

| BLOCK/WDTOUT    | -                |                                                                        |

| MRD             | _                |                                                                        |

| LMWR/WE         |                  |                                                                        |

| UMWR            |                  |                                                                        |

| IORD            |                  |                                                                        |

| ĪOWR            | _                |                                                                        |

| CLKOUT          |                  |                                                                        |

| CS0/REFRQ       | _                |                                                                        |

| CS1-CS3         |                  |                                                                        |

| INTP00/TO00     | 8                | Connected to VDD through a resistor.                                   |

| INTP01          | 2                | Connected to VDD through a resistor.                                   |

| INTP02/TO01     | 8                | Connected to VDD through a resistor.                                   |

| INTP03          | 2                | Connected to VDD through a resistor.                                   |

| INTP10-INTP12   |                  |                                                                        |

| INTP13/TI       | _                |                                                                        |

| NMI             | -                |                                                                        |

| RESET           |                  |                                                                        |

| RAS             | 4                | Open                                                                   |

| LCAS            |                  |                                                                        |

| UCAS            | _                |                                                                        |

| X2              | -                | 1                                                                      |

| IC              | -                | Connected to GND through a resistor.                                   |

Figure 1-1. Pin I/O Circuits

# 2. INTERNAL UNITS

### 2.1 Bus Interface Unit (BIU)

Controls the pins of the address bus, data bus, and control bus. A bus cycle activated by the CPU or DMAC is controlled via the WCU, DRAMC, and ROMC.

Phase-out/Discontinued

## 2.2 Wait Control Unit (WCU)

Manages the four blocks corresponding to four chip select signals (CS0-CS3). This block generates chip select signals, performs wait control, and selects a bus cycle type.

### 2.3 DRAM Controller (DRAMC)

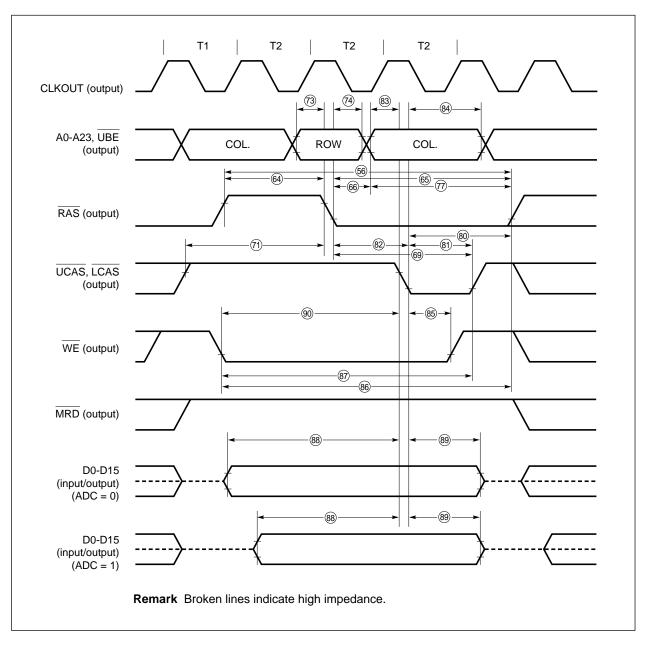

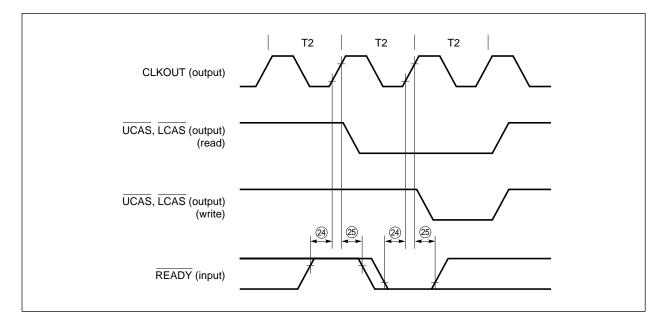

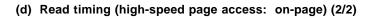

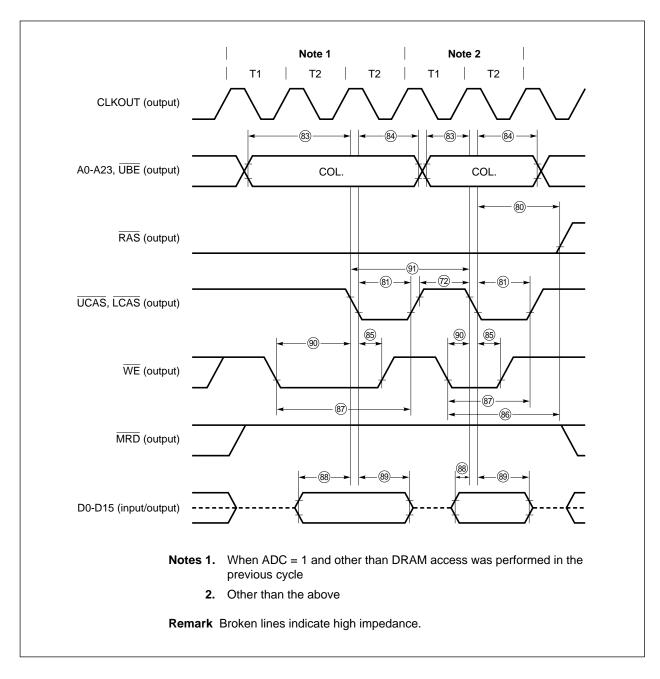

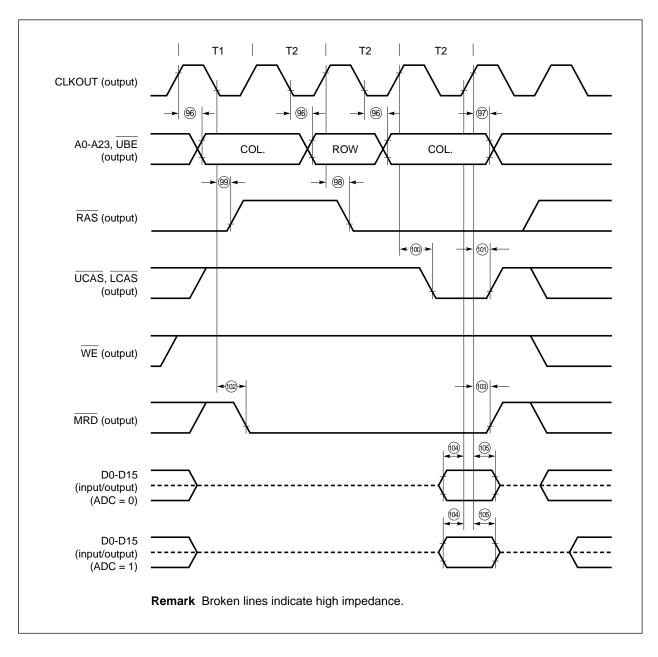

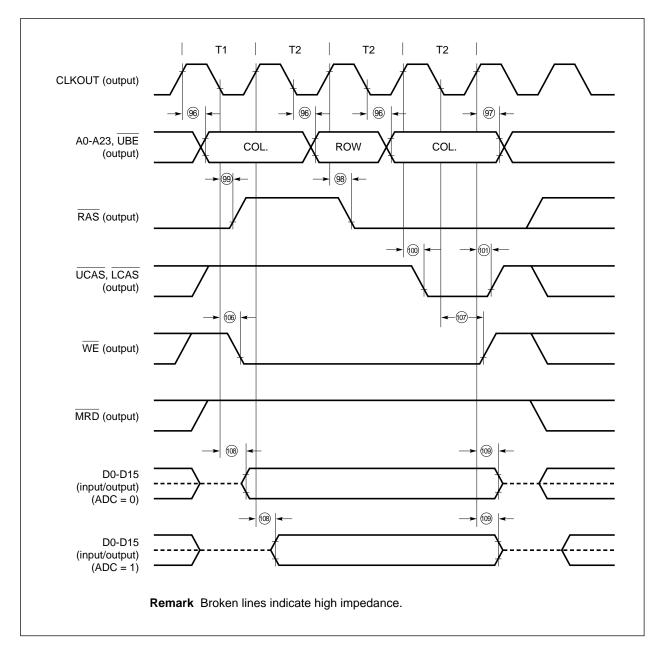

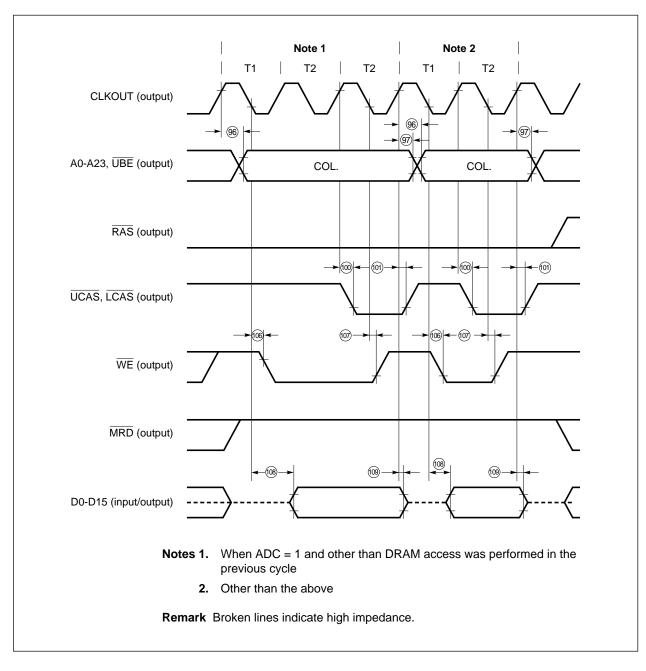

Generates the RAS, UCAS, and LCAS signals (2CAS control) and controls access to DRAM.

This block supports DRAM high-speed page mode. Access to DRAM can be of either of two types, each having a different cycle, normal access (off-page) or high-speed page access (on-page).

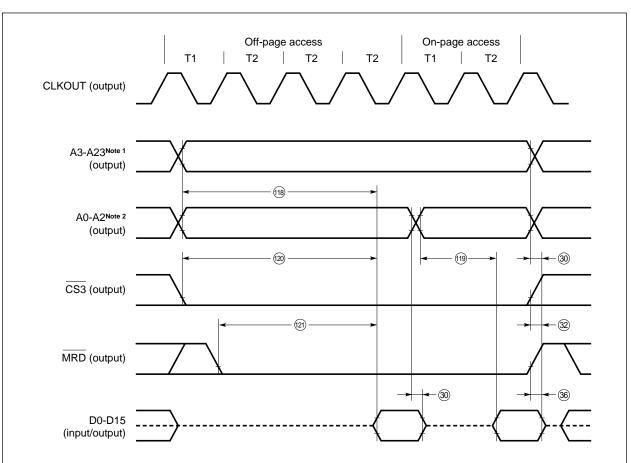

#### 2.4 ROM Controller (ROMC)

Supports access to ROM supporting a page access function.

Performs address comparison relative to the previous bus cycle and performs wait control for normal access (offpage)/page access (on-page). It supports page widths of 8-64 bytes.

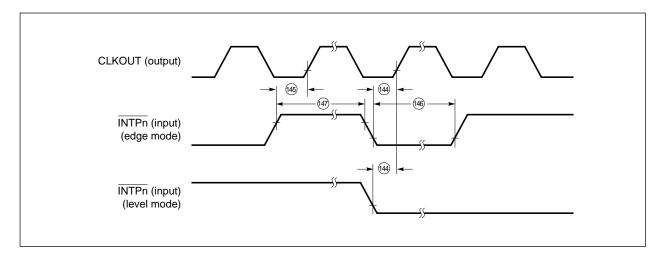

#### 2.5 Interrupt Controller

Handles maskable interrupt requests (INTP00-INTP03, INTP10-INTP13) from both the built-in and external peripheral hardware. Priorities can be specified for these interrupt requests, in units of four groups. It can apply multiple handling control to the interrupt sources.

### 2.6 DMA Controller (DMAC)

Transfers data between memory and I/O, as instructed by the CPU.

There are two address modes, fly-by (1-cycle) transfer and 2-cycle transfer. There are three bus modes, single transfer, single-step transfer, and block transfer.

#### 2.7 Serial Interfaces (UART/CSI)

As serial interfaces, the V821 features an asynchronous serial interface (UART) and a synchronous serial interface (CSI), one channel being assigned to each.

The UART transfers data via pins TXD and RXD.

The CSI transfers data via pins SO, SI, and SCLK.

Either the baud rate generator or the system clock can be selected as the serial clock source.

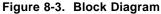

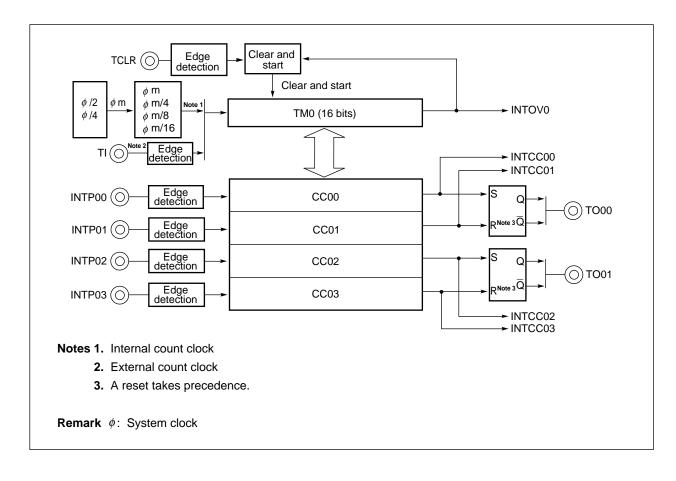

#### 2.8 Real-Time Pulse Unit (RPU)

This block incorporates a 16-bit timer/event counter and a 16-bit interval timer. It can calculate pulse intervals and frequencies and output programmable pulses.

# 2.9 Watchdog Timer (WDT)

This block incorporates an 8-bit watchdog timer to detect a program hanging up or system errors. If the watchdog timer overflows, the WDTOUT pin becomes active.

**Phase-out/Discontinued**

## 2.10 Clock Generator (CG)

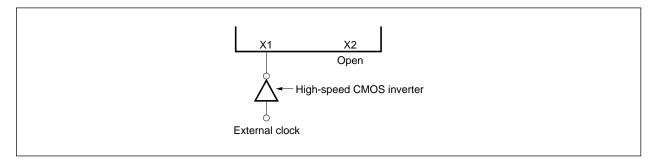

Supplies clock pulses at a frequency five times greater than that of the oscillator connected to pins X1 and X2 (when the built-in PLL is being used) or at half the frequency (when the built-in PLL is not being used) of the operating clock pulses for the CPU. Also, instead of connecting an oscillator, external clock pulses can be input.

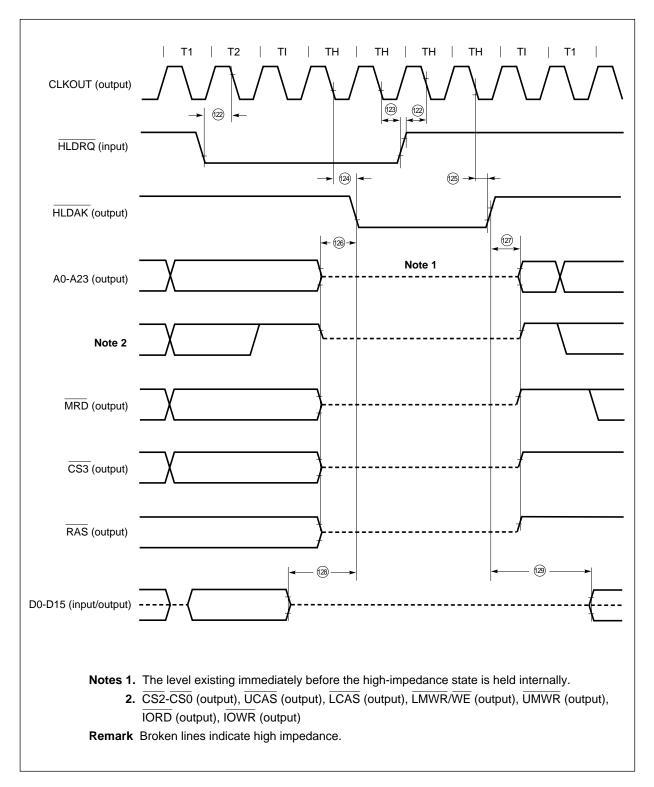

#### 2.11 Bus Arbitration Unit (BAU)

Arbitrates any contention over bus mastership between the bus masters (CPU, DRAMC, DMAC, external bus master). Bus mastership can be switched in each bus cycle and also in the idle state.

#### 2.12 Port

Port 0 provides a total of ten input/output port pins. The pins can be used as either port or control pins.

# 3. CPU FUNCTIONS

The CPU has functions equivalent to those of the V810 microprocessor, designed for built-in control. It offers bit string instructions, floating-point instructions, and quick real-time response.

Phase-out/Discontinued

### 3.1 Features

The features of the CPU are:

- High-performance 32-bit RISC microprocessor

- Built-in 1-Kbyte cache memory

- Pipeline structure of 1-clock pitch

- 16-bit data bus

- 32-bit general-purpose registers: 32

- 4-Gbyte linear address space

- Instructions ideal for various application fields

- Floating-point operation instructions (conforming to the IEEE754 data format)

- Bit string instructions

- High-speed interrupt response

- Debug support functions

### 3.2 Address Space

The V821 supports internal memory and I/O spaces of 4G bytes each. The V821 outputs 24-bit addresses to memory and I/O, such that the addresses range from 0 to  $2^{24}$  - 1.

In byte data, bit 0 is defined as the LSB (Least Significant Bit) and bit 7 as the MSB (Most Significant Bit). In multiplebyte data, bit 0 of the byte data in the lower address is defined as the LSB and bit 7 of the byte data in the upper address as the MSB, unless noted otherwise.

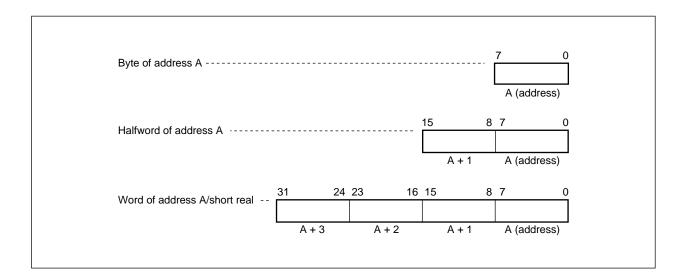

In the case of the V821, 2-byte data is referred to as halfword data, and 4-byte data as word data. In this data sheet, in representations of multiple-byte memory and I/O data, the right address corresponds to the lower address and the left address to the upper address, as shown below.

# 3.2.1 Memory map

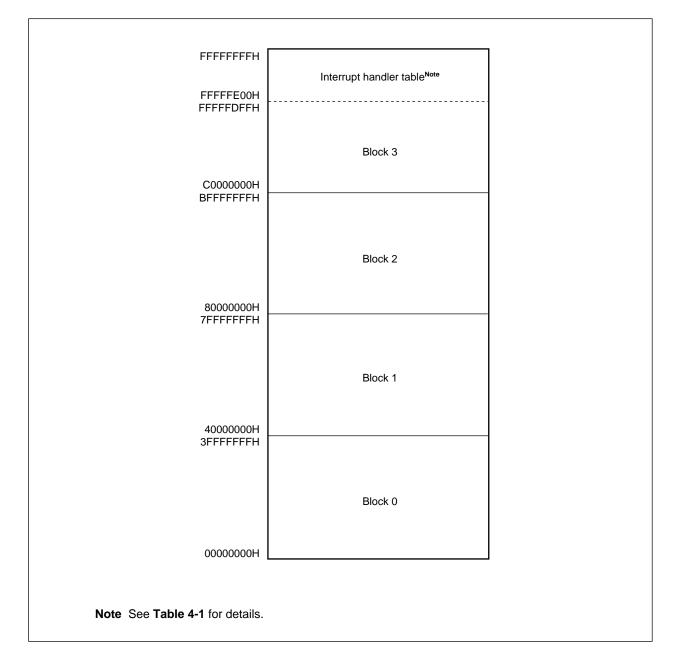

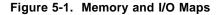

Figure 3-1 shows the memory map of the V821.

The internal 4-Gbyte memory space is divided into blocks of 1G byte each.

Each block has a linear address space of 16M bytes. (The lower 24 bits of a 32-bit address are output.)

# 3.2.2 I/O map

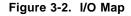

Figure 3-2 shows the I/O map of the V821.

The internal 4-Gbyte memory space is divided into blocks of 1G byte each.

Each block has a linear address space of 16M bytes. (The lower 24 bits of a 32-bit address are output.)

The V821 reserves I/O addresses C0000000H-FFFFFFH (I/O block 3) as an internal I/O space. Each unit is mapped to this internal I/O space.

**Phase-out/Discontinued**

See Section 3.4 for details of the configuration of the internal I/O space.

# μ**PD70741**

# 3.3 CPU Register Set

The registers of the V821 belong to one of two sets, the general-purpose program register set and the dedicated system register set. All registers are 32 bits in wide.

**Phase-out/Discontinued**

# Program register set

| 31  |                                 | 0 |

|-----|---------------------------------|---|

| r0  | Zero Register                   |   |

| r1  | Reserved for Address Generation | 1 |

| r2  | Handler Stack Pointer (hp)      |   |

| r3  | Stack Pointer (sp)              |   |

| r4  | Global Pointer (gp)             |   |

| r5  | Text Pointer (tp)               |   |

| r6  |                                 |   |

| r7  |                                 |   |

| r8  |                                 |   |

| r9  |                                 |   |

| r10 |                                 |   |

| r11 |                                 |   |

| r12 |                                 |   |

| r13 |                                 |   |

| r14 |                                 |   |

| r15 |                                 |   |

| r16 |                                 |   |

| r17 |                                 |   |

| r18 |                                 |   |

| r19 |                                 |   |

| r20 |                                 |   |

| r21 |                                 |   |

| r22 |                                 |   |

| r23 |                                 |   |

| r24 |                                 |   |

| r25 |                                 |   |

| r26 | String Destination Bit Offset   |   |

| r27 | String Source Bit Offset        |   |

| r28 | String Length                   |   |

| r29 | String Destination              |   |

| r30 | String Source                   |   |

| r31 | Link Pointer (lp)               |   |

| 31  |                                 | 0 |

| PC  | Program Counter                 |   |

|       | System register set      |   |

|-------|--------------------------|---|

| 31    |                          | 0 |

| EIPC  | Exception/Interrupt PC   |   |

| EIPSW | Exception/Interrupt PSW  |   |

| 31    |                          | 0 |

| FEPC  | Fatal Error PC           |   |

| FEPSW | Fatal Error PSW          |   |

| 31    |                          | 0 |

| ECR   | Exception Cause Register |   |

| 31    |                          | 0 |

| PSW   | Program Status Word      |   |

| 31    |                          | 0 |

| PIR   | Processor ID Register    |   |

| 31    |                          | 0 |

| TKCW  | Task Control Word        |   |

| 31    |                          | 0 |

| CHCW  | Cache Control Word       |   |

| 31    |                          | 0 |

| ADTRE | Address Trap Register    |   |

### 3.3.1 Program register set

The program register set includes general-purpose registers and a program counter.

## (1) General-purpose registers

The V821 has 32 general-purpose registers, r0-r31. These registers can be used for data or address variables. Registers r0 and r26-r30 are used implicitly with instructions. Caution is therefore necessary when using these registers. Registers r1-r5 and r31 are used implicitly by the assembler and the C compiler. Before using these registers, therefore, the contents of the registers must be saved to prevent their being destroyed. After using the registers, their contents must be restored.

**Phase-out/Discontinued**

| Name   | Use                                       | Explanation                                                                    |

|--------|-------------------------------------------|--------------------------------------------------------------------------------|

| r0     | Zero register                             | Always stores zeros.                                                           |

| r1     | Assembler-reserved register               | Used as a working register to create 32-bit immediate.                         |

| r2     | Handler stack pointer                     | Used as a stack pointer for the handler.                                       |

| r3     | Stack pointer                             | Used to create a stack frame at a function call.                               |

| r4     | Global pointer                            | Used to access a global variable in a data area.                               |

| r5     | Text pointer                              | Points to the top of a text area                                               |

| r6-r25 | -                                         | Register for an address/data variable                                          |

| r26    | String destination start bit offset       | Used to execute a bit string instruction.                                      |

| r27    | String source start bit offset            |                                                                                |

| r28    | String length register                    |                                                                                |

| r29    | String destination start address register |                                                                                |

| r30    | String start address register             |                                                                                |

| r31    | Link pointer                              | Stores a return point address according to the execution of a JAL instruction. |

#### Table 3-1. Program Registers

#### (2) Program counter

Stores the address of an instruction while a program is running. Bit 0 of the program counter (PC) is fixed to 0, thus preventing a branch to an odd address. It is initialized to FFFFFF0H at reset.

# 3.3.2 System register set

System registers are used to control the state of the CPU and store interrupt information.

| No.   | Register name | Use                                                                                            | Explanation                                                                                                                                                                                                                                                                            |

|-------|---------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | EIPC          | Registers for saving the current<br>status upon the occurrence of an<br>exception or interrupt | Retain the contents of PC and PSW if an exception or interrupt occurs. Note, however, that there is only one pair of these registers.                                                                                                                                                  |

| 1     | EIPSW         |                                                                                                | When multiple interrupts are allowed, therefore, the contents of the registers must be saved by the program.                                                                                                                                                                           |

| 2     | FEPC          | Registers for saving the current<br>status upon the occurrence of an                           | Retain the contents of PC and PSW if an<br>NMI or double exception occurs.                                                                                                                                                                                                             |

| 3     | FEPSW         | NMI or double exception                                                                        |                                                                                                                                                                                                                                                                                        |

| 4     | ECR           | Exception source register                                                                      | Stores the source of an exception, maskable interrupt, or<br>NMI. The upper 16 bits of this register are called<br>"FECC" and set to the exception code of an NMI/double<br>exception. The lower 16 bits are called "EICC" and set<br>to the exception code of an exception/interrupt. |

| 5     | PSW           | Program status word                                                                            | The program status word is a set of flags indicating the state of the program (result of executing an instruction) and the state of the CPU.                                                                                                                                           |

| 6     | PIR           | Processor ID register                                                                          | Used to identify a CPU type number.                                                                                                                                                                                                                                                    |

| 7     | TKCW          | Task control word                                                                              | Used to control a floating-point operation.                                                                                                                                                                                                                                            |

| 8-23  | Reserved      |                                                                                                |                                                                                                                                                                                                                                                                                        |

| 24    | CHCW          | Cache control word                                                                             | Used to control the built-in instruction cache.                                                                                                                                                                                                                                        |

| 25    | ADTRE         | Address trap register                                                                          | Stores the address used to detect an address match with PC, and to generate an address trap.                                                                                                                                                                                           |

| 26-31 | Reserved      | •                                                                                              |                                                                                                                                                                                                                                                                                        |

Table 3-2. System Register Numbers

Read and write operations made to these system registers can be performed using the system register load/store instructions (LDSR and STSR) with the system register numbers specified.

# 3.4 Built-in Peripheral I/O Registers

The built-in peripheral I/O registers are allocated to the 256-byte area between C0000000H and C00000FFH in the 1-Gbyte space between C0000000H and FFFFFFFH. Starting from address C0000100H, 256-byte images are created every 256 bytes.

**Phase-out/Discontinued**

The least significant bit of an address is not decoded. Thus, when byte access is attempted to a register at an odd address (2n+1), a register at an even address (2n) is actually performed.

When 16-bit access is attempted to an 8-bit I/O register, the upper eight bits are ignored for write, and become undefined for read.

Table 3-3 lists the built-in peripheral I/O registers.

|          |                                               |              | Manipulat | able bits |                                   |

|----------|-----------------------------------------------|--------------|-----------|-----------|-----------------------------------|

| Address  | Function register name                        | Abbreviation | 8-bits    | 16-bits   | <ul> <li>Initial value</li> </ul> |

| C0000010 | Port mode control register 0                  | PMC0         |           | 0         | 0000H                             |

| C0000012 | Port mode register 0                          | PM0          |           | 0         | 03FFH                             |

| C0000014 | Port register 0                               | P0           |           | 0         | Not defined                       |

| C0000020 | Bus cycle type control register               | BCTC         | 0         |           | 01H                               |

| C0000022 | Programmable wait control register 0          | PWC0         | 0         |           | 77H                               |

| C0000024 | Programmable wait control register 1          | PWC1         | 0         |           | 77H                               |

| C0000026 | Programmable wait control register 2          | PWC2         | 0         |           | 77H                               |

| C0000028 | DRAM configuration register                   | DRC          | 0         |           | 81H                               |

| C000002A | Refresh control register                      | RFC          | 0         |           | 80H                               |

| C000002C | Page-ROM configuration register               | PRC          | 0         |           | 80H                               |

| C0000040 | DMA source address register 0H                | DSA0H        |           | 0         | Not defined                       |

| C0000042 | DMA source address register 0L                | DSA0L        |           | 0         | Not defined                       |

| C0000044 | DMA destination address register 0H           | DDA0H        |           | 0         | Not defined                       |

| C0000046 | DMA destination address register 0L           | DDA0L        |           | 0         | Not defined                       |

| C0000048 | DMA source address register 1H                | DSA1H        |           | 0         | Not defined                       |

| C000004A | DMA source address register 1L                | DSA1L        |           | 0         | Not defined                       |

| C000004C | DMA destination address register 1H           | DDA1H        |           | 0         | Not defined                       |

| C000004E | DMA destination address register 1L           | DDA1L        |           | 0         | Not defined                       |

| C0000050 | DMA byte count register 0                     | DBC0         |           | 0         | Not defined                       |

| C0000052 | DMA byte count register 1                     | DBC1         |           | о         | Not defined                       |

| C0000054 | DMA channel control register 0                | DCHC0        |           | 0         | 0000H                             |

| C0000056 | DMA channel control register 1                | DCHC1        |           | 0         | 0000H                             |

| C0000060 | Timer unit mode register 0                    | TUM0         |           | 0         | 0A00H                             |

| C0000062 | Timer control register 0                      | TMC0         | 0         |           | 00H                               |

| C0000064 | Timer control register 1                      | TMC1         | 0         |           | 00H                               |

| C0000066 | Timer output control register 0               | TOC0         | 0         |           | 03H                               |

| C0000068 | Timer overflow status register                | TOVS         | 0         |           | 00H                               |

| C0000070 | Timer register 0                              | тмо          |           | 0         | 0000H                             |

| C0000072 | Capture/compare register 00                   | CC00         |           | о         | Not defined                       |

| C0000074 | Capture/compare register 01                   | CC01         |           | о         | Not defined                       |

| C0000076 | Capture/compare register 02                   | CC02         |           | о         | Not defined                       |

| C0000078 | Capture/compare register 03                   | CC03         |           | о         | Not defined                       |

| C000007C | Timer register 1                              | TM1          |           | о         | 0000H                             |

| C000007E | Compare register 1                            | CM1          |           | о         | Not defined                       |

| C0000080 | Asynchronous serial interface mode register   | ASIM         | 0         |           | 00H                               |

| C0000082 | Asynchronous serial interface status register | ASIS         | 0         |           | 00H                               |

# Table 3-3. Built-in Peripheral I/O Registers (1/2)

| Address  | Function register name                     | Abbreviation | Manipula | _ Initial value |             |

|----------|--------------------------------------------|--------------|----------|-----------------|-------------|

| Address  | runction register name                     | ADDIEVIALION | 8-bits   | 16-bits         |             |

| C0000084 | Reception buffer                           | RXB          |          | 0               | Not defined |

| C0000086 | Reception buffer L                         | RXBL         | 0        |                 | Not defined |

| C0000088 | Transmission shift register                | TXS          |          | 0               | Not defined |

| C00008A  | Transmission shift register L              | TXSL         | 0        |                 | Not defined |

| C0000090 | Synchronous serial interface mode register | CSIM         | 0        |                 | 00H         |

| C0000092 | Serial I/O shift register                  | SIO          | 0        |                 | Not defined |

| C00000A0 | Baud rate generator register               | BRG          | 0        |                 | Not defined |

| C00000A2 | Baud rate generator prescale mode register | BPRM         | 0        |                 | 00H         |

| C00000B0 | Interrupt group priority register          | IGP          | 0        |                 | E4H         |

| C00000B2 | Interrupt clear register                   | ICR          |          | 0               | 0000H       |

| C00000B4 | Interrupt request register                 | IRR          |          | 0               | 0000H       |

| C00000B6 | Interrupt request mask register            | IMR          |          | 0               | FFFFH       |

| C00000B8 | ICU mode register                          | IMOD         |          | 0               | ААААН       |

| C00000C0 | WDT mode register                          | WDTM         | 0        |                 | 00H         |

| C00000D0 | Standby control register                   | STBC         | 0        |                 | 00H         |

| C00000E0 | Clock control register                     | CGC          | 0        |                 | 03H         |

# Table 3-3. Built-in Peripheral I/O Registers (2/2)

22

## 3.5 Data Types

### 3.5.1 Data types

The data types supported by the V821 are as follows:

- Integer (8, 16, 32 bits)

- Unsigned integer (8, 16, 32 bits)

- Bit string

- Single-precision floating-point data (32 bits)

## (1) Data type and addressing

The V821 uses the little-endian data addressing. In this addressing, if fixed-length data is located in a memory area, the data must be either of the data types shown below.

Phase-out/Discontinued

## (a) Byte

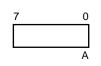

A byte is consecutive 8-bit data whose first-bit address is aligned to a byte boundary. Each bit in a byte is numbered from 0 to 7: LSB (the least significant bit) is bit 0 and MSB (the most significant bit) is bit 7. To access a byte, specify address A. (See diagram below.)

### (b) Halfword

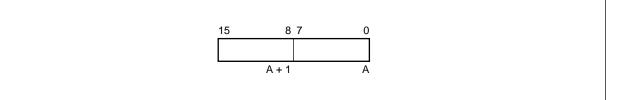

A halfword is consecutive 16-bit (= 2 bytes) data whose first-bit address is aligned to a halfword boundary. Each bit in a halfword is numbered from 0 to 15: LSB (the least significant bit) is bit 0 and MSB (the most significant bit) is bit 15. To access a halfword, specify the address A only (lowest bit must be 0).

### (c) Word/short real

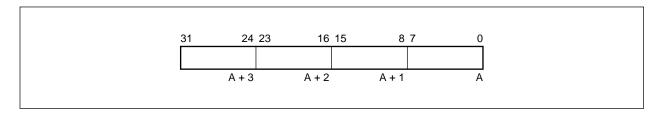

A word, also called short real, is consecutive 32-bit (= 4 bytes) data whose first-bit address is aligned to a word boundary. Each bit in a word is numbered from 0 to 31: LSB (the least significant bit) is bit 0 and MSB (the most significant bit) is bit 31. To access a word or short real, specify the address A only (lower two bits must be 0).

# (2) Integer

In the V821, all integers are expressed in the two's-complement binary notation, and are composed of either 8 bits, 16 bits, or 32 bits. Regardless of the data length, bit 0 is the least significant bit, and higher-numbered bits express higher digits of the integer with the highest bit expressing its sign.

Phase-out/Discontinued

| Data        | a length | Range                            |

|-------------|----------|----------------------------------|

| Byte 8 bits |          | -128 to +127                     |

| Halfword    | 16 bits  | -32 768 to +32 767               |

| Word        | 32 bits  | -2 147 483 648 to +2 147 483 647 |

# (3) Unsigned integer

An unsigned integer is either zero or a positive integer unlike the integer explained in (2) which can be negative as well as zero and positive. Unsigned integers are expressed in the binary notation in the same way as integers, and are either 8 bits, 16 bits, or 32 bits long. Regardless of the data length, the bit assignments are the same as in the case of integers except that unsigned integers do not include a sign bit; the highest bit is also a part of the integer.

| Data     | a length | Range              |

|----------|----------|--------------------|

| Byte     | 8 bits   | 0 to 255           |

| Halfword | 16 bits  | 0 to 65 535        |

| Word     | 32 bits  | 0 to 4 294 967 295 |

# (4) Bit string

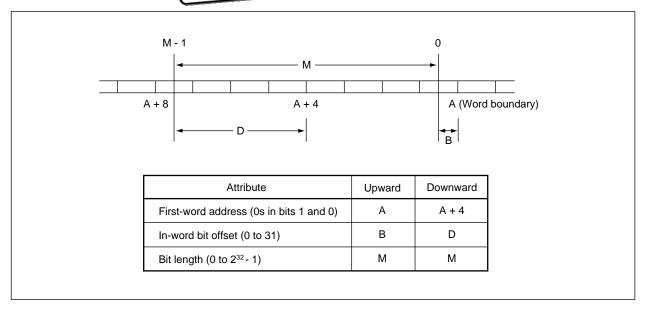

A bit string is a type of data whose bit length is variable from 0 to  $2^{32}$  - 1. To specify a bit-string data, define the following three attributes.

- A : address of the string data's first word (lower two bits must be 0.)

- B : in-word bit offset in the string data (0 to 31)

- M : bit length of the string data (0 to 2<sup>32</sup> 1)

The above three attributes may vary depending on the bit-string data manipulation direction: upward or downward, as shown below. The former is the direction from lower addresses to higher addresses while the latter is the direction from higher to lower addresses.

# (5) Single-precision floating-point data

This data type is 32 bits long and its bit allocation complies with the IEEE single format. A single-precision floatingpoint data consists of 1-bit mantissa sign bit, 8-bit exponent, and 23-bit mantissa. The exponent is offsetexpressed from the bias value - 127, and the mantissa is binary-expressed with the integer part omitted.

| 31 30 23  | 3 22 0        |

|-----------|---------------|

| s exp (8) | mantissa (23) |

# 3.5.2 Data alignment

In the V821, a word data must be aligned to a word boundary (with the lowest two bits of the address fixed to 0s), and a halfword data to a halfword boundary (with the lowest bit of the address fixed to 0). If a data is not aligned as specified, the lowest two bits (in the case of word) or one bit (in the case of halfword) of its address will forcibly be masked with 0s when the data is accessed.

μ**PD70741**

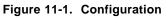

# 3.6 Cache

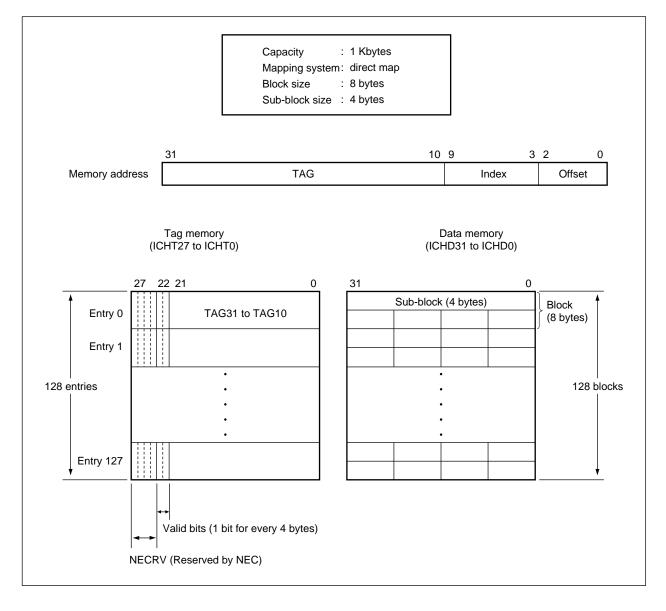

Figure 3-3 shows the instruction cache configuration provided to the V821.

Figure 3-3. Cache Configuration

# 4. INTERRUPT/EXCEPTION HANDLING FUNCTIONS

The V821 features an interrupt controller (ICU) that is dedicated to interrupt handling. The V821 thus supports a powerful interrupt handling function capable of handling interrupt requests issued by up to 16 sources.

Phase-out/Discontinued

As referred to in this manual, an interrupt is an event which occurs independently of program execution while an exception is an event that depends on program execution. In general, an exception assumes a higher priority than an interrupt.

The V821 can handle interrupt requests issued by both built-in peripheral hardware and external devices. Exception handling can be triggered by executing an instruction (TRAP instruction) as well as by the occurrence of an exception (such as an address trap or invalid instruction code).

### 4.1 Features

- Interrupts

- Nonmaskable interrupt : 1 source

- Maskable interrupt : 15 sources

- · Programmable priority control with four groups

- · Multiple interrupt handling control according to priority

- · Mask specification for each maskable interrupt request

- · Valid edge specification for external interrupt requests

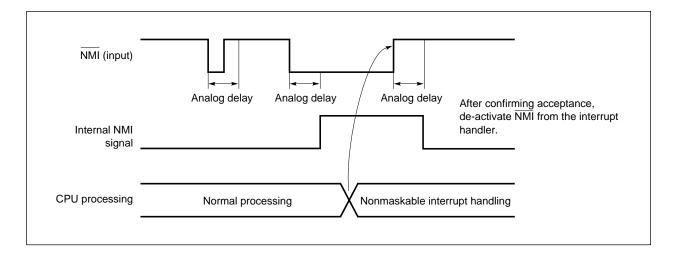

- The noise eliminator introducing an analog delay (60 to 300 ns) is incorporated into the nonmaskable interrupt (NMI) pin.

#### ○ Exceptions

- Software exception: 32 sources

- Exception trap : 10 sources

Table 4-1 lists the interrupt and exception sources.

μ**PD70741**

| Туре             | Category  | Group | Priority         | In      | terrupt/exception sour                        | Exception | Handler | Return    |                  |  |

|------------------|-----------|-------|------------------|---------|-----------------------------------------------|-----------|---------|-----------|------------------|--|

|                  |           |       | in group         | Name    | Source                                        | Unit      | code    | address   | PCNote 1         |  |

| Reset            | Interrupt | -     | -                | RESET   | Reset input                                   | -         | FFF0H   | FFFFFFF0H | Undefined        |  |

| Non-<br>maskable | Interrupt | -     | -                | NMI     | NMI input                                     | -         | FFD0H   | FFFFFD0H  | Next<br>PCNote 2 |  |

| Software         | Exception | -     | -                | TRAP1nH | trap instruction                              | -         | FFBnH   | FFFFFB0H  | Next PC          |  |

| exception        |           | -     | -                | TRAP0nH | trap instruction                              | -         | FFAnH   | FFFFFFA0H | Next PC          |  |

| Exception        | Exception | -     | -                | DP-EX   | Double exception                              | -         | Note 3  | FFFFFFD0H | Current          |  |

| trap             |           | -     | -                | AD-TR   | Address trap                                  | -         | FFC0H   | FFFFFFC0H | PC               |  |

|                  |           | -     | -                | I-OPC   | Invalid instruction code                      | -         | FF90H   | FFFFF90H  |                  |  |

|                  | DIV0 [    |       | Division by zero | -       | FF80H                                         | FFFFFF80H |         |           |                  |  |

|                  |           | -     | -                | FIZ     | Invalid floating-<br>point operation          | -         | FF70H   | FFFFF60H  |                  |  |

|                  |           | -     | -                | FZD     | Floating-point<br>division by zero            | -         | FF68H   | FFFFF60H  |                  |  |

|                  |           | -     | -                | FOV     | Floating-point<br>overflow                    | -         | FF64H   | FFFFF60H  |                  |  |

|                  |           | -     | -                | FUD     | Floating-point<br>underflowNote 4             | -         | FF62H   | FFFFF60H  |                  |  |

|                  |           | -     | -                | FPR     | Floating-point<br>degraded<br>precisionNote 4 | -         | FF61H   | FFFFF60H  |                  |  |

|                  |           | -     | -                | FRO     | Floating-point reserved operand               | -         | FF60H   | FFFFF60H  |                  |  |

Table 4-1. Interrupts (1/2)

Phase-out/Discontinued

Remark n = 0H to FH

Notes 1. PC value saved in EIPC or FEPC at the beginning of interrupt/exception handling

- Return PC = current PC if an interrupt occurred during the execution of an instruction which was stopped by an interrupt (DIV/DIVU, floating-point, and bit string instructions).

- **3.** The exception code for the exception which occurred first is written into in the 16 low-order bits of ECR, while and that for the second exception is written into the 16 high-order bits.

- 4. The V821 is not subject to floating-point underflow or degraded precision exceptions.

| Type Category |                                   | Group | Priority | Priority Interrupt/exception source |                                        |                  | Exception | Handler   | Return   |

|---------------|-----------------------------------|-------|----------|-------------------------------------|----------------------------------------|------------------|-----------|-----------|----------|

|               | in group Name                     |       | Source   | Unit                                | code                                   | address          | PCNote 1  |           |          |

| Maskable      | skable Interrupt GR3 3 RESERVED R |       | Reserved | -                                   | FEF0H                                  | FFFFFEF0H        | Next      |           |          |

|               |                                   |       | 2        | INTOV0                              | Timer 0<br>overflow                    | RPU              | FEE0H     | FFFFEE0H  | PCNote 2 |

|               |                                   |       | 1        | INTSER                              | UART recep-<br>tion error              | UART             | FED0H     | FFFFFED0H |          |

|               |                                   |       | 0        | INTP13                              | INTP13 pin<br>input                    | External         | FEC0H     | FFFFFEC0H |          |

|               |                                   | GR2   | 3        | INTSR                               | UART recep-<br>tion end                | UART             | FEB0H     | FFFFFEB0H |          |

|               |                                   |       | 2        | INTST                               | UART trans-<br>mission end             | UART             | FEA0H     | FFFFFEA0H |          |

|               |                                   |       | 1        | INTCSI                              | CSI transmis-<br>sion/reception<br>end | CSI              | FE90H     | FFFFE90H  |          |

|               |                                   |       | 0        | INTP12                              | INTP12 pin<br>input                    | External         | FE80H     | FFFFE80H  |          |

|               |                                   | GR1   | 3        | INTDMA                              | DMA transfer<br>end                    | DMAC             | FE70H     | FFFFFE70H |          |

|               |                                   |       | 2        | INTP00/<br>INTCC00                  | INTP00 pin<br>input/CC00<br>match      | External/<br>RPU | FE60H     | FFFFE60H  |          |

|               |                                   |       | 1        | INTP01/<br>INTCC01                  | INTP01 pin<br>input/CC01<br>match      | External/<br>RPU | FE50H     | FFFFE50H  |          |

|               |                                   |       | 0        | INTP11                              | INTP11 pin<br>input                    | External         | FE40H     | FFFFFE40H |          |

|               |                                   | GR0   | 3        | INTCM1                              | CM1 match                              | RPU              | FE30H     | FFFFFE30H |          |

|               |                                   |       | 2        | INTP02/<br>INTCC02                  | INTP02 pin<br>input/CC02<br>match      | External/<br>RPU | FE20H     | FFFFE20H  |          |

|               |                                   |       | 1        | INTP03/<br>INTCC03                  | INTP03 pin<br>input/CC03<br>match      | External/<br>RPU | FE10H     | FFFFE10H  |          |

|               |                                   |       | 0        | INTP10                              | INTP10 pin<br>input                    | External         | FE00H     | FFFFE00H  |          |

Notes 1. PC value saved in EIPC or FEPC at the beginning of interrupt/exception handling

- 2. Return PC = current PC if an interrupt occurred during the execution of an instruction which was stopped by an interrupt (DIV/DIVU, floating-point, and bit string instructions).

- Caution The exception code and handler address for a maskable interrupt assume the values existing when the default priority is specified.

# NEC

# 5. WAIT CONTROL FUNCTIONS

The wait control unit (WCU) manages the four blocks corresponding to the four chip select signals, generates the chip select signals, performs wait control, and selects the bus cycle types.

Phase-out/Discontinued

# 5.1 Features

- Able to control up to four blocks in the memory and I/O spaces

- Linear address space of each block: 16 Mbytes

- Wait control

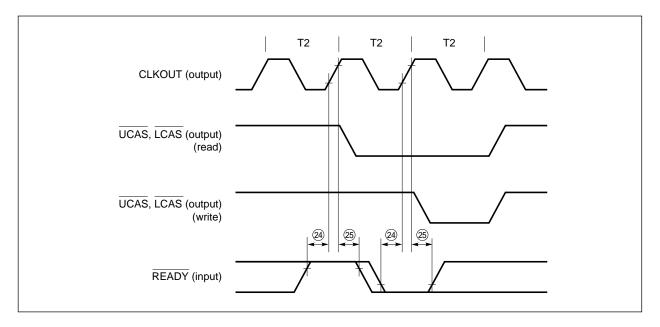

- Automatic insertion of 0-7 waits per block

- Insertion of waits using the READY pin

- Bus cycle selection function

- Page-ROM cycle selectable (address block 3)

- DRAM cycle selectable (address block 0)

| Bus cycle                          |          | Programmable wait | Wait with the READY pin |  |  |  |

|------------------------------------|----------|-------------------|-------------------------|--|--|--|

| SRAM (ROM) cycle (Blocks 0-3)      |          | 0-7 waits         | 0                       |  |  |  |

| DRAM cycle (Block 0)               | off-page | 2 or 3 waits      | 0                       |  |  |  |

|                                    | on-page  | 0 or 1 wait       | ×                       |  |  |  |

| Page-ROM cycle (Block 3)           | off-page | 0-7 waits         | ×                       |  |  |  |

|                                    | on-page  | 0 or 1 wait       | ×                       |  |  |  |

| External I/O cycle (Blocks 0-2)    |          | 0-7 waits         | 0                       |  |  |  |

| Internal I/O cycle (Block 3)       |          | 1 or 2 waits      | ×                       |  |  |  |

| CBR refresh cycle                  |          | Fixed (3 waits)   | 0                       |  |  |  |

| CBR self-refresh cycle             |          | -                 | ×                       |  |  |  |

| Fly-by DMA transfer                |          |                   |                         |  |  |  |

| SRAM (ROM) cycle (Blocks 0         | -3)      | 0-7 waits         | 0                       |  |  |  |

| DRAM cycle (Block 0)               | off-page | 2-7 waits         | 0                       |  |  |  |

|                                    | on-page  | 0-7 waits         | ×                       |  |  |  |

| Page-ROM cycle (Block 3)           | off-page | 0-7 waits         | ×                       |  |  |  |

|                                    | on-page  | 0-7 waits         | ×                       |  |  |  |

| Halt acknowledge cycle             |          | Fixed (0 wait)    | ×                       |  |  |  |

| Machine fault cycle (I/O block 0 w | /rite)   | 0-7 wait          | 0                       |  |  |  |

# Table 5-1. Bus Cycles during Which the Wait Function Is Effective

Remark o: Effective

$\times$ : Not effective

# 6. MEMORY ACCESS CONTROL FUNCTIONS

# 6.1 DRAM Controller (DRAMC)

The DRAM controller (DRAMC) generates the REFRQ, RAS, LCAS, and UCAS signals, and controls access to DRAM. Access to DRAM is achieved by multiplexing the DRAM row and column addresses and outputting them from the address pins.

Phase-out/Discontinued

The microprocessor assumes the connected DRAM to be of  $\times$  4 bits or more, and that it supports high-speed page mode. There are two types of DRAM access cycles, on-page (2 or 3 clock pulses) and off-page (4 or 5 pulses).

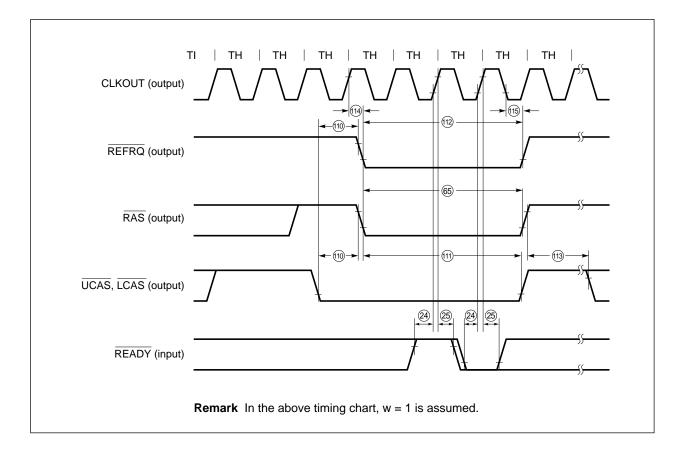

Refresh uses the  $\overline{CAS}$  before  $\overline{RAS}$  method, allowing the user to set any refresh period. In IDLE and STOP modes, CBR self-refresh is performed.

## 6.1.1 Features

- Generates the REFRQ, RAS, LCAS, and UCAS signals.

- Supports DRAM high-speed page mode.

- Address multiplexing function: 8, 9, 10, and 11 bits

- CBR refresh and CBR self-refresh functions

## 6.1.2 Address multiplexing function

In the DRAM cycle, row and column addresses are multiplexed according to the value of the DAW bits of the DRAM configuration register (DRC), then output, as shown in Figure 6-1. In Figure 6-1, a0-a23 are the addresses output from the CPU, while A0-A23 are the address pins of the V821. For example, if DAW = 11, row address a12-a22 and column address a1-a11 are output from address pins (A1-A11).

Table 6-1 lists the relationship between the connectable DRAMs and address multiplexing widths. Depending on the connected DRAM, the DRAM space can be between 128 Kbytes and 8 Mbytes.

| Address pin    | A23→ A16  | A15 | A14 | A13 | A12 | A11 | A10 | A9  | A8  | A7  | A6  | A5  | A4  | A3  | A2  | A1  | A0          |

|----------------|-----------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------------|

| Row address    |           |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |             |

| DAW = 11       | a23 → a16 | a15 | a14 | a13 | a23 | a22 | a21 | a20 | a19 | a18 | a17 | a16 | a15 | a14 | a13 | a12 | a11         |

|                |           |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |             |

| DAW = 10       | a23 → a16 | a15 | a14 | a23 | a22 | a21 | a20 | a19 | a18 | a17 | a16 | a15 | a14 | a13 | a12 | a11 | a10         |

|                |           |     |     |     |     |     |     |     |     | -   |     |     |     |     | -   |     |             |

| DAW = 01       | a23 → a16 | a15 | a23 | a22 | a21 | a20 | a19 | a18 | a17 | a16 | a15 | a14 | a13 | a12 | a11 | a10 | a9          |

|                |           |     | -   |     |     |     |     |     |     |     |     |     |     |     |     |     |             |

| DAW = 00       | a23 → a16 | a23 | a22 | a21 | a20 | a19 | a18 | a17 | a16 | a15 | a14 | a13 | a12 | a11 | a10 | a9  | a8          |

|                |           |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |             |

| Column address | a23       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     | <b>→</b> a0 |

|                |           |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |             |

# Figure 6-1. Output of Row and Column Addresses

| Address multiplexing width | DRAM capacity (in bits) and configuration |           |                        |                        | DRAM space (in bytes) |

|----------------------------|-------------------------------------------|-----------|------------------------|------------------------|-----------------------|

|                            | 256 K                                     | 1 M       | 4 M                    | 16 M                   |                       |

| 8 bits                     | 64 K × 4                                  | -         | -                      | -                      | 128 K                 |

| 9 bits                     | -                                         | 256 K × 4 | 256 K × 16             | -                      | 512 K                 |

|                            | -                                         | -         | 512 K × 8              | -                      | 1 M                   |

| 10 bits                    | -                                         | -         | $1 \text{ M} \times 4$ | 1 M × 16               | 2 M                   |

|                            | -                                         | -         | -                      | 2  M 	imes 8           | 4 M                   |

| 11 bits                    | -                                         | -         | -                      | $4 \text{ M} \times 4$ | 8 M                   |

### Table 6-1. Examples of DRAM and Address Multiplexing Width

### 6.1.3 Refresh function

DRAMC can automatically generate the distributed CBR refresh cycle needed to refresh external DRAM. Whether refresh should be enabled or disabled, and the refresh interval, are specified using the refresh control register (RFC).

While another bus master is occupying a bus, DRAMC cannot forcibly acquire the bus. In this case, in response to a refresh request issued from DRAMC, BAU makes the HLDAK pin inactive to post notification of the occurrence of a refresh request. In this state, by making the HLDRQ pin inactive, the refresh cycle is activated.

## 6.1.4 Self-refresh function

DRAMC generates the CBR self-refresh cycle in IDLE and STOP modes. The self-refresh cycle is activated by setting the SMD bit of the standby control register (STBC) to IDLE or STOP mode and executing the HALT instruction.

To enable DRAM to perform self-refresh, the standard  $\overline{RAS}$  pulse width for DRAM (100  $\mu$ s or greater) must be ensured.

Self-refresh is canceled using the RESET or  $\overline{\text{NMI}}$  pin. The procedure for cancellation by  $\overline{\text{RESET}}$  input is the same as that for normal reset.

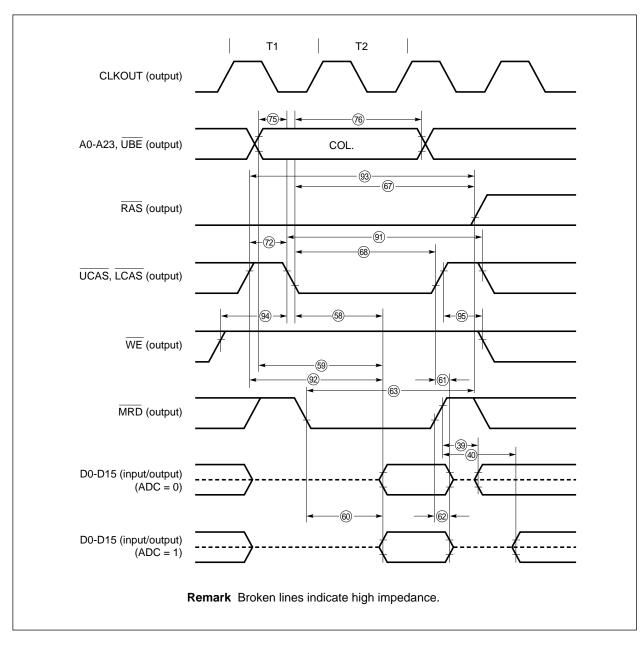

# 6.2 ROM Controller (ROMC)

The ROM controller supports access to ROM having a page access function (page-ROM).

The ROM controller performs address comparison with the previous bus cycle and performs wait control for normal access (off-page)/page access (on-page). It supports page widths of 8-64 bytes.

The page-ROM cycle is supported with address block 3.

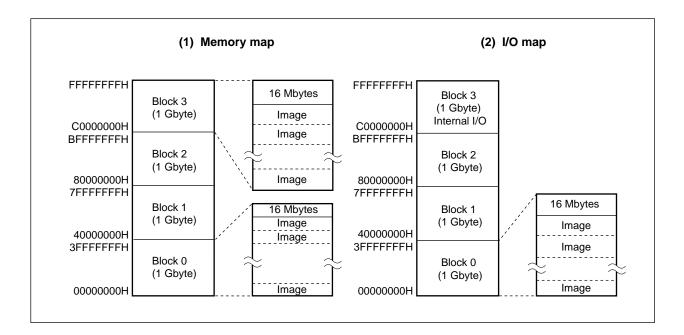

# 6.2.1 on-page/off-page decision

Whether the page-ROM cycle is on-page or off-page is determined by latching the address during the previous cycle and comparing it with the address during the current cycle.

The address(es) (A3-A5) to be masked (not compared) is set using the page-ROM configuration register (PRC), according to the configuration of the connected page-ROM and the number of consecutively readable bits.

# NEC

# Phase-out/Discontinued

### Figure 6-2. on-page/off-page Decision When ROM Having a Page Access Function Is Connected

34

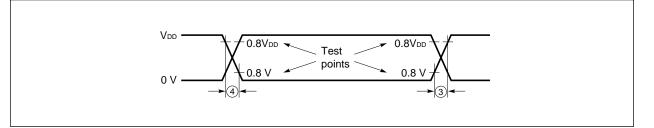

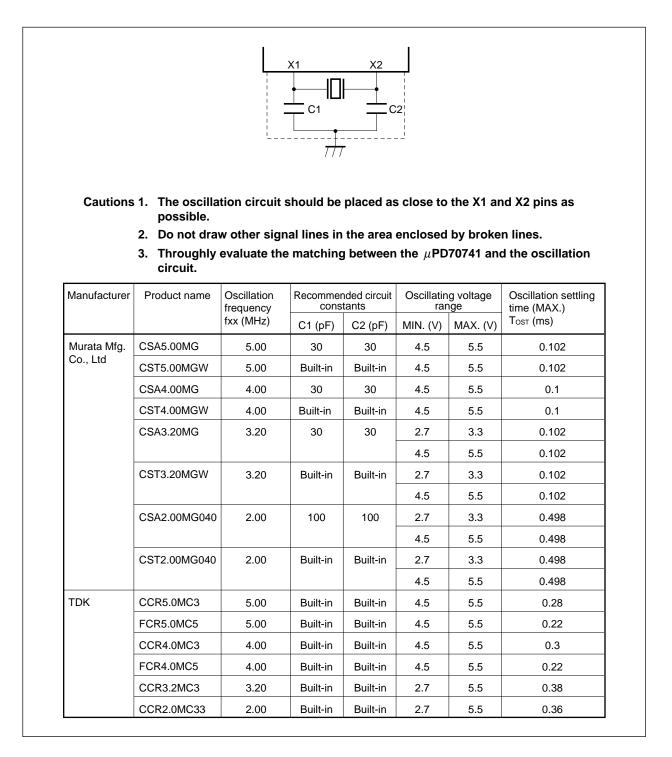

# 7. DMA FUNCTIONS (DMA CONTROLLER)