## High Performance Serial Backplane Transceiver

# Features

- Performs 32-Bit Parallel to Serial and Serial to Parallel Functions

- Serial Data Rates are 2.0Gb/s

- Designed in Conjunction with the VSC880 Serial Crosspoint Switch

- Performs Bit Alignment, Word Alignment and Cell Alignment

- Three Modes of Operation: Distributed Control *Packet Mode*, Central Control *Cell Mode* and *Direct Mode*

- Support for Multicast and Multiple Input Queues

- Supports Priorities, Camp-on and Retransmission Capability in Packet Mode

- Built-in Flow Control Channel in Packet Mode

- Supports Cell Synchronization in Cell Mode

- Interfaces Directly with Industry Standard FIFOs

- Contains Redundant Serial I/Os and Internal Loopback Mode

- 5V Tolerant TTL Inputs

- Single 3.3V Power Supply

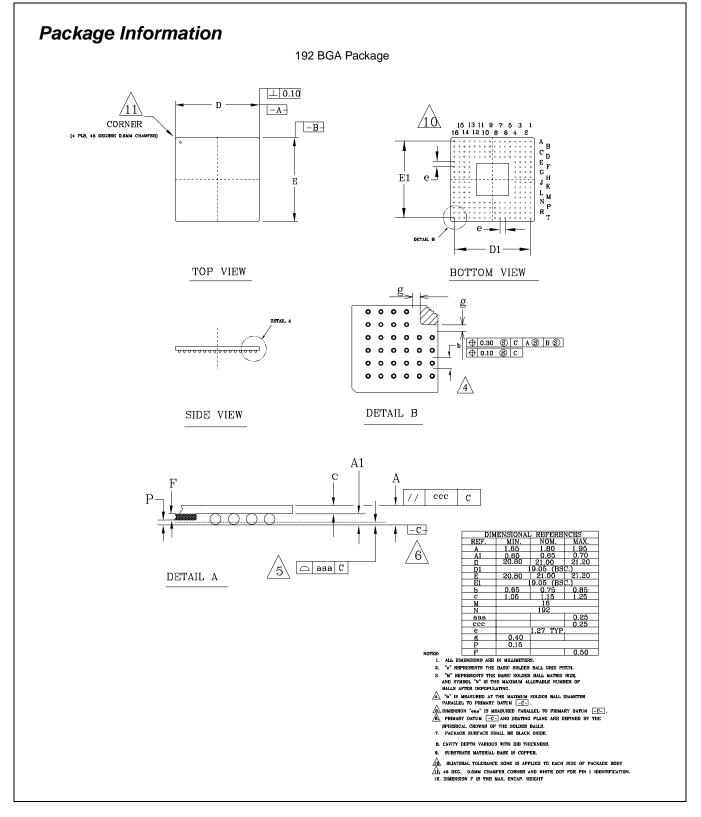

- Available in 192 BGA Package

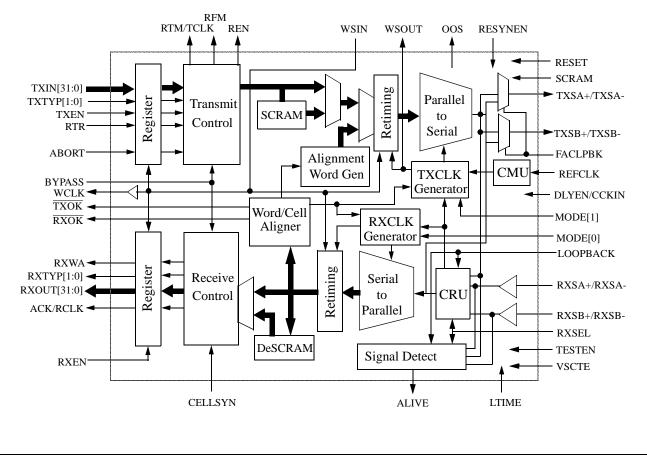

# VSC870 Block Diagram

G52190-0, Rev 4.1 01/05/01

Data Sheet VSC870

# **General Description**

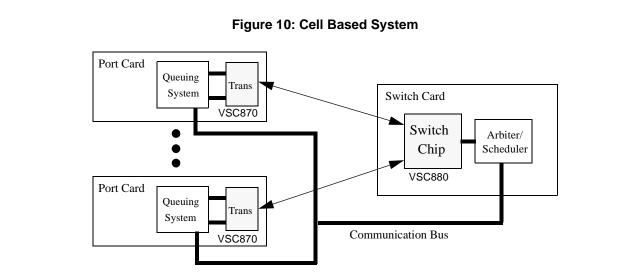

The VSC870 serial backplane transceiver has been designed to operate with the VSC880 serial crosspoint switch to establish a synchronous high performance switching system. The VSC870 can also connect directly to another transceiver to act as a high bandwidth backplane interconnect link. The transmitter converts a 32-bit parallel interface operating at 62.5Mb/s to a 34-bit serial data stream operating a 2.125Gb/s. The receiver converts a 34-bit serial interface operating at 2.125Gb/s to a 32-bit parallel interface operating at 62.5Mb/s. The transceiver performs automatic bit alignment, word alignment and cell alignment to a connected switch chip or another transceiver. The parallel interface has been designed with industry-standard FIFOs in mind to provide such features as automatic packet retransmission, multicast with retransmission, camp-on and support for virtual output queues. These features can also be bypassed to give the user direct control of the serial data stream. In addition, the transceiver and switch chip can operate in a early arbitration mode that greatly improves bandwidth utilization. The transceiver also contains a built-in a flow control channel and redundant serial I/O buffers.

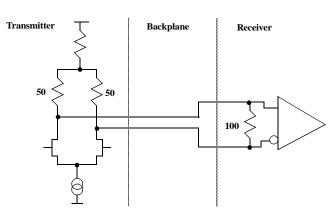

The transceiver and switch chip have been optimized to be used in both distributed-controlled packet-based switching systems (Packet Mode), and centrally-controlled cell-based switching systems (Cell Mode). The transceiver can also be directly connected to another transceiver (Direct Mode) for backplane interconnect applications. The transceiver runs off a 3.3V power supply. The serial I/O buffers contain on-chip termination resistors (See Figure 19).

## High Performance Serial Backplane Transceiver

# Package Pin Descriptions

| Symbol                                           | Name                      | <i>I/O</i>      | Freq<br>Type                                                                                                                                                                                                                                                                                                                                       | Description                                                                                                                                                                                                                                                |

|--------------------------------------------------|---------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXIN[31:0]                                       | Transmit Parallel Data In | Ι               | 62.5Mb/s<br>TTL                                                                                                                                                                                                                                                                                                                                    | 32-bit parallel data input for the transmit side.                                                                                                                                                                                                          |

| TXTYP[1:0]                                       | Transmit Word Type        | Ι               | 62.5Mb/s<br>TTL                                                                                                                                                                                                                                                                                                                                    | If BYPASS is LOW, these signals designate the transmit<br>word type. If BYPASS is HIGH, these signals directly<br>control the overhead bits sent on the serial channel.                                                                                    |

| TXEN                                             | Transmit Enable           | Ι               | 62.5Mb/s<br>TTL                                                                                                                                                                                                                                                                                                                                    | When TXEN is HIGH, TXIN[31:0], TXTYP[1:0] are<br>loaded in to the transceiver on the next WCLK. When<br>TXEN is LOW, the transceiver ignores TXIN[31:0] and<br>TXTYP[1:0] and sends IDLE words at the serial output.                                       |

| RTR Ready To Receive I 6                         |                           | 62.5Mb/s<br>TTL | When RTR is HIGH, the receiving side memory system is<br>ready to receive data. If LOW, it sends a back pressure<br>(flow control) signal to the source port card telling it to<br>stop sending data. In Cell Mode, set RTR LOW to cell<br>synchronize to the external cell clock. If RTR is HIGH,<br>cell clock is recovered from the bit stream. |                                                                                                                                                                                                                                                            |

| RTM/TCLK Retransmit Mode/<br>Transmit Cell Clock |                           | 0               | 62.5Mb/s<br>TTL                                                                                                                                                                                                                                                                                                                                    | In Packet Mode, when BYPASS is LOW, RTM/TCLK is<br>set HIGH at the beginning of each data transmission and<br>set LOW when the data packet has been successfully sent<br>to all outputs. In Cell Mode, a HIGH pulse represents the<br>transmit cell clock. |

| RFM                                              | Read From Mark            | 0               | 62.5Mb/s<br>TTL                                                                                                                                                                                                                                                                                                                                    | When BYPASS is LOW, RFM is set HIGH whenever a retransmission of data is required due to contention for destination ports.                                                                                                                                 |

| ТХОК                                             | Transmit signal OK        | 0               | <1MHz<br>TTL                                                                                                                                                                                                                                                                                                                                       | This signal is LOW if MODE[1] is HIGH and the transceiver is word aligned on the transmit side. After initialization it will go HIGH for one word clock if there is a cell clock error.                                                                    |

| REN                                              | Read Enable               | 0               | 62.5Mb/s<br>TTL                                                                                                                                                                                                                                                                                                                                    | When REN is HIGH, the transceiver is ready to read data at TXIN[31:0] and TXTYP[1:0]. This signal can be forced low by the received flow control signal.                                                                                                   |

| MODE[1:0]                                        | Mode Control              | Ι               | <1MHz<br>TTL                                                                                                                                                                                                                                                                                                                                       | These mode control pins are used to configure link synchronization. See Section 1.5.                                                                                                                                                                       |

| TXSA+/<br>TXSA-                                  | Transmit Serial Output A  | 0               | 2.125Gb/s<br>LVDS                                                                                                                                                                                                                                                                                                                                  | High speed serial differential transmit channel A                                                                                                                                                                                                          |

| TXSB+/<br>TXSB-                                  | Transmit Serial Output B  | 0               | 2.125Gb/s<br>LVDS                                                                                                                                                                                                                                                                                                                                  | High speed serial differential transmit channel B                                                                                                                                                                                                          |

| LOOPBACK                                         | Loop Back                 | Ι               | <1MHz<br>TTL                                                                                                                                                                                                                                                                                                                                       | When LOOPBACK is HIGH, the CRU and signal detector select the serial data output channel as an input.                                                                                                                                                      |

| RXSA+/<br>RXSA-                                  | Receive Serial Input A    | Ι               | 2.125Gb/s<br>LVDS                                                                                                                                                                                                                                                                                                                                  | High speed serial differential receive channel A                                                                                                                                                                                                           |

| RXSB+/<br>RXSB-                                  | Receive Serial Input B    | Ι               | 2.125Gb/s<br>LVDS                                                                                                                                                                                                                                                                                                                                  | High speed serial differential receive channel B                                                                                                                                                                                                           |

G52190-0, Rev 4.1 01/05/01

## High Performance Serial Backplane Transceiver

| Symbol      | Name                                | <i>I/O</i> | Freq<br>Type    | Description                                                                                                                                                                                                                                                                                         |

|-------------|-------------------------------------|------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXSEL       | Receive Input Select                | Ι          | <1MHz<br>TTL    | When RXSEL is LOW and LOOPBACK is LOW, RXSA<br>is selected as the input to the CRU and RXSB is selected<br>as the input to the Signal Detector. When RXSEL is<br>HIGH and LOOPBACK is LOW, RXSB is selected as the<br>input to the CRU and RXSA is selected as the input to the<br>Signal Detector. |

| ALIVE       | Redundant Input Alive               | 0          | <1MHz<br>TTL    | This output is high if at least one edge transition is<br>detected every word clock period on the redundant input<br>serial line.                                                                                                                                                                   |

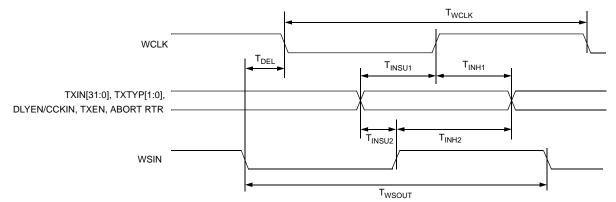

| RXOK        | Receive Signal OK                   | 0          | <1MHz<br>TTL    | This signal goes LOW if the VSC870 is word aligned on<br>the receive side. After initialization, it goes HIGH if there<br>is error in the IDLE words.                                                                                                                                               |

| RXEN        | Receive Enable                      | Ι          | 62.5Mb/s<br>TTL | When RXEN is LOW, the RXOUT[31:0] and RXTYP[1:0] outputs become high impedance.                                                                                                                                                                                                                     |

| RXOUT[31:0] | Receive Parallel Data<br>Out        | 0          | 62.5Mb/s<br>TTL | 32-bit parallel data output for the receive side.                                                                                                                                                                                                                                                   |

| RXTYP[1:0]  | Receive Word Type                   | 0          | 62.5Mb/s<br>TTL | If BYPASS is LOW, these signals tell the received word<br>type. If BYPASS is HIGH, these signals reflect the<br>overhead bits received on the serial channel.                                                                                                                                       |

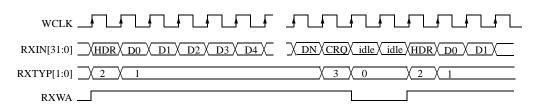

| RXWA        | Receive Word Available              | 0          | 62.5Mb/s<br>TTL | When RXWA is LOW, RXTYP[1:0] and RXOUT[31:0] is an IDLE word.                                                                                                                                                                                                                                       |

| ACK/RCLK    | Acknowledge /<br>Receive Cell Clock | 0          | 62.5Mb/s<br>TTL | In Packet Mode, the ACK signal will be set high if a<br>Connection Request on the transmit side is granted. In<br>Cell mode, a high pulse represents the receive cell clock.                                                                                                                        |

| ABORT       | Connection Request<br>Abort         | Ι          | 62.5Mb/s<br>TTL | When BYPASS is LOW and ABORT is HIGH, the connection request and data transmission process is aborted.                                                                                                                                                                                              |

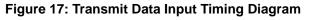

| WSIN        | Word Synch In                       | Ι          | 62.5MHz<br>TTL  | The WSIN signal provides the word clock input and must<br>be driven by a signal frequency locked to the WSOUT<br>signal either from itself or another transceiver.                                                                                                                                  |

| WSOUT       | Word Synch Out                      | 0          | 62.5MHz<br>TTL  | The WSOUT signal is the internally generated word clock<br>and is synchronized to the transmit word clock.                                                                                                                                                                                          |

| RESYNEN     | Resync Enable                       | Ι          | <1MHz<br>TTL    | If RESYNEN is HIGH and the transceiver detects a link error, it will start the Link Initialization process.                                                                                                                                                                                         |

| OOS         | Out Of Sync                         | 0          | <1MHz<br>TTL    | If OOS is HIGH, the transceiver is in the link initialization process. It is LOW during normal operation.                                                                                                                                                                                           |

| SCRAM       | Scramble Enable                     | Ι          | <1MHz<br>TTL    | If SCRAM is HIGH, data words will be scrambled and descrambled.                                                                                                                                                                                                                                     |

| BYPASS      | Bypass Mode                         | Ι          | <1MHz<br>TTL    | BYPASS is set HIGH for direct control and monitoring of<br>the overhead bits in the serial data streams as in cell mode<br>and direct mode. This also disables the transceiver Packet<br>Mode functions.                                                                                            |

| CELLSYN     | Cell Synchronization<br>Enable      | Ι          | <1MHz<br>TTL    | CELLSYN is set HIGH to allow cell synchronization during link initialization.                                                                                                                                                                                                                       |

Page 4

# High Performance Serial Backplane Transceiver

| Symbol          | Name                             | <i>I/O</i> | Freq<br>Type    | Description                                                                                                                                                                                 |

|-----------------|----------------------------------|------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DLYEN/<br>CCKIN | Delay Enable/Cell Clock<br>Input | Ι          | <1MHz<br>TTL    | If BYPASS is LOW, this signal can be set HIGH to enable<br>REN delay mode. In Cell Mode, DLYEN/CCKIN can be<br>used as an input for cell clock alignment.                                   |

| FACLPBK         | Facility Loopback                | Ι          | <1MHz<br>TTL    | When this signal is HIGH, the serial input is looped back to the serial output. It should be normally set LOW.                                                                              |

| WCLK            | Word Clock                       | 0          | 62.5MHz<br>TTL  | The word clock is a delayed version of the WSIN signal.                                                                                                                                     |

| REFCLK          | Local Reference Clock            | I          | 62.5MHz<br>TTL  | A 62.5 MHz local reference clock that is used to keep the CRU close to the incoming bit clock frequency before the alignment process begins. Is also used as a reference clock for the CMU. |

| RESET           | Reset                            | Ι          | <1MHz<br>TTL    | Global chip reset (active HIGH).                                                                                                                                                            |

| TESTEN          | Scan Test Enable                 | Ι          | <1MHz<br>TTL    | When TESTEN is HIGH, the REFCLK is used in place<br>of the bit clock for low speed testing. Used for ATE<br>testing only. Set to logic LOW during normal operation.                         |

| LTIME           | Loop Time Mode                   | Ι          | 62.5Mb/s<br>TTL | LTIME is set HIGH to use the recovered bit clock for the transmit side.                                                                                                                     |

| VSCTE           | NOR Chain Test Enable            | Ι          | <1MHz<br>TTL    | Used for ATE testing of the parametric NOR chain in the I/O frame. Set to logic LOW during normal operation.                                                                                |

| VDDA            | CMU Power Supply                 | Р          | 3.3V            | Clean power supply for CMU                                                                                                                                                                  |

| VSSA            | CMU Ground                       | Р          | 0V              | Clean ground for CMU                                                                                                                                                                        |

Data Sheet VSC870

# Functional Description

The VSC870 transceiver can be used in one of the three operation modes: Packet Mode, Cell Mode and Direct Mode. In Packet mode, the VSC870 is intended to work in conjunction with the VSC880 switch chip to provide a self routing switching system and to support variable length data packets. In Cell Mode, the transceiver works in conjunction with the VSC880 switch chip to provide a cell synchronized switching system. In this mode, it can support only fixed length data packets (cells), and routing decisions are carried out in a user defined controller chip and synchronized to a cell clock. In Direct mode, the VSC870 can connect to other transceivers to provide a high bandwidth serial backplane data link.

The following sections give a detailed description of generic features which are provided in all three modes, followed by the operation of the transceiver in each mode. Most of the discussions in this data sheet include some of the switch chip functions (see the VSC880 data sheet).

# 1.0 Common Features

#### 1.1 Synchronization

#### 1.1.1 Link Characteristic

The serial link is used to connect the transceivers to the switch chip or to other transceivers. These links operate at 2.125Gb/s and are initialized simultaneously at power up, or separately when a link error occurs. A link is first bit synchronized, then word synchronized and, if CELLSYN is HIGH, cell synchronized. In Packet or Cell mode, the switch acts as the master, generating the bit clock along with the word and cell boundary information. The transceivers act as slaves, recovering the bit clock, word clock and cell clock. In Direct mode, the transceivers can be configured as either masters or slaves using the MODE[1:0] signals, with the masters generating the bit and word clocks. The transceiver also contains redundant serial inputs and outputs which can be used with a redundant switch chip or redundant transceiver.

#### 1.1.2 Data Scrambling

A 15% edge transition density must be guaranteed on the serial data links for the CRU to work properly. All command words and connection request words contain this required density. In order to get this density on data words, scrambling is employed. If SCRAM is set HIGH, the 32-bit data words are scrambled in the transmitter and de-scrambled in the receiver with a  $(1+X^1+X^7)$  pattern to guarantee high transition density. This is the same pattern used in SONET scrambling. In all operating modes, data words are recognized by TXTYP[1:0] = 01 or 10. Words such as the connection request and header word in Packet Mode or cell clock in Cell Mode or the IDLE word in Direct Mode are used to initiate the scrambling pattern. If the user can guarantee edge densities greater than or equal to 15%, scrambling can be turned off by setting SCRAM = LOW.

#### 1.1.3 Bit Synchronization

In Packet and Cell Mode, the switch acts as the source of the bit clock. It multiplies the local 62.5MHz word clock by 34 to generate a 2.125GHz clock, and uses this clock to serialize the 32-bit data word and 2 overhead bits.

## High Performance Serial Backplane Transceiver

The transceiver receives and feeds this serial data stream to a digital CRU to recover the bit clock and deserialize the data stream to a 32 bit word plus 2 overhead bits at 62.5MHz. The transceiver also uses this recovered clock to serialize its transmit data words that are sent to the switch. In this way, the switch and all the transceivers are frequency-locked to one clock source which is provided by the word clock on the switch card. The transceiver provides its own CMU which multiplies a local REFCLK by 34. The output of the CMU helps the CRU obtain lock and provides the clock source for the transceiver in loopback mode. This local REFCLK must be within 100ppm of the switch chip reference clock frequency. In Direct Mode, the master transceiver uses the CMU to provide a clock for the transmit data. The slave receivers recover the clock from the serial bit streams.

#### 1.1.4 Word Synchronization

During power up or at reset, the transceiver can initiate the word synchronization process. First, the transceiver sends reset patterns to the switch (or the master transceiver in Direct mode) to request that the switch starts the initialization process. The switch, upon receiving this request, will send out special ALIGN words. The transceiver receives this serial data stream from the switch, and uses the RXCLK Generator to adjust the receive word clock boundary one bit at a time until the Word/Cell Aligner detects proper alignment. Upon detecting the correct word alignment, the  $\overrightarrow{RXOK}$  signal is set LOW and the word alignment process is started on the transmit side. In this process, the transceiver continuously sends ALIGN words to the switch using the Alignment Word Generator. The switch uses its own word clock to detect this ALIGN word. If the transmitters word is not aligned to the switch chip word clock when it arrives at the switch, the switch chip continues to send out ALIGN words. After receiving every 32 ALIGN words from the switch chip, the transceiver changes its transmit word boundary by one bit position using the TXCLK Generator and then repeats the process (this limits the distance from the transceiver to the switch to less then 180nS one way). If the switch detects this ALIGN word correctly, it sends IDLE words to the transceiver to signal that the transmitter has now word synchronized with the switch. When the transceiver detects these IDLE words, the signal TXOK goes LOW and the parallel data signals TXIN[31:0], TXTYP[1:0], RXOUT[31:0] and RXTYP[1:0] are then phase aligned to the word clock (WSOUT).

The transmit word clock is output on the pin WSOUT. If a single transceiver is used on a port card, WSOUT must be tied directly to WSIN. The signal WSIN is the clock input for all of the transceiver parallel logic and provides the word clock output (WCLK). Retiming blocks are used in the transceiver to span the phase boundary between WSIN and the transmit word clock and the receive word clock. If two or more transceivers are used in parallel on a port card in order to increase bandwidth, each will have its own transmit word clock. Since these word clocks are derived from the same source on the switch card, they will have the same frequency but a phase difference of up to 8nS. This phase difference (skew) depends on the I/O delay of the switch and transceiver and the serial data line delay between these chips. To properly phase align all transceiver parallel interfaces, one transceiver acts as the master, providing its WSOUT signal not only to its own WSIN, but the WSIN on all other transceivers on the port card (see Application Note 32: Design Guide for a Cell Based Switch with Central Control). This means that the parallel logic blocks on all transceivers are clocked by the same source derived from the transmit word clock of the master transceiver. In this way, skew between the parallel interfaces on all transceivers is minimized. Other logic on the port card can be clocked using WSOUT of the master transceiver, or the WCLK output of any transceiver which is a delayed version of WSOUT. A phase shifted word clock can also be used to drive WSIN provided that it is frequency locked to the WSOUT signal. In this way, both the receive and transmit parallel interfaces can be phase aligned to this word clock.

G52190-0, Rev 4.1 01/05/01

Data Sheet VSC870

#### 1.1.5 Cell Synchronization

If the CELLSYN signal is set HIGH, after the word synchronization process, the transceiver starts the cell synchronization process. In this process, the transceiver detects the received cell clock sent from the switch. The cell clock is embedded in the command words with overhead bits '00' as described in section 3.2. The received cell clock is output on ACK/RCLK. The switch chip connects each port to itself after link initialization. By sending a special ALIGN word to itself, the transceiver can adjust the transmit cell clock (RTM/TCLK) until it is properly phase shifted relative to the received cell clock. If cells are sent from the transceiver aligned to this transmit cell clock, they will arrive at the switch aligned to the master cell clock which is originated at the switch. The received cell clock on the serial link is therefore shifted by N word clocks to create a phase shifted cell clock which is output on RTM/TCLK. An on-chip counter provides this phase shift, with the frequency and phase shift determined during the cell synchronization process. For this alignment process to work, the minimum cell size is 13 words (52 bytes).

#### 1.1.6 Cell Synchronization for Multiple Transceivers

If two or more transceivers are used in parallel on a port card in order to increase bandwidth, skew between signals could cause the transmit cell clock (RTM/TCLK) in one or more transceivers to be shifted in phase by one word clock relative to the other transceivers. To adjust out this offset, a marker cell clock can be sent to both transceivers. This is done by sending the signal RTM/TCLK from the master transceiver to the DLYEN/CCKIN input on the slave transceivers. At the end of the cell synchronization process, the pipeline offset is adjusted out using this marker cell clock. See Application Note 32 for more details.

#### 1.1.7 Link Error Detection

Receive errors are declared if the transceiver detects a bit pattern error in an IDLE word in the received serial data by generating a HIGH pulse on  $\overline{\text{RXOK}}$ . In cell mode, if an IDLE word is received at the end of the cell period and it does not contain the embedded cell clock, or it receives an embedded cell clock at the wrong time, it generates a HIGH pulse on  $\overline{\text{TXOK}}$ . This error is stored internally and if the RESYNEN goes HIGH, the VSC870 will start the link initialization process. The  $\overline{\text{RXOK}}$  and  $\overline{\text{TXOK}}$  signals can therefore be tied to the RESYNEN signal to start the link initialization process immediately, or the user logic can monitor the  $\overline{\text{RXOK}}$  and  $\overline{\text{TXOK}}$  signals when OOS is LOW and assert RESYNEN only after an error threshold has been reached. It is up to the user to make sure enough IDLE words are used to detect errors during system operation. The switch can initiate the initialization process by forcing zeroes on the serial link. If the transceiver receives 4 consecutive words of all zeroes, it will immediately start the initialization process.

#### 1.2 Data Encoding Format

To provide self routing and signalling functions, the transceiver and switch require different data types to differentiate between data words, connection request words or command words. Depending on the mode that the transceiver is in, different data types are recognized at the transceiver parallel interface. These word types are encoded using the RXTYP[1:0] or TXTYP[1:0] bits. At the transceiver to switch serial interface, these data types are encoded in the two overhead bits (B[1:0]). Sections 2.2, 3.2 and 4.2 describe these data types in more detail.

The format for data words and command words the transceiver parallel interfaces and on the serial data lines between the transceiver and switch chip are described in the following sections. The format for the connection request word is described later in the Packet Mode section.

# High Performance Serial Backplane Transceiver

## 1.2.1 Data Word Format at Transceiver Parallel Interface

Data words contain a 32 bit user defined payload which is sent between the transmitting and receiving port cards as shown below. The RXTYP[1:0] and TXTYP[1:0] data word encoding format for different modes are described in later sections.

| 31 30 29 28 | 27 26 25 24  | 23 22 21 20 | 19 18 17 16 | 15 14 13 12 | 11 10 09 08 | 07 06 05 04 | 03 02 01 00 |  |  |  |  |

|-------------|--------------|-------------|-------------|-------------|-------------|-------------|-------------|--|--|--|--|

| DDDD        | DDDD         | DDDD        | DDDD        | DDDD        | DDDD        | DDDD        | DDDD        |  |  |  |  |

| 31 30 29 28 | 27 26 25 24  | 23 22 21 20 | 19 18 17 16 | 15 14 13 12 | 11 10 09 08 | 07 06 05 04 | 03 02 01 00 |  |  |  |  |

|             | Data Payload |             |             |             |             |             |             |  |  |  |  |

Where:

D[31:0]32 bit data payload

#### 1.2.2 Data Word Format on the Serial Data Lines

The data word format as seen at the serial output of the transceiver or switch chip is shown below. Two overhead bits are added by the transceiver or switch chip to designate a data word to the receiving switch chip or transceiver. The serial data is transmitted with the MSB first (B1, B0, D31, D30... D00).

| 33 32      | 31 30 29 28            | 27 26 25 24            | 23 22 21 20            | 19 18 17 16            | 15 14 13 12            | 11 10 09 08            | 07 06 05 04            | 03 02 01 00            |  |  |  |  |

|------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|--|--|--|--|

| B B<br>1 0 | D D D D<br>31 30 29 28 | D D D D<br>27 26 25 24 | D D D D<br>23 22 21 20 | D D D D<br>19 18 17 16 | D D D D<br>15 14 13 12 | D D D D<br>11 10 09 08 | D D D D<br>07 06 05 04 | D D D D<br>03 02 01 00 |  |  |  |  |

|            |                        | Data Payload           |                        |                        |                        |                        |                        |                        |  |  |  |  |

Where:

B[1:0]If BYPASS=0,01=Flow control channel,

10=Flow control channel,

11=Acknowledge from switch chip or data header to switch chip

If BYPASS = 1, RXTYP[1:0]=B[1:0]=TXTYP[1:0]

D[31:0]32 bit data payload

#### 1.2.3 Command Word Format at Transceiver Parallel Interface

There are several command words that are used for sending information to the switch chip or a receiving port card. The command word format at the transceiver parallel interface is shown below. IDLE words are discussed in the next sections. A delay enable value can also be programmed into the transceiver for Packet Mode using this command word.

| 31 30 29 | 28 27 26 25 24 | 23 22 21 20            | 19 18 17 16            | 15 14 13 12            | 11 10 09 08            | 07 06 05 04 | 03 02 01 00 |

|----------|----------------|------------------------|------------------------|------------------------|------------------------|-------------|-------------|

| XXX      |                | D D D D<br>15 14 13 12 | D D D D<br>11 10 09 08 | D D D D<br>07 06 05 04 | D D D D<br>03 02 01 00 | XXXX        | XXXX        |

|          | Command        |                        |                        |                        |                        |             |             |

Where:

C[4:0]Command type:

00XXX=Link Control (00111=IDLE word)

01XX0=Command word for transceiver (01000=set DLYEN/CCKIN value) 10XX0=Command word for switch

G52190-0, Rev 4.1 01/05/01

Data Sheet VSC870

11XX0=Command word for receiving port card D[15:0]Optional data payload: Default=101010101010100 IDLE Word from switch=Output(s) this port is connected to; D[15] is equal to port 0, and D[0] is equal to port 15. If C[4:0]=01000, D[3:0]=DLYEN/CCKIN value

#### 1.2.4 Command Word Format on the Serial Data Lines

The command word format as seen at the serial output of the transceiver or switch chip is shown below. Two overhead bits are added by the transceiver or switch to designate a command word (00) to the receiving switch chip or transceiver. The serial data is transmitted with the MSB first. In Packet Mode, the IDLE word from the switch always returns the current output connections for the port.

| 3 32 | 31 30 29     | 28 27 26 25 24              | 23 22 21 20            | 19 18 17 16            | 15 14 13 12         | 11 10 09 08            | 07 06 05 04 | 03 02 01 00 |

|------|--------------|-----------------------------|------------------------|------------------------|---------------------|------------------------|-------------|-------------|

| 0    | 1 B B<br>1 0 | C C C C C<br>04 03 02 01 00 | D D D D<br>15 14 13 12 | D D D D<br>11 10 09 08 | DDDD<br>07 06 05 04 | D D D D<br>03 02 01 00 | 1010        | 1010        |

|      |              | Command                     | Data                   |                        |                     |                        |             |             |

Where:

B[1:0]00=Undefined (during normal operation) or alignment word

01=Flow control channel,

10=Flow control channel,

11=Acknowledge (from switch chip only) or link initialization reset or cell clock in cell mode C[4:0]Command type:

00XXX=Link Control (00000=ALIGN word, 00111=IDLE word)

01XX0=Command word for transceiver (01000=set DLYEN/CCKIN value)

10XX0=Command word for switch

11XX0=Command word for receiving port card)

D[15:0]Optional data payload:

Default=1010101010101010

IDLE Word from switch=Output(s) this port is connected to;

D[15] is equal to port 0, and D[0] is equal to port 15.

If C[4:0]=01000, D[3:0]=DLYEN/CCKIN value

#### 1.2.5 IDLE Words

IDLE words are the default word used on the serial channel when none of the other word types are present. In most cases, these words are automatically generated by the transceiver or switch chip. In Packet Mode, IDLE words are inserted between packets and the IDLE word from the switch always returns the current output connections for the port that is receiving the IDLEs. If the user does not have data to send, IDLE words can be loaded into the parallel interface, or the TXEN signal can be set LOW which forces the transceiver to send IDLEs to the switch chip. In cell mode, IDLEs will be transmitted from the switch chip if the Force IDLE bit is set in the switch chip (see the VSC880 data sheet). See sections 2.0 and 3.0 for more details. IDLE words are also used to detect link error conditions. If the transceiver detects and IDLE word, it uses a bit mask to verify the proper bit pattern within the word.

High Performance Serial Backplane Transceiver

#### 1.3 Loopback Mode

The VSC870 supports two loopback functions at the serial interface. If the LOOPBACK signal is set HIGH, the serial transmit data is looped back to the CRU on the serial receiving side. The transmitted serial data is generated using the CMU clock. This mode can be used to test the high speed circuitry (except for the serial input/output buffers) using the low speed parallel interface. The serial data can also be looped back through the I/O of the switch chip or other connected transceiver if the other device is in FACLPBK mode (see the table below). If FACLPBK is set HIGH, the receive serial data is recovered using the CRU and looped back to the serial output.

#### 1.4 Redundancy

There are two serial output buffers and two serial input buffers on the transceiver. These can be used to connect to redundant switch chips or redundant transceivers. The serial inputs are also connected to a signal detector circuit which is used to determine if there is an average of one transition for every 34 bits of data. If there is, the signal ALIVE remains HIGH. Which ever input is not connected to the CRU is connected to the signal detector. An example system would have the redundant serial output connected to a redundant switch chip. This switch chip has the LPBK bits in the status and control registers set HIGH such that the transceiver output signal (which is looped through the switch input/output buffer) comes back to itself at the redundant serial input buffer (see Application Note 35). If the primary switch chip fails, and the ALIVE signal is HIGH on all transceivers, the redundant switch chip can be activated in its place after it goes through the link initialization process. The signal RXSEL on the transceiver is used to select the redundant input buffer.

#### 1.5 Operating Modes

The following table summarizes the operating modes for the transceiver that have been discussed in the previous sections. The pin LTIME selects the source of the bit clock for the transmit side. LTIME is normally set HIGH. In this case, the received bit clock is use for the transmit bit clock. If LTIME is set LOW, the transceivers CMU is used as the source of the transmit bit clock. This signal must be set LOW to test the transceiver in loopback mode or when used as a master transceiver in Direct Mode (see section 4.0).

|              |       | Control Sig | nal Name |            |             |                                               |  |  |  |

|--------------|-------|-------------|----------|------------|-------------|-----------------------------------------------|--|--|--|

| LOOP<br>BACK | LTIME | MODE[1]     | MODE[0]  | BY<br>PASS | CELL<br>SYN | Description of Operation                      |  |  |  |

| 0            | 1     | 1           | 1        | 0          | 0           | Normal Packet Mode operation                  |  |  |  |

| 0            | 1     | 1           | 1        | 1          | 1           | Normal Cell Mode operation                    |  |  |  |

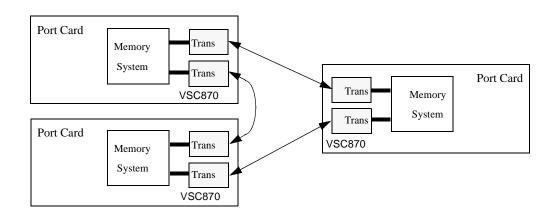

| 0            | 0     | 0           | 1        | 1          | 0           | Master transceiver in Direct Mode (figure 13) |  |  |  |

| 0            | 1     | 0           | 1        | 1          | 0           | Slave transceiver in Direct Mode (figure 13)  |  |  |  |

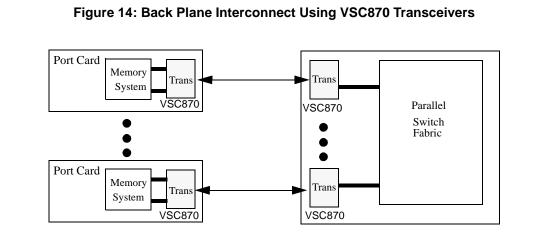

| 0            | 0     | 0           | 0        | 1          | 0           | Master transceiver in Direct Mode (figure 14) |  |  |  |

| 0            | 1     | 1           | 1        | 1          | 0           | Slave transceiver in Direct Mode (figure 14)  |  |  |  |

| 1            | 0     | 1           | 0        | 1          | 0           | Loopback mode internal to the transceiver     |  |  |  |

| 0            | 1     | 1           | 0        | 1          | 0           | Loopback mode through a VSC880                |  |  |  |

| 0            | 0     | 1           | 0        | 1          | 0           | Loopback mode through an external cable       |  |  |  |

| 0            | Х     | 0           | 0        | 0          | 1           | Mux/Demux Mode - No word alignment            |  |  |  |

G52190-0, Rev 4.1 01/05/01

Data Sheet VSC870

# 2.0 Packet Mode

#### 2.1 Overview

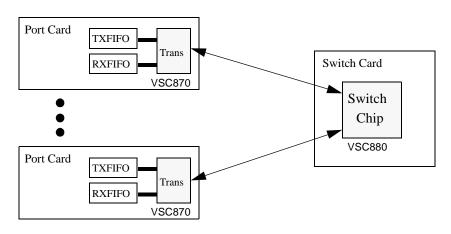

In Packet Mode the BYPASS signal is set LOW to allow the transceiver to utilize the built-in retransmission, camp-on, virtual output queue and delayed read enable logic. In addition, the signal CELLSYN is held LOW to disable the cell synchronization process. A special command word can be sent through the transceiver to the switch chip requesting connection to one or multiple output ports. Acknowledge (ACK) information will be returned to the transceiver from the switch allowing the port card to start transmitting data (see Application Note 31: Design Guide for a Packet Based Switch with Distributed Control). This special command word, a Connection Request (CRQ) Command, can be put on the front of the data packet to make the packet self routing. In this mode of operation, no controller chip needs to be connected to the switch chip as the switch chip handles all arbitration for connection requests (see the VSC880 data sheet). If the system designer wants to bypass the features described in this section, the signal BYPASS can be set HIGH. The user will then have direct control of the data stream between the transceiver and the switch. A picture of a Packet Mode system is shown below. The minimum packet size in this mode of operation is 4 words or 16 bytes.

#### Figure 1: Packet Mode System

#### 2.2 Data Encoding Format

The data and command words are described in section 1.0. In this section the Connection Request (CRQ) word format at 4 interfaces (transceiver parallel transmit port, serial line to switch, serial line from switch and transceiver parallel receive port) is described. In this mode the TXTYP[1:0] and RXTYP[1:0] bits are encoded differently than the overhead bits (B[1:0]) to effectively support a variety of features in the Packet Mode. The encoding for these data types are described in the following section.

High Performance Serial Backplane Transceiver

#### 2.2.1 Packet Format

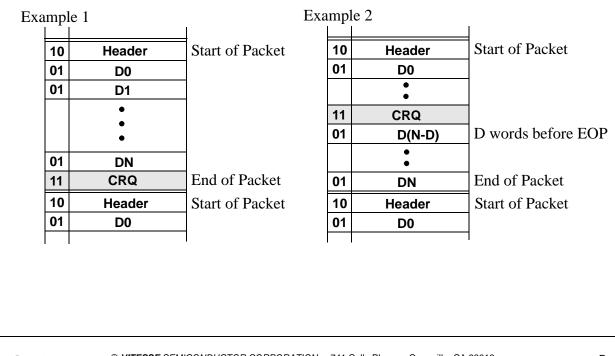

At both the transmit and receive sides, a start of packet is identified using a header word with TXTYP[1:0] and RXTYP[1:0] set to "10". Following this header word are the rest of the data words with TXTYP[1:0] and RXTYP[1:0] set to "01". This is shown in the table below.

| <i>TXTYP</i> [1:0]<br><i>RXTYP</i> [1:0] | Transmit<br>B[1:0] | Receive<br>B[1:0] | Word Type          | SCRAM = 1   | SCRAM = 0   | Error Check |

|------------------------------------------|--------------------|-------------------|--------------------|-------------|-------------|-------------|

| 0 0                                      | 0 0                | 0 0               | Command Word       | No Scramble | No Scramble | IDLE words  |

| 0 1                                      | 01 or 10           | 01,10,11          | Data Word          | Scramble    | No Scramble | No          |

| 10                                       | 11                 | 0 0               | Header Word        | No Scramble | No Scramble | No          |

| 11                                       | 0 0                | 0 0               | Connection Request | No Scramble | No Scramble | No          |

Two general ways of transmitting a data packets are shown in the figure below. In the first example, when the transceiver reads a CRQ word (which signals the start of a new packet) it waits for the ACK signal before transmitting the header word. In the second example, the CRQ word is sent D words before the end of the packet in order to utilize early arbitration and optimize the throughput. If there is no available packet for the next transmission, a null CRQ word and a null header word are used as end of packet. Command words such as IDLEs can be embedded inside the packet. On the receive side, the packets are delineated by the header word at the beginning and a CRQ word at the end. The word sequence loaded into the VSC870 parallel interface is also shown in the figure below. More details can be found in Application Note 31.

#### Figure 2: Packet Transmission Format

The IDLE word acts as a null word. The transceivers ignore these words at the transmit side. If there is no valid word at the transmit side, the signal TXEN should be set LOW. When the transceiver is loaded with IDLE words at the parallel transmit side, the transceiver will formulate its own IDLE word and send it through the serial output. At the receiving side, the transceiver sets the RXWA signal LOW if it receives an IDLE word from the serial line. IDLE words contain switch connection information that may be used by external logic. This information is also used for automatic packet retransmission as discussed in section 2.3.6. The connection information is in the same format as shown in section 2.2.4 below. The next CRQ word will also be forwarded through the switch to the current receiving port card. These can be ignored.

#### 2.2.2 Header Word Format at the Transceiver Parallel Interface

The header word format at the transceiver parallel interface is shown below. A maximum of 20 bits can be used to send data to the receiving port card. These bits can contain the first bytes of the data packet or other information. For a NULL header word, these bits are all X's.

|             |             | 19 18 17 16 | 9 18 17 16 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 |             |             |             |             |  |  |  |

|-------------|-------------|-------------|------------------------------------------------------------|-------------|-------------|-------------|-------------|--|--|--|

| хххх        | XXXX        | DDDD        | DDDD                                                       | DDDD        | DDDD        | DDDD        | хххх        |  |  |  |

| 31 30 29 28 | 27 26 25 24 | 23 22 21 20 | 19 18 17 16                                                | 15 14 13 12 | 11 10 09 08 | 07 06 05 04 | 03 02 01 00 |  |  |  |

Where: D[19:0]20 bit data payload

#### 2.2.3 Header word Format on the Serial Data Lines

The header word format as seen at the serial output of the transceiver or switch chip is shown below. Two overhead bits are added to designate a header word to the receiving chip. The serial data is transmitted with the MSB first.

| 33 32      | 31 30 29 28    | 27 26 25 24 | 23 22 21 20            | 19 18 17 16            | 15 14 13 12            | 11 10 09 08            | 07 06 05 04            | 03 02 01 00 |  |  |

|------------|----------------|-------------|------------------------|------------------------|------------------------|------------------------|------------------------|-------------|--|--|

| A A<br>1 0 | 0 B B 1<br>1 0 | 0110        | D D D D<br>19 18 17 16 | D D D D<br>15 14 13 12 | D D D D<br>11 10 09 08 | D D D D<br>07 06 05 04 | D D D D<br>03 02 01 00 | 1010        |  |  |

|            |                |             |                        | Data Payload           |                        |                        |                        |             |  |  |

Where:

A[1:0]11=to switch chip, 00=from switch chip B[1:0]00=Undefined, 01=Flow control channel, 10=Flow control channel, 11=Acknowledge D[19:0]20 bit data payload

## High Performance Serial Backplane Transceiver

#### 2.2.4 CRQ Format at the Transceiver TXIN[31:0] Interface

The connection request command word format at the TXIN[31:0] interface is shown below. The signals CT[2:0] and MD[1:0] are used by the transceiver to control modes of operation that are described later in this section. For a NULL CRQ word, set all the connection bits LOW.

| 31 30 29 | 28 27 26   | 25 24 | 23 22 21 20            | 19 18 17 16            | 15 14 13 12            | 11 10 09 08            | 07 06 05 04            | 03 02 01 00 |

|----------|------------|-------|------------------------|------------------------|------------------------|------------------------|------------------------|-------------|

| XXX      | ССС<br>ТТТ |       | C C C C<br>00 01 02 03 | C C C C<br>04 05 06 07 | C C C C<br>08 09 10 11 | C C C C<br>12 13 14 15 | D D D D<br>03 02 01 00 | XXXX        |

|          | 2 1 0      | 10    |                        | Conn                   | Data                   |                        |                        |             |

Where:

CT[2:0]Control bits

MD[1:0] Mode;

ode; 00=Camp-on with Priority Mode, CT[2:0]=camp-on frequency

01=Camp-on with Recast Mode, CT[2:0]=number of CRQ commands to send

10=Multi Queue Mode, CT[2:0]=camp-on frequency

C[0:15]] Connection request bit map. Set bit high for each output requested.

C[0] is for port 0 and C[15] is for port 15.

D[3:0] User defined data sent by transmitting port card

#### 2.2.5 CRQ Word Format on the Serial Data Lines to the Switch

The CRQ command word format as seen at the output of the transceiver is shown below. Two overhead bits are added by the transceiver to designate a CRQ word to the receiving switch chip. The signals AOA and BRK are used to control modes of operation in the switch chip which are discussed in the VSC880 data sheet. The serial data is transmitted with the MSB first.

| 33 32 | 31 30 29 28 27   | 26 25 24   | 23 22 21 20            | 19 18 17 16            | 15 14 13 12            | 11 10 09 08            | 07 06 05 04            | 03 02 01 00 |

|-------|------------------|------------|------------------------|------------------------|------------------------|------------------------|------------------------|-------------|

| 0 0   | 0 B B 1 0<br>1 0 | AAB<br>ROR | C C C C<br>00 01 02 03 | C C C C<br>04 05 06 07 | C C C C<br>08 09 10 11 | C C C C<br>12 13 14 15 | D D D D<br>03 02 01 00 | 1010        |

|       |                  | ВАК        |                        | Conn                   | ection Bits            |                        | Data                   |             |

Where:

B[1:0]00=Undefined,

01=Flow control channel,

10=Flow control channel,

11=Undefined

ARB1=Multi Queue arbitration, 0=Normal operation

AOA1=Acknowledge-On-All connections granted, 0=Acknowledge-On-Any connections granted

BRK 1=Break previous connection, 0=Do not break previous connection

C[0:15] Connection request bit map. Set bit high for each output requested, C[0] for output port 0 etc

D[3:0] User defined data sent by transmitting port card

#### 2.2.6 CRQ Word Format on the Serial Data Lines from the Switch

The CRQ command word format as seen at the output of the switch chip is shown below. Two overhead bits are added by the switch chip to designate a command word (00) to the transceiver. This command word contains the current active connections for the transmitting port card. The serial data is transmitted with the MSB first.

Data Sheet VSC870

|       |                      | к      |                        | Active (            | Connections            |                        | Data                   |             |

|-------|----------------------|--------|------------------------|---------------------|------------------------|------------------------|------------------------|-------------|

| 0 0   | 0 B B 1 0 1 0<br>1 0 | B<br>R | M M M M<br>00 01 02 03 | MMMM<br>04 05 06 07 | M M M M<br>08 09 10 11 | M M M M<br>12 13 14 15 | D D D D<br>03 02 01 00 | 1010        |

| 33 32 | 31 30 29 28 27 26 25 |        | 23 22 21 20            | 19 18 17 16         | 15 14 13 12            | 11 10 09 08            |                        | 03 02 01 00 |

Where:

B[1:0]00=Undefined,

01=Flow control channel,

10=Flow control channel,

11=Acknowledge

BRK1=This is the CRQ word for the next packet, 0=End of packet

M[0:15]Current outputs the transmit side is connected to

D[3:0] User defined data sent by transmitting port card

#### 2.2.7 CRQ Word Format at the Transceiver RXOUT[31:0] Interface

This is the CRQ command word format on the parallel interface RXOUT[31:0] of the transceiver. The two overhead bits are removed. This word arrives at the transceiver D words before the end of packet and also at the end of packet. The BRK bit is used to designate the end of packet (see Application Note 31). The data bits D[3:0] can be used by the transmitting port card to send information to the receiving port card such as port ID number.

| 31 30 29 28 | 27 26 25 | 24 | 23 22 21 20            | 19 18 17 16            | 15 14 13 12            | 11 10 09 08 | 07 06 05 04            | 03 02 01 00 |

|-------------|----------|----|------------------------|------------------------|------------------------|-------------|------------------------|-------------|

| 0000        | 000      | -  | M M M M<br>00 01 02 03 | M M M M<br>04 05 06 07 | M M M M<br>08 09 10 11 |             | D D D D<br>03 02 01 00 | 0000        |

|             |          | К  |                        | Active (               | Connections            |             | Data                   |             |

Where:

BRK1=This is the CRQ word for the next packet, 0=End of packet M[0:15]Current outputs the transmit side is connected to D[3:0] User defined data sent by transmitting port card

#### 2.3 Transmitter Operation

In Packet Mode, the transmitter is loaded with a connection request (CRQ) word followed by data words at the parallel interface. The operation of the transceiver is such that a single CRQ word loaded into TXIN[31:0] may cause the transceiver to send multiple CRQ words to the switch chip. When this happens, data may be blocked for several word clocks until the switch grants the request. In order to improve bandwidth utilization, a system wide mode of operation (called 'early arbitration') can be used where the switch matrix reconfiguration time is delayed D word clocks from the time arbitration results are determined. This allows the user logic to receive arbitration results just as the first word of the next data packet is ready for transmission, thus improving bandwidth utilization.

The CRQ word has several control bits that are shown in the definitions above. Five of these bits control the operation of the transceiver. The mode bits MD[1:0] determine the transceiver operating mode for a particular connection request. The control bits CT[2:0] determine priority levels or time-out values depending on the mode of operation. A summary of these operating modes is shown below. All of these modes will operate with early arbitration as described in the next sections.

## High Performance Serial Backplane Transceiver

| MD[1:0] | CRQ Mode                   | CT[2:0] Definition                         |

|---------|----------------------------|--------------------------------------------|

| 0 0     | Camp-on with Priority Mode | Number of IDLE words between each CRQ word |

| 0 1     | Multicast with Recast Mode | Number of CRQ words to send in a row       |

| 10      | Multi Queue Mode           | Number of IDLE words between each CRQ word |

Camp-on with Priority means the transceiver sends a repeated sequence of connection request words to the switch at a variable frequency until the request is granted. Multicast with Recast means the transceiver sends a fixed number of connection request words to the switch. If some but not all outputs are granted, the packet is sent. After the packet is transmitted successfully, the process is repeated for the rest of the ungranted outputs. In this mode, the FIFO or memory system is required to provide retransmit capability. Multi Queue mode allows multiple unicast requests to be sent to the switch in the same CRQ word. The switch returns data to the transceiver describing which connection was granted. This mode also supports priority camp-on as described above. In all of these modes, to release its connection, the port sends a new CRQ to the switch. If the CRQ does not have any output port bit set, the switch interprets this as a connection release command. If a destination is released, the switch keeps sending IDLE words to the destination port until a new connection is made.

#### 2.3.1 ABORT Signal

If the CRQ cannot be granted by the switch (for example, a time out expires in the user logic), the user can set the ABORT signal HIGH to abort the transaction. Upon detecting that the ABORT signal is HIGH, the transceiver sends out one more CRQ command with the connection request bit map cleared. This will force the switch to release any connections it has accumulated and all data words up to the next CRQ at the user interface will be read and ignored. The ABORT signal has to be held HIGH longer than the round trip delay between the transceiver and switch chip (> 9 clock cycles). This guarantees that any ACK generated during that time will be discarded. If ABORT is held HIGH for only a single cycle, then it can not be followed by another CRQ within 9 cycles. If the ABORT is set HIGH in the middle of a packet, the transceiver will also send a CRQ to the switch to break the current connections.

#### 2.3.2 Early Arbitration

In order to optimize throughput, early arbitration can be performed by sending the CRQ words to the switch D words before the end of the current packet. When arbitration results are known, the arbiter reserves the switch output for the granted input until the current data transmission is completed for that output. The end of the current transmission is identified by the header word of the next packet. When the switch receives the header word, the switch matrix will be reconfigured for the outputs that were reserved from the last arbitration. The maximum value for D is based on the round-trip delay from the time the port submits a CRQ until an ACK is received and the FIFO is ready to send a data word. In a typical system, the round trip delay is 9 cycles plus the FIFO response time. If the transmission line delay on the serial data line is significant, this time will increase. The value of D can be set higher than the round trip delay (i.e. maximum D = 9 + delay enable value). For example, if the round trip delay is 9 and D is set to 10, the minimum delay enable value is 2. The number D is a system wide value that must be used by all port

G52190-0, Rev 4.1 01/05/01

Data Sheet VSC870

cards. During Early Arbitration, the early CRQ is camped on in the switch and is arbitrated every cycle until another IDLE or CRQ word arrives. This means it is at the highest priority level regardless of CT counter. If the connection has not been granted at this point, CRQ sequences begin based on the MD and CT bits in the CRQ word as described below.

#### 2.3.3 Delay Enable Signal

If the signal DLYEN/CCKIN is set HIGH, a pre-programmed delay will occur between the time an ACK is received from the switch chip, and the signal REN (read enable) goes HIGH to start reading data at the parallel interface. Users can set this number to any value between 0 & 15 by using the 4 bits described in the command word in section 1.2.3. The default value is 6 word clock cycles. If the signal DLYEN/CCKIN is set LOW, the value is 0 no matter what value was programmed in. If the input buffer system is a single queue FIFO, after receiving ACK, the FIFO can send data out at once. In this case, the DLYEN/CCKIN signal can be set LOW to force REN HIGH right after receiving ACK signal. If the input buffer system is designed with multiple data queues, users can use the Multi Queue mode to improve throughput. In this mode, after the ACK signal is sent back to the FIFO, the transceiver takes 4 more cycles to send 4 bits of information containing the granted queue ID. The FIFO might take some extra time to process this information before it can send out data to the new destination. To account for this extra latency, The DLYEN/CCKIN signal can be set HIGH to force the transceiver to wait for 6 more cycles after receiving ACK before it can sends the data for the next packet. This 6 cycles of delay is set by default in the transceiver after reset. If the default value of 6 cycles is used, the value for early arbitration should be set to 9+6=14.

#### 2.3.4 Out of Synch Conditions

There are two out of synch conditions that can occur during packet mode operation. The serial link from the transmitting port card can go out of synch, or the serial link to the receiving port card can go out of synch. If the serial link on the transmitting side goes out of synch, the switch will send alignment patterns to the transceiver, and the transmitting port card is signaled on the OOS pin of the transceiver. When this happens, there is a chance that the receiving port card will receive only a partial packet. In this case, the CRQ word with BRK set HIGH will not be received; therefore, the receiving port card knows it did not receive the end of packet properly. If the serial link on the receiving side goes out of synch, the receiving transceiver will set the RXOK and TXOK pins high, and the OOS pin will also go high to indicate that the transceiver is in the link initialization process. The transmitting port card is not signaled for this condition through the switch chip. The user must make this condition known to the transmitting port card through some other means. If one of the output ports on the switch chip is in the out of synch state, any request for connection to this output will always be granted. In addition, no flow control back pressure will be applied from this output. This is to make sure multicast connections will not get permanently locked up, but packets could be lost in this case.

#### 2.3.5 Unicast / Multicast Camp-on with Priority Mode (MD[1:0] = 00)

In this mode, after the transceiver is loaded with a single CRQ at the parallel interface, it will send one CRQ word to the switch and wait for the ACK. During early arbitration, the switch will store this CRQ and arbitrate until all the outputs requested are granted. During this time, the transceiver can send more data words for the end of the last packet (the number of data words sent must be less than or equal to D). The value for D can also be set to zero. If the transceiver detects the header word for the next packet at the parallel interface before receiving an ACK (see figure

## High Performance Serial Backplane Transceiver

2), it stops reading from the parallel interface by setting REN LOW, sets RTM/TCLK HIGH and starts sending a repeated sequence of CRQ words to the switch which are arbitrated only on the cycle that they arrive. During this operation, the CRQ words are not stored at the switch. If all connections are granted, the transceiver will receive an ACK from the switch. If DLYEN/CCKIN is LOW, it sets the REN signal HIGH when it receives the ACK, and sends the header word and data to the switch. If DLYEN/CCKIN is HIGH, it waits for N more cycles before it sets REN HIGH and then sends header word and data to the switch.

During the repeated sequence of CRQs described above, different priorities for connections can be established by the number of the IDLE words sent between each CRQ words (determined by the CT[2:0]). The number of IDLEs after each CRQ word can range from 0-7 as shown in the table below. Generally, the more often a CRQ is received by the switch, the higher the probability that this connection will be granted.

| CT[2:0] | Number of<br>IDLE Words | CT[2:0] | Number of<br>IDLE Words |

|---------|-------------------------|---------|-------------------------|

| 0 0 0   | 0                       | 100     | 4                       |

| 001     | 1                       | 101     | 5                       |

| 010     | 2                       | 110     | 6                       |

| 011     | 3                       | 111     | 7                       |

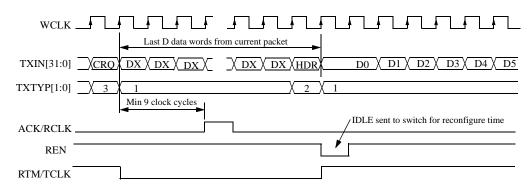

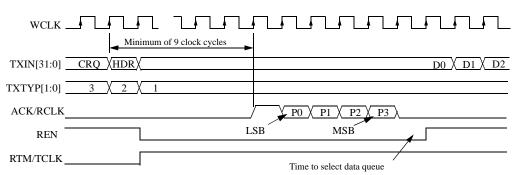

The functional timing diagram for camp-on mode with DLYEN/CCKIN set LOW is shown in figure 3. There are a minimum of 9 word clock cycles between loading the CRQ into the transceiver and the signal REN going HIGH (to start sending the data packet D0, D1, D2 etc.). This time will be longer if the requested output is busy or the port card is located further from the switch card. For multicast, the switch will reserve any available outputs and accumulate them as more CRQ commands are processed. This continues until all connections are reserved. At this point an ACK signal is sent back to the transceiver.

| TXIN[31:0]     CRQ (HDR)     D0 (D1) (D2)       TXTYP[1:0]     3 (2) (1       ACK/RCLK |  |

|----------------------------------------------------------------------------------------|--|

|                                                                                        |  |

| REN                                                                                    |  |

|                                                                                        |  |

| RTM/TCLK                                                                               |  |

#### Figure 3: Camp-on with Priority Transmitter Functional Timing (no early arbitration)

G52190-0, Rev 4.1 01/05/01

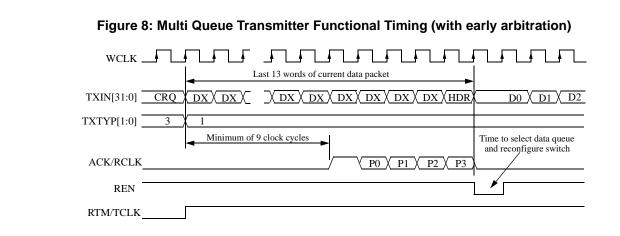

If early arbitration is used, the first CRQ word is sent to the switch D cycles before the end of the current packet. If the ACK is not received before the end of the current packet, the transceiver then operates the same as shown in the figure above. If the ACK is received before the end of the current packet, the transceiver will set the signal REN low for one cycle at the end of the current packet after the DLYEN/CCKIN counter has expired. The transceiver then sends an IDLE to the switch to give it time to reconfigure before the next data packet arrives. The functional timing diagrams are shown below.

Figure 4: Camp-on with Priority Transmitter Functional Timing (with early arbitration)

In the first CRQ the transceiver sends to the switch, the BRK bit is set. In subsequent CRQ words, this bit is cleared. The AOA bit is always set in this mode. The user logic can monitor the RTM/TCLK signal, which goes HIGH after the transceiver receives a new header word, and set LOW when the transceiver sees a new CRQ. In the case of multicast-with-recast, the RTM/TCLK signal will not go low until it sees a new CRQ during the last recast. If the RTM/TCLK signal stays HIGH too long, the user logic can abort the CRQ by setting ABORT HIGH.

Because these are camp-on requests, when several multicast CRQs of this type are received by the switch, there is a potential for a lock-up condition. The chances for lock-up can be reduced by minimizing the number of multicast requests. Lock-up can be broken by aborting the CRQ after a time-out period determined by the RTM/TCLK signal. If each port card uses a random time-out period before aborting, there is a higher probability that one of the multicast requests will be granted. A more efficient multicast method is shown in the next section.

#### 2.3.6 Multicast with Recast Mode (MD[1:0] = 01)

In this mode, after the transceiver is loaded with a single CRQ at the parallel interface, it will send one CRQ word to the switch and wait for the ACK. During early arbitration, the switch will store this CRQ and arbitrate until all the outputs requested are granted. During this time it can send a maximum of D (D can be greater than or equal to zero and is described in section 1.2.3) more data words until the packet header. If the transceiver detects the header word for the next packet at the parallel interface (see figure 2), it stops reading from the parallel interface by setting REN LOW. It also sets RTM/TCLK HIGH and starts sending more CRQ words to the switch depending on the value of CT[2:0]. During this camp-on period, the switch chip will accumulate the available outputs that were requested. If all connections are granted at some point during this period, the transceiver will receive an ACK from the switch. If DLYEN/CCKIN is LOW, at this time it sets the REN signal HIGH and sends the header word and data to the switch

### High Performance Serial Backplane Transceiver

as shown in Figure 3. If DLYEN/CCKIN is HIGH, it waits for N more cycles before it sets REN HIGH. If the counter set by the CT[2:0] bits has expired and the transceiver has not received the ACK signal, it sends out a CRQ word with AOA bit set LOW so that an ACK is returned if any output is granted. The transceiver keeps sending this CRQ word until it receives the ACK signal. When the ACK is received, the transceiver sets the REN signal HIGH and sends the header word and data to the switch for any output that was granted. This occurs right after receiving ACK if DLYEN/CCKIN is LOW or N cycles later if DLYEN/CCKIN is HIGH. The table below shows the number of CRQ words sent for each value of CT[2:0].

| CT[2:0] | Number of<br>CRQ Words |

|---------|------------------------|

| 000     | 1                      |

| 001     | 8                      |

| 010     | 16                     |

| 011     | 32                     |

| CT[2:0] | Number of<br>CRQ Words |

|---------|------------------------|

| 100     | 64                     |

| 101     | 128                    |

| 110     | 256                    |

| 111     | 512                    |

#### **Recast Operation**

If an ACK is not received before the CT[2:0] counter expires, the transceiver converts to recast mode. In this mode, the memory system or FIFO should support retransmit capability. When the transceiver first reads the Header word from the user interface, it sets the signal RTM/TCLK HIGH (Figure 5). This signal can be used to mark the FIFO location of the first data word in this packet and not allow the user logic to overwrite this data packet in the FIFO (see Application Note 31). The signal RTM/TCLK goes LOW when data has been sent to all requested destinations or if ABORT signal is asserted HIGH. If during a multicast, the CT[2:0] counter expires and some connections were not granted, an IDLE word or CRQ word will be returned to the transceiver from the switch chip describing the current connection status of the port. Upon detecting the CRQ word for the next packet at the parallel transmit interface, the transceiver will use this information from the switch to automatically form a new CRQ word requesting the outputs that were not granted. This CRQ word will replace the CRQ word at the parallel interface and is sent to the switch followed by remaining data if early arbitration is used. The process is repeated as if this is a new multicast CRQ for the current Packet. Also in early arbitration mode, the CRQ for the next packet remains in the external FIFO or memory system, and it is used after the last recast for the current packet. The ACK will toggle every time the transceiver performs recast.

When the transceiver reads the header of the next packet, the RFM signal is toggled to set the FIFO pointer back to the earlier location marked by RTM/TCLK in order to recast this packet to the new locations (Figure 6). Note that the RTM/TCLK signal is set after the transceiver loads the Header word for the current packet. Therefor the header word is lost and not retransmitted. During recast, this word will not be sent to the new locations if RTM/TCLK is used to mark the retransmit location. Users can externally adjust the RTM/TCLK to account for this latency or use an extra header word which will be lost during recast (see Application Note 31).

If the end of packet is reached before the connection information is returned from the switch, IDLE words will be sent to the switch while waiting for this response word. The retransmission process will continue until the data has been sent to all the requested destinations or ABORT is set HIGH. If ABORT is set HIGH (transmission is aborted), all of the following data words will not be retransmitted and will be ignored. The transceiver will then look for the next CRQ word at the parallel interface.

G52190-0, Rev 4.1 01/05/01

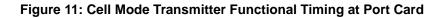

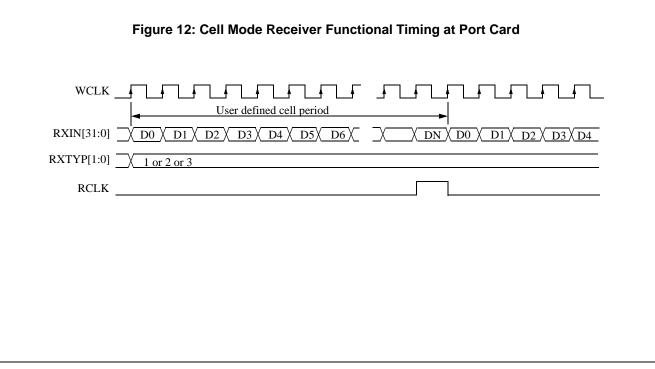

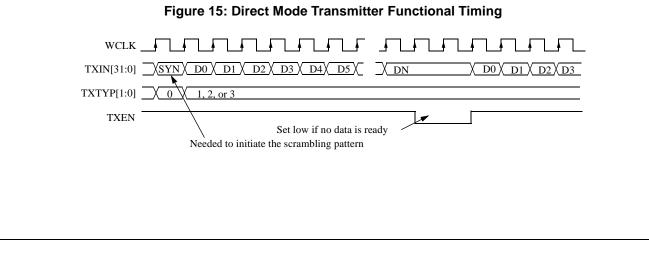

Data Sheet