**Panasonic**

## MN89306

## XGA LCD Display Controller

#### Overview

The MN89306 is an LCD display controller IC that provides high-speed graphics and high-quality display. The built-in BitBLT graphics accelerator supports 16 two-operand raster operations. The MN89306 also provides a full complement of power management functions to implement low-power video systems.

#### ■ Features

• LCD display functions

Color TFT  $(800 \times 600 \text{ and } 640 \times 480)$

Color DSTN/SSTN ( $800 \times 600$  and  $640 \times 480$ )

Display modes

$800 \times 600$ : 4 and 8 bpp

$640 \times 480$ : 4 and 8 bpp

$320 \times 480$ : 16 bpp (when  $320 \times 480$  resolution images are displayed on a  $640 \times 480$  panel)

• Host interface

ISA (16 bits), 386 and 486 (16 bits)

RISC CPUs (16-bit WAIT/RDY control)

• Memory interface

16M or 4M EDO, Fast Page Mode DRAM, SDRAM. (16-bit bus)

• Memory write FIFO

16 bits  $\times$  4 stages

• BitBLT accelerator

Video memory internal transfers

Host to video memory transfers

Pattern expansion

16 raster operations with 2-operand

Monochrome expansion and transfer

Filling of rectangular areas

LCD panel screen size correction

The screen size correction can be set independently in the horizontal and vertical directions.

- Power management mode

- Automatic stop function for clock supply to non-operation blocks (BitBLT and graphics blocks)

Standby mode

Suspend mode

Sleep mode

• Supply voltage

3.0 V to 3.6 V (The host interface pins also support 5 V inputs.)

#### Applications

• Word processors, POS terminals and other equipment with LCD display

Note) The term bpp stands for bits per pixel.

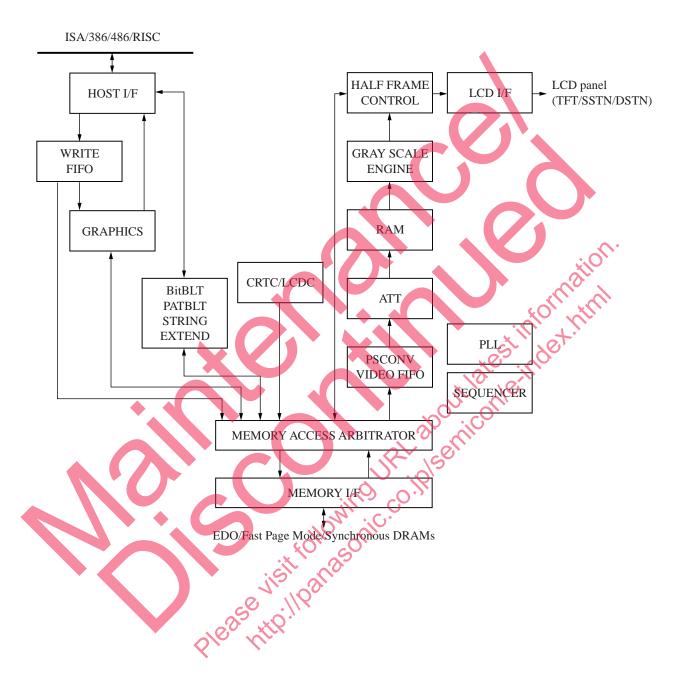

#### ■ Block Diagram

#### ■ Function Block Descriptions

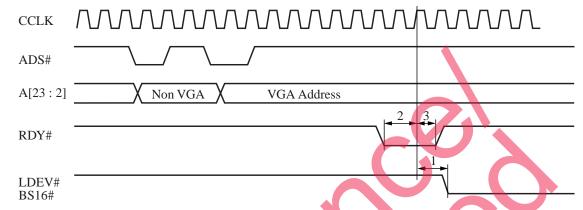

#### 1) Host interface

The host interface decodes the host bus addresses, generates the I/O and memory access enable signals, and transfers required information for read and write operations to the chip internal registers and for memory read and write operations. Data transfers are performed in 16-bit units for the ISA, 386, 486, and RISC buses.

| Host bus type  | Data bus width |

|----------------|----------------|

| ISA            | 16 bits        |

| 386SX, 486, VL | 16 bits        |

| RISC CPU       | 16 bits        |

Furthermore, since the MN89306 supports linear addressing, the CPU address calculation time can be reduced. Thus memory accesses are faster than if memory were accessed using a VGA compatible address area.

Note) 1. ISA bus is a registered trademark of the (US) Industry Standards Architecture.

- 2. VL bus is a registered trademark of the (US) Video Electronics Standard Association.

- 3. VGA is a registered trademark of International Business Machines, Inc.

#### 2) Write FIFO

The write FIFO provides a function that temporarily accumulates memory write requests from the CPU bus, and thus significantly increases the speed with which the IC can handle CPU bus memory write requests. The FIFO can hold 4 units of 16-bit data. This buffer compensates for the periods when the IC cannot accept CPU memory access requests due to display refresh operations, thus significantly reducing the wait time associated with CPU memory writes. Furthermore, in display modes that do not require VGA compatible processing, the graphics speed is increased even further since data can be sent directly from the write FIFO to the memory access arbitrator.

#### 3) Graphics controller

The graphics controller processes data from the write FIFO according to the mode specified by the current register settings. According to the operating mode, this module performs data expansion processing on the data from the write FIFO and then the resultant data is sent to the memory access arbitrator. Furthermore, according to the operating mode, this module processes data read from memory and then sends the resultant data to the host interface.

#### 4) Memory access arbitrator

The memory access arbitrator arbitrates memory access requests from the write FIFO, memory access requests from the graphics controller, memory access requests from the BitBLT block, display data read requests from the LCD controller, and memory access requests from the half frame controller. It then sends the memory access request, address, and data to the memory interface.

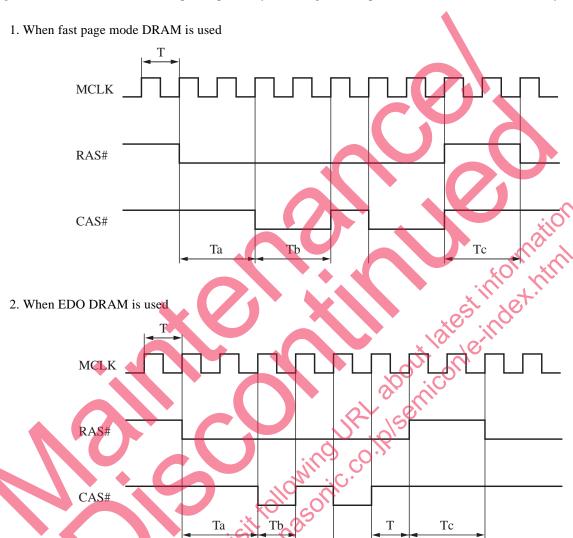

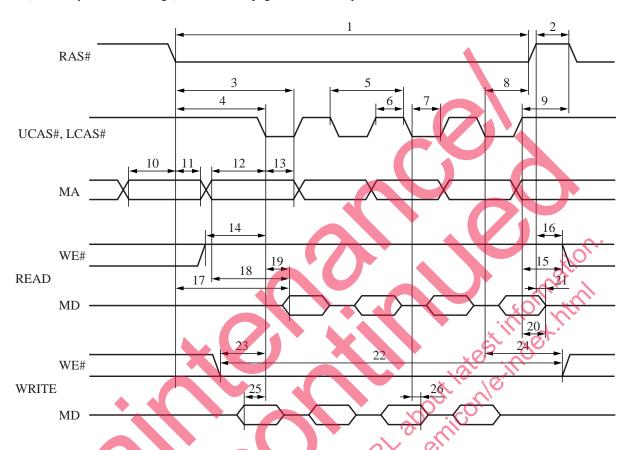

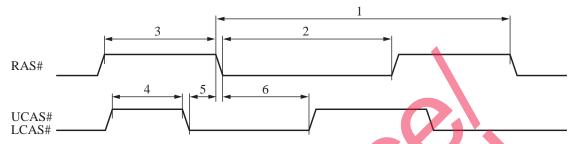

#### 5) Memory access interface

The memory access interface accesses memory according to request signals from the memory access arbitrator. DRAM with fast page mode is used to read display data from memory as quickly as possible. The memory access interface supports variable memory access timings to get the maximum speed possible from memory when fast DRAMs are used. The memory access interface also outputs refresh signals according to the operating state of the chip.

#### 6) CRT/LCD controller

This block generates the display address, display enable, and vertical and horizontal synchronizing signals required for display. It also performs image enlargement in the vertical direction.

#### ■ Block Functional Descriptions (continued)

#### 7) Video FIFO/PSCONV

The video FIFO temporarily stores data read out of memory in fast page mode, converts that data to dot units according to control signals from the CRT/LCD controller, and outputs that display data. In text mode, this circuit calculates font addresses and issues access requests to the memory interface.

#### 8) Attribute controller

The attribute controller processes data from the video FIFO according to the display mode and generates color data for each dot. It also implements blinking, underlining, and enlargement in the horizontal direction.

#### 9) Color palette

The color palette generates 4-bit data for each of the three colors red, green, and blue by accessing internal palette memory according to data from the attribute controller.

#### 10) Gray scale engine

The gray scale engine calculates a brightness level from a color signal and generates a monochrome level signal when a monochrome STN LCD panel is used. This circuit supports two techniques for calculating the intensity: a technique in which the G signal data is used directly as the intensity level and a technique in which the dot brightness is calculated by simulating the NTSC luminance signal calculation. The generated monochrome level signal is output as a gray-scale pattern optimal for that level. If a color STN is used, this circuit is used to generate gray-scale patterns for each of the red, green, and blue data values from the color palette. These gray-scale patterns allow up to 16 levels to be displayed by controlling the frame rate.

#### 11) Half-frame control

When displaying on a DSTN panel, the post-level control data is stored for half the screen in video memory. Then, a high refresh rate can be implemented at a low clock frequency by reading out data for half a frame from video memory and sending that data to the LCD panel interface simultaneously with the data sent from the gray scale engine.

#### 12) LCD panel interface

The LCD panel interface outputs the required synchronizing signals, data clock signals, and display data appropriate for the type of LCD panel connected. This circuit supports both STN (including color and monochrome units as well as SSTN and DSTN devices) and color TFT LCD panels. Note that if a DSTN panel is used, a data area (with 3 bits per pixel) large enough to hold a half frame of data must be allocated in video memory.

#### 13) BitBLT engine

The BitBLT engine provides high-speed data transfers either from the host to video memory or between areas in video memory. During these data transfers, the BitBLT engine supports 16 operations that correspond to two-operand (source and destination) raster operations. The monochrome source expansion function provided by this circuit can also convert 1-bpp data to 4-, 8-, or 16-bpp data and transfer that data to the destination area. In addition, it also provides a rectangular area fill function and a transparent function. These operations are supported only in the graphics display modes, and operate in packed pixel mode (8 or 16 bits per pixel). The BitBLT engine can also be operated in 8-dot units in plane mode, and in 2-dot units in 4-bpp packed pixel mode.

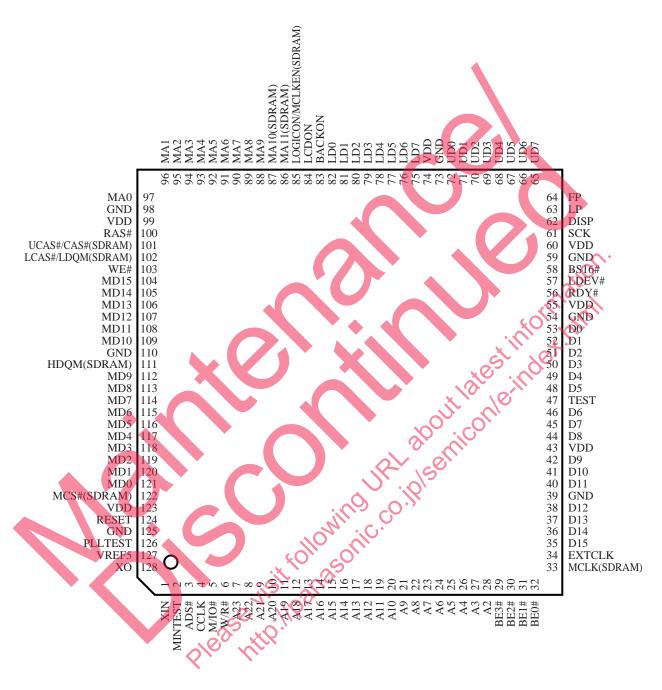

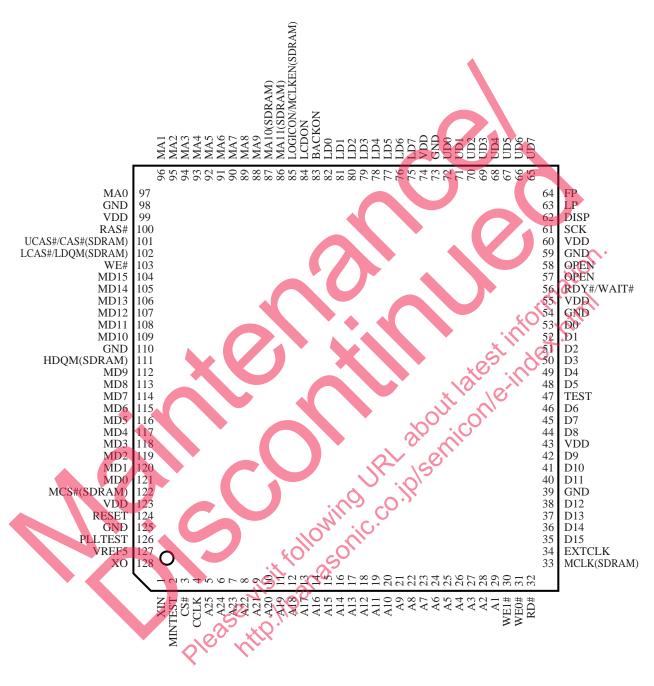

#### ■ Pin Arrangement

1) 486/386DX Local Bus Mode

(TOP VIEW)

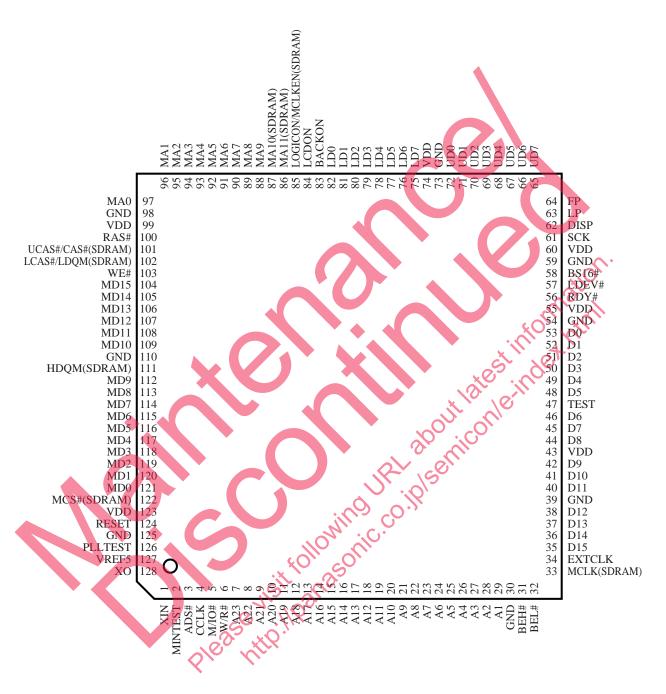

#### ■ Pin Arrangement (continued)

2) 386SX Local Bus Mode

(TOP VIEW)

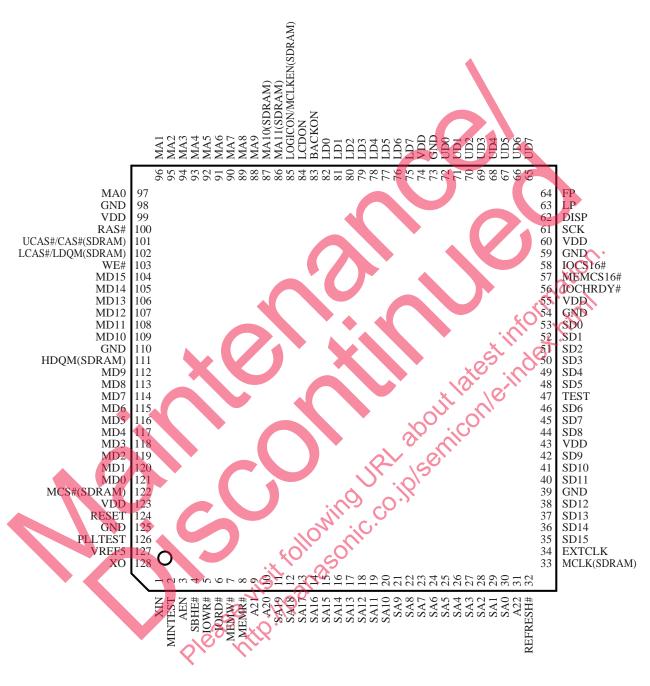

#### ■ Pin Arrangement (continued)

3) ISA Bus Mode

(TOP VIEW)

#### ■ Pin Arrangement (continued)

4) RISC CPU Mode

(TOP VIEW)

#### ■ Pin Descriptions

This section describes the functions of each pin. The pins are classified by their I/O type as input (I), output (O), or I/O (I/O). The Level column indicates the input interface levels for the pin, either 5 V TTL for 5 V inputs or CMOS for 3.3 V CMOS inputs. Pin names that are followed by a number sign (#) are inverted logic (active low) signals.

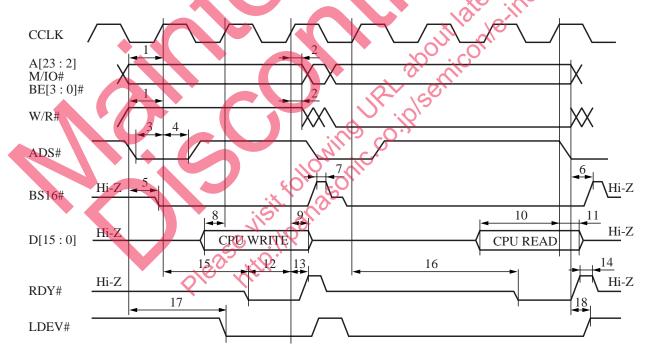

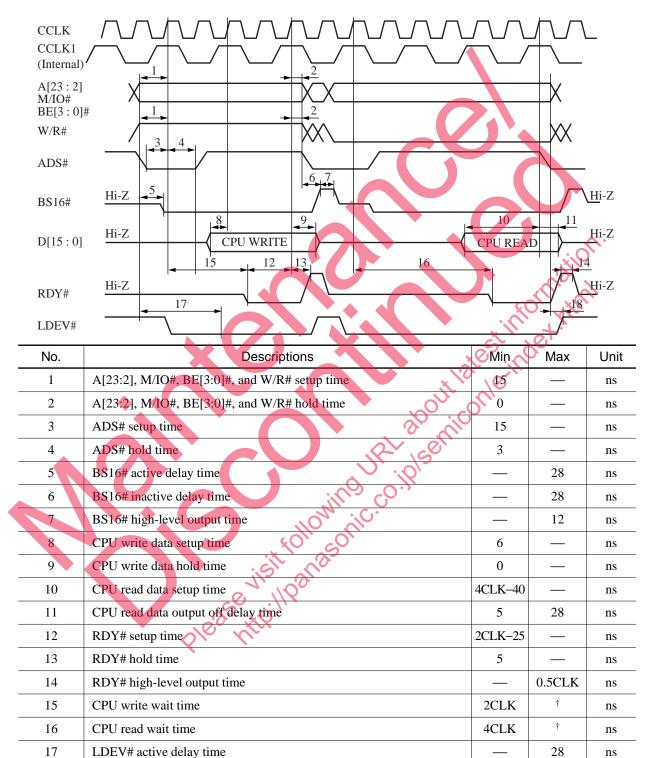

#### 1) 386/486 Local Bus Related Pins

| Pin Name                                                | I/O     | Level   | Function                                                                                                                                                                         |

|---------------------------------------------------------|---------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADS#                                                    | I       | 5 V TTL | Address strobe Indicates that the host address is valid.                                                                                                                         |

| M/IO#                                                   | I       | 5 V TTL | Memory or I/O access Indicates whether an access is a memory access or an I/O access. A high level indicates a memory access and a low level indicates an I/O access.            |

| W/R#                                                    | I       | 5 V TTL | Write/Read control Controls whether a host access is read or write. A high level indicates a write and a low level indicates a read.                                             |

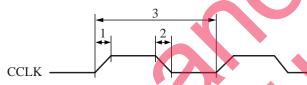

| CCLK                                                    | I       | 5 V TTL | Local bus clock The local bus clock                                                                                                                                              |

| A[23 : 2]<br>A1(386SX)                                  | I       | 5 V TTL | Host address These inputs are the host address bus.                                                                                                                              |

| BE[3:0]#<br>(486/386DX)<br>BEH# (386SX)<br>BEL# (386SX) | I       | 5 V TTL | Byte enable These inputs indicate which bytes in the data bus are valid.  Data bus Host data bus I/O signals.                                                                    |

| D[15:0]                                                 | I/O     | 5 V TTL | Data bus<br>Host data bus I/O signals.                                                                                                                                           |

| RDY#                                                    | I/O     | 5 V TTL | Ready Indicates to the host that processing has completed. External circuits can monitor the external -RDY signal to determine when a 386 mode pipelined sequence has completed. |

| LDEV#                                                   | 0       |         | Local device Indicates to the host that this chip was accessed as a local bus device.                                                                                            |

| BS16#                                                   | 0       |         | 16-bit data bus Indicates to the host that this chip was accessed as a 16-bit device.                                                                                            |

|                                                         |         |         | eas hith: I'l                                                                                                                                                                    |

| 2) ISA Bus Relate                                       | ed Pins | X       |                                                                                                                                                                                  |

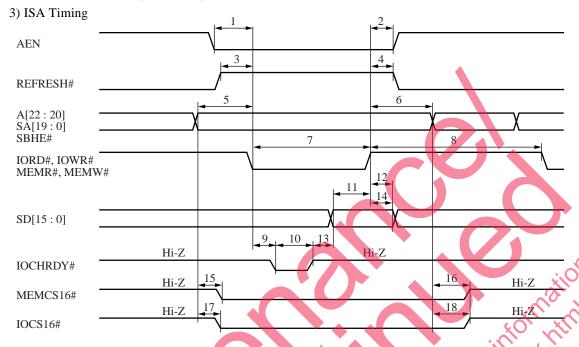

#### 2) ISA Bus Related Pins

| Pin Name | I/O | Level   | Function                                                                                                                                                                   |

|----------|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AEN      | I   | 5 V TTL | Address enable A high level on this input indicates that a DMA operation is in progress. Therefore, the MN89306 will not respond to an I/O access when this input is high. |

## ■ Pin Descriptions (continued)

## 2) ISA Bus Related Pins (continued)

| Pin Name                               | I/O | Level                                   |                                                                                                                                                                                       |                        | Function                                                                                                                                                                                                                        |  |  |  |  |  |

|----------------------------------------|-----|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| SBHE#                                  | I   | 5 V TTL                                 |                                                                                                                                                                                       |                        | gh enable<br>he 16-bit bus is being used.                                                                                                                                                                                       |  |  |  |  |  |

|                                        |     |                                         | SBHE                                                                                                                                                                                  | SAO                    | Bus status                                                                                                                                                                                                                      |  |  |  |  |  |

|                                        |     |                                         | 0                                                                                                                                                                                     | 0                      | 16-bit transfer                                                                                                                                                                                                                 |  |  |  |  |  |

|                                        |     |                                         | 0                                                                                                                                                                                     | 1                      | High-order byte transfer                                                                                                                                                                                                        |  |  |  |  |  |

|                                        |     |                                         | 1                                                                                                                                                                                     | 0                      | Low-order byte transfer                                                                                                                                                                                                         |  |  |  |  |  |

|                                        |     |                                         | 1                                                                                                                                                                                     | 1                      | Disabled                                                                                                                                                                                                                        |  |  |  |  |  |

| ************************************** | -   | - * * * * * * * * * * * * * * * * * * * | */0                                                                                                                                                                                   |                        |                                                                                                                                                                                                                                 |  |  |  |  |  |

| IOWR#                                  | I   | 5 V TTL                                 | I/O writ<br>Indicate                                                                                                                                                                  |                        | O write request.                                                                                                                                                                                                                |  |  |  |  |  |

| IORD#                                  | I   | 5 V TTL                                 | I/O read<br>Indicate                                                                                                                                                                  |                        | read request.                                                                                                                                                                                                                   |  |  |  |  |  |

| MEMW#                                  | I   | 5 V TTL                                 | Memory<br>Indicate                                                                                                                                                                    |                        | nory write request.                                                                                                                                                                                                             |  |  |  |  |  |

| MEMR#                                  | I   | 5 V TTL                                 | Memory<br>Indicate                                                                                                                                                                    |                        | nory read request.                                                                                                                                                                                                              |  |  |  |  |  |

| A[22 : 20]                             | I   | 5 V TTL                                 | Address<br>Address                                                                                                                                                                    | s[22 : 20<br>s bits 20 | o to 22.                                                                                                                                                                                                                        |  |  |  |  |  |

| SA[19:0]                               | I   | 5 V TTL                                 | Address                                                                                                                                                                               |                        |                                                                                                                                                                                                                                 |  |  |  |  |  |

| SD[15:0]                               | I   | 5 V TTL                                 | Data[15<br>Host bu                                                                                                                                                                    |                        | us pins. R Self                                                                                                                                                                                                                 |  |  |  |  |  |

| IOCHRDY#                               | 0   |                                         |                                                                                                                                                                                       | output                 | dy s either a low level or a high-impedance state. It goes to the low ait is applied to either an I/O or memory access.                                                                                                         |  |  |  |  |  |

| MEMCS16#                               | 0   |                                         | Memory                                                                                                                                                                                | y chip se              | elect 160                                                                                                                                                                                                                       |  |  |  |  |  |

|                                        |     |                                         | from the                                                                                                                                                                              | s pin fo<br>s are pos  | s either a low level or a high-impedance state. A low-level output of a memory access to this chip informs the system that 16-bit saible for this memory access. Note that 16-bit transfers are always esses to display memory. |  |  |  |  |  |

| IOCS16#                                | 0   | <i>P</i>                                | from thi                                                                                                                                                                              | outputs                | s either a low level or a high-impedance state. A low-level output<br>r an I/O access to this chip informs the system that 16-bit transfers                                                                                     |  |  |  |  |  |

| REFRESH#                               | I   | 5 V TTL                                 | are possible for this I/O access.  Refresh A low level input to this pin indicates the timing for DRAM refresh. All memory access requests issued when this input is low are ignored. |                        |                                                                                                                                                                                                                                 |  |  |  |  |  |

## ■ Pin Descriptions (continued)

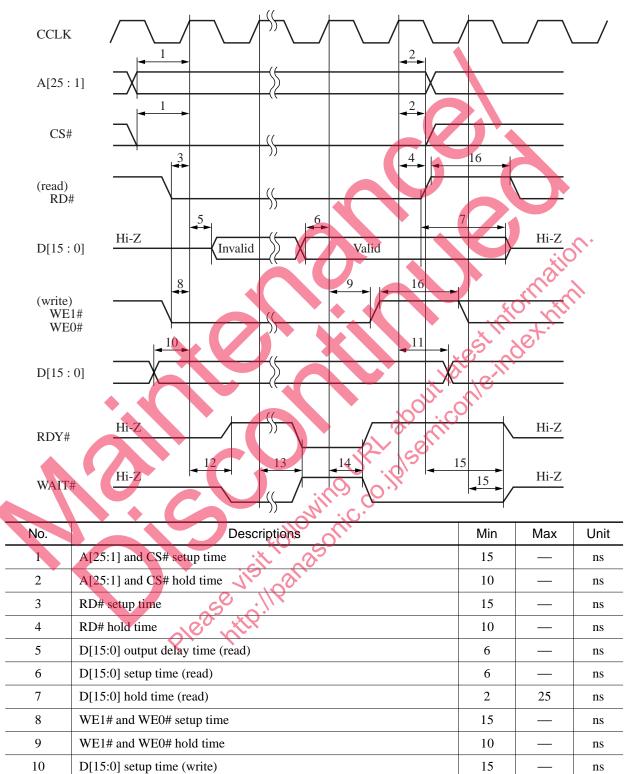

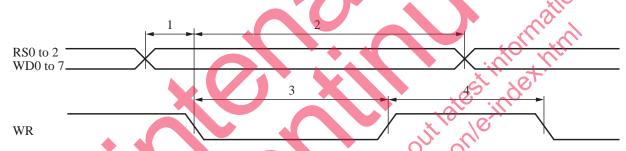

## 3) RISC CPU Related Pins

| 5 V TT 5 V TT | CPU bus synchronization clock. A clock frequency of up to 33 MHz can be supported.  L Chip select The MN89306 will only accept access operations when CS# is low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | The MN89306 will only accept access operations when CS# is low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5 V TT        | L Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|               | Reads out MN89306 I/O registers or memory. This line is always used for word access.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5 V TT        | Write low byte Write signal for the CPU data bus low order byte, bits [7:0]. The MN89306 can be set to operate as either a big endian or a little endian machine.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5 V TT        | Write high byte Write signal for the CPU data bus high order byte, bits [15:8]. The MN89306 can be set to operate as either a big endian or a little endian machine.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5 V TT        | L Address CPU address lines.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5 V TT        | Data CPU data bus. The MN89306 can be set to operate as either a big endian or a little endian machine.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5 V TT        | The functions of this signal differs depending on the type of CPU selected.  RDY# control when MA[2:0] = 101.  Reports to the CPU that processing has completed. This pin outputs a high level when a wait is required to access the MN89306. When processing completes, the MN89306 announces that fact by outputting a low level for 1 CCLK cycle.  Then, after outputting a high level for 1 CCLK cycle, it sets the output to the high-impedance state.  WAIR# control when MA[2:0] = 110.  Issues a wait request to the CPU. This pin outputs a low level only for the time that the CPU must wait to access the MN89306. When processing completes, the MN89306 informs the CPU that processing has completed by outputting a high level for 1 CCLK cycle. Then, the output is set to the high-impedance state.  An external pull-up resistor is required, whichever function is used. Determine the value of the pull-up resistor based on the range of the current capacities of this |

|               | 5 V TT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

#### ■ Pin Descriptions (continued)

#### 3) RISC CPU Related Pins (continued)

Due to the differences between the buses, the pin functions correspond as shown in the table.

| ISA      | 386SX   | 386DX/486 | RISC       |

|----------|---------|-----------|------------|

| AEN      | ADS#    | ADS#      | CS#        |

| SBHE#    | CCLK    | CCLK      | CCLK       |

| IOWR#    | M/IO#   | M/IO#     | A25        |

| IORD#    | W/R#    | W/R#      | A24        |

| MEMW#    | A23     | A23       | A23        |

| MEMR#    | A22     | A22       | A22        |

| A21      | A21     | A21       | A21        |

| A20      | A20     | A20       | A20        |

| SA[19:2] | A[19:2] | A[19:2]   | A[19:2]    |

| SA1      | A1      | BE3#      | A1         |

| SA0      | GND     | BE2#      | WE1#       |

| A22      | BEH#    | BE1#      | WE0#       |

| REFRESH# | BEL#    | BEO#      | RD#        |

| IOCHRDY# | RDY#    | RDY#      | RDY#/WAIT# |

| MEMCS16# | LDEV#   | LDEV#     | OPEN       |

| IOCS16#  | BS16#   | BS16#     | OPEN       |

| SD[15:0] | D[15:0] | D[15:0]   | D[15:0]    |

Note) If a RISC CPU is used, the pins marked OPEN must be left open.

If the host type is ISA or RISC, big endian or little endian may be selected as shown below.

A Interface (little endian)

#### ISA Interface (little endian)

| SBHE | SA0 | SD15 | SD14 | SD13 | SD12 | SD11 | SD10 | SD9        | SD8 | SD7 | SD6 | SD5 | SD4 | SD3 | SD2 | SD1 | SD0 |

|------|-----|------|------|------|------|------|------|------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0    | 0   | D15  | D14  | D13  | D12  | D11  | D10  | <b>D</b> 9 | D8  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| 0    | 1   | D15  | D14  | D13  | D12  | D11  | D10  | D9         | Ъ8  |     |     | _   | _   |     | _   |     | _   |

| 1    | 0   |      | _    |      | —    | 0    | 7-/  | 6.0        |     | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

## ISA Interface (big endian)

| SBHE | SA0 | SD15 | SD14 | SD13 | SD12 | SD11 | SD10 | SD9 | SD8 | SD7 | SD6 | SD5 | SD4 | SD3 | SD2 | SD1 | SD0 |

|------|-----|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0    | 0   | D7   | D6   | D5   | D4   | D3   | D2   | D1  | D0  | D15 | D14 | D13 | D12 | D11 | D10 | D9  | D8  |

| 0    | 1   | D7   | D6   | D5   | D4   | D3   | D2   | D1  | D0  | _   |     | _   | _   |     | _   |     | _   |

| 1    | 0   |      |      |      |      |      | _    | _   |     | D15 | D14 | D13 | D12 | D11 | D10 | D9  | D8  |

#### ■ Pin Descriptions (continued)

#### 3) RISC CPU Related Pins (continued)

#### RISC Interface (little endian)

| WE1# | WE0# | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|------|------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| 0    | 0    | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 0    | 1    | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 |    |    |    | _  | _  | _  | _  | _  |

| 1    | 0    |     |     |     |     |     |     |    |    | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

#### RISC Interface (big endian)

| WE1# | WE0# | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7  | D6  | D5  | D4  | D3  | D2  | D1 | D0 |

|------|------|-----|-----|-----|-----|-----|-----|----|----|-----|-----|-----|-----|-----|-----|----|----|

| 0    | 0    | D7  | D6  | D5  | D4  | D3  | D2  | D1 | D0 | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 |

| 0    | 1    | D7  | D6  | D5  | D4  | D3  | D2  | D1 | D0 |     | -   |     | _   |     | -   |    | _  |

| 1    | 0    |     | _   |     |     | _   | _   |    |    | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 |

The little endian or big endian state is set with bit 7 in the ENA register for I/O access, and with bit 0 in the XSRIE gister for memory access.

Memory Access Related Pins hen EDO/Fast Page Mode DRAM is used. register for memory access.

#### 4) Memory Access Related Pins

When EDO/Fast Page Mode DRAM is used.

| Pin Name | I/O | Level | Function 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MA[9:0]  | I/O | CMOS  | Display memory address These pins are set to input mode by a reset, and the pins MA[2:0] are used to decide the chip host type. The pins MA[9:3] are latched internally to the IC as the expansion pin monitor register data.  16M DRAM RAS address: MA[9:0], CAS address: MA[9:0] MA[11:10]: Low-level output  4M DRAM RAS address: MA[8:0], CAS address: MA[8:0] MA[11:9]: Low-level output  Display memory address10 After a reset, functions as the pin that selects whether SDRAM or EDO/fast page mode memory is used. Do not pull up this line if EDO or fast page mode memory is used. |

| RAS#     | О   |       | Row address strobe Row address latch strobe signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| LCAS#    | 0   |       | Lower column address strobe for RAM RAM low-order byte column address strobe signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| UCAS#    | О   |       | Upper column address strobe for RAM RAM high-order byte column address strobe signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| WE#      | 0   |       | Write enable Data write signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MD[15:0] | I/O | CMOS  | Memory data bus DRAM memory data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

13

## ■ Pin Descriptions (continued)

4) Memory Access Related Pins (continued)

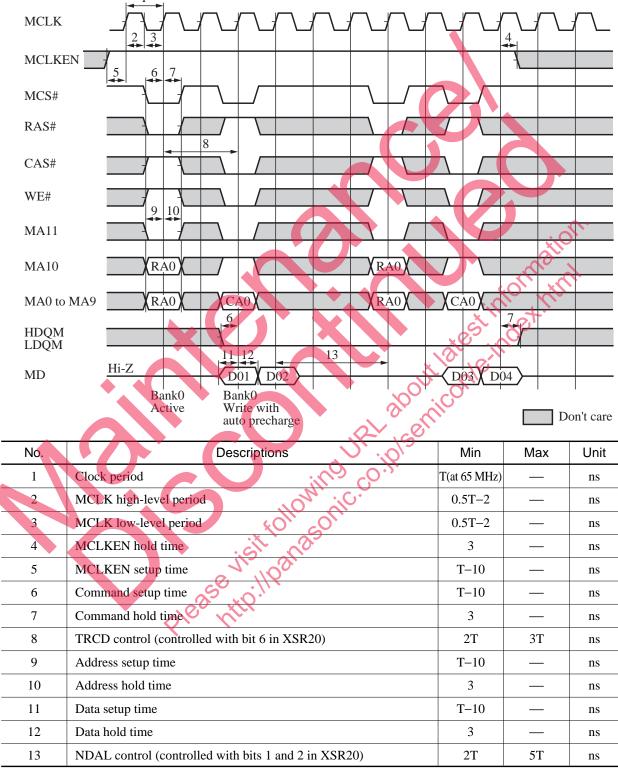

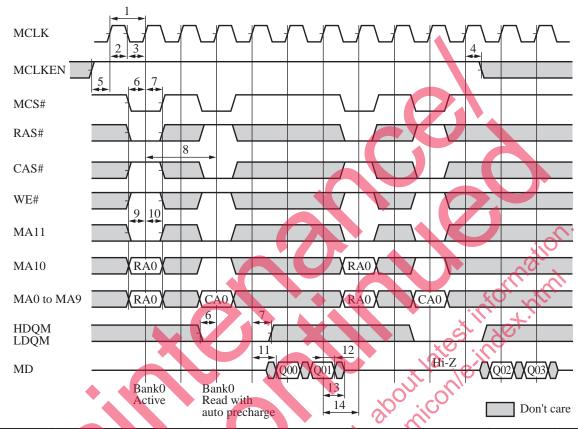

When SDRAM is used.

| Pin Name | I/O | Level | Function                                                                                                                                                                                              |

|----------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MA11     | О   |       | Display memory address                                                                                                                                                                                |

| MA[10:0] | I/O | CMOS  | Display memory address                                                                                                                                                                                |

|          |     |       | These pins are set to input mode by a reset, and the pins MA[2:0] are used to set                                                                                                                     |

|          |     |       | the chip host type. The pins MA[9:3] are latched internally to the IC as the                                                                                                                          |

|          |     |       | expansion pin monitor register data. Pull up the MA10 pin if SDRAM is used.                                                                                                                           |

|          |     |       | 16M DRAM                                                                                                                                                                                              |

|          |     |       | RAS address: MA[10:0], CAS address: MA[7:0]                                                                                                                                                           |

|          |     |       | MA11: Bank select                                                                                                                                                                                     |

|          |     |       | 4M DRAM                                                                                                                                                                                               |

|          |     |       | RAS address: MA[8:0], CAS address: MA[7:0]                                                                                                                                                            |

|          |     |       | MA9: Bank select, MA[11:10]: Low-level output                                                                                                                                                         |

| MCLK     | О   |       | Memory clock                                                                                                                                                                                          |

|          |     |       | SDRAM operating clock.                                                                                                                                                                                |

| MCS#     | О   |       | Chip select                                                                                                                                                                                           |

|          |     |       | SDRAM command signal.                                                                                                                                                                                 |

| RAS#     | О   |       | Row address strobe                                                                                                                                                                                    |

|          |     |       | Row address strobe output.                                                                                                                                                                            |

| CAS#     | О   |       | Column address strobe                                                                                                                                                                                 |

|          |     |       | SDRAM operating clock.  Chip select SDRAM command signal.  Row address strobe Row address strobe output.  Column address strobe Column address strobe output.  Write enable Data write signal output. |

| WE#      | O   |       | Write enable                                                                                                                                                                                          |

|          |     |       | Data write signal output.                                                                                                                                                                             |

| LDQM     | 0   |       | Low data                                                                                                                                                                                              |

|          |     |       | Low-order byte output mask signal.                                                                                                                                                                    |

| HDQM     | 0   |       | High data                                                                                                                                                                                             |

|          |     |       | High-order byte output mask signal.                                                                                                                                                                   |

| MCLKEN   | 0   |       | Memory clock enable                                                                                                                                                                                   |

|          |     |       | Sets the SDRAM to the operating state. This pin outputs a high level during normal                                                                                                                    |

|          |     |       | operation, but is set to low in suspend and sleep modes.                                                                                                                                              |

|          |     |       | This pin cannot be used in external RAMDAC mode. In that mode, tie the SDRAM                                                                                                                          |

| ,        |     |       | CLKEN pin high.                                                                                                                                                                                       |

|          |     |       | Note that both suspend and sleep mode cannot be used with external                                                                                                                                    |

|          |     | 6,    | RAMDAC mode.                                                                                                                                                                                          |

| MD[15:0] | I/O | CMOS  | Memory data bus                                                                                                                                                                                       |

|          |     |       | DRAM memory data.                                                                                                                                                                                     |

## ■ Pin Descriptions (continued)

## 5) LCD Related Pins

| Pin Name            | I/O | Level | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BACKON              | I/O | CMOS  | Back light on Outputs a signal that requests that the backlight be turned on. This pins can also be used as the LOGICON signal output pin by setting a control register.  Low: Backlight off High: Backlight on This pin can also be used as a general-purpose I/O port. In external RAMDAC mode, this pin is set to the output state and is used as the register write signal to the RAMDAC.                                                                                                                                                                           |

| LCDON               | I/O | CMOS  | LCD drive power supply on Outputs a signal that requests that the LCD panel drive power supply be turned on. Low: LCD drive power supply off High: LCD drive power supply on This pin can also be used as a general-purpose I/O port. In external RAMDAC mode, this pin is set to the output state and is used as the register address bit 0 signal to the RAMDAC.                                                                                                                                                                                                      |

| LOGICON<br>(MCLKEN) | I/O | CMOS  | LCD logic system power on Outputs a signal that requests that the LCD panel logic system power supply be turned on. If SDRAM is used with LCD display, this pin is used as the SDRAM MCKLEN pin. If the LOGICON function is required the LOGICON signal can be output from the BACKON pin by setting register values.  Low: LCD logic system power supply off High: LCD logic system power supply on This pin can also be used as a general purpose I/O port, except if SDRAM is used.  In external RAMDAC mode, this pin is set to the output state and is used as the |

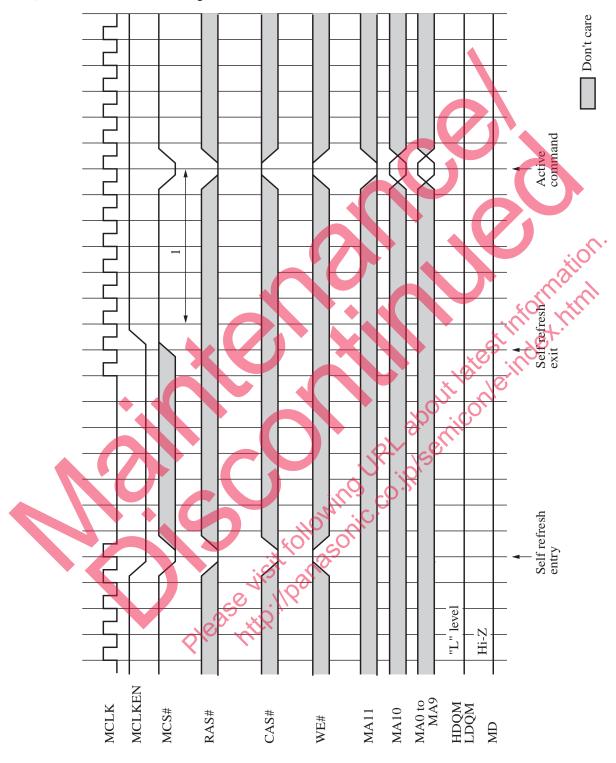

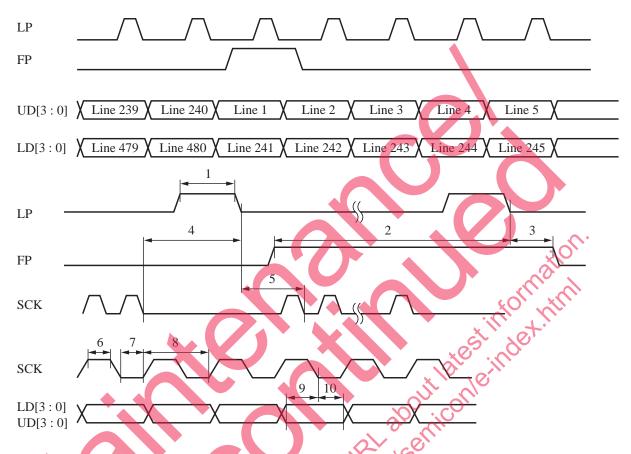

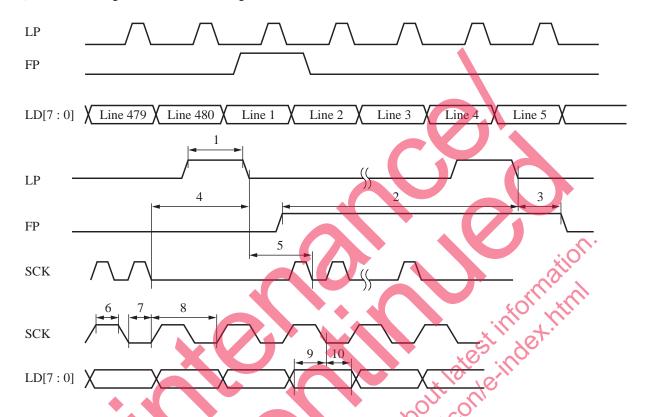

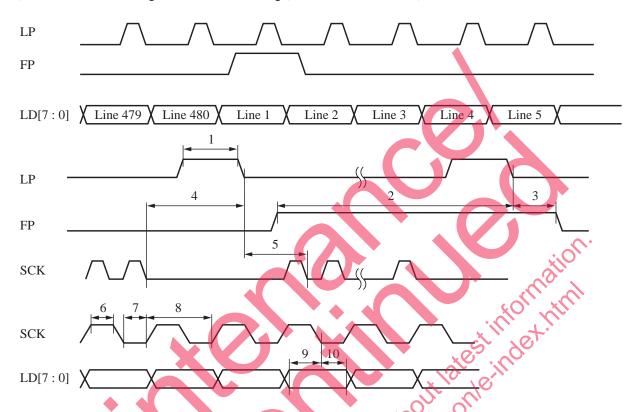

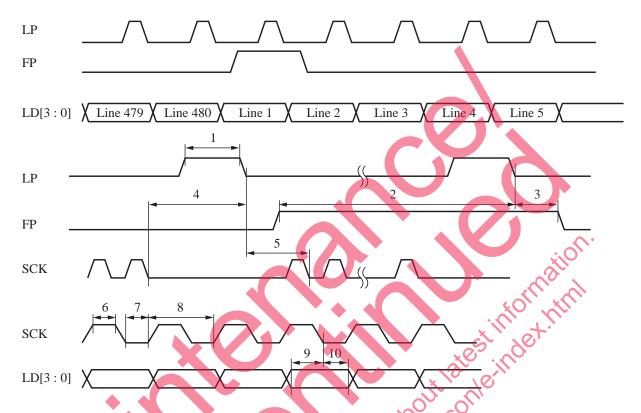

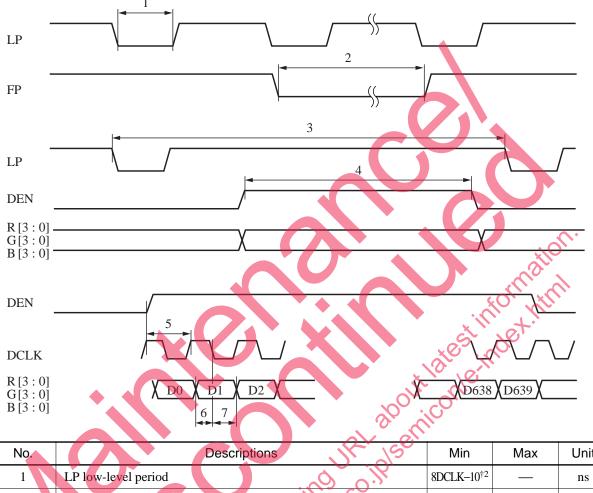

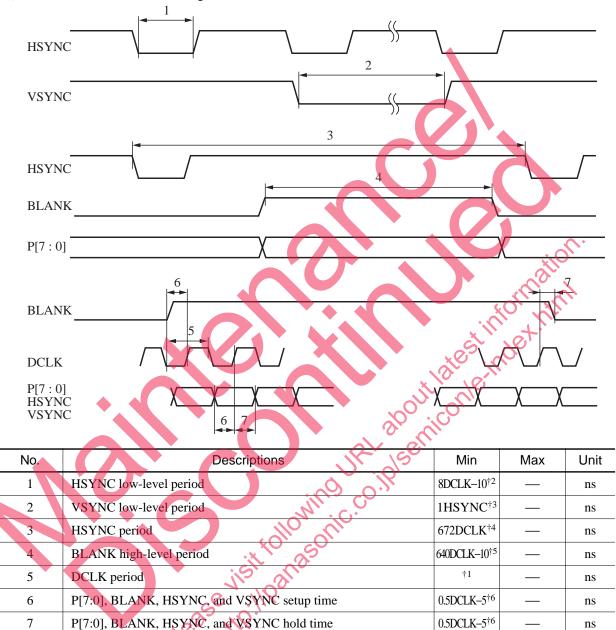

| LP<br>FP            | 0   |       | register address bit I signal to the RAMDAC.  Latch pulse Pulse output that indicates the latch timing for one line of data for an STN LCD panel. This output is used as the horizontal synchronizing signal when a TFT LCD panel is used or in external RAMDAC mode.  Frame pulse                                                                                                                                                                                                                                                                                      |

| DISP                | О   | 6//   | Pulse output that indicates the frame start for an STN LCD panel. This output is used as the vertical synchronizing signal when a TFT LCD panel is used or in external RAMDAC mode.  Display enable Display enable signal output to the LCD. This output is used as the blanking signal in external RAMDAC mode and as the display enable signal when a TFT                                                                                                                                                                                                             |

| SCK                 | 0   |       | LCD panel is used.  Data shift clock/Dot clock  This output is used as the dot clock output for a TFT LCD panel or in external RAMDAC mode. It is also used as the data shift clock output to an STN LCD panel.                                                                                                                                                                                                                                                                                                                                                         |

#### ■ Pin Descriptions (continued)

#### 5) LCD Related Pins (continued)

| Pin Name           | I/O | Level | Function                                                                                                                                                                     |

|--------------------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UD[7:0]<br>LD[7:0] | О   |       | Upper/Lower data 7:0 Display data outputs. In external RAMDAC mode LD[7:0] are used as the display data and UD[0:7] are used as the write data lines to the RAMDAC register. |

The table below shows the pin functions for each panel type.

|      | 1          |                | 1 71    |                                        |

|------|------------|----------------|---------|----------------------------------------|

| Pin  | TFT        | STN(1S)        | STN(2S) | External RAMDAC                        |

| DISP | DEN        | DISP           | DISP    | BLANK                                  |

| LP   | HSYNC      | LP             | LP      | HSYNC                                  |

| FP   | VSYNC      | FP             | FP      | VSYNC                                  |

| SCK  | DCLK       | SCK            | SCK     | DCLK                                   |

| UD7  | R3         | _              | UD7     | WD7                                    |

| UD6  | R2         | - \            | UD6     | WD6 COIL HULL                          |

| UD5  | R1         |                | UD5     | VSYNC DCLK WD7 WD6 WD5 WD4 WD3 WD2 WD2 |

| UD4  | R0         | <b>/ / / /</b> | UD4     | WD4                                    |

| UD3  | _          |                | UD3     | WD3                                    |

| UD2  |            |                | UD2     | WD2                                    |

| UD1  | G3         | _              | UD1     | WDI                                    |

| UD0  | G2         |                | UD0     | WD0                                    |

| LD7  | G1         | LD7            | LD7     | P7                                     |

| LD6  | <b>G</b> 0 | LD6            | LD6     | P6                                     |

| LD5  | <b>*</b>   | LD5            | LD5     | P5                                     |

| LD4  |            | LD4            | LD4     | P4                                     |

| LD3  | В3         | LD3            | LD3     | Р3                                     |

| LD2  | B2         | LD2            | DD2     | P2                                     |

| LD1  | B1         | ED1 .\\        | LD1     | P1                                     |

| LD0  | В0         | LDO            | LD0     | P0                                     |

|      |            |                |         |                                        |

Note) 1. The pins marked with a dash (—) in the table are set to the output state, and therefore should be left open.

<sup>2.</sup> In external RAMDAC mode, WD[7:0] are used as write data to the external RAMDAC register. Writes to an external RAMDAC are controlled with the BACKON, LOGICON, and LCDON pins.

## ■ Pin Descriptions (continued)

## 6) Chip Settings

| Pin Name        | I/O | Level  | Function                                                                                                                                                                                                                                                             |  |  |  |  |

|-----------------|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

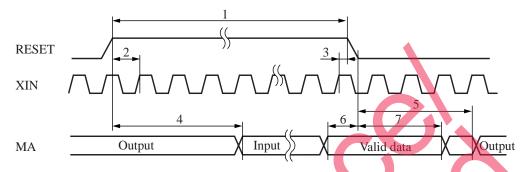

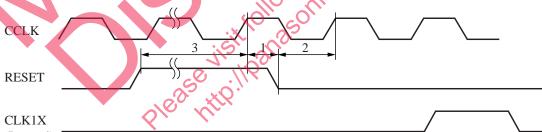

| RESET           | I   | 5 VTTL | RESET(ISA, 386, 486, RISC) When a high level is input to this pin, the chip is reset to its initial state. When 386 mode is used for the host type, this reset signal is also used for clock phase adjustment Note that this pin functions as an active-high signal. |  |  |  |  |

| MA[2:0]         | I   | CMOS   | HOST type The MA[2:0] pins are set to input mode during the reset period. When these pins are in input mode, they are used to decide the type of the connected host. Settings other than those listed in the table are not permitted.  MA[2:0]  Host type            |  |  |  |  |

|                 |     |        | 0 0 0 ISA                                                                                                                                                                                                                                                            |  |  |  |  |

|                 |     |        | 0 0 1 386SX                                                                                                                                                                                                                                                          |  |  |  |  |

|                 |     |        | 0 1 0 386DX                                                                                                                                                                                                                                                          |  |  |  |  |

|                 |     |        | 0 1 1 486                                                                                                                                                                                                                                                            |  |  |  |  |

|                 |     |        | 1 0 0 Reserved                                                                                                                                                                                                                                                       |  |  |  |  |

|                 |     |        | 1 0 1 RISC CPU (RDY# interface)                                                                                                                                                                                                                                      |  |  |  |  |

|                 |     |        | 1 0 RISC CPU (WAIT# interface)                                                                                                                                                                                                                                       |  |  |  |  |

|                 |     |        | 1 0 0 Reserved                                                                                                                                                                                                                                                       |  |  |  |  |

|                 |     |        | 15/0/10                                                                                                                                                                                                                                                              |  |  |  |  |

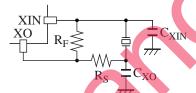

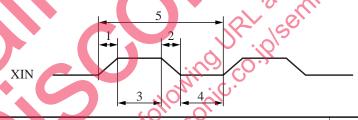

| XIN/XO          | 1/0 | CMOS   | Clock In/Out Chip clock input and output. Connect a crystal oscillator between these pins. The input frequency must be in the range 14 MHz to 33 MHz.                                                                                                                |  |  |  |  |

| EXTCLK          | ı   | CMOS   | External MCLK Used for IC testing. This pin must be held at the ground level during normal operation.                                                                                                                                                                |  |  |  |  |

| MINTEST<br>TEST | I   | CMOS   | Used for IC testing. These pin must be held at the ground level during normal operation.                                                                                                                                                                             |  |  |  |  |

| PLLTEST         | I/O |        | Used for PLL testing. This pin must be held at the ground level during normal operation.                                                                                                                                                                             |  |  |  |  |

## 7) Power Supply

| Pin Name | I/O | Level | Function                                      |

|----------|-----|-------|-----------------------------------------------|

| VDD      |     |       | Digital system power supply (3.3 V)           |

| GND      |     |       | Digital system power supply (GND)             |

| VREF5    |     |       | 5 V input pin power supply (4.75 V to 5.25 V) |

17

#### ■ Electrical Characteristics

#### 1. Absolute Maximum Ratings at $V_{SS} = 0 \text{ V}$

| Parameter                         | Symbol            | Rating                               | Unit   |

|-----------------------------------|-------------------|--------------------------------------|--------|

| Supply voltage                    | $V_{DD}$          | - 0.3 to +4.6                        | V      |

| 5 V reference voltage †1          | V <sub>REF5</sub> | - 0.3 to +5.7                        | V      |

| Input pin voltage (except TYPE*)  | V <sub>I</sub>    | - 0.3 to V <sub>DD</sub> +0.3        | V      |

| Input pin voltage (TYPE-A)        | V <sub>I5</sub>   | $-0.3 \text{ to } +6.0 ^{\dagger 2}$ | V      |

| Input pin voltage (TYPE-B)        | V <sub>I5</sub>   | $-0.3$ to $V_{REF5} + 0.3^{+2}$      | V      |

| Output pin voltage (except TYPE*) | Vo                | − 0.3 to V <sub>DD</sub> +0.3        | V      |

| Output pin voltage (TYPE-C)       | $V_{O5}$          | $-0.3$ to $V_{REF5} + 0.3^{+2}$      | V      |

| Output current (TYPE-HL1)         | I <sub>O</sub>    | ±3                                   | mA     |

| Output current (TYPE-HL2)         | I <sub>O</sub>    | ±6                                   | mA     |

| Output current (TYPE-HL4)         | I <sub>O</sub>    | ±12                                  | mA     |

| Output current (TYPE-HL8)         | I <sub>O</sub>    | ±24                                  | mA     |

| Power dissipation                 | $P_{\mathrm{D}}$  | 800                                  | mW     |

| Operating temperature             | T <sub>opr</sub>  | 0 to +70                             | 11 110 |

| Storage temperature               | T <sub>stg</sub>  | -55 to +150                          | √, °C  |

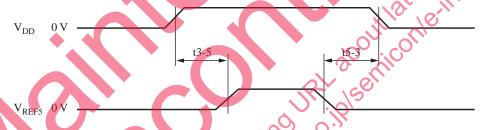

Note) 1. †1:The power application sequence must meet the following stipulations.

The periods t3-5 and t5-3 must be 0 or longer.

$V_{DD}$  and  $V_{REF5}$  must change smoothly.

If the periods t3-5 and t5-3 ever become negative,  $V_{REF5} - V_{DD}$  must be less than 3.6 V.

†2: When  $V_{DD} \le 1.4 \text{ V:} -0.3 \text{ V to } +4.6 \text{ V.}$

2. Type A pins: A20 to A22, SA0 to SA19, AEN, IQRD#, IQWR#, MEMR#, MEMW#, SBHE#, REFRESH#, RESET

Type B pins: SD0 to SD15, IOCHRDY#

Type C pins: SD0 to SD15, IOCHRDY#, IOCS16#, MEMCS16#

Type HL1 pins: LCDON, BACKON, EXTCLK

Type HL2 pins: MA0 to MA11, SD0 to SD15, WE#, LCAS#, UCAS#, RAS#, MD0 to MD15

MCLK, HDQM, MCS#, LOGICON

Type HL4 pins: FP, LD0 to LD7, LP, UD0 to UD7, SCK, DISP

Type HL8 pins: IOCS16#, MEMCS16#, IOCHRDY#

- 3. The absolute maximum ratings are limiting values under which the chip will not be destroyed. Operation is not guaranteed within these ranges.

- 4. All of the VDD, VSS, and VREF5 pins must connected directly, and by the shortest routes possible, to the power supply or ground, respectively.

- 5. The crystal oscillator element used must be evaluated thoroughly in advance using the oscillator cell for this device.

#### ■ Electrical Characteristics (continued)

## 2. Recommended Operating Conditions at $V_{\text{SS}} = 0 \text{ V}$

| Parameter             | Symbol            | Conditions  | Min  | Тур | Max  | Unit |

|-----------------------|-------------------|-------------|------|-----|------|------|

| Supply voltage        | $V_{DD}$          |             | 3.0  | 3.3 | 3.6  | V    |

| 5 V reference voltage | V <sub>REF5</sub> |             | 4.75 | 5.0 | 5.25 | V    |

| Ambient temperature   | Ta                |             | 0    | _   | 70   | °C   |

| Input rise time       | t <sub>r</sub>    |             | 0    | _   | 100  | ns   |

| Input fall time       | $t_{\mathrm{f}}$  |             | 0    | _   | 100  |      |

| Oscillator frequency  | f <sub>OSC</sub>  | 33 MHz Xtal | 15   |     | 33   | MHz  |

Note) The oscillator characteristics differ depending on the device used, external capacitances, and other conditions. Consult with the manufacturer of the oscillator element to determine appropriate circuit values.

# 3. DC Characteristics at $V_{DD} = 3.0$ V to 3.6 V, $V_{REF5} = 4.75$ V to 5.25 V, $V_{SS} = 0$ V, $f_{TEST} = 20$ MHz, $T_a = 0$ °C to 70°C

| Parameter                                          | Symbol             | Conditions                                                                                                                                                                                                                                                                                                                          | Min | Тур  | Max | Unit |

|----------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Quiescent current                                  | I <sub>DDS</sub>   | $V_{I}$ (pull up) = OPEN<br>$V_{I}$ (pull down) = OPEN<br>$V_{I}$ (xIN) = $V_{DD}^{\dagger}$<br>Apply either the $V_{SS}$ or $V_{DD}$<br>level at the same time to all<br>other input pins and I/O pins<br>in the high-impedance state.<br>$V_{DD} = 3.6 \text{ V}$<br>$V_{REF5} = 5.25 \text{ V}$<br>$T_{a} = 25 ^{\circ}\text{C}$ |     | PUT. | 30  | μА   |

| 5 V reference supply (VREF5) input leakage current | I <sub>REF</sub>   | $V_{DD} = 3.6 \text{ V}$ $V_{REFS} = 5.25 \text{ V}$                                                                                                                                                                                                                                                                                | -20 | _    | 20  | μΑ   |

| Operating supply current                           | CI <sub>DD0</sub>  | $V_I = V_{DD}$ or $V_{SS}$<br>f = 20 MHz, output pins open<br>$V_{DD} = 3.3$ V<br>$V_{REF5} = 5.0$ V                                                                                                                                                                                                                                | _   | _    | 80  | mA   |

| Operating supply current<br>Standby mode           | $I_{\mathrm{DDI}}$ | $V_I = V_{DD}$ or $V_{SS}$<br>f = 20 MHz, output pins open<br>$V_{DD} = 3.3$ V<br>$V_{REF5} = 5.0$ V<br>With the LSI set to standby<br>mode via register settings.                                                                                                                                                                  | _   | _    | 35  | mA   |

Note)  $\dagger$ :  $V_{DD}$  applied to the XIN pin is another power supply than that used in  $I_{DD}$  measurement.

3. DC Characteristics at  $V_{DD}=3.0~V$  to 3.6 V,  $V_{REF5}=4.75~V$  to 5.25 V,  $V_{SS}=0~V$ ,  $f_{TEST}=20~MHz$ ,  $T_a=0$ °C to 70°C (continued)

| Parameter                                | Symbol                                                       | Conditions                                                                                                                                                                                                                                                | Min                   | Тур         | Max                 | Unit |  |  |  |

|------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------|---------------------|------|--|--|--|

| Operating supply current<br>Suspend mode | $I_{DD2}$                                                    | $\begin{split} &V_{I} = V_{DD} \text{ or } V_{SS} \\ &f = 20 \text{ MHz, output pins open} \\ &V_{DD} = V_{DDPLL} = 3.3 \text{ V} \\ &V_{REF5} = 5.0 \text{ V} \\ &\text{With the LSI set to standby} \\ &\text{mode via register settings.} \end{split}$ |                       | -           | 10                  | mA   |  |  |  |

| Operating supply current<br>Sleep mode   | $I_{\mathrm{DD3}}$                                           | $\begin{split} &V_{I} = V_{DD} \text{ or } V_{SS} \\ &f = 0 \text{ MHz, output pins open} \\ &V_{DD} = 3.3 \text{ V} \\ &V_{REF5} = 5.0 \text{ V} \\ &\text{With the LSI set to suspend} \\ &\text{mode via register settings.} \end{split}$              |                       | 0           | 3                   | mA   |  |  |  |

| Input with pull-down resisitor (C        | CMOS leve                                                    | el): TEST, MINTEST                                                                                                                                                                                                                                        |                       |             | John,               |      |  |  |  |

| High-level input voltage                 | $V_{IH}$                                                     |                                                                                                                                                                                                                                                           | $V_{DD} \times 0.7$   |             | $V_{DD}$            | V    |  |  |  |

| Low-level input voltage                  | $V_{IL}$                                                     |                                                                                                                                                                                                                                                           | 0                     | -101        | $V_{DD} \times 0.3$ | V    |  |  |  |

| Pull-down resistor                       | $R_{IL}$                                                     | $V_{\rm I} = V_{\rm DD} = 3.3 \text{ V}$                                                                                                                                                                                                                  | 10                    | <i>c</i> 30 | <b>6</b> 90         | kΩ   |  |  |  |

| Input leakage current                    | $I_{LIL}$                                                    | $V_I = V_{SS}$                                                                                                                                                                                                                                            |                       |             | ±10                 | μΑ   |  |  |  |

| Input (TTL level): A20 to A22,           | SA0 to SA                                                    | 19, AEN, IORD#, IOWR#, MI                                                                                                                                                                                                                                 | EMR#, MEI             | MW#, SBI    | HE#, REFR           | ESH# |  |  |  |