Fixed, Quad, Voltage Output, Single or Dual Supply 8-Bit Digital-to-Analog Converter

### **FEATURES**

- MPS Pioneered Segmented DAC Approach

- Four 8-Bit DACs with Buffer Amplifiers

- Bipolar Amplifier Inputs for Low Noise and Drift Process Controls

- **Operates with Single or Dual Supplies**

- μP Compatible (95ns WR)

- No External Adjustments Required

- **Power-on-Reset Function**

- Specified for 5 to 15 V Operation

- **ESD Protection: 2000 Volts Minimum**

- Latch-Up Proof

- Octal Available: MP7228

### **APPLICATIONS**

- Function Generators

- **Automatic Test Equipment**

### **BENEFITS**

- Reduced Board Space; Lower System Cost

- Reduced System Errors due to Excellent DAC-to-DAC **Matching and Tracking**

- Easy to Design with Microprocessors

- Stable, High Reliability through Advanced Processing

- Lower 1/f Noise Increases Useful Dynamic Range

### GENERAL DESCRIPTION

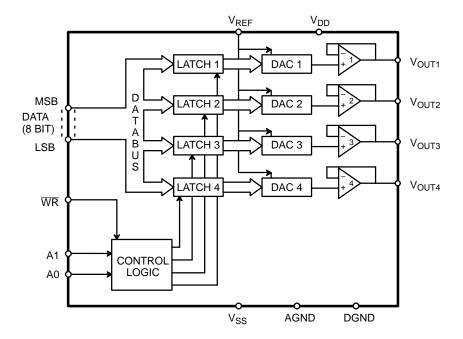

The MP7226 contains four 8-bit voltage-output Digital-to-Analog Converters, with BiCMOS output buffer amplifiers and interface logic on a monolithic chip. Separate on-chip latches logic is speed compatible with most 8-bit microprocessors. All digital inputs are TTL/CMOS(5V) compatible.

The MP7226 is manufactured using advanced thin film resistors on a double metal BiCMOS process. The MP7226 incorporates a unique bit decoding technique yielding lower glitch, higher speed and excellent accuracy over temperature and time. The MP7226 maintains 8-Bit accuracy over the full operating temperature range without laser trim or external adjustments.

### SIMPLIFIED BLOCK DIAGRAM

### ORDERING INFORMATION

| Package<br>Type | Temperature<br>Range | Part No.  | INL<br>(LSB) | DNL<br>(LSB) | Full Scale<br>Error (LSB) |

|-----------------|----------------------|-----------|--------------|--------------|---------------------------|

| Plastic Dip     | –40 to +85°C         | MP7226KN  | 1            | ±1/2         | ±1                        |

| Plastic Dip     | –40 to +85°C         | MP7226LN* | 1/2          | ±1/2         | ±1/2                      |

| PLCC            | –40 to +85°C         | MP7226KP  | 1            | ±1/2         | ±1                        |

| PLCC            | –40 to +85°C         | MP7226LP* | 1/2          | ±1/2         | ±1/2                      |

| SOIC            | –40 to +85°C         | MP7226KS  | 1            | ±1/2         | ±1                        |

| SOIC            | –40 to +85°C         | MP7226LS* | 1/2          | ±1/2         | ±1/2                      |

<sup>\*</sup>Contact factory for availability.

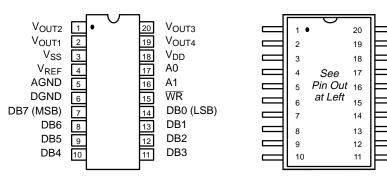

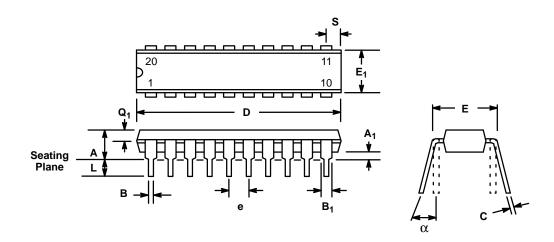

### **PIN CONFIGURATIONS**

See Packaging Section for Package Dimensions

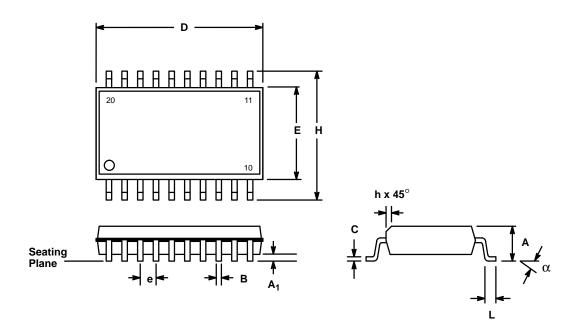

20 Pin PDIP (0.300") 20 Pin SOIC (Jedec, 0.300") S20

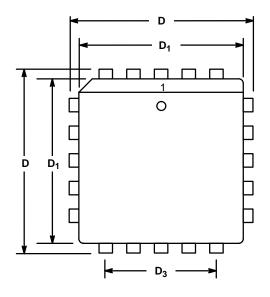

20 Pin PLCC P20

### **PIN OUT DEFINITIONS**

| PIN NO. | NAME              | DESCRIPTION                         |

|---------|-------------------|-------------------------------------|

| 1       | V <sub>OUT2</sub> | DAC 2 Voltage Output                |

| 2       | V <sub>OUT1</sub> | DAC 1 Voltage Output                |

| 3       | $V_{SS}$          | Negative Power Supply (0 V to –5 V) |

| 4       | $V_{REF}$         | Reference Input Voltage             |

| 5       | AGND              | Analog Ground                       |

| 6       | DGND              | Digital Ground                      |

| 7       | DB7               | Data Input Bit 7 (MSB)              |

| 8       | DB6               | Data Input Bit 6                    |

| 9       | DB5               | Data Input Bit 5                    |

| 10      | DB4               | Data Input Bit 4                    |

| PIN N | 0. | NAME              | DESCRIPTION                         |

|-------|----|-------------------|-------------------------------------|

| 11    |    | DB3               | Data Input Bit 3                    |

| 12    |    | DB2               | Data Input Bit 2                    |

| 13    |    | DB1               | Data Input Bit 1                    |

| 14    |    | DB0               | Data Input Bit 0 (LSB)              |

| 15    |    | WR                | Write (Active Low)                  |

| 16    |    | A1                | DAC Address Bit 1                   |

| 17    |    | A0                | DAC Address Bit 0                   |

| 18    |    | $V_{DD}$          | Positive Power Supply (+5 to +15 V) |

| 19    |    | V <sub>OUT4</sub> | DAC 4 Voltage Output                |

| 20    |    | V <sub>OUT3</sub> | DAC 3 Voltage Output                |

Rev. 2.00

## **ELECTRICAL CHARACTERISTICS**

Single or Dual Supply Operation (V<sub>DD</sub> = +10.8 V to 16.5 V, V<sub>SS</sub> = 0 V or –5 V  $\pm$ 10%, AGND = 0 V, DGND = 0 V, V<sub>REF</sub> = +2 V to +10 V, R<sub>L</sub> = 2k $\Omega$ , C<sub>L</sub> = 100pF unless otherwise noted)

| Parameter                                                                                              | Symbol                                                   | Min    | 25°C<br>Typ | Max                 | Tmin to<br>Min | Tmax<br>Max         | Units              | Test Conditions/Comments                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------|-------------|---------------------|----------------|---------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| STATIC PERFORMANCE                                                                                     |                                                          |        |             |                     |                |                     |                    |                                                                                                                                                          |

| Resolution (All Grades)                                                                                | N                                                        | 8      |             |                     | 8              |                     | Bits               |                                                                                                                                                          |

| Integral Non-Linearity<br>(Relative Accuracy)<br>K                                                     | INL                                                      |        |             | 1                   |                | 1                   | LSB                | End Point Linearity Spec                                                                                                                                 |

| L Differential Non-Linearity K L                                                                       | DNL                                                      |        |             | 1/2<br>±1/2<br>±1/2 |                | 1/2<br>±3/4<br>±3/4 | LSB                | All grades monotonic over full temperature range.                                                                                                        |

| Total Unadjusted Error <sup>2</sup> K L                                                                |                                                          |        |             | ±2<br>±1            |                | ±2<br>±1            | LSB                | $V_{DD}$ = 15 V ±10%, $V_{REF}$ = +10 V                                                                                                                  |

| Full Scale Error <sup>3</sup> K L                                                                      |                                                          |        |             | ±1<br>±1/2          |                | ±1<br>±1/2          | LSB                | $V_{REF}$ = +10 V typ. Tempco is 5 ppm/°C                                                                                                                |

| Zero Code Error<br>K<br>L                                                                              |                                                          |        |             | ±20<br>±15          |                | ±30<br>±20          | mV                 | TA = 25°C typ. Tempco is $30\mu V/^{\circ}C$                                                                                                             |

| Output Load Resistance                                                                                 |                                                          | 2      |             |                     | 2              |                     | kΩ                 | V <sub>OUT</sub> = +10 V                                                                                                                                 |

| DYNAMIC PERFORMANCE <sup>4</sup>                                                                       |                                                          |        |             |                     |                |                     |                    |                                                                                                                                                          |

| Voltage Output Slew Rate<br>Voltage Output Settling Time                                               |                                                          | 2      | 4           | 4                   | 2              | 5                   | V/μs<br>μs         | $V_{REF}$ = +10 V; Settling Time to $\pm 1/2$ LSB                                                                                                        |

| Digital Feedthrough                                                                                    |                                                          |        | 25          |                     |                |                     | nVs                | Code transition all 0s to all 1s                                                                                                                         |

| Digital Crosstalk <sup>5</sup>                                                                         |                                                          |        | 25          |                     |                |                     | nVs                | $V_{REF} = 0 \text{ V}, \overline{WR} = V_{DD}$<br>Code transition all 0s to all 1s<br>$V_{REF} = +10 \text{ V}, \overline{WR} = 0 \text{ V}$            |

| REFERENCE INPUT                                                                                        |                                                          |        |             |                     |                |                     |                    |                                                                                                                                                          |

| Reference Input Range <sup>1</sup> Reference Input Resistance Reference Input Capacitance <sup>4</sup> | R <sub>IN</sub>                                          | 1<br>2 | 500         | 10                  | 1<br>2         | 10                  | V<br>kΩ<br>pF      | Limitation: V <sub>REF</sub> – V <sub>SS</sub> < 11 V<br>Min R <sub>IN</sub> at Code 149 <sub>10</sub><br>Occurs when all DACs are loaded<br>with all 1s |

| AC Feedthrough                                                                                         |                                                          |        | -70         |                     |                |                     | dB                 | V <sub>REF</sub> = 10 kHz, 5 V p-p sinewave                                                                                                              |

| DIGITAL INPUTS                                                                                         |                                                          |        |             |                     |                |                     |                    |                                                                                                                                                          |

| Input High Voltage Input Low Voltage Input Leakage Current Input Capacitance <sup>4</sup> Input Coding | V <sub>INH</sub><br>V <sub>INL</sub><br>I <sub>LKG</sub> | 2.4    |             | 0.8<br>±1<br>8      | 2.4            | 0.8<br>±1<br>8      | V<br>V<br>μA<br>pF | $V_{IN} = 0 \text{ V or } V_{DD}$ Binary                                                                                                                 |

# **ELECTRICAL CHARACTERISTICS (CONT'D)**

| Parameter                                                                                                                                  | Symbol                                                                          | Min                      | 25°C<br>Typ | Max                      | Tmin to<br>Min            | Tmax<br>Max              | Units          | Test Conditions/Comments                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------|-------------|--------------------------|---------------------------|--------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER SUPPLY                                                                                                                               |                                                                                 |                          |             |                          |                           |                          |                |                                                                                                                                                                                                     |

| V <sub>DD</sub> Range<br>V <sub>SS</sub> Range (Dual Supplies) <sup>8</sup><br>I <sub>DD</sub><br>I <sub>SS</sub> (Dual Supplies)          |                                                                                 | 10.8<br>0                |             | 16.5<br>-5.5<br>12<br>10 | 10.8<br>0                 | 16.5<br>-5.5<br>14<br>12 | V<br>V<br>mA   | For specified performance For specified performance Outputs unloaded; V <sub>IN</sub> =V <sub>INL</sub> or V <sub>INH</sub> Outputs unloaded; V <sub>IN</sub> =V <sub>INL</sub> or V <sub>INH</sub> |

| SWITCHING<br>CHARACTERISTICS <sup>4, 6, 7</sup>                                                                                            |                                                                                 |                          |             |                          |                           |                          |                |                                                                                                                                                                                                     |

| Address to WR Setup Time, t1 Address to WR Hold Time, t2 Data Valid to WR Setup Time, t3 Data Valid to WR Hold Time, t4 WR Pulse Width, t5 | tas<br>t <sub>AH</sub><br>t <sub>DS</sub><br>t <sub>DH</sub><br>t <sub>WR</sub> | 0<br>0<br>70<br>10<br>95 |             |                          | 0<br>0<br>95<br>10<br>120 |                          | ns<br>ns<br>ns |                                                                                                                                                                                                     |

### NOTES:

- <sup>1</sup> V<sub>OUT</sub> must be less than V<sub>DD</sub> by 3.5 V to ensure correct operation.

- Total Unadjusted Error includes zero code error, relative accuracy and full-scale error.

- <sup>3</sup> Calculated after zero code error has been adjusted out.

- Sample tested at 25°C to ensure compliance.

- 5 The glitch impulse transferred to the output of one converter (not adjusted) due to a change in the digital input code to another addressed converter.

- All input rise and fall times are measured from 10% to 90% of +5 V,  $t_R = t_F = 5$  ns.

- 7 Timing measurement reference level is  $(V_{INH} + V_{INL})/2$ .

Specifications are subject to change without notice

### **ELECTRICAL CHARACTERISTICS**

Single & Dual  $\pm 5$  V Supply Operation (V<sub>DD</sub> = +5 V  $\pm 5$ %, V<sub>SS</sub> = 0 V to -5 V  $\pm 10$ %, V<sub>REF</sub> = +1.25 V, AGND = 0 V, DGND = 0 V, R<sub>L</sub> = 2k $\Omega$ , C<sub>L</sub> = 100pF unless otherwise noted)

| Parameter                                                                                                | Symbol                                                   | Min    | 25°C<br>Typ | Max            | Tmin to<br>Min | Tmax<br>Max    | Units               | Test Conditions/Comments                                                                                                                       |

|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------|-------------|----------------|----------------|----------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| STATIC PERFORMANCE                                                                                       |                                                          |        |             |                |                |                |                     |                                                                                                                                                |

| Resolution (All Grades)                                                                                  | N                                                        | 8      |             |                | 8              |                | Bits                |                                                                                                                                                |

| Integral Non-Linearity<br>(Relative Accuracy)<br>K                                                       | INL                                                      |        |             | 2              |                | 2              | LSB                 | End Point Linearity Spec                                                                                                                       |

| L                                                                                                        |                                                          |        |             | 1              |                | 1              |                     |                                                                                                                                                |

| Differential Non-Linearity  K L                                                                          | DNL                                                      |        |             | ±1<br>±1       |                | ±1<br>±1       | LSB                 | All grades monotonic over full temperature range.                                                                                              |

| Total Unadjusted Error <sup>2</sup>                                                                      |                                                          |        |             | ±4             |                |                | LSB                 | $V_{DD}$ = 5 V $\pm$ 5%, $V_{REF}$ = 1.25 V                                                                                                    |

| Full Scale Error <sup>3</sup> K L                                                                        |                                                          |        |             | ±4<br>±2       |                | ±4<br>±2       | LSB                 | V <sub>REF</sub> = +1.25 V                                                                                                                     |

| Zero Code Error                                                                                          |                                                          |        |             | ±20            |                |                | mV                  |                                                                                                                                                |

| Output Load Resistance                                                                                   |                                                          | 2      |             |                |                |                | kΩ                  | V <sub>OUT</sub> = +10 V                                                                                                                       |

| DYNAMIC PERFORMANCE <sup>4</sup>                                                                         |                                                          |        |             |                |                |                |                     |                                                                                                                                                |

| Voltage Output Slew Rate<br>Voltage Output Settling Time                                                 |                                                          | 2      | 4           | 4              |                |                | V/μs<br>μs          | $V_{REF}$ = +1.25 V; Settling Time to +1/2 LSB                                                                                                 |

| Digital Feedthrough                                                                                      |                                                          |        | 25          |                |                |                | nVs                 | Code transition all 0s to all 1s                                                                                                               |

| Digital Crosstalk <sup>5</sup>                                                                           |                                                          |        | 25          |                |                |                | nVs                 | $V_{REF} = 0 \text{ V}, \overline{WR} = V_{DD}$ Code transition all 0s to all 1s $V_{REF} = +1.25 \text{ V}, \overline{WR} = 0 \text{ V}$      |

| REFERENCE INPUT                                                                                          |                                                          |        |             |                |                |                |                     |                                                                                                                                                |

| Reference Input Range Reference Input Resistance Reference Input Capacitance <sup>4</sup> AC Feedthrough | R <sub>IN</sub>                                          | 1<br>2 | 500<br>-70  | 1.6            | 1<br>2         | 1.6            | V<br>kΩ<br>pF<br>dB | V <sub>OUT</sub> must be < V <sub>DD</sub> by 3.2V  Occurs when all DACs are loaded with all 1s  V <sub>REF</sub> = 10 kHz, 1/2 V p-p sinewave |

| DIGITAL INPUTS                                                                                           |                                                          |        |             |                |                |                |                     |                                                                                                                                                |

| Input High Voltage Input Low Voltage Input Leakage Current Input Capacitance <sup>4</sup> Input Coding   | V <sub>INH</sub><br>V <sub>INL</sub><br>I <sub>LKG</sub> | 2.4    |             | 0.8<br>±1<br>8 | 2.4            | 0.8<br>±1<br>8 | V<br>V<br>μA<br>pF  | V <sub>IN</sub> = 0 V or V <sub>DD</sub><br>Binary                                                                                             |

### **ELECTRICAL CHARACTERISTICS (CONT'D)**

| Parameter                                                                                                                                  | Symbol                                                                                      | Min                     | 25°C<br>Typ | Max            | Tmin to<br>Min      | Tmax<br>Max    | Units          | Test Conditions/Comments                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------|-------------|----------------|---------------------|----------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER SUPPLY                                                                                                                               |                                                                                             |                         |             |                |                     |                |                |                                                                                                                                                                                       |

| V <sub>DD</sub> Range<br>I <sub>DD</sub><br>I <sub>SS</sub> (Dual Supplies)                                                                |                                                                                             | 4.75                    |             | 5.25<br>8<br>6 | 4.75                | 5.25<br>8<br>6 | V<br>mA        | For specified performance<br>Outputs unloaded;<br>V <sub>IN</sub> =V <sub>INL</sub> or V <sub>INH</sub><br>Outputs unloaded;<br>V <sub>IN</sub> =V <sub>INL</sub> or V <sub>INH</sub> |

| SWITCHING<br>CHARACTERISTICS <sup>4, 6, 7</sup>                                                                                            |                                                                                             |                         |             |                |                     |                |                |                                                                                                                                                                                       |

| Address to WR Setup Time, t1 Address to WR Hold Time, t2 Data Valid to WR Setup Time, t3 Data Valid to WR Hold Time, t4 WR Pulse Width, t5 | t <sub>AS</sub><br>t <sub>AH</sub><br>t <sub>DS</sub><br>t <sub>DH</sub><br>t <sub>WR</sub> | 0<br>0<br>70<br>0<br>95 |             |                | 0<br>0<br>95<br>120 |                | ns<br>ns<br>ns |                                                                                                                                                                                       |

### NOTES:

- V<sub>OUT</sub> must be less than V<sub>DD</sub> by 3.5 V to ensure correct operation.

- Total Unadjusted Error includes zero code error, relative accuracy and full-scale error.

- <sup>3</sup> Calculated after zero code error has been adjusted out.

- Sample tested at 25°C to ensure compliance.

- 5 The glitch impulse transferred to the output of one converter (not adjusted) due to a change in the digital input code to another addressed converter.

- All input rise and fall times are measured from 10% to 90% of +5 V,  $t_R = t_F = 5$  ns.

- Timing measurement reference level is (V<sub>INH</sub> + V<sub>INL</sub>)/2.

### Specifications are subject to change without notice

# ABSOLUTE MAXIMUM RATINGS (TA = +25°C unless otherwise noted)<sup>1, 2</sup>

| V <sub>DD</sub> to AGND, DGND 0 to +17 V   | Storage Temperature65°C to +150°C               |

|--------------------------------------------|-------------------------------------------------|

| Digital Input Voltage to DGND              | Lead Temperature (Soldering, 10 seconds) +300°C |

| V <sub>SS</sub> to AGND, DGND +0.5 to -7 V | Package Power Dissipation Rating to 75°C        |

| AGND to DGND                               | PDIP, SOIC, PLCC 900mW                          |

| (Functionality Guaranteed <u>+</u> 0.5 V)  | Derates above 75°C                              |

### NOTES:

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation at or above this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

conditions for extended periods may affect device reliability.

Any input pin which can see a value outside the absolute maximum ratings should be protected by Schottky diode clamps (HP5082-2835) from input pin to the supplies. *All inputs have protection diodes* which will protect the device from short transients outside the supplies of less than 100mA for less than 100µs.

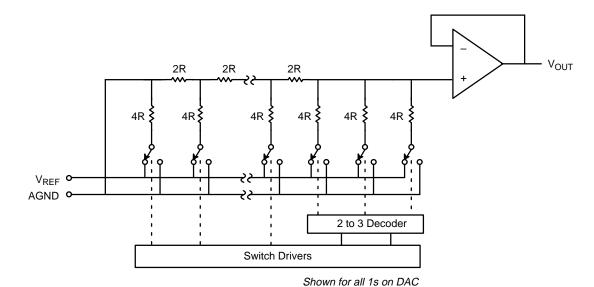

### D/A CONVERTER SECTION

The MP7226 contains four matched, 8-bit, voltage-mode Digital-to-Analog Converters (DACs) which incorporate an MPS pioneered unique bit decoding technique. This decoding scheme reduces the maximum binary weight carried by any resistor switch, reducing the accuracy required of the switches and resistor network.

In the MP7226, the first three MSBs are decoded into three equal current sources, each contributing 25% of the full scale output current.

Decoding two bits to three, a 1% change in any one of the converter's three decoded current sources affects the output by no more than 0.25% of full scale, compared with 0.5% in a conventional R-2R type CMOS DAC.

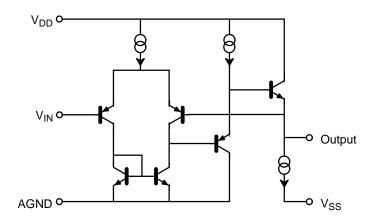

The output voltages have the same polarity as the reference voltage, allowing single supply operation. The voltage reference range is from +2V to +10V. Each DAC uses a highly-stable, thin-film, ladder network and high-speed NMOS switches. *Figure 1.* shows a simplified circuit diagram for one channel.

Figure 1. Simplified D/A Circuit Diagram

### **V<sub>REF</sub>** Input

The V<sub>REF</sub> and AGND are common to all four DACs and set the full-scale output. The input impedance of the V<sub>REF</sub> pin is the parallel combination of the four individual DAC reference impedances and is code dependent. This impedance varies from  $2k\Omega$  to  $500k\Omega$ . Therefore, it is very important that the external reference source output impedance is low enough so that its output voltage will not be affected by the varying digital code. Due to transient currents at the V<sub>REF</sub> input during digital code changes, a  $0.1\mu F$  or greater decoupling capacitor on that V<sub>REF</sub> input is recommended. The input capacitance at the V<sub>REF</sub> pin is also code dependent and typically varies from less than 120pF to 350pF.

Each V<sub>OUT</sub> voltage can be represented by a digitally programmable voltage source using the following expression :

$$V_{OUT} = Dn X V_{REF}/256$$

where Dn is the decimal equivalent to the digital input code and can vary from 0 to 255.

### **Output Buffer Amp**

Each D/A converter output is buffered by a unity gain noninverting BiCMOS amplifier which has slew rate greater than 2 V/  $\mu s$ . The output buffer settles to  $\pm 1/2$  LSB in less than 4 $\mu s$  when driving a load of 2k $\Omega$  in parallel with 100pF with a full scale transition from 0V to +10V or from +10V to 0V . The buffers can drive 2k $\Omega$  and 500pF to 10V levels without oscillation.

A simplified circuit diagram of the output buffer is shown in Figure 2. The Input stage is provided by BiCMOS PNP transistors with resulting lower input offset voltage, offset voltage drift over time and noise when compared to MOS process. The amplifier output stage uses a substrate NPN bipolar device to provide a low output impedance, high-output current capability.

The MP7226 is specified for single or dual power supply operation, with only the buffer amplifier outputs using  $V_{SS}$  supply current . Operating the MP7226 from dual supplies will improve the negative going output settling time near ground. In dual supply voltage operation , the output amplifier can sink  $500\mu A$  when  $V_{OUT}=0~V.$

T@M

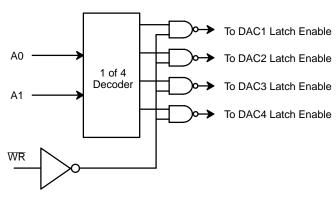

Figure 3. Input Control Logic

Figure 2. Simplified Output Buffer Amplifiers

The amplifiers outputs may be shorted to ground. However, the power dissipation of the package should not exceed the maximum limit.

### **Digital Inputs**

All of the digital inputs to this DAC maintain TTL level interface compatibility and can also be driven directly with 5V CMOS logic inputs. The digital inputs are ESD protected to a rating of 2000 volts.

### **Digital Interface Logic**

The MP7226 allows direct interface to most microprocessor buses without additional interface circuitry.

Figure 3. shows the input control logic circuit diagram and Table 1. shows the control logic truth table and operation for  $\overline{WR}$ , A1, A0. The address lines A0, and A1 determine which DAC will accept the input data. The  $\overline{WR}$  input determines whether the selected DAC is transparent (output follows the input), latched, or no operation. The  $\overline{WR}$  input will also inhibit power on reset of the DAC latches to 0, if its initial state = 0 after 5 µs of power.

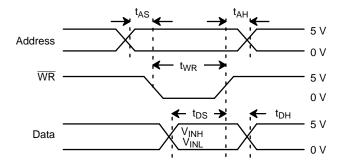

Figure 4. shows the write cycle timing diagram. When the  $\overline{WR}$  signal is low, the input latch of the selected DAC is transparent, and the DAC's output corresponds to the value present on the data bus. On some data buses, data is not always valid for the entire period that the  $\overline{WR}$  signal is low and can cause unwanted data at the output. Ensuring that the write pulse ( $\overline{WR}$ ) conforms to the data hold time, (t4) spec will prevent this problem.

| WR | A1 | A0 | Operation                            |

|----|----|----|--------------------------------------|

| Н  | Х  | Х  | No Operation;<br>Device Not Selected |

| L  | L  | L  | DAC 1 Transparent                    |

| ₹  | L  | L  | DAC 1 Latched                        |

| L  | L  | Н  | DAC 2 Transparent                    |

| L  | Н  | L  | DAC 3 Transparent                    |

| L  | Н  | Н  | DAC 4 Transparent                    |

|    |    |    |                                      |

Table 1. Truth Table

NOTE: When the  $\overline{WR}$  signal is low, the input latch of the selected DAC is transparent and any invalid data at this time will cause erroneous output.

Figure 4. Write Cycle Timing Diagram

### APPLICATIONS INFORMATION

### **Power On Reset**

At power up, all inputs are reset to 0 V if  $\overline{WR} = 1$ . For  $\overline{WR} = 0$ , the addressed DAC will receive input data.

### **Power Supply**

The MP7226 can operate with either a single or dual power supply. Improved zero-code settling error can be obtained by using dual power supplies. The dual power supply specifications are a positive supply (V\_DD) range of +10.5V to +16.5V, and a –5V supply (V\_SS) . The single power supply specifications are a positive supply (V\_DD) range of +10.5V to +16.5V, or range of +4.75V to 5.5V . The specified reference voltage (V\_REF) range under these conditions is from +2V to V\_DD—4V. For those applications requiring +10V at the output (V\_REF = +10V), V\_DD must be +14V minimum to meet data sheet limits . 8-bit performance is guaranteed for single supply operation (V\_SS = 0V); however, zero code output sink capability is improved with V\_SS = –5V. For adequate DAC and Buffer operation, V\_REF must always be below V\_DD by at least 3.5V.

### **Power Supply Decoupling**

The Power Supplies used with the MP7226 should be well regulated and filtered. Local power supply decoupling consisting of a  $10\mu F$  tantalum capacitor in parallel with a  $0.01\mu F$  ceramic is recommended. The decoupling capacitors should be connected between the V<sub>DD</sub> and AGND, and between V<sub>SS</sub> and AGND if V<sub>SS</sub> = –5V.

### **Unipolar Output Operation**

In this configuration, the reference voltage is the same polarity as the output voltage. Since the reference voltage must always be positive with respect to GND, the output can only be 0 or positive.

*Table 2.* shows the code relationship for the part in unipolar operation

| Digital Input   | Analog Output, V <sub>OUT</sub>                                  |

|-----------------|------------------------------------------------------------------|

| 1111111         | $+ V_{REF} (\frac{255}{256})$                                    |

| 10000001        | $+ V_{REF} (\frac{129}{256})$                                    |

| 10000000        | $+ V_{REF} \left( \frac{128}{256} \right) = + \frac{V_{REF}}{2}$ |

| 0 1 1 1 1 1 1 1 | $+ V_{REF} (\frac{127}{256})$                                    |

| 00000001        | $+ V_{REF} (\frac{1}{256})$                                      |

| 00000000        | 0 V                                                              |

Note:

$$1 LSB = (2^{-8}) (V_{REF}) = \frac{1}{256} (V_{REF})$$

Table 2. Unipolar Code Table

| Digital Input | Analog Output                           |

|---------------|-----------------------------------------|

| 11111111      | $+ V_{REF} (\frac{127}{128})$           |

| 10000001      | $+ V_{REF} (\frac{1}{128})$             |

| 10000000      | 0 V                                     |

| 01111111      | $-V_{REF} (\frac{1}{128})$              |

| 00000001      | $-V_{REF} (\frac{127}{128})$            |

| 00000000      | $-V_{REF} (\frac{128}{128}) = -V_{REF}$ |

Table 3. Bipolar Code Table

# V<sub>REF</sub> V<sub>OUT</sub> V<sub>OUT</sub> V<sub>OUT</sub> V<sub>OUT</sub> V<sub>OUT</sub> V<sub>OUT</sub> V<sub>SS</sub> AGND

$$\begin{split} &V_{OUT} = D_n \; X \; V_{REF} \; X \; (1+R2/R1) - V_{REF} \; X \; R2/R1 \\ &\text{if } R1 = R2 \\ &V_{OUT} = V_{REF} \; X \; (2D_n - 1) \\ &\text{Where } D_n \; \text{is the digital input code and can vary from 0 to 255} \end{split}$$

Figure 5. Bipolar Output Circuit

### **Bipolar Binary Operation**

The Bipolar Mode configuration for each DAC requires one external op-amp and two resistors per channel.

Figure 5. shows a typical Bipolar Operation circuit using the MP7226. Table 3. shows the code relationship for the circuit of Figure 5. assuming R1 = R2.

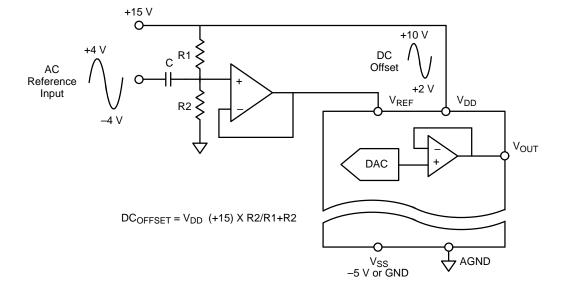

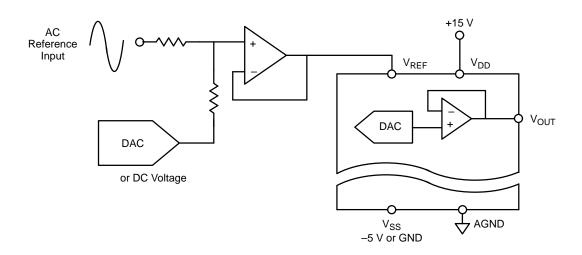

### **AC Reference Signal**

An AC signal can be applied to the reference of the MP7226 for multiplying capability within the upper (+10V) and lower (+2V) limits of the reference voltage input, with either single or dual supplies. This signal must be level shifted or AC coupled with proper bias level before being applied to the reference input. Figure 6. shows techniques for applying an AC signal to the MP7226. Since all four DACs share a common reference, they will all share this AC modulated reference. Input frequencies up to 50kHz will typically be distorted less than 0.1%.

Figure 6. AC Reference Input Signal Circuit (AC Couple)

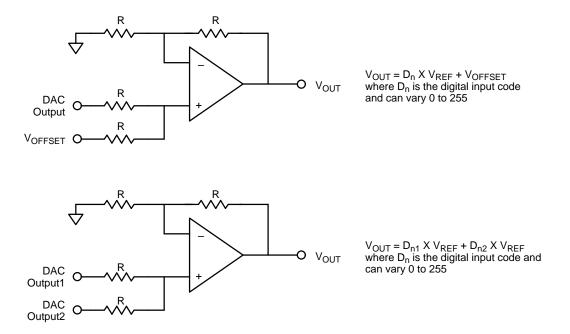

Figure 7. Digitally Programmable Offset Adjustment Circuits

Figure 8. Digitally Programmable AC Reference Input Signal Circuit (DC Couple)

### **Offsetting DAC Outputs**

Figure 7. shows examples of offset circuits.

### **DAC** offset effects

When using the device in single supply applications, and minimum reference voltage, there is a possibility that the DAC output will not change when the code is incremented from 0. Once the DAC has reached the offset voltage of the output

buffer, the DAC output will begin to increment in a normal operation.

### **5V Operation**

The MP7226 can be operated with a single power supply (V<sub>DD</sub> = +5V) or dual power supplies (V<sub>DD</sub> = +5V and V<sub>SS</sub> = -5V). The reference voltage range is reduced along with Some performance parameter degradation. However the DNL of each DAC remains at  $\pm 1$  LSB guaranteeing monotonicity.

Rev. 2.00

11

### PERFORMANCE CHARACTERISTICS

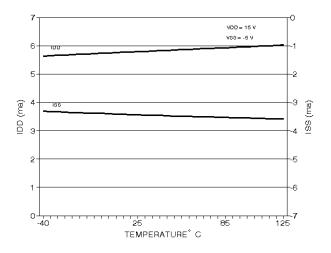

Graph 1. Power Supply Current vs. Temperature

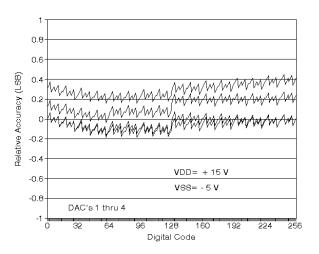

Graph 2. Relative Accuracy vs. Digital Code

# 20 LEAD PLASTIC DUAL-IN-LINE (300 MIL PDIP) N20

|                    | INC   | HES    | MILLIN | METERS |

|--------------------|-------|--------|--------|--------|

| SYMBOL             | MIN   | MAX    | MIN    | MAX    |

| Α                  | _     | 0.200  | _      | 5.08   |

| A <sub>1</sub>     | 0.015 |        | 0.38   | _      |

| В                  | 0.014 | 0.023  | 0.356  | 0.584  |

| B <sub>1</sub> (1) | 0.038 | 0.065  | 0.965  | 1.65   |

| С                  | 0.008 | 0.015  | 0.203  | 0.381  |

| D                  | 0.945 | 1.060  | 24.0   | 26.92  |

| Е                  | 0.295 | 0.325  | 7.49   | 8.26   |

| E <sub>1</sub>     | 0.220 | 0.310  | 5.59   | 7.87   |

| е                  | 0.10  | 00 BSC | 2.5    | 4 BSC  |

| L                  | 0.115 | 0.150  | 2.92   | 3.81   |

| α                  | 0°    | 15°    | 0°     | 15°    |

| Q <sub>1</sub>     | 0.055 | 0.070  | 1.40   | 1.78   |

| S                  | 0.040 | 0.080  | 1.02   | 2.03   |

Note: (1) The minimum limit for dimensions B1 may be 0.023" (0.58 mm) for all four corner leads only.

# 20 LEAD SMALL OUTLINE (300 MIL JEDEC SOIC) S20

|                | INCHES    |        | MILLIMETERS |       |

|----------------|-----------|--------|-------------|-------|

| SYMBOL         | MIN       | MAX    | MIN         | MAX   |

| А              | 0.097     | 0.104  | 2.464       | 2.642 |

| A <sub>1</sub> | 0.0050    | 0.0115 | 0.127       | 0.292 |

| В              | 0.014     | 0.019  | 0.356       | 0.483 |

| С              | 0.0091    | 0.0125 | 0.231       | 0.318 |

| D              | 0.500     | 0.510  | 12.70       | 12.95 |

| Е              | 0.292     | 0.299  | 7.42        | 7.59  |

| е              | 0.050 BSC |        | 1.27 BSC    |       |

| Н              | 0.400     | 0.410  | 10.16       | 10.41 |

| h              | 0.010     | 0.016  | 0.254       | 0.406 |

| L              | 0.016     | 0.035  | 0.406       | 0.889 |

| α              | 0°        | 8°     | 0°          | 8°    |

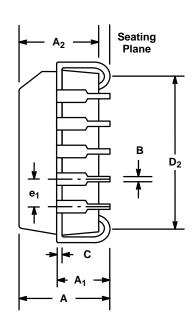

# 20 LEAD PLASTIC LEADED CHIP CARRIER (PLCC) P20

|                    | INCHES    |       | MILLIMETERS |       |

|--------------------|-----------|-------|-------------|-------|

| SYMBOL             | MIN       | MAX   | MIN         | MAX   |

| А                  | 0.165     | 0.180 | 4.19        | 4.57  |

| A <sub>1</sub>     | 0.100     | 0.110 | 2.54        | 2.79  |

| A <sub>2</sub>     | 0.148     | 0.156 | 3.76        | 3.96  |

| В                  | 0.013     | 0.021 | 0.330       | 0.533 |

| С                  | 0.008     | 0.012 | 0.203       | 0.305 |

| D                  | 0.385     | 0.395 | 9.78        | 10.03 |

| D <sub>1</sub> (1) | 0.350     | 0.354 | 8.89        | 8.99  |

| D <sub>2</sub>     | 0.290     | 0.330 | 7.37        | 8.38  |

| $D_3$              | 0.200 Ref |       | 5.08 Ref.   |       |

| e <sub>1</sub>     | 0.050 BSC |       | 1.27 BSC    |       |

$\begin{array}{ccc} \text{Note:} & \text{(1)} & \text{Dimension D}_1 \text{ does not include mold protrusion.} \\ & \text{Allowed mold protrusion is 0.254 mm/0.010 in.} \end{array}$

### NOTICE

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contains here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Copyright 1993 EXAR Corporation Datasheet April 1995

Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.

Rev. 2.00