# LC72146, 72146M, 72146V

# PLL Frequency Synthesizer for Electronic Tuning

## Overview

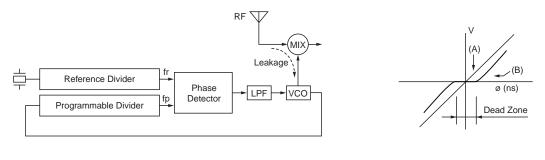

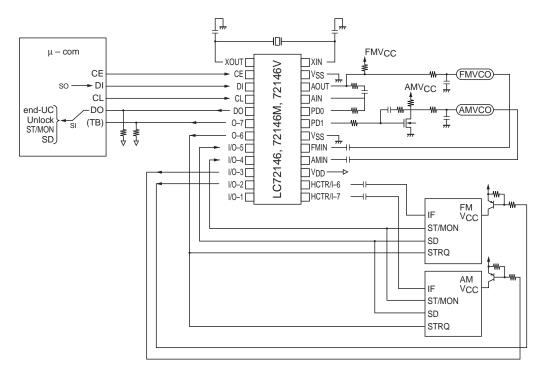

The LC72146 is a PLL frequency synthesizer LSI circuit for electronic tuning in car stereo systems. The LC72146 supports the construction of high-performance, multifunctional electronic tuning systems for the VHF MW, and LW bands.

# Features

- High-speed programmable dividers for

- 10 to 160 MHz on FMIN using pulse swallower

- 0.5 to 40.0 MHz on AMIN using pulse swallower and direct division

- General-purpose counters

- HCTR for 0.4 to 25.0 MHz frequency measurement

- LCTR for 10 to 500 kHz frequency measurement and 1.0 Hz to  $20 \times 10^3$  kHz period measurement

- Reference frequencies: Twelve selectable reference frequencies (4.5 or 7.2 MHz crystal) 1, 3, 5, 9, 10, 3.125, 6.25, 12.5, 25, 30, 50 and 100 kHz

- Phase comparator

- Insensitive band control

- Unlock detection

- Sub-charge pump for high-speed locking

- Deadlock clear circuit

- CCB input/output data interface

- Power-on reset circuit

- Built-in MOS transistor for a low-pass filter

- Inputs/outputs (using five general-purpose input/output ports)

- Maximum of seven inputs (max)

- Maximum of seven outputs (max/four n-channel open-drain and three CMOS outputs)

- Time-base output for clock (8 Hz)

- Operating ranges

- Supply voltage ......4.5 to 5.5 V

- Opetating temperature .....–40 to 85°C

- Package

- DIP24S, MFP24S, SSOP24

- CCB is a trademark of SANYO ELECTRIC CO., LTD.

CCB is SANYO's original bus format and all the bus addresses are controlled by SANYO.

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

SANYO Electric Co., Ltd. Semiconductor Company TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

N2001TN (OT)/73096HA (OT)/11095TH (OT) No. 4922-1/22

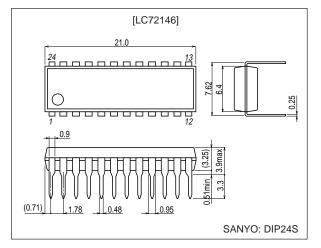

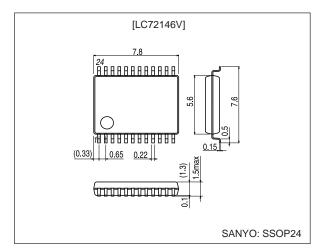

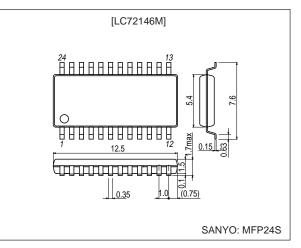

# **Package Dimensions**

unit: mm

## 3067A-DIP24S

unit: mm

#### 3175B-SSOP24

unit: mm

## 3112A-MFP24S

Downloaded from **Elcodis.com** electronic components distributor

# Specifications

# Absolute Maximum Ratings at $Ta=25^{\circ}C,\,V_{SS}$ = 0 V

| Parameter                   | Symbol                | Conditions                                             | Ratings                       | Unit |

|-----------------------------|-----------------------|--------------------------------------------------------|-------------------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max   | V <sub>DD</sub>                                        | -0.3 to +7.0                  | V    |

|                             | V <sub>IN</sub> 1 max | CE, CL, DI                                             | -0.3 to +7.0                  | V    |

| Maximum input voltage       | V <sub>IN</sub> 2 max | XIN, FMIN, AIN, AMIN, HCTR/I-6, LCTR/I-7, I/O-4, I/O-5 | -0.3 to V <sub>DD</sub> + 0.3 | V    |

|                             | V <sub>IN</sub> 3 max | I/O-1 to I/O-3                                         | -0.3 to +15                   | V    |

|                             | V <sub>O</sub> 1 max  | DO                                                     | -0.3 to +7.0                  | V    |

| Maximum output voltage      | V <sub>O</sub> 2 max  | XOUT, I/O-4, I/O-5, O-6, PD0, PF1, AIN                 | -0.3 to V <sub>DD</sub> + 0.3 | V    |

|                             | V <sub>O</sub> 3 max  | I/O-1 to I/O-3, AOUT, O-7                              | -0.3 to +15                   | V    |

|                             | l <sub>O</sub> 1 max  | I/O-4, I/O-5, O-6, O-7                                 | 0 to 3.0                      | mA   |

| Maximum output current      | I <sub>O</sub> 2 max  | DO, AOUT                                               | 0 to 6.0                      | mA   |

|                             | I <sub>O</sub> 3 max  | I/O-1 to I/O-3                                         | 0 to 10                       | mA   |

|                             |                       | DIP24S:Ta ≤ 85°C                                       | 350                           | mW   |

| Allowable power dissipation | Pd max                | MFP24S:Ta ≤ 85°C                                       | 220                           | mW   |

|                             |                       | SSOP24:Ta ≤ 85°C                                       | 150                           | mW   |

| Operating temperature       | Topr                  |                                                        | -40 to +85                    | °C   |

| Storage temperature         | Tstg                  |                                                        | -55 to +125                   | °C   |

# Allowable Operating Ranges at Ta = –40 to $85^{\circ}C,\,V_{SS}$ = 0 V

| Parameter                                    | Symbol              | Conditions                                                           | min  | typ | max             | Unit  |

|----------------------------------------------|---------------------|----------------------------------------------------------------------|------|-----|-----------------|-------|

| Supply voltage                               | V <sub>DD</sub> 1   | V <sub>DD</sub>                                                      | 4.5  |     | 5.5             | V     |

| Supply voltage                               | V <sub>DD</sub> 2   | V <sub>DD</sub> : Serial data retain voltage                         | 2.0  |     |                 | V     |

| han of head and and the sec                  | V <sub>IH</sub> 1   | CE, CL, DI, I/O-1 to I/O-3                                           | 2.2  |     | 6.5             | V     |

| Input high-level voltage                     | V <sub>IH</sub> 2   | I/O-4, I/O-5, HCTR/I-6 and LCTR/I-7                                  | 2.2  |     | V <sub>DD</sub> | V     |

| Input low-level voltage                      | V <sub>IL</sub> 1   | CE, CL, DI and I/O-1 to I/O-5, HCTR/I-6, LCTR/I-7                    | 0    |     | 0.8             | V     |

| Input high-leve lvoltage                     | V <sub>IH</sub> 3   | LCTR/I-7, Pulse wave*1                                               | 2.2  |     | V <sub>DD</sub> | V     |

| Input low-level voltage                      | V <sub>IL</sub> 2   | LCTR/I-7, Pulse wave*1                                               | 0    |     | 0.8             | V     |

| Output valtage                               | V <sub>O</sub> 1    | DO                                                                   | 0    |     | 6.5             | V     |

| Output voltage                               | V <sub>O</sub> 2    | I/O-1 to I/O-3, AOUT, O-7                                            | 0    |     | 13              | V     |

|                                              | f <sub>IN</sub> 1   | XIN; Sine wave, capacitive coupling                                  | 1.0  |     | 8.0             | MHz   |

|                                              | f <sub>IN</sub> 2   | FMIN; Sine wave, capacitive coupling                                 | 10   |     | 160             | MHz   |

| Input frequency                              | f <sub>IN</sub> 3   | AMIN; Sine wave, capacitive coupling                                 | 0.5  |     | 40              | MHz   |

|                                              | f <sub>IN</sub> 4   | HCTR/I-6; Sine wave, capacitive coupling                             |      |     | 25              | MHz   |

|                                              | f <sub>IN</sub> 5   | LCTR/I-7; Sine wave, capacitive coupling                             | 10   |     | 500             | kHz   |

|                                              | f <sub>IN</sub> 6   | LCTR/I-7; Pulse wave, DC coupling*1                                  | 1.0  |     | $20 	imes 10^3$ | Hz    |

| Guaranteed oscillator<br>element frequencies | Xtal                | XIN, XOUT *2                                                         | 4.0  |     | 8.0             | MHz   |

|                                              | V <sub>IN</sub> 1   | XIN                                                                  | 200  |     | 1500            | mVrms |

|                                              | V <sub>IN</sub> 2-1 | FMIN; 50 ≤ f < 130 MHz <sup>*3</sup>                                 | 40   |     | 1500            | mVrms |

|                                              | V <sub>IN</sub> 2-2 | FMIN; $10 \le f < 50 \text{ MHz}^{*3}$ , $130 \le f 160 \text{ MHz}$ | 70   |     | 1500            | mVrms |

|                                              | V <sub>IN</sub> 3-1 | AMIN; $2 \le f < 25 \text{ MHz}^{*3}$                                | 40   |     | 1500            | mVrms |

|                                              | V <sub>IN</sub> 3-2 | AMIN; $25 \le f < 40 \text{ MHz}^{*3}$                               | 70   |     | 1500            | mVrms |

|                                              | V <sub>IN</sub> 3-3 | AMIN; $0.5 \le f < 2.5 \text{ MHz}^{*3}$                             | 40   |     | 1500            | mVrms |

| Input amplitude                              | V <sub>IN</sub> 3-4 | AMIN; 2.5 ≤ f < 10 MHz*3                                             | 70   |     | 1500            | mVrms |

|                                              | V <sub>IN</sub> 4-1 | HCTR/I-6; 0.4 ≤ f < 25 MHz <sup>*4</sup>                             | 40   |     | 1500            | mVrms |

|                                              | V <sub>IN</sub> 4-2 | HCTR/I-6; 8 ≤ f < 12 MHz <sup>*5</sup>                               | 70   |     | 1500            | mVrms |

|                                              | V <sub>IN</sub> 5-1 | LCTR/I-7; 10 ≤ f < 400 kHz <sup>*4</sup>                             | 40   |     | 1500            | mVrms |

|                                              | V <sub>IN</sub> 5-2 | LCTR/I-7; $400 \le f < 500 \text{ kHz}^{*4}$                         | 20   |     | 1500            | mVrms |

|                                              | V <sub>IN</sub> 5-3 | LCTR/I-7; 400 ≤ f < 500 kHz <sup>*5</sup>                            | 70   |     | 1500            | mVrms |

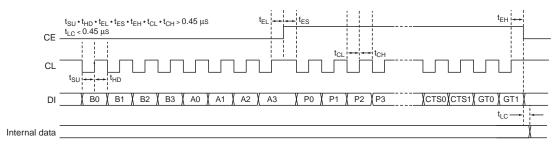

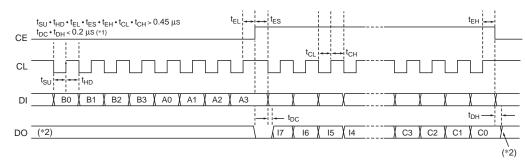

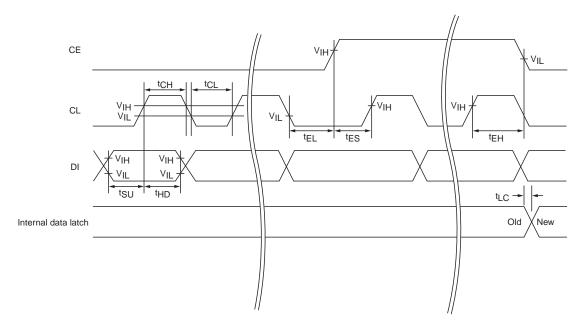

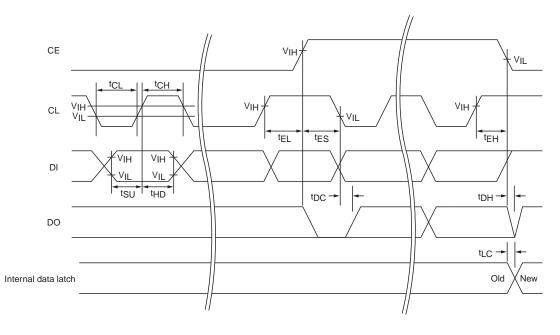

| Data set up time                             | t <sub>SU</sub>     | DI, CL*6                                                             | 0.45 |     |                 | μS    |

| Data hold time                               | t <sub>HD</sub>     | DI, CL*6                                                             | 0.45 |     |                 | μS    |

| Parameter                      | Symbol          | Conditions                          | min  | typ | max  | Unit |

|--------------------------------|-----------------|-------------------------------------|------|-----|------|------|

| Clock low-level time           | t <sub>CL</sub> | CL*5                                | 0.45 |     |      | μs   |

| Clock high-level time          | t <sub>CH</sub> | CL*5                                | 0.45 |     |      | μs   |

| CE wait time                   | t <sub>EL</sub> | CE, CL <sup>*5</sup>                | 0.45 |     |      | μs   |

| CE setup time                  | t <sub>ES</sub> | CL, CE <sup>*5</sup>                | 0.45 |     |      | μs   |

| CE hold time                   | t <sub>EH</sub> | CE, CL <sup>*5</sup>                | 0.45 |     |      | μs   |

| Chip enable to data latch time | t <sub>LC</sub> | *5                                  |      |     | 0.45 | μs   |

| Data output time               | t <sub>DC</sub> | DO, CL; Depends on pull-up resistor |      |     | 0.2  | μs   |

Note: 1. Period measurement

2. Recommended crystal oscillator CI values:

CI  $\leq$  120  $\Omega$  (For a 4.5 MHz crystal) CI  $\leq$  70  $\Omega$  (For a 7.2 MHz crystal)

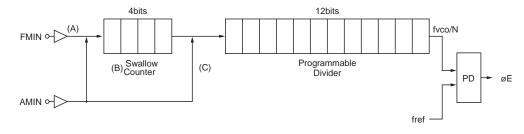

See the description of the structure of the programmable divider.

With the CTC bit in the serial data set to 0

5. With the CTC bit in the serial data set to 1

6. See the description of the serial data timing.

## Electrical Characteristics at Ta = –40 to +85°C, $V_{SS}$ = 0 V

| Parameter                              | Symbol            | Conditions                                           |                                        | min                   | typ                   | max | Unit |

|----------------------------------------|-------------------|------------------------------------------------------|----------------------------------------|-----------------------|-----------------------|-----|------|

|                                        | Rf1               | XIN                                                  |                                        |                       | 1.0                   |     | MΩ   |

|                                        | Rf2               | FMIN                                                 |                                        |                       | 500                   |     | kΩ   |

| Internal feedback resistance           | Rf3               | AMIN                                                 |                                        |                       | 500                   |     | kΩ   |

|                                        | Rf4               | HCTR/I-6                                             |                                        |                       | 250                   |     | kΩ   |

|                                        | Rf5               | LCTR/I-7                                             |                                        |                       | 250                   |     | kΩ   |

| Sub charge pump<br>internal resistance | R1S               | AIN                                                  |                                        |                       | 100                   |     | Ω    |

| Hysteresis                             | V <sub>HIS</sub>  | CE, CL, DI, LCTR/I-7                                 |                                        |                       | 0.1 V <sub>DD</sub>   |     | V    |

|                                        |                   |                                                      | l <sub>O</sub> = 0.5 mA                | V <sub>DD</sub> - 0.5 |                       |     | V    |

| Output high-level voltage              | V <sub>OH</sub> 1 | PD0, PD1, I/O-4, I/O-5, O-6                          | I <sub>O</sub> = 1 mA                  | V <sub>DD</sub> - 1.0 |                       |     | V    |

|                                        |                   |                                                      | I <sub>O</sub> = 2 mA                  | V <sub>DD</sub> - 2.0 |                       |     | V    |

|                                        | V <sub>OH</sub> 2 | AIN: I <sub>O</sub> = 1 mA                           |                                        | V <sub>DD</sub> - 0.6 | V <sub>DD</sub> - 0.3 |     | V    |

|                                        |                   |                                                      | l <sub>O</sub> = 0.5 mA                |                       |                       | 0.5 | V    |

|                                        | V <sub>OL</sub> 1 | PD0, PD1, I/O-4,                                     | I <sub>O</sub> = 1 mA                  |                       |                       | 1.0 | V    |

|                                        |                   | I/O-5, O-6, O-7                                      | I <sub>O</sub> = 2 mA                  |                       |                       | 2.0 | V    |

|                                        | V <sub>OL</sub> 2 | AIN: I <sub>O</sub> = 1 mA                           |                                        |                       | 0.3                   | 0.6 | V    |

| Output low-level voltage               |                   |                                                      | I <sub>O</sub> = 1 mA                  |                       |                       | 0.2 | V    |

| e alparien ierer renage                | V <sub>OL</sub> 3 | I/O-1 to I/O-3                                       | I <sub>O</sub> = 2.5 mA                |                       |                       | 0.5 | V    |

|                                        | VOLO              |                                                      | I <sub>O</sub> = 5 mA                  |                       |                       | 1.0 | V    |

|                                        |                   |                                                      | I <sub>O</sub> = 9 mA                  |                       |                       | 1.8 | V    |

|                                        | V <sub>OL</sub> 4 | DO; I <sub>O</sub> = 5 mA                            |                                        |                       |                       | 1.0 | V    |

|                                        | V <sub>OL</sub> 5 | AOUT; I <sub>O</sub> = 1 mA, AIN = 1.3               | V                                      |                       |                       | 0.5 | V    |

|                                        | I <sub>IH</sub> 1 | CE, CL, DI; V <sub>I</sub> = 6.5 V                   |                                        |                       |                       | 5.0 | μA   |

|                                        | I <sub>IH</sub> 2 | I/O-1 to I/O-3; V <sub>I</sub> = 13 V                |                                        |                       |                       | 5.0 | μA   |

| Input high-level current               | I <sub>IH</sub> 3 | I/O-4, I/O-5, HCTR/I-6, LCTR                         | /I-7; V <sub>I</sub> = V <sub>DD</sub> |                       |                       | 5.0 | μA   |

| input ingit lot of our out             | I <sub>IH</sub> 4 | XIN; $V_I = V_{DD}$                                  |                                        | 2.0                   |                       | 11  | μA   |

|                                        | I <sub>IH</sub> 5 | FMIN, AMIN; V <sub>I</sub> = V <sub>DD</sub>         |                                        | 4.0                   |                       | 22  | μA   |

|                                        | I <sub>IH</sub> 6 | HCTR/I-6, LCTR/I-7; V <sub>I</sub> = V <sub>DI</sub> | 5                                      | 8.0                   |                       | 44  | μA   |

|                                        | I <sub>IL</sub> 1 | CE, CL, DI; V <sub>I</sub> = 0 V                     |                                        |                       |                       | 5.0 | μA   |

|                                        | I <sub>IL</sub> 2 | I/O-1 to I/O5; V <sub>I</sub> = 0 V                  |                                        |                       |                       | 5.0 | μA   |

| Input low-level current                | I <sub>IL</sub> 3 | HCTR/I-6, LCTR/I-7; V <sub>I</sub> = 0 V             |                                        |                       |                       | 5.0 | μA   |

|                                        | I <sub>IL</sub> 4 | XIN; V <sub>I</sub> = 0 V                            |                                        | 2.0                   |                       | 11  | μA   |

|                                        | I <sub>IL</sub> 5 | FMIN, AMIN; $V_I = 0 V$                              |                                        | 4.0                   |                       | 22  | μA   |

|                                        | I <sub>IL</sub> 6 | HCTR/I-6, LCTR/I-7; $V_{I} = 0 V$                    |                                        | 8.0                   |                       | 44  | μA   |

| Parameter                                     | Symbol             | Conditions                                                                      | min | typ  | max | Unit |

|-----------------------------------------------|--------------------|---------------------------------------------------------------------------------|-----|------|-----|------|

| Output off leakage current                    | I <sub>OFF</sub> 1 | I/O-1 to I/O3, AOUT, O-7; V <sub>O</sub> = 13 V                                 |     |      | 5.0 | μA   |

| output on leakage current                     | I <sub>OFF</sub> 2 | DO; V <sub>O</sub> = 6.5 V                                                      |     |      | 5.0 | μA   |

| High-level three state<br>off leakage current | I <sub>OFFH</sub>  | PD0, PD1, AIN; V <sub>O</sub> = V <sub>DD</sub>                                 |     | 0.01 | 200 | nA   |

| Lowh-level three state<br>off leakage current | IOFFL              | PD0, PD1, AIN; V <sub>O</sub> = 0 V                                             |     | 0.01 | 200 | nA   |

| Input cacitance                               | C <sub>IN</sub>    | FMIN                                                                            |     | 6    |     | pF   |

| Pull-down transistor                          | R <sub>pd</sub> 1  | FMIN                                                                            | 80  | 200  | 600 | kΩ   |

| on resistance                                 | R <sub>pd</sub> 2  | AMIN                                                                            | 80  | 200  | 600 | kΩ   |

|                                               |                    | V <sub>DD</sub> ; Xtal = 7.2 MHz, f <sub>IN</sub> 2 = 160 MHz,                  |     |      |     |      |

|                                               | I <sub>DD</sub> 1  | $V_{IN}2 = 70 \text{ mVrms}, f_{IN}4 = 25 \text{ MHz}$                          |     | 10   | 15  | mA   |

| Supply current                                |                    | V <sub>IN</sub> 4 = 40 mVrms                                                    |     |      |     |      |

|                                               | I <sub>DD</sub> 2  | V <sub>DD</sub> ; PLL inhibited,<br>crystal oscillator running (Xtal = 7.2 MHz) |     | 0.5  | 1.5 | mA   |

|                                               | I <sub>DD</sub> 3  | V <sub>DD</sub> ; PLL inhibited, crystal oscillator stoped                      |     |      | 10  | μA   |

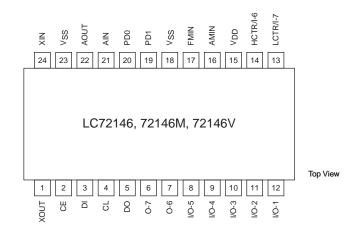

#### **Pin Assignment**

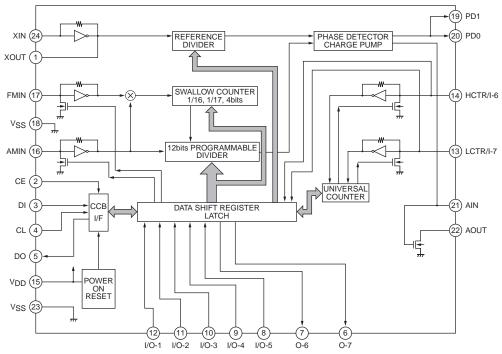

**Block Diagram**

## LC72146, 72146M, 72146V

## **Pin Functions**

| Number         | Symbol                  | Туре                             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Equivalent circuit      |

|----------------|-------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| 24<br>1        | XIN<br>XOUT             | Xtal OSC                         | Connection for crystal oscillator element (7.2 or 4.5 MHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                         |

| 17             | FMIN                    | Local oscillator<br>signal input | <ul> <li>Serial data input: FMIN is selected when DVS is set to 1.<br/>Input frequency range: 10 to 160 MHz</li> <li>The signal is transmitted directly to the swallow counter</li> <li>Divisor value range: 272 to 65535</li> </ul>                                                                                                                                                                                                                                                                               |                         |

| 16             | AMIN                    | Local oscillator<br>signal input | <ul> <li>Serial data input: AMIN is selected when DVS is set to 0.</li> <li>Serial data input: when SNS is set to 1.</li> <li>Input frequency range: 2 to 40 MHz</li> <li>The signal is transmitted directly to the swallow counter.</li> <li>Divisor value range: 272 to 65535</li> <li>Serial data input: when SNS is set to 0.</li> <li>Input frequency range: 0.5 to 10 MHz</li> <li>The signal is transmitted directly to the 12-bit programmable divider.</li> <li>Divisor value range: 4 to 4095</li> </ul> |                         |

| 2              | CE                      | Chip enable                      | <ul> <li>This pin must be set high to input serial data to the<br/>LC72146 DI pin or to output serial data from the DO pin.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                             | □ <u></u> \$>>>         |

| 4              | CL                      | Clock                            | <ul> <li>Inputs the clock used for data synchronization when<br/>inputting serial data to the LC72146 DI pin or outputting<br/>serial data from the DO pin.</li> </ul>                                                                                                                                                                                                                                                                                                                                             | □ <u>(</u> ŝ>>          |

| 3              | DI                      | Input data                       | <ul> <li>Input pin for serial data transmitted to the LC72146 from<br/>a controller.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                    | □ <u></u> \$>~          |

| 5              | DO                      | Output data                      | <ul> <li>Output pin for serial data transmitted from the LC72146 to<br/>a controller.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |

| 15             | V <sub>DD</sub>         | Power supply                     | <ul> <li>The LC72146 power supply connection. A voltage between 4.5 and 5.5 volts must be supplied when the PLL circuit is used.</li> <li>The power on reset circuit operates when power is first applied.</li> </ul>                                                                                                                                                                                                                                                                                              |                         |

| 18<br>23       | V <sub>DD</sub>         | Ground                           | The LC72146 ground connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                         |

| 12<br>11<br>10 | I/O-1<br>I/O-2<br>I/O-3 | General-purpose<br>I/O port      | <ul> <li>General-purpose I/O ports</li> <li>Output mode circuit type: open drain</li> <li>Function after a power on reset: input port</li> <li>Can be set up to function as output ports by bits I/O-1 to I/O-3 in the serial data sent from the controller.</li> </ul>                                                                                                                                                                                                                                            | Continued on next page. |

| Number   | Symbol         | Туре                                                 | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Equivalent circuit |

|----------|----------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 9<br>8   | I/O-4<br>I/O-5 | General-purpose<br>I/O port                          | <ul> <li>General-purpose I/O ports</li> <li>Output mode circuit type: complementary</li> <li>Function after a power on reset: input port</li> <li>Can be set up to function as output ports by bits I/O-4 and I/O-5 in the serial data sent from the controller.</li> </ul>                                                                                                                                                                                                                                                                                                                                                         |                    |

| 7        | O-6            | Output port                                          | <ul> <li>The LC72146 latches the OUT6 bit in the serial data and<br/>outputs it from pin O-6.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |

| 6        | 0-7            | Output port                                          | <ul> <li>The LC72146 latches the OUT7 bit in the serial data and outputs it from pin O-7.</li> <li>Outputs a time base signal (8 Hz) when TBC is set to 1.</li> <li>Function after a power on reset: open circuit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                        |                    |

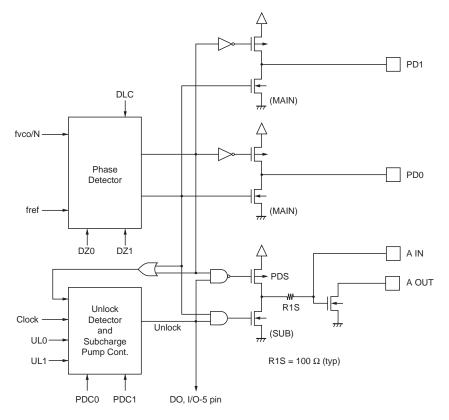

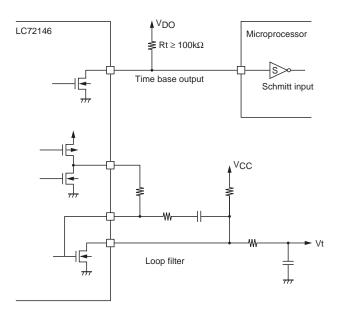

| 20<br>19 | PD0<br>PD1     | Charge pump<br>output                                | <ul> <li>PLL charge pump output pin<br/>If the frequency generated by dividing the local oscillator<br/>frequency by N is higher than the reference frequency, a<br/>high level will be output from PD0, and if it is lower, a low<br/>level will be output. PD0 goes to the high-impedance<br/>state when the frequencies match.</li> <li>PD1 operates identically.</li> </ul>                                                                                                                                                                                                                                                     |                    |

| 21<br>22 | AIN<br>AOUT    | Connections for the<br>low-pass filter<br>transistor | <ul> <li>Connections to the n-channel MOS transistor used for<br/>the PLL active low-pass filter.</li> <li>A high-speed locking circuit can be formed by using<br/>these pins with the built-in sub charge pump.</li> <li>See the item on the structure of the charge pump for<br/>details.</li> </ul>                                                                                                                                                                                                                                                                                                                              |                    |

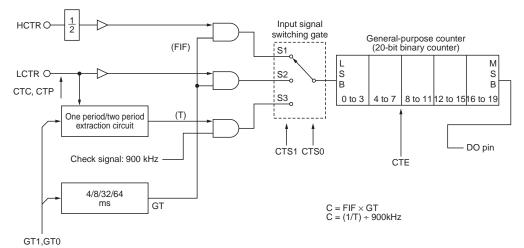

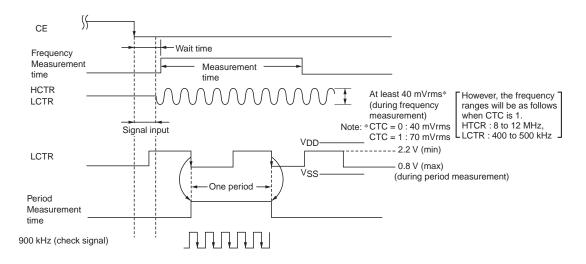

| 14       | HCTR/I-6       | General-purpose<br>counter                           | <ul> <li>HCTR is selected when CTS1 is set to 1.</li> <li>Input frequency range: 0.4 to 25 MHz</li> <li>The signal is passed through a divide-by-two circuit and then input to a general-purpose counter. This input also supports an integrating count function.</li> <li>The result is output from the DO output pin starting with the MSB of the general-purpose counter.</li> <li>See the item on the structure of the general-purpose counter for details.</li> <li>When the H/I-6 bit in the serial data is set to 0:</li> <li>This pin functions as an input port, and the value input is output from the DO pin.</li> </ul> |                    |

| Number Symb | ol Type                         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Equivalent circuit |

|-------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 13 LCTR/    | /I-7 General-purpose<br>counter | <ul> <li>LCTR is selected when CTS1 is set to 0.</li> <li>If the CTS0 bit in the serial data is set to 1:</li> <li>The circuit operates in frequency measurement mode.</li> <li>nput frequency range: 10 to 500 kHz</li> <li>The signal is directly transmitted to the general-purpose counter without passing through the divide-by-two circuit.</li> <li>If the CTS0 bit in the serial data is set to 0:</li> <li>The circuit operates in period measurement mode.</li> <li>nput frequency range: 1 Hz to 20 kHz</li> <li>The measurement period can be set to be either one or two periods of the input signal, and if two period measurement is selected, the input frequency range becomes 2 Hz to 40 kHz.</li> <li>The result is output from the DO output pin starting with the MSB of the general-purpose counter.</li> <li>See the item on the structure of the general-purpose counter for details.</li> <li>When the L/I-7 bit in the serial data is set to 0:</li> <li>This pin functions as an input port. The value input is output from the DO pin.</li> </ul> |                    |

# **Functional Description**

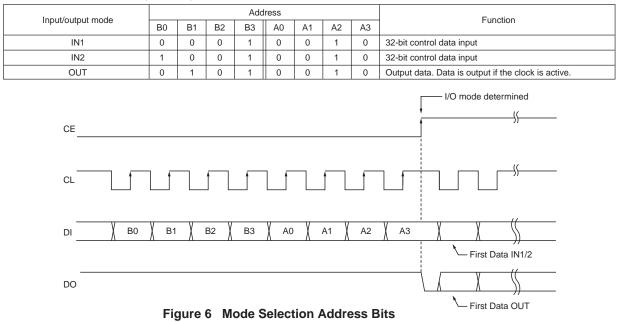

## Serial Data Input

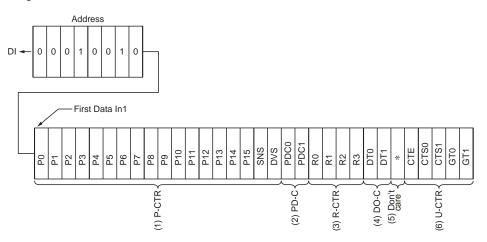

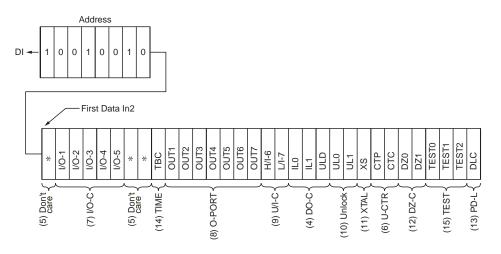

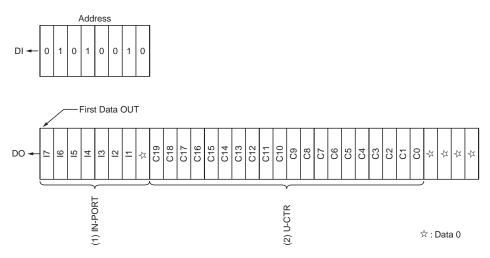

The LC72146 operating parameters are initialized by two 40-bit data words on the serial data input, DI, as shown in Figure 1 and Figure 2 and Table 1.

Figure 1 Input Data Word IN1

Figure 2 Input Data Word IN2

# Table 1 Input Data Functions

| No. | Name       |                                                        |                                                  | I                                                                                                                                                                                                                                                                                                         | Function                                                                                                 | Related bits  |  |  |  |

|-----|------------|--------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------|--|--|--|

|     |            |                                                        | The divider ra<br>own in Table 2                 | and Table 3. P0                                                                                                                                                                                                                                                                                           | ge and LSB are determined by the setting of the DVS and to P3 are ignored if P4 is the LSB.              |               |  |  |  |

|     |            | DVS                                                    | SNS                                              | LSB                                                                                                                                                                                                                                                                                                       | Divider ratio (N)                                                                                        |               |  |  |  |

|     |            | 1                                                      | X                                                | P0                                                                                                                                                                                                                                                                                                        | 272 to 65535                                                                                             |               |  |  |  |

|     |            | 0                                                      |                                                  |                                                                                                                                                                                                                                                                                                           |                                                                                                          |               |  |  |  |

|     | P0 to P15, | 0                                                      | 1                                                | P0<br>P4                                                                                                                                                                                                                                                                                                  | 272 to 65535<br>4 to 4095                                                                                |               |  |  |  |

| (1) | DVS, SNS   |                                                        | -                                                | Г4                                                                                                                                                                                                                                                                                                        | 4 10 4095                                                                                                |               |  |  |  |

|     |            | Note: × = don't<br>Table 3 Frequ                       |                                                  | ttinas                                                                                                                                                                                                                                                                                                    |                                                                                                          |               |  |  |  |

|     |            | DVS                                                    | SNS                                              | Input port                                                                                                                                                                                                                                                                                                | Input frequency range (MHz)                                                                              |               |  |  |  |

|     |            | 1                                                      | ×                                                | FMIN                                                                                                                                                                                                                                                                                                      | 10 to 160                                                                                                |               |  |  |  |

|     |            | 0                                                      | 1                                                | AMIN                                                                                                                                                                                                                                                                                                      | 2 to 40                                                                                                  |               |  |  |  |

|     |            | 0                                                      | 0                                                | AMIN                                                                                                                                                                                                                                                                                                      | 0.5 to 10                                                                                                |               |  |  |  |

|     |            | Note: $\times = don't$                                 |                                                  |                                                                                                                                                                                                                                                                                                           | 0.0 10 10                                                                                                |               |  |  |  |

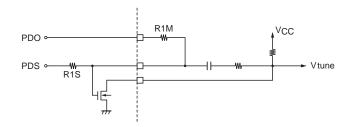

|     |            | connected to the                                       | PDC1 control the gate of the low imp) to build a | w-pass filter trans<br>fast locking PLL.                                                                                                                                                                                                                                                                  | tate as shown in Table 4. The sub-charge pump is istor. This can be used in conjunction with PD0 and PD1 |               |  |  |  |

| (2) | PDC0,      |                                                        |                                                  |                                                                                                                                                                                                                                                                                                           | Charge sums state                                                                                        | UL0, UL1, DLC |  |  |  |

| (2) | PDC1       | PDC1                                                   | PDC0                                             |                                                                                                                                                                                                                                                                                                           | Charge pump state                                                                                        |               |  |  |  |

|     |            | 0                                                      | ×                                                | High imped                                                                                                                                                                                                                                                                                                |                                                                                                          |               |  |  |  |

|     |            | 1                                                      | 1                                                |                                                                                                                                                                                                                                                                                                           | operates continuously)                                                                                   |               |  |  |  |

|     |            |                                                        | 0                                                | Operating (                                                                                                                                                                                                                                                                                               | when PLL is unlocked)                                                                                    |               |  |  |  |

|     |            | Note: × = don't<br>* See the "Char                     |                                                  | age 16 for details                                                                                                                                                                                                                                                                                        |                                                                                                          |               |  |  |  |

|     |            | Reference frequ<br>Bits R0 to R3 dis<br>Table 5 Refere | sable the PLL of                                 |                                                                                                                                                                                                                                                                                                           | ence frequency as shown in Table 5.                                                                      |               |  |  |  |

|     |            | R <sub>3</sub>                                         | R <sub>2</sub>                                   | R <sub>1</sub> R <sub>0</sub>                                                                                                                                                                                                                                                                             | Reference frequency (kHz)                                                                                |               |  |  |  |

|     |            | 0                                                      | 0                                                | 0 0                                                                                                                                                                                                                                                                                                       | 100                                                                                                      |               |  |  |  |

|     |            | 0                                                      | 0                                                | 0 1                                                                                                                                                                                                                                                                                                       | 50                                                                                                       |               |  |  |  |

|     |            | 0                                                      | 0                                                | 1 0                                                                                                                                                                                                                                                                                                       | 25                                                                                                       |               |  |  |  |

|     |            |                                                        |                                                  |                                                                                                                                                                                                                                                                                                           |                                                                                                          |               |  |  |  |

|     |            | 0                                                      | 0                                                | 1 1                                                                                                                                                                                                                                                                                                       | 25                                                                                                       |               |  |  |  |

|     |            | 0                                                      | 0 1                                              | 1 1<br>0 0                                                                                                                                                                                                                                                                                                | 25<br>12.5                                                                                               |               |  |  |  |

|     |            |                                                        | -                                                |                                                                                                                                                                                                                                                                                                           |                                                                                                          |               |  |  |  |

|     | Dot: Do    | 0                                                      | 1                                                | 0 0                                                                                                                                                                                                                                                                                                       | 12.5                                                                                                     |               |  |  |  |

| (3) | R0 to R3   | 0                                                      | 1 1                                              | 0 0<br>0 1                                                                                                                                                                                                                                                                                                | 12.5<br>6.25                                                                                             |               |  |  |  |

| (3) | R0 to R3   | 0<br>0<br>0                                            | 1<br>1<br>1<br>1                                 | 0 0<br>0 1<br>1 0                                                                                                                                                                                                                                                                                         | 12.5<br>6.25<br>3.125                                                                                    |               |  |  |  |

| (3) | R0 to R3   | 0<br>0<br>0<br>0                                       | 1<br>1<br>1<br>1<br>1                            | 0 0<br>0 1<br>1 0<br>1 1                                                                                                                                                                                                                                                                                  | 12.5<br>6.25<br>3.125<br>3.125                                                                           |               |  |  |  |

| (3) | R0 to R3   | 0<br>0<br>0<br>0<br>1                                  | 1<br>1<br>1<br>1<br>1<br>0                       | 0         0           0         1           1         0           1         1           0         0                                                                                                                                                                                                       | 12.5<br>6.25<br>3.125<br>3.125<br>10                                                                     |               |  |  |  |

| (3) | R0 to R3   | 0<br>0<br>0<br>1<br>1                                  | 1<br>1<br>1<br>1<br>0<br>0                       | 0         0           0         1           1         0           1         1           0         0           0         1                                                                                                                                                                                 | 12.5<br>6.25<br>3.125<br>3.125<br>10<br>9                                                                |               |  |  |  |

| (3) | R0 to R3   | 0<br>0<br>0<br>1<br>1<br>1                             | 1 1 1 1 1 0 0 0 0 0                              | 0         0           0         1           1         0           1         1           0         0           0         1           1         1           0         0           1         1                                                                                                               | 12.5         6.25         3.125         3.125         10         9         5                             |               |  |  |  |

| (3) | R0 to R3   | 0<br>0<br>0<br>1<br>1<br>1<br>1<br>1                   | 1<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>0        | 0         0           0         1           1         0           1         1           0         0           0         1           1         0           0         1           1         0           1         1           1         0           1         1           1         1                       | 12.5         6.25         3.125         3.125         10         9         5         1                   |               |  |  |  |

| (3) | R0 to R3   | 0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>1         | 1<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>0<br>1   | 0         0           0         1           1         0           1         1           0         0           0         1           1         0           1         1           0         0           1         0           1         0           1         0           1         0           0         0 | 12.5         6.25         3.125         3.125         10         9         5         1         3         |               |  |  |  |

| No. | Name          |            |              |               |                                       | unction                                      |              |                          |     | Related bits       |

|-----|---------------|------------|--------------|---------------|---------------------------------------|----------------------------------------------|--------------|--------------------------|-----|--------------------|

|     |               | DO and I/0 | D-5 outpu    | t control dat |                                       |                                              |              |                          | -   |                    |

|     |               | Bits ULD,  | DT0, DT1     | , IL0 and IL  | 1 control the mo                      | e of outputs DO and                          | I/O-5 as sho | own in Table 6 and Table | 97. |                    |

|     |               | Table 6    | DO and I/    | O-5 output    | flag selection                        |                                              |              |                          |     |                    |

|     |               | ULD        | DT           | F1 C          | 0T0                                   | DO                                           |              | I/O-5                    |     |                    |

|     |               | 0          | C            | )             | 0 Unlock                              | ag                                           |              |                          |     |                    |

|     |               | 0          | C            | )             | 1 Open                                |                                              | OUT5 fla     | na*2                     |     |                    |

|     |               | 0          | 1            |               | 0 End-UC                              |                                              |              | .9 .                     |     |                    |

|     |               | 0          | 1            |               | 1 IN. See                             | able 7.                                      |              |                          |     |                    |

|     |               | 1          | C            |               | 0 Open                                |                                              | _            |                          |     |                    |

|     |               | 1          | C            |               | 1 Open                                | -                                            | Unlock fla   | ag <sup>*2</sup> .       |     |                    |

|     |               | 1          | 1            |               | 0 End-UC                              | 8                                            | _            |                          |     |                    |

|     |               | 1          | 1            | I             | 1 IN. See                             |                                              |              |                          |     |                    |

|     |               |            |              |               | neral-purpose co<br>5 is set to be an | nter operation has fin                       | nished.      |                          |     |                    |

| (4) | ULD, DT0,     | 2.         | , applicable |               |                                       |                                              | _            |                          |     | UT5, I/O-1, I/O-2, |

| (., | DT1, IL0, IL1 |            | DO           | λ             | 1                                     | ļ                                            |              |                          | 1/C | D-5                |

|     |               |            |              |               |                                       |                                              |              |                          |     |                    |

|     |               |            |              | S             | tart                                  | Finish                                       | CE : H       | Hi                       |     |                    |

|     |               |            |              |               |                                       | (I-1 chang                                   | le)          |                          |     |                    |

|     |               |            |              |               |                                       |                                              |              | A02691                   |     |                    |

|     |               |            |              |               | Figure 3                              | DO output state                              |              |                          |     |                    |

|     |               | Table 7    | N state s    | election      |                                       |                                              |              |                          |     |                    |

|     |               | IL1        |              | IL0           |                                       | IN s                                         | state        |                          |     |                    |

|     |               | 0          |              | 0             | Open                                  |                                              |              |                          |     |                    |

|     |               | 0          |              | 1             | I-1 input                             |                                              |              |                          |     |                    |

|     |               | 1          |              | 0             | I-2 input                             |                                              |              |                          |     |                    |

|     |               | 1          |              | 1             | DO goes lo                            | when I1 changes.                             |              |                          |     |                    |

|     |               |            |              |               |                                       | ort, IN becomes oper                         |              |                          |     |                    |

|     |               |            |              | -             | -                                     | scillator has stopped<br>R3 = R2 = R1 = 1; I |              |                          |     |                    |

| (5) |               | Don't care |              | nce nequen    | icles are as tries                    | $K_{3} = K_{2} = K_{1} = 1, 1$               | KU = U]      |                          | _   |                    |

| (5) | *             | Counter co |              |               |                                       |                                              |              |                          | _   |                    |

|     |               |            |              | 1 select the  | counter input as                      | shown in Table 8.                            |              |                          |     |                    |

|     |               | Table 8    | Counter i    | nput and m    | easurement mo                         | le selection                                 |              |                          |     |                    |

|     |               | 0.704      | 0700         |               | Measuremen                            |                                              |              |                          |     |                    |

|     |               | CTS1       | CTS0         | Input         | mode                                  |                                              |              |                          |     |                    |

|     |               | 1          | ×            | HCTR          | Frequency                             |                                              |              |                          |     |                    |

|     |               | 0          | 1            | LCTR          | Frequency                             |                                              |              |                          |     |                    |

|     |               | 0          | 0            | LCTR          | Period                                |                                              |              |                          |     |                    |

|     | CTS0,         | Note: ×=   |              |               |                                       |                                              |              |                          |     |                    |

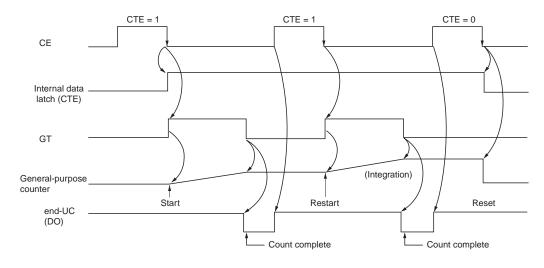

|     | CTS1, CTE,    |            |              |               |                                       | counter, when 0.                             | ament mode   | or the number of         |     |                    |

|     | GT0, GT1      |            |              |               |                                       | shown in Table 9.                            |              |                          |     |                    |

| (6) |               | Table 9    | Measuren     | nent durati   | on selection                          |                                              |              |                          |     | H/I-6, L/I-7       |

|     |               |            |              |               | Free                                  | ency measurement                             |              | Period measurement       |     |                    |

|     |               | GT1        |              | GT0           | Measurem                              | nt Maining                                   |              | Quality                  |     |                    |

|     |               |            |              |               | duration (r                           | s) Wait tim                                  | ie (ms)      | Cycles                   |     |                    |

|     |               | 0          |              | 0             | 4                                     | 3 to                                         | <sub>4</sub> | 1                        |     |                    |

|     |               | 0          |              | 1             | 8                                     |                                              |              |                          |     |                    |

|     |               | 1          |              | 0             | 32                                    | 7 to                                         | 0.8          | 2                        |     |                    |

|     |               | 1          |              | 1             | 64                                    |                                              |              | -                        |     |                    |

|     |               |            |              |               |                                       |                                              |              |                          |     |                    |

|     |               |            |              |               |                                       |                                              |              |                          |     |                    |

|     | CTP, CTC      |            |              |               | ed down, and wh<br>ms before CTE      | n CTP is 1 it is not. (                      | Wait time: 1 | to 2 ms.)                |     |                    |

| No.  | Name              |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Function                                                                |                                                                                                                                              | Related bits  |

|------|-------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------|