# ISP1104 Advanced Universal Serial Bus transceiver Rev. 02 — 14 October 2003

**Product data**

## 1. General description

The ISP1104 Universal Serial Bus (USB) transceiver is compliant with the *Universal Serial Bus Specification Rev. 2.0*. The ISP1104 can transmit and receive USB data at full-speed (12 Mbit/s). It allows single and differential input modes selectable by a MODE input.

It allows USB Application Specific Integrated Circuits (ASICs) and Programmable Logic Devices (PLDs) with power supply voltages from 1.65 V to 3.6 V to interface with the physical layer of the USB. It has an integrated 5 V-to-3.3 V voltage regulator for direct powering via the USB supply line V<sub>BUS</sub>. It has an integrated voltage detector to detect the presence of the V<sub>BUS</sub> line voltage (V<sub>CC(5.0)</sub>). When V<sub>BUS</sub> (V<sub>CC(5.0)</sub>) is lost, the D+ and D– pins can be shared with other serial protocols.

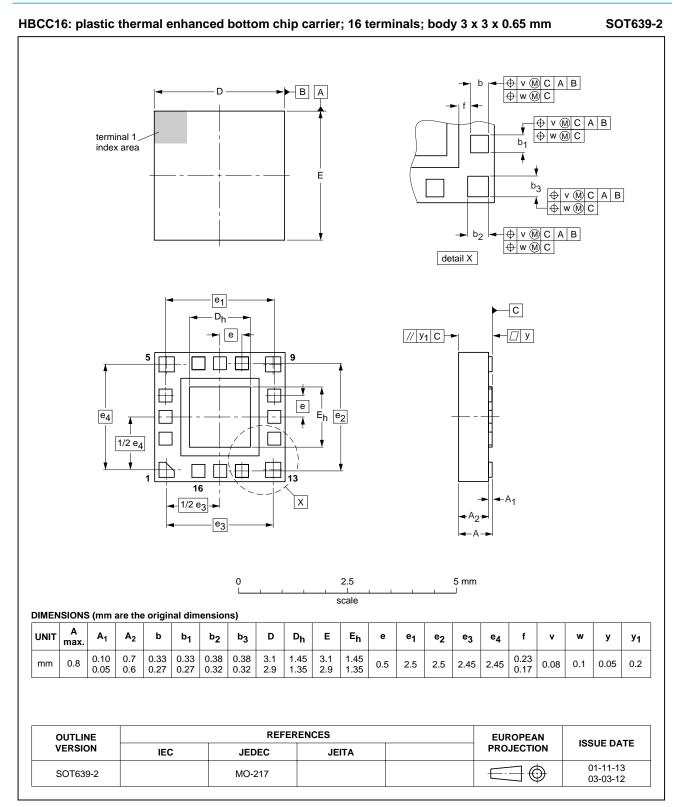

The ISP1104 is available in HBCC16 package.

The ISP1104 is ideal for use in portable electronic devices, such as mobile phones, digital still cameras, personal digital assistants and information appliances.

### 2. Features

- Complies with Universal Serial Bus Specification Rev. 2.0

- Supports full-speed (12 Mbit/s) serial data rate

- Integrated 5 V-to-3.3 V voltage regulator for powering via USB line V<sub>BUS</sub>

- V<sub>BUS</sub> voltage presence indication on pin VBUSDET

- Used as USB device transceiver or USB transceiver

- Stable RCV output during single-ended zero (SE0) condition

- Two single-ended receivers with hysteresis

- Low-power operation

- Supports I/O voltage range from 1.65 V to 3.6 V

- ±12 kV ESD protection at pins D+, D-, V<sub>CC(5.0)</sub> and GND

- Full industrial operating temperature range from –40 °C to +85 °C

- Available in HBCC16 lead-free and halogen-free package.

### 3. Applications

- Portable electronic devices, such as:

- Mobile phone

- Digital Still Camera (DSC)

- Personal Digital Assistant (PDA)

- Information Appliance (IA).

# 4. Ordering information

| Table 1: | Ordering info | ormation                                                                                        |          |

|----------|---------------|-------------------------------------------------------------------------------------------------|----------|

| Туре     | Package       |                                                                                                 |          |

| number   | Name          | Description                                                                                     | Version  |

| ISP1104W | HBCC16        | plastic thermal enhanced bottom chip carrier;<br>16 terminals; body $3 \times 3 \times 0.65$ mm | SOT639-2 |

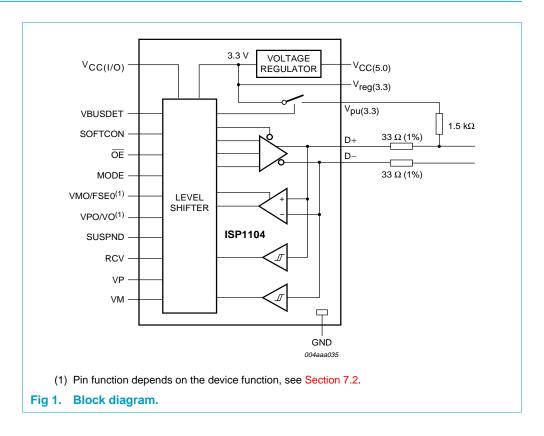

# 5. Block diagram

9397 750 11229

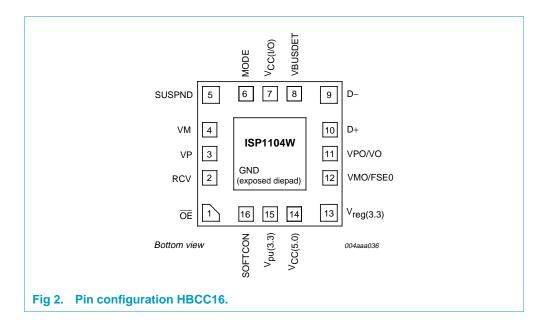

# 6. Pinning information

### 6.1 Pinning

### 6.2 Pin description

| Table 2:              | Pin desc | ription |                                                                                                                                                                                                                                                                                                               |

|-----------------------|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol <sup>[1]</sup> | Pin      | Туре    | Description                                                                                                                                                                                                                                                                                                   |

| ŌĒ                    | 1        | I       | input for output enable (CMOS level with respect to $V_{CC(I/O)}$ , active LOW); enables the transceiver to transmit data on the USB bus                                                                                                                                                                      |

|                       |          |         | input pad; push pull; CMOS                                                                                                                                                                                                                                                                                    |

| RCV                   | 2        | 0       | differential data receiver output (CMOS level with respect to $V_{CC(I/O)}$ ); driven LOW when input SUSPND is HIGH; the output state of RCV is preserved and stable during an SE0 condition                                                                                                                  |

|                       |          |         | output pad; push pull; 4 mA output drive; CMOS                                                                                                                                                                                                                                                                |

| VP                    | 3        | 0       | single-ended D+ receiver output (CMOS level with<br>respect to $V_{CC(I/O)}$ ); for external detection of SE0, error<br>conditions and speed of connected device; driven HIGH<br>when no supply voltage is connected to $V_{CC(5.0)}$ and<br>$V_{reg(3.3)}$<br>output pad; push pull; 4 mA output drive; CMOS |

| VM                    | 4        | 0       | single-ended D– receiver output (CMOS level with<br>respect to $V_{CC(I/O)}$ ); for external detection of SE0, error<br>conditions and speed of connected device; driven HIGH<br>when no supply voltage is connected to $V_{CC(5.0)}$ and<br>$V_{reg(3.3)}$<br>output pad; push pull; 4 mA output drive; CMOS |

| Symbol <sup>[1]</sup> | Pin     | Туре | Description                                                                                                                                                                                                                                                    |

|-----------------------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SUSPND                | 5       | 1    | suspend input (CMOS level with respect to $V_{CC(I/O)}$ ); a HIGH level enables low-power state while the USB bus is inactive and drives output RCV to a LOW level                                                                                             |

|                       |         |      | input pad; push pull; CMOS                                                                                                                                                                                                                                     |

| MODE                  | 6       | I    | mode input (CMOS level with respect to $V_{CC(I/O)}$ ); a HIGH level enables the differential input mode (pins VPO and VMO) whereas a LOW level enables a single-ended input mode (pins VO and FSE0); see Table 4 and Table 5                                  |

|                       |         |      | input pad; push pull; CMOS                                                                                                                                                                                                                                     |

| V <sub>CC</sub> (I/O) | 7       | -    | supply voltage for digital I/O pins (1.65 V to 3.6 V); when $V_{CC(I/O)}$ is not connected, the pins D+ and D– are in three-state; this supply pin is totally independent of $V_{CC(5.0)}$ and $V_{reg(3.3)}$ and must never exceed the $V_{reg(3.3)}$ voltage |

| VBUSDET               | 8       | 0    | $V_{BUS}$ indicator output (CMOS level with respect to $V_{CC(I/O)}$ ); when $V_{BUS}$ > 4.1 V, then VBUSDET = HIGH and when $V_{BUS}$ < 3.6 V, then VBUSDET = LOW                                                                                             |

|                       |         |      | output pad; push pull; 4 mA output drive; CMOS                                                                                                                                                                                                                 |

| D-                    | 9       | AI/O | negative USB data bus connection (analog, differential)                                                                                                                                                                                                        |

| D+                    | 10      | AI/O | positive USB data bus connection (analog, differential); connect a 1.5 k $\Omega$ resistor to pin V <sub>pu(3.3)</sub>                                                                                                                                         |

| VPO/VO                | 11      | I    | driver data input (CMOS level with respect to $V_{CC(I/O)}$ ,<br>Schmitt trigger); see Table 4 and Table 5                                                                                                                                                     |

| VMO/FSE0              | 12      | 1    | input pad; push pull; CMOS                                                                                                                                                                                                                                     |

| VINO/FSE0             | 12      | 1    | driver data input (CMOS level with respect to $V_{CC(I/O)}$ ,<br>Schmitt trigger); see Table 4 and Table 5<br>input pad; push pull; CMOS                                                                                                                       |

| V <sub>reg(3.3)</sub> | 13      | -    | regulated supply voltage output (3.0 V to 3.6 V); a                                                                                                                                                                                                            |

| v reg(3.3)            | 10      |      | decoupling capacitor of at least 0.1 $\mu$ F is required                                                                                                                                                                                                       |

| V <sub>CC(5.0)</sub>  | 14      | -    | supply voltage input (4.0 V to 5.5 V); can be connected directly to the USB supply line $V_{\text{BUS}}$                                                                                                                                                       |

| V <sub>pu(3.3)</sub>  | 15      | -    | pull-up supply voltage (3.3 V $\pm$ 10 %); connect an external 1.5 k $\Omega$ resistor on pin D+ (full-speed); pin function is controlled by input SOFTCON                                                                                                     |

|                       |         |      | <b>SOFTCON = LOW</b> — $V_{pu(3.3)}$ floating (high impedance); ensures zero pull-up current                                                                                                                                                                   |

|                       |         |      | <b>SOFTCON = HIGH</b> — $V_{pu(3.3)}$ = 3.3 V; internally connected to $V_{reg(3.3)}$                                                                                                                                                                          |

| SOFTCON               | 16      | 1    | software controlled USB connection input; a HIGH level applies 3.3 V to pin $V_{pu(3.3)}$ , which is connected to an external 1.5 k $\Omega$ pull-up resistor; this allows USB connect or disconnect signalling to be controlled by software                   |

|                       |         |      | input pad; push pull; CMOS                                                                                                                                                                                                                                     |

| GND                   | exposed | -    | ground supply; down bonded to the exposed die pad                                                                                                                                                                                                              |

[1] Symbol names with an overscore (for example, NAME) indicate active LOW signals.

# 7. Functional description

### 7.1 Function selection

| Table 3: | Function | table                    |                         |        |                                                              |

|----------|----------|--------------------------|-------------------------|--------|--------------------------------------------------------------|

| SUSPND   | OE       | D+ and D-                | RCV                     | VP/VM  | Function                                                     |

| L        | L        | driving/<br>receiving    | active                  | active | normal driving<br>(differential receiver active)             |

| L        | Н        | receiving <sup>[1]</sup> | active                  | active | receiving                                                    |

| Η        | L        | driving                  | inactive <sup>[2]</sup> | active | driving during 'suspend'<br>(differential receiver inactive) |

| Н        | Н        | high-Z <sup>[1]</sup>    | inactive <sup>[2]</sup> | active | low-power state                                              |

[1] Signal levels on pins D+ and D– are determined by other USB devices and external pull-up or pull-down resistors.

[2] In the suspend mode (pin SUSPND = HIGH), the differential receiver is inactive and the output RCV is always LOW. Out-of-suspend (K) signalling is detected via the single-ended receivers VP and VM.

### 7.2 Operating functions

# Table 4:Driving function using single-ended input data interface (pin $\overline{OE}$ = L and pin MODE = L)

| FSE0 | VO | Data                 |

|------|----|----------------------|

| L    | L  | differential logic 0 |

| L    | Н  | differential logic 1 |

| Н    | L  | SE0                  |

| Н    | Н  | SE0                  |

# Table 5: Driving function using differential input data interface (pin $\overline{OE}$ = L and pin MODE = H)

|     | P   |                      |

|-----|-----|----------------------|

| VMO | VPO | Data                 |

| L   | L   | SE0                  |

| L   | Н   | differential logic 1 |

| Н   | L   | differential logic 0 |

| Н   | Н   | illegal state        |

#### Table 6:Receiving function (pin $\overline{OE} = H$ )

| D+ and D-            | RCV                 | <b>VP</b> <sup>[1]</sup> | <b>VM</b> <sup>[1]</sup> |

|----------------------|---------------------|--------------------------|--------------------------|

| differential logic 0 | L                   | L                        | Н                        |

| differential logic 1 | Н                   | Н                        | L                        |

| SE0                  | RCV* <sup>[2]</sup> | L                        | L                        |

[1] VP = VM = H indicates the sharing mode ( $V_{CC(5.0)}$  is disconnected).

[2] RCV\* denotes the signal level on output RCV just before the SE0 state occurs. This level is stable during the SE0 period.

### 7.3 Power supply configurations

The ISP1104 can be used with different power supply configurations, which can be changed dynamically. Table 8 provides an overview of power supply configurations.

**Normal mode** — Both V<sub>CC(I/O)</sub> and V<sub>CC(5.0)</sub> are connected. For 5 V operation, V<sub>CC(5.0)</sub> is connected to a 5 V source (4.0 V to 5.5 V). The internal voltage regulator then produces 3.3 V for USB connections. V<sub>CC(I/O)</sub> is independently connected to a voltage source (1.65 V to 3.6 V), depending on the supply voltage of the external circuit.

**Disable mode** —  $V_{CC(I/O)}$  is not connected and  $V_{CC(5.0)}$  is connected. In this mode, the internal circuits of the ISP1104 ensure that the D+ and D- pins are in three-state and the power consumption drops to the low-power (suspended) state level. Some hysteresis is built into the detection of  $V_{CC(I/O)}$  lost.

**Sharing mode** — V<sub>CC(I/O)</sub> is connected and V<sub>CC(5.0)</sub> < 3.6 V to differentiate between the USB mode and other modes when sharing the V<sub>BUS</sub>. In this mode, pins D+ and D- are made three-state and the ISP1104 allows external signals of up to 3.6 V to share the D+ and D- lines. The internal circuits of the ISP1104 ensure that virtually no current (maximum 10  $\mu$ A) is drawn via the D+ and D- lines. The power consumption through pin V<sub>CC(I/O)</sub> and pin V<sub>CC(5.0)</sub> drops to the low-power (suspended) state level. Pins VP and VM are driven HIGH and pins VBUSDET and RCV are driven LOW to indicate this mode. Some hysteresis is built into the detection of V<sub>CC(5.0)</sub> lost.

Table 7:Pin states in disable or sharing mode

| Pin                                            | Disable mode           | Sharing mode          |

|------------------------------------------------|------------------------|-----------------------|

| V <sub>CC(5.0)</sub>                           | 5 V input              | <3.6 V                |

| V <sub>reg(3.3)</sub>                          | 3.3 V output           | pulled-down           |

| V <sub>CC(I/O)</sub>                           | not present            | 1.65 V to 3.6 V input |

| V <sub>pu(3.3)</sub>                           | high impedance (off)   | high impedance (off)  |

| D+, D-                                         | high impedance         | high impedance        |

| VP, VM                                         | invalid <sup>[1]</sup> | Н                     |

| RCV                                            | invalid <sup>[1]</sup> | L                     |

| VBUSDET                                        | invalid <sup>[1]</sup> | L                     |

| VPO/VO, VMO/FSE0, MODE,<br>SUSPND, OE, SOFTCON | high impedance         | high impedance        |

[1] High impedance or driven LOW.

#### Table 8: Power supply configuration overview

| V <sub>CC(5.0)</sub>       | V <sub>CC(I/O)</sub> | Configuration | Special characteristics                                                                                                              |

|----------------------------|----------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------|

| connected                  | connected            | normal mode   | -                                                                                                                                    |

| connected                  | not connected        | disable mode  | D+, D– and V <sub>pu(3.3)</sub> high impedance;<br>VP, VM, RCV: invalid <sup>[1][2]</sup>                                            |

| not connected<br>or <3.6 V | connected            | sharing mode  | D+, D- and $V_{pu(3.3)}$ high impedance;<br>VP, VM driven HIGH; RCV driven<br>LOW; VBUSDET driven LOW; $V_{reg(3.3)}$<br>pulled-down |

[1] High impedance or driven LOW.

[2]  $V_{reg(3.3)}$  may not be operational.

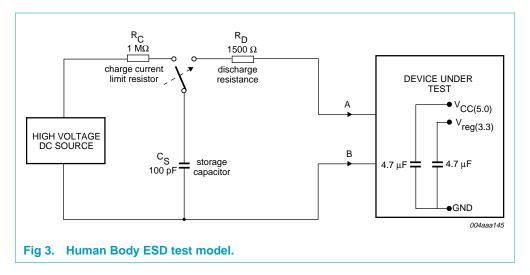

# 8. Electrostatic discharge (ESD)

### 8.1 ESD protection

The pins that are connected to the USB connector (D+, D–, V<sub>CC(5.0)</sub> and GND) have a minimum of ±12 kV ESD protection. The ±12 kV measurement is limited by the test equipment. Capacitors of 4.7  $\mu$ F connected from V<sub>reg(3.3)</sub> to GND and V<sub>CC(5.0)</sub> to GND are required to achieve this ±12 kV ESD protection (see Figure 3).

The ISP1104 can withstand  $\pm$ 12 kV using the Human Body Model and  $\pm$ 5 kV using the Contact Discharge Method as specified in *IEC 61000-4-2*.

### 8.2 ESD test conditions

A detailed report on test set-up and results is available on request.

Downloaded from Elcodis.com electronic components distributor

# 9. Limiting values

#### Table 9: Absolute maximum ratings

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol               | Parameter                       | Conditions                                                  | Min           | Мах                 | Unit |

|----------------------|---------------------------------|-------------------------------------------------------------|---------------|---------------------|------|

| V <sub>CC(5.0)</sub> | supply voltage                  |                                                             | -0.5          | +6.0                | V    |

| V <sub>CC(I/O)</sub> | I/O supply voltage              |                                                             | -0.5          | +4.6                | V    |

| VI                   | DC input voltage                |                                                             | -0.5          | $V_{CC(I/O)} + 0.5$ | V    |

| l <sub>lu</sub>      | latch-up current                | $V_{I} = -1.8 V$ to +5.4 V                                  | -             | 100                 | mA   |

| V <sub>esd</sub>     | electrostatic discharge voltage | on pins D+, D–, $V_{CC(5.0)}$ and GND; $I_{LI}$ < 1 $\mu A$ | [1][2] -12000 | +12000              | V    |

|                      |                                 | on other pins; $I_{LI} < 1 \ \mu A$                         | -2000         | +2000               | V    |

| T <sub>stg</sub>     | storage temperature             |                                                             | -40           | +125                | °C   |

[1] Testing equipment limits measurement to only ±12 kV. Capacitors needed on V<sub>CC(5.0)</sub> and V<sub>reg(3.3)</sub> (see Section 8).

[2] Equivalent to discharging a 100 pF capacitor via a 1.5 k $\Omega$  resistor (Human Body Model).

# **10. Recommended operating conditions**

#### Table 10: Recommended operating conditions

| Symbol               | Parameter                  | Conditions     | Min  | Тур | Max                  | Unit |

|----------------------|----------------------------|----------------|------|-----|----------------------|------|

| V <sub>CC(5.0)</sub> | supply voltage             |                | 4.0  | 5.0 | 5.5                  | V    |

| V <sub>CC(I/O)</sub> | I/O supply voltage         |                | 1.65 | -   | 3.6                  | V    |

| VI                   | input voltage              |                | 0    | -   | V <sub>CC(I/O)</sub> | V    |

| V <sub>I(AI/O)</sub> | input voltage on AI/O pins | pins D+ and D– | 0    | -   | 3.6                  | V    |

| T <sub>amb</sub>     | ambient temperature        |                | -40  | -   | +85                  | °C   |

### **11. Static characteristics**

#### Table 11: Static characteristics: supply pins

$V_{CC(5.0)} = 4.0 V$  to 5.5 V;  $V_{CC(I/O)} = 1.65 V$  to 3.6 V;  $V_{GND} = 0 V$ ;  $T_{amb} = -40 \circ C$  to  $+85 \circ C$ ; unless otherwise specified.

| 00(0.0)                       |                                                |                                                                                         |            |     |     |      |

|-------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------|------------|-----|-----|------|

| Symbol                        | Parameter                                      | Conditions                                                                              | Min        | Тур | Max | Unit |

| V <sub>reg(3.3)</sub>         | regulated supply voltage output                | internal regulator option;<br>I <sub>load</sub> ≤ 300 μA                                | [1][2] 3.0 | 3.3 | 3.6 | V    |

| I <sub>CC</sub>               | operating supply current                       | transmitting and receiving at<br>12 Mbit/s; C <sub>L</sub> = 50 pF on<br>pins D+ and D– | [3] _      | 4   | 8   | mA   |

| I <sub>CC(I/O)</sub>          | operating I/O supply current                   | transmitting and receiving at 12 Mbit/s                                                 | [3] _      | 1   | 2   | mA   |

| I <sub>CC(idle)</sub>         | supply current during full-speed idle and SE0  | idle: $V_{D+} > 2.7$ V, $V_{D-} < 0.3$ V;<br>SE0: $V_{D+} < 0.3$ V, $V_{D-} < 0.3$ V    | [4] _      | -   | 500 | μA   |

| I <sub>CC(I/O)(static)</sub>  | static I/O supply current                      | idle, SE0 or suspend                                                                    | -          | -   | 20  | μA   |

| I <sub>CC(susp)</sub>         | suspend supply current                         | SUSPND = H                                                                              | [4] _      | -   | 100 | μA   |

| I <sub>CC-I/O(dis)</sub>      | disable current from $V_{CC}$ to $V_{CC(I/O)}$ | $V_{CC(I/O)}$ not connected                                                             | [4] _      | -   | 100 | μA   |

| I <sub>CC(I/O)(sharing)</sub> | sharing mode I/O supply current                | $V_{CC(5.0)}$ not connected                                                             | -          | -   | 20  | μA   |

<sup>9397 750 11229</sup> Product data

#### Table 11: Static characteristics: supply pins...continued

$V_{CC(5.0)} = 4.0 V$  to 5.5 V;  $V_{CC(l/O)} = 1.65 V$  to 3.6 V;  $V_{GND} = 0 V$ ;  $T_{amb} = -40 \circ C$  to  $+85 \circ C$ ; unless otherwise specified.

| Symbol                   | Parameter                                      | Conditions                                                    | Min | Тур  | Max | Unit |

|--------------------------|------------------------------------------------|---------------------------------------------------------------|-----|------|-----|------|

| I <sub>Dx(sharing)</sub> | sharing mode load current on<br>pins D+ and D– | $V_{CC(5.0)}$ not connected;<br>SOFTCON = L; $V_{Dx}$ = 3.6 V | -   | -    | 10  | μΑ   |

| V <sub>CC(5.0)th</sub>   | supply voltage detection                       | $1.65~V \leq V_{CC(I/O)} \leq 3.6~V$                          |     |      |     |      |

|                          | threshold                                      | supply lost                                                   | -   | -    | 3.6 | V    |

|                          |                                                | supply present                                                | 4.1 | -    | -   | V    |

| V <sub>CC(5.0)hys</sub>  | supply voltage detection<br>hysteresis         | V <sub>CC(I/O)</sub> = 1.8 V                                  | -   | 70   | -   | mV   |

| V <sub>CC(I/O)th</sub>   | I/O supply voltage detection                   | V <sub>reg(3.3)</sub> = 2.7 V to 3.6 V                        |     |      |     |      |

|                          | threshold                                      | supply lost                                                   | -   | -    | 0.5 | V    |

|                          |                                                | supply present                                                | 1.4 | -    | -   | V    |

| V <sub>CC(I/O)hys</sub>  | I/O supply voltage detection<br>hysteresis     | V <sub>reg(3.3)</sub> = 3.3 V                                 | -   | 0.45 | -   | V    |

[1]  $I_{load}$  includes the pull-up resistor current via pin  $V_{pu(3.3)}$ .

[2] The minimum voltage is 2.7 V in the suspend mode.

[3] Characterized only, not tested in production.

[4] Excluding any load current and V<sub>pu(3.3)</sub> or V<sub>sw</sub> source current to the 1.5 kΩ and 15 kΩ pull-up and pull-down resistors (200 μA typ.).

#### Table 12: Static characteristics: digital pins

$V_{CC(I/O)} = 1.65 \text{ V to } 3.6 \text{ V}; V_{GND} = 0 \text{ V}; T_{amb} = -40 \circ C \text{ to } +85 \circ C; unless otherwise specified.$

| Symbol            | Parameter                            | Conditions               | Min                         | Тур | Max                     | Unit |

|-------------------|--------------------------------------|--------------------------|-----------------------------|-----|-------------------------|------|

| $V_{CC(I/O)} = 1$ | .65 V to 3.6 V                       |                          |                             |     |                         |      |

| Input levels      |                                      |                          |                             |     |                         |      |

| VIL               | LOW-level input voltage              |                          | -                           | -   | 0.3V <sub>CC(I/O)</sub> | V    |

| VIH               | HIGH-level input voltage             |                          | 0.6V <sub>CC(I/O)</sub>     | -   | -                       | V    |

| Output leve       | ls                                   |                          |                             |     |                         |      |

| V <sub>OL</sub>   | LOW-level output voltage             | I <sub>OL</sub> = 100 μA | -                           | -   | 0.15                    | V    |

|                   |                                      | I <sub>OL</sub> = 2 mA   | -                           | -   | 0.4                     | V    |

| V <sub>OH</sub>   | HIGH-level output voltage            | I <sub>OH</sub> = 100 μA | V <sub>CC(I/O)</sub> – 0.15 | -   | -                       | V    |

|                   |                                      | I <sub>OH</sub> = 2 mA   | $V_{CC(I/O)} - 0.4$         | -   | -                       | V    |

| Leakage cu        | irrent                               |                          |                             |     |                         |      |

| ILI               | input leakage current                |                          | <sup>[1]</sup> –1           | -   | +1                      | μA   |

| Capacitand        | ce                                   |                          |                             |     |                         |      |

| C <sub>IN</sub>   | input capacitance                    | pin to GND               | -                           | -   | 10                      | pF   |

| Example 1         | : $V_{CC(I/O)}$ = 1.8 V $\pm$ 0.15 V |                          |                             |     |                         |      |

| Input levels      |                                      |                          |                             |     |                         |      |

| V <sub>IL</sub>   | LOW-level input voltage              |                          | -                           | -   | 0.5                     | V    |

| V <sub>IH</sub>   | HIGH-level input voltage             |                          | 1.2                         | -   | -                       | V    |

| Output leve       | ls                                   |                          |                             |     |                         |      |

| V <sub>OL</sub>   | LOW-level output voltage             | I <sub>OL</sub> = 100 μA | -                           | -   | 0.15                    | V    |

|                   |                                      | $I_{OL} = 2 \text{ mA}$  | -                           | -   | 0.4                     | V    |

#### Table 12: Static characteristics: digital pins...continued

$V_{CC(I/O)}$  = 1.65 V to 3.6 V;  $V_{GND}$  = 0 V;  $T_{amb}$  = -40 °C to +85 °C; unless otherwise specified.

| Symbol          | Parameter                           | Conditions               | Min  | Тур | Max  | Unit |

|-----------------|-------------------------------------|--------------------------|------|-----|------|------|

| V <sub>OH</sub> | HIGH-level output voltage           | l <sub>OH</sub> = 100 μA | 1.5  | -   | -    | V    |

|                 |                                     | I <sub>OH</sub> = 2 mA   | 1.25 | -   | -    | V    |

| Example 2       | : $V_{CC(I/O)}$ = 2.5 V $\pm$ 0.2 V |                          |      |     |      |      |

| Input levels    |                                     |                          |      |     |      |      |

| V <sub>IL</sub> | LOW-level input voltage             |                          | -    | -   | 0.7  | V    |

| V <sub>IH</sub> | HIGH-level input voltage            |                          | 1.7  | -   | -    | V    |

| Output leve     | ls                                  |                          |      |     |      |      |

| V <sub>OL</sub> | LOW-level output voltage            | I <sub>OL</sub> = 100 μA | -    | -   | 0.15 | V    |

|                 |                                     | $I_{OL} = 2 \text{ mA}$  | -    | -   | 0.4  | V    |

| V <sub>OH</sub> | HIGH-level output voltage           | I <sub>OH</sub> = 100 μA | 2.15 | -   | -    | V    |

|                 |                                     | I <sub>OH</sub> = 2 mA   | 1.9  | -   | -    | V    |

| Example 3       | : $V_{CC(I/O)}$ = 3.3 V $\pm$ 0.3 V |                          |      |     |      |      |

| Input levels    |                                     |                          |      |     |      |      |

| V <sub>IL</sub> | LOW-level input voltage             |                          | -    | -   | 0.9  | V    |

| V <sub>IH</sub> | HIGH-level input voltage            |                          | 2.15 | -   | -    | V    |

| Output leve     | ls                                  |                          |      |     |      |      |

| V <sub>OL</sub> | LOW-level output voltage            | I <sub>OL</sub> = 100 μA | -    | -   | 0.15 | V    |

|                 |                                     | $I_{OL} = 2 \text{ mA}$  | -    | -   | 0.4  | V    |

| V <sub>OH</sub> | HIGH-level output voltage           | I <sub>OH</sub> = 100 μA | 2.85 | -   | -    | V    |

|                 |                                     | I <sub>OH</sub> = 2 mA   | 2.6  | -   | -    | V    |

[1] If  $V_{CC(I/O)} \ge V_{reg(3.3)}$ , then the leakage current will be higher than the specified value.

### Table 13: Static characteristics: analog I/O pins D+ and D-

$V_{CC(5.0)} = 4.0$  V to 5.5 V;  $V_{GND} = 0$  V;  $T_{amb} = -40$  °C to +85 °C; unless otherwise specified.

| 00(0.0)          |                                  |                                           | •       |     |     |      |

|------------------|----------------------------------|-------------------------------------------|---------|-----|-----|------|

| Symbol           | Parameter                        | Conditions                                | Min     | Тур | Мах | Unit |

| Input levels     | S                                |                                           |         |     |     |      |

| Differential I   | receiver                         |                                           |         |     |     |      |

| V <sub>DI</sub>  | differential input sensitivity   | $ V_{I(D+)} - V_{I(D-)} $                 | 0.2     | -   | -   | V    |

| V <sub>CM</sub>  | differential common mode voltage | includes V <sub>DI</sub> range            | 0.8     | -   | 2.5 | V    |

| Single-ende      | ed receiver                      |                                           |         |     |     |      |

| V <sub>IL</sub>  | LOW-level input voltage          |                                           | -       | -   | 0.8 | V    |

| V <sub>IH</sub>  | HIGH-level input voltage         |                                           | 2.0     | -   | -   | V    |

| V <sub>hys</sub> | hysteresis voltage               |                                           | 0.4     | -   | 0.7 | V    |

| Output leve      | els                              |                                           |         |     |     |      |

| V <sub>OL</sub>  | LOW-level output voltage         | $R_L$ = 1.5 k $\Omega$ to +3.6 V          | -       | -   | 0.3 | V    |

| V <sub>OH</sub>  | HIGH-level output voltage        | $R_L = 15 \text{ k}\Omega \text{ to GND}$ | [1] 2.8 | -   | 3.6 | V    |

| Leakage cu       | urrent                           |                                           |         |     |     |      |

| I <sub>LZ</sub>  | OFF-state leakage current        |                                           | –1      | -   | +1  | μA   |

|                  |                                  |                                           |         |     |     |      |

#### Table 13: Static characteristics: analog I/O pins D+ and D-...continued

$V_{CC(5.0)} = 4.0$  V to 5.5 V;  $V_{GND} = 0$  V;  $T_{amb} = -40$  °C to +85 °C; unless otherwise specified.

| ( )               |                                                                     |                    |        | -   |     |     |      |

|-------------------|---------------------------------------------------------------------|--------------------|--------|-----|-----|-----|------|

| Symbol            | Parameter                                                           | Conditions         |        | Min | Тур | Max | Unit |

| Capacitanc        | е                                                                   |                    |        |     |     |     |      |

| C <sub>IN</sub>   | transceiver capacitance                                             | pin to GND         |        | -   | -   | 20  | pF   |

| Resistance        |                                                                     |                    |        |     |     |     |      |

| Z <sub>DRV</sub>  | driver output impedance                                             | steady-state drive | [2]    | 34  | 39  | 44  | Ω    |

| Z <sub>INP</sub>  | input impedance                                                     |                    |        | 10  | -   | -   | MΩ   |

| R <sub>SW</sub>   | internal switch resistance at pin $V_{\text{pu}(3.3)}$              |                    |        | -   | -   | 10  | Ω    |

| Termination       | ı                                                                   |                    |        |     |     |     |      |

| V <sub>TERM</sub> | termination voltage for<br>upstream port pull-up (R <sub>pu</sub> ) |                    | [3][4] | 3.0 | -   | 3.6 | V    |

|                   |                                                                     |                    |        |     |     |     |      |

[1]  $V_{OH(min)} = V_{reg(3.3)} - 0.2 V.$

[2] Includes external resistors of 33  $\Omega\pm$ 1 % on both pins D+ and D–.

[3] This voltage is available at pins  $V_{reg(3.3)}$  and  $V_{pu(3.3)}$ .

[4] The minimum voltage is 2.7 V in the suspend mode.

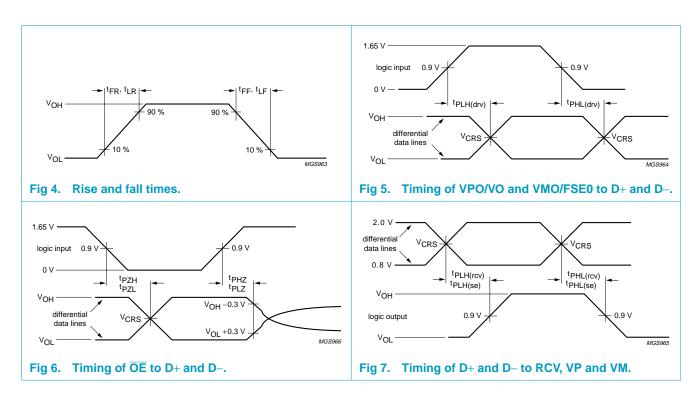

# **12. Dynamic characteristics**

#### Table 14: Dynamic characteristics: analog I/O pins D+ and D-

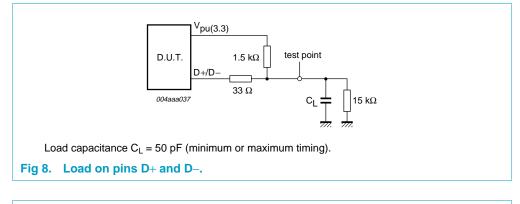

$V_{CC(5.0)} = 4.0$  V to 5.5 V;  $V_{CC(I/O)} = 1.65$  V to 3.6 V;  $V_{GND} = 0$  V;  $T_{amb} = -40$  °C to +85 °C; see Figure 8; unless otherwise specified.

| opoomoa.              |                                                                             |                                                                                                            |                    |     |       |      |

|-----------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|------|

| Symbol                | Parameter                                                                   | Conditions                                                                                                 | Min                | Тур | Max   | Unit |

| Driver char           | acteristics                                                                 |                                                                                                            |                    |     |       |      |

| t <sub>FR</sub>       | rise time                                                                   | C <sub>L</sub> = 50 pF to 125 pF;<br>10 % to 90 % of  V <sub>OH</sub> – V <sub>OL</sub>  ;<br>see Figure 4 | 4                  | -   | 20    | ns   |

| t <sub>FF</sub>       | fall time                                                                   | C <sub>L</sub> = 50 pF to 125 pF;<br>90 % to 10 % of  V <sub>OH</sub> – V <sub>OL</sub>  ;<br>see Figure 4 | 4                  | -   | 20    | ns   |

| FRFM                  | differential rise/fall time<br>matching (t <sub>FR</sub> /t <sub>FF</sub> ) | excluding the first transition from idle state                                                             | 90                 | -   | 111.1 | %    |

| V <sub>CRS</sub>      | output signal crossover voltage                                             | excluding the first transition from idle state; see Figure 5                                               | <sup>[1]</sup> 1.3 | -   | 2.0   | V    |

| <b>Driver timin</b>   | ng                                                                          |                                                                                                            |                    |     |       |      |

| t <sub>PLH(drv)</sub> | driver propagation delay<br>(VPO/VO, VMO/FSE0 to<br>D+, D–)                 | LOW-to-HIGH; see Figure 5                                                                                  | -                  | -   | 18    | ns   |

| t <sub>PHL(drv)</sub> | driver propagation delay<br>(VPO/VO, VMO/FSE0 to<br>D+, D–)                 | HIGH-to-LOW; see Figure 5                                                                                  | -                  | -   | 18    | ns   |

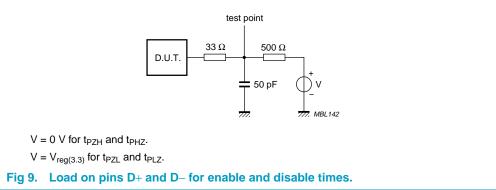

| t <sub>PHZ</sub>      | driver disable delay ( $\overline{OE}$ to D+, D–)                           | HIGH-to-OFF; see Figure 6                                                                                  | -                  | -   | 15    | ns   |

| t <sub>PLZ</sub>      | driver disable delay<br>(OE to D+, D–)                                      | LOW-to-OFF; see Figure 6                                                                                   | -                  | -   | 15    | ns   |

#### Table 14: Dynamic characteristics: analog I/O pins D+ and D-...continued

$V_{CC(5.0)} = 4.0 \text{ V to } 5.5 \text{ V}; V_{CC(I/O)} = 1.65 \text{ V to } 3.6 \text{ V}; V_{GND} = 0 \text{ V}; T_{amb} = -40 \circ \text{C} \text{ to } +85 \circ \text{C}; \text{ see Figure 8}; \text{ unless otherwise specified.}$

| Symbol                | Parameter                               | Conditions                | Min | Тур | Max | Unit |

|-----------------------|-----------------------------------------|---------------------------|-----|-----|-----|------|

| t <sub>PZH</sub>      | driver enable delay<br>(OE to D+, D–)   | OFF-to-HIGH; see Figure 6 | -   | -   | 15  | ns   |

| t <sub>PZL</sub>      | driver enable delay<br>(OE to D+, D–)   | OFF-to-LOW; see Figure 6  | -   | -   | 15  | ns   |

| Receiver ti           | mings                                   |                           |     |     |     |      |

| Differential          | receiver                                |                           |     |     |     |      |

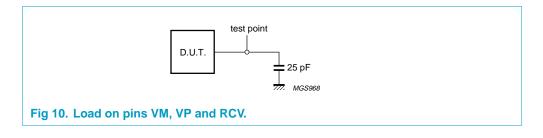

| t <sub>PLH(rcv)</sub> | propagation delay<br>(D+, D– to RCV)    | LOW-to-HIGH; see Figure 7 | -   | -   | 15  | ns   |

| t <sub>PHL(rcv)</sub> | propagation delay<br>(D+, D– to RCV)    | HIGH-to-LOW; see Figure 7 | -   | -   | 15  | ns   |

| Single-ende           | ed receiver                             |                           |     |     |     |      |

| t <sub>PLH(se)</sub>  | propagation delay<br>(D+, D– to VP, VM) | LOW-to-HIGH; see Figure 7 | -   | -   | 18  | ns   |

| t <sub>PHL(se)</sub>  | propagation delay<br>(D+, D– to VP, VM) | HIGH-to-LOW; see Figure 7 | -   | -   | 18  | ns   |

|                       |                                         |                           |     |     |     |      |

[1] Characterized only, not tested. Limits guaranteed by design.

**Product data**

# **13. Test information**

Downloaded from Elcodis.com electronic components distributor

## 14. Package outline

#### Fig 11. HBCC16 package outline.

9397 750 11229

**Product data**

### 15. Packaging

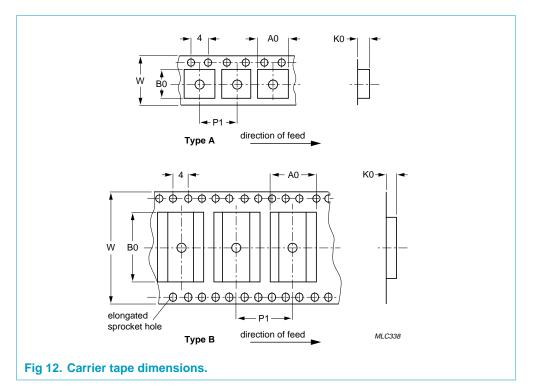

The ISP1104W (HBCC16 package) is delivered on a type A carrier tape, see Figure 12. The tape dimensions are given in Table 15.

The reel diameter is 330 mm. The reel is made of polystyrene (PS) and is not designed for use in a baking process.

The cumulative tolerance of 10 successive sprocket holes is  $\pm 0.02$  mm. The camber must not exceed 1 mm in 100 mm.

Table 15:

Type A carrier tape dimensions for the ISP1104W

| Dimension | Value        | Unit |

|-----------|--------------|------|

| A0        | 3.3          | mm   |

| В0        | 3.3          | mm   |

| К0        | 1.1          | mm   |

| P1        | 8.0          | mm   |

| W         | $12.0\pm0.3$ | mm   |

# **16. Additional soldering information**

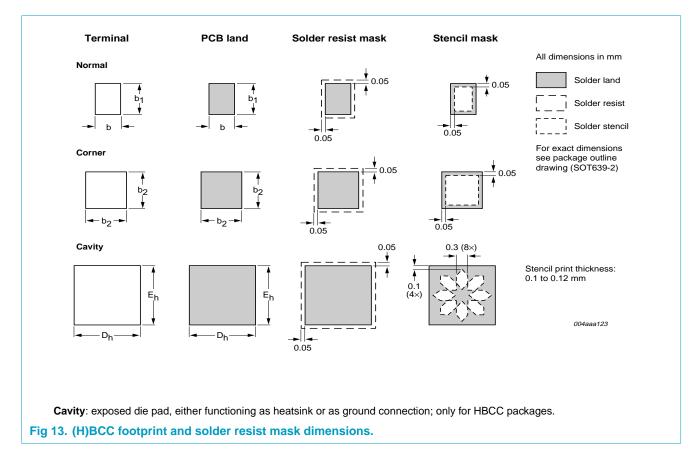

### 16.1 (H)BCC packages: footprint

The surface material of the terminals on the resin protrusion consists of a 4-layer metal structure (Au, Pd, Ni and Pd). The Au + Pd layer (0.1  $\mu$ m min.) ensures solderability, the Ni layer (5  $\mu$ m min.) prevents diffusion, and the Pd layer on top (0.5  $\mu$ m min.) ensures effective wire bonding.

### 16.2 (H)BCC packages: reflow soldering profile

The conditions for reflow soldering of (H)BCC packages are as follows:

- Preheating time: minimum 90 s at T = 145 to 155 °C

- Soldering time: minimum 90 s (BCC) or minimum 100 s (HBCC) at T > 183 °C

- Peak temperature:

- Ambient temperature: T<sub>amb(max)</sub> = 260 °C

- Device surface temperature:  $T_{case(max)} = 255 \ ^{\circ}C$ .

9397 750 11229

# **17. Revision history**

| Table | 16:   | Revisi | ion history |                                                                                                                     |

|-------|-------|--------|-------------|---------------------------------------------------------------------------------------------------------------------|

| Rev   | Date  |        | CPCN        | Description                                                                                                         |

| 02    | 20031 | 014    | -           | Product data (9397 750 11229)                                                                                       |

|       |       |        |             | Modifications:                                                                                                      |

|       |       |        |             | <ul> <li>Changed USB 1.1 reference to USB 2.0; also added data transfer rates</li> </ul>                            |

|       |       |        |             | Section 2: updated                                                                                                  |

|       |       |        |             | • Figure 1, Figure 8 and Figure 9: removed the figure note on 33 $\Omega$                                           |

|       |       |        |             | <ul> <li>Table 2: updated the description for pin 8; added pad details</li> </ul>                                   |

|       |       |        |             | <ul> <li>Section 7.3 sharing mode: updated the first sentence</li> </ul>                                            |

|       |       |        |             | • Table 8: updated                                                                                                  |

|       |       |        |             | Table 9: added a table note                                                                                         |

|       |       |        |             | <ul> <li>Table 11: changed I<sub>CC(dis)</sub> to I<sub>CC-I/O(dis)</sub>; also, changed the description</li> </ul> |

|       |       |        |             | <ul> <li>Table 13: removed Z<sub>DRV2</sub>, and also the relevant (old) table note 3.</li> </ul>                   |

| 01    | 20020 | )826   | -           | Product data (9397 750 09784)                                                                                       |

### **18. Data sheet status**

| Level | Data sheet status <sup>[1]</sup> | Product status <sup>[2][3]</sup> | Definition                                                                                                                                                                                                                                                                                     |

|-------|----------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I     | Objective data                   | Development                      | This data sheet contains data from the objective specification for product development. Philips<br>Semiconductors reserves the right to change the specification in any manner without notice.                                                                                                 |

| II    | Preliminary data                 | Qualification                    | This data sheet contains data from the preliminary specification. Supplementary data will be published<br>at a later date. Philips Semiconductors reserves the right to change the specification without notice, in<br>order to improve the design and supply the best possible product.       |

| 111   | Product data                     | Production                       | This data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design, manufacturing and supply. Relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). |

[1] Please consult the most recently issued data sheet before initiating or completing a design.

[2] The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.

[3] For data sheets describing multiple type numbers, the highest-level product status determines the data sheet status.

### **19. Definitions**

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

# **20. Disclaimers**

Life support — These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

**Right to make changes** — Philips Semiconductors reserves the right to make changes in the products - including circuits, standard cells, and/or software - described or contained herein in order to improve design and/or performance. When the product is in full production (status 'Production'), relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no licence or title under any patent, copyright, or mask work right to these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

### **Contact information**

For additional information, please visit http://www.semiconductors.philips.com. For sales office addresses, send e-mail to: sales.addresses@www.semiconductors.philips.com.

9397 750 11229

**Product data**

Fax: +31 40 27 24825

© Koninklijke Philips Electronics N.V. 2003. All rights reserved.

### **Contents**

| 1    | General description                       | 1        |

|------|-------------------------------------------|----------|

| 2    | Features                                  | 1        |

| 3    | Applications                              | 1        |

| 4    | Ordering information                      | 2        |

| 5    | Block diagram                             | 2        |

| 6    | Pinning information                       | 3        |

| 6.1  | Pinning                                   | 3        |

| 6.2  | Pin description                           | 3        |

| 7    | Functional description                    | 5        |

| 7.1  | Function selection                        | -        |

| 7.2  | Operating functions                       |          |

| 7.3  | Power supply configurations               |          |

| 8    | Electrostatic discharge (ESD)             |          |

| 8.1  | ESD protection                            |          |

| 8.2  | ESD test conditions                       |          |

| 9    | Limiting values                           |          |

| 10   | Recommended operating conditions          |          |

| 11   | Static characteristics                    | 8        |

| 12   | Dynamic characteristics                   | 11       |

| 13   | Test information                          | 13       |

| 14   | Package outline                           | 14       |

| 15   | Packaging                                 | 15       |

| 16   | Soldering                                 | 16       |

| 16.1 | Introduction to soldering surface mount   | 40       |

| 16.2 | packages                                  | 16<br>16 |

| 16.3 | Wave soldering                            | 16       |

| 16.4 | Manual soldering                          | 17       |

| 16.5 | Package related soldering information     | 17       |

| 17   |                                           | 19       |

| 17.1 | (H)BCC packages: footprint                | 19       |

| 17.2 | (H)BCC packages: reflow soldering profile | 19       |

| 18   | Revision history                          | 20       |

| 19   | Data sheet status                         | 21       |

| 20   | Definitions                               | 21       |

| 21   | Disclaimers                               | 21       |

|      |                                           |          |

#### © Koninklijke Philips Electronics N.V. 2003. Printed in The Netherlands

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

Let's make things better.