### INTEGRATED CIRCUITS

# DATA SHEET

# **SA8025A**

Low-voltage 1.8GHz fractional-N synthesizer

Product specification

1996 Oct 15

IC17 Data Handbook

### 1.8GHz low-voltage Fractional-N synthesizer

**SA8025A**

#### DESCRIPTION

The SA8025A is a monolithic low power, high performance dual frequency synthesizer fabricated in QUBiC BiCMOS technology. The SA8025A is an improved version of the SA8025, suitable for narrow band systems like the Japan Personal Digital Cellular (PDC) system. The new design improves the performance of the fractional spur compensation circuitry. The new version is pin-for-pin compatible with the previous version. Featuring Fractional-N division with selectable modulo 5 or 8 implemented in the Main synthesizer to allow the phase detector comparison frequency to be five or eight times the channel spacing. This feature reduces the overall division ratio yielding a lower noise floor and faster channel switching. The phase detectors and charge pumps are designed to achieve phase detector comparison frequencies up to 5MHz. A four modulus prescaler (divide by 64/65/68/73) is integrated on chip with a maximum input frequency of 1.8GHz at 3V. Programming and channel selection are realized by a high speed 3-wire serial interface. A 1GHz version (SA7025DK) is also available with the same pinout.

#### **FEATURES**

- Operation up to 1.8GHz at 3V

- Fast locking by "Fractional-N" divider

- Auxiliary synthesizer

- Digital phase comparator with proportional and integral charge pump output

- High speed serial input

- Low power consumption

- Programmable charge pump currents

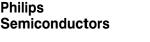

#### PIN CONFIGURATION

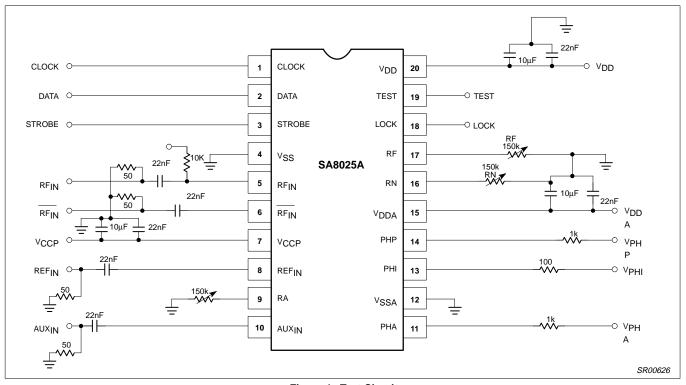

Figure 1. Pin Configuration

- Supply voltage range 2.7 to 5.5V

- Excellent input sensitivity: V<sub>RF IN</sub> = −20dBm

#### **APPLICATIONS**

- PHS (Personal Handy-phone System)

- PDC (Personal Digital Cellular)

- PCS (Personal Communication Service)

- Portable communication systems

#### ORDERING INFORMATION

| DESCRIPTION                                        | TEMPERATURE RANGE | ORDER CODE | DWG#     |

|----------------------------------------------------|-------------------|------------|----------|

| 20-Pin Plastic Shrink Small Outline Package (SSOP) | −40 to +85°C      | SA8025ADK  | SOT266-1 |

#### **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL           | PARAMETER                                                             | RATING                          | UNITS |

|------------------|-----------------------------------------------------------------------|---------------------------------|-------|

| V                | Supply voltage, V <sub>DD</sub> , V <sub>DDA</sub> , V <sub>CCP</sub> | -0.3 to +6.0                    | V     |

| V <sub>IN</sub>  | Voltage applied to any other pin                                      | -0.3 to (V <sub>DD</sub> + 0.3) | V     |

| T <sub>STG</sub> | Storage temperature range                                             | -65 to +150                     | °C    |

| T <sub>A</sub>   | Operating ambient temperature range                                   | -40 to +85                      | °C    |

**NOTE:** Thermal impedance ( $\theta_{JA}$ ) = 117°C/W. This device is ESD sensitive.

# 1.8GHz low-voltage Fractional-N synthesizer

SA8025A

### **PIN DESCRIPTIONS**

| Symbol            | Pin | Description                                                                                                               |

|-------------------|-----|---------------------------------------------------------------------------------------------------------------------------|

| CLOCK             | 1   | Serial clock input                                                                                                        |

| DATA              | 2   | Serial data input                                                                                                         |

| STROBE            | 3   | Serial strobe input                                                                                                       |

| V <sub>SS</sub>   | 4   | Digital ground                                                                                                            |

| RF <sub>IN</sub>  | 5   | Prescaler positive input                                                                                                  |

| RFIN              | 6   | Prescaler negative input                                                                                                  |

| V <sub>CCP</sub>  | 7   | Prescaler positive supply voltage. This pin supplies power to the prescaler and RF input buffer                           |

| REF <sub>IN</sub> | 8   | Reference divider input                                                                                                   |

| RA                | 9   | Auxiliary current setting; resistor to V <sub>SSA</sub>                                                                   |

| AUX <sub>IN</sub> | 10  | Auxiliary divider input                                                                                                   |

| PHA               | 11  | Auxiliary phase detector output                                                                                           |

| V <sub>SSA</sub>  | 12  | Analog ground                                                                                                             |

| PHI               | 13  | Integral phase detector output                                                                                            |

| PHP               | 14  | Proportional phase detector output                                                                                        |

| V <sub>DDA</sub>  | 15  | Analog supply voltage. This pin supplies power to the charge pumps, Auxiliary prescaler, Auxiliary and Reference buffers. |

| RN                | 16  | Main current setting; resistor to V <sub>SSA</sub>                                                                        |

| RF                | 17  | Fractional compensation current setting; resistor to V <sub>SSA</sub>                                                     |

| LOCK              | 18  | Lock detector output                                                                                                      |

| TEST              | 19  | Test pin; connect to V <sub>DD</sub>                                                                                      |

| V <sub>DD</sub>   | 20  | Digital supply voltage. This pin supplies power to the CMOS digital part of the device                                    |

# 1.8GHz low-voltage Fractional-N synthesizer

SA8025A

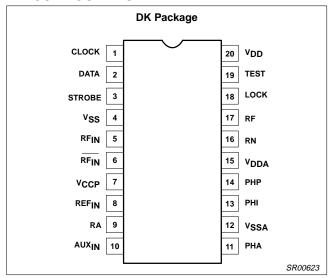

#### **BLOCK DIAGRAM**

Figure 2. Block Diagram

# 1.8GHz low-voltage Fractional-N synthesizer

SA8025A

#### DC ELECTRICAL CHARACTERISTICS

$V_{DD} = V_{DDA} = V_{CCP} = 3V$ ;  $T_A = 25^{\circ}C$ , unless otherwise specified.

| SYMBOL                                 | PARAMETER                                                       | TEST CONDITIONS                                                 |                      | LIMITS   |                       | UNITS |  |

|----------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------|----------------------|----------|-----------------------|-------|--|

| STWIBUL                                | PARAMETER                                                       | TEST CONDITIONS                                                 | MIN                  | TYP      | MAX                   | UNITS |  |

| V <sub>SUPPLY</sub>                    | Recommended operating conditions                                | $V_{CCP} = V_{DD}, V_{DDA} \ge V_{DD}$                          | 2.7                  |          | 5.5                   | V     |  |

| I <sub>STANDBY</sub>                   | Total standby supply currents                                   | $EM = EA = 0, I_{RN} = I_{RF} = I_{RA} = 0$                     |                      | 50       | 500                   | μΑ    |  |

| Operational                            | supply currents: $I = I_{DD} + I_{CCP} + I_{DDA}$ ; $I$         | $_{RN}$ = 25 $\mu$ A, $I_{RA}$ = 25 $\mu$ A, (see Note 5)       |                      |          |                       |       |  |

| $I_{AUX}$                              | Operational supply currents                                     | EM = 0, EA = 1                                                  |                      | 3.5      |                       | mA    |  |

| I <sub>MAIN</sub>                      | Operational supply currents                                     | EM = 1, EA = 0                                                  |                      | 11.0     |                       | mA    |  |

| I <sub>TOTAL</sub>                     | Operational supply currents                                     | EM = EA = 1                                                     |                      | 13.5     |                       | mA    |  |

| Digital inpu                           | ts CLK, DATA, STROBE                                            |                                                                 |                      |          |                       |       |  |

| $V_{IH}$                               | High level input voltage range                                  |                                                                 | 0.7xV <sub>DD</sub>  |          | $V_{DD}$              | V     |  |

| $V_{IL}$                               | Low level input voltage range                                   |                                                                 | 0                    |          | 0.3xV <sub>DD</sub>   | V     |  |

| Digital outp                           | uts LOCK                                                        |                                                                 |                      |          |                       |       |  |

| $V_{OL}$                               | Output voltage LOW                                              | I <sub>O</sub> = 2mA                                            |                      |          | 0.4                   | V     |  |

| V <sub>OH</sub>                        | Output voltage HIGH                                             | $I_O = -2mA$                                                    | V <sub>DD</sub> -0.4 |          |                       | V     |  |

| Charge pun                             | nps: $V_{DDA} = 3V / I_{RX} = 25\mu A$ or $V_{DDA} = 5^{\circ}$ | V / I <sub>RX</sub> = 62.5μA, V <sub>PHX</sub> in range, unless | otherwise sp         | ecified. |                       |       |  |

|                                        | Setting current range for any setting re-                       | 2.7V < V <sub>DDA</sub> < 5.5V                                  |                      | 25       |                       |       |  |

| I <sub>RX</sub>                        | sistor                                                          | 4.5V < V <sub>DDA</sub> < 5.5V                                  |                      | 62.5     |                       | μΑ    |  |

| V <sub>PHOUT</sub>                     | Output voltage range                                            |                                                                 | 0.7                  |          | V <sub>DDA</sub> -0.8 | V     |  |

| Charge pun                             | np PHA                                                          | •                                                               |                      |          |                       | •     |  |

|                                        |                                                                 | $I_{RN} = -62.5\mu A; V_{PHP} = V_{DDA}/2^{13}$                 | 400                  | 500      | 600                   |       |  |

| I <sub>PHA</sub>                       | Output current PHA                                              | $I_{RN} = -25\mu A; V_{PHP} = V_{DDA}/2$                        | 160                  | 200      | 240                   | μΑ    |  |

| $\Delta I_{PHP\_A}$                    |                                                                 |                                                                 |                      | _        |                       | ٠,    |  |

| I I <sub>PHP_A</sub>                   | Relative output current variation PHA                           | $I_{RA} = -62.5 \mu A^{2, 13}$                                  |                      | 2        | 6                     | %     |  |

| ' FHF_A'                               |                                                                 | V <sub>DDA</sub> = 3V, I <sub>RA</sub> = 25μA                   |                      |          | ±50                   |       |  |

| $\Delta I_{PHA_{M}}$                   | Output current matching PHA pump                                | $V_{DDA} = 5V, I_{RA} = 62.5\mu A$                              |                      |          | ±65                   | μΑ    |  |

| Charge pun                             | np PHP, normal mode <sup>NO TAG, 4, 6</sup> V <sub>RF</sub> =   |                                                                 |                      |          |                       |       |  |

| 3- p                                   | I Ki                                                            | $I_{RN} = -62.5\mu A; V_{PHP} = V_{DDA}/2^{13}$                 | 440                  | 550      | 660                   |       |  |

| I <sub>PHP_N</sub>                     | Output current PHP                                              | $I_{RN} = -25\mu A; V_{PHP} = V_{DDA}/2$                        | 175                  | 220      | 265                   | μΑ    |  |

| ΔΙ                                     |                                                                 |                                                                 | 1                    |          | 1                     |       |  |

| $\frac{\Delta I_{PHP_N}}{I_{-\cdots}}$ | Relative output current variation PHP                           | $I_{RN} = -62.5 \mu A^{2, 13}$                                  |                      | 2        | 6                     | %     |  |

| I <sub>PHP_N</sub>                     | Outside some of sectoric at DLID                                | V <sub>DDA</sub> = 3V, I <sub>RA</sub> = 25μA                   | 1                    |          | ±50                   |       |  |

| $\Delta I_{PHP\_N\_M}$                 | Output current matching PHP normal mode                         | $V_{DDA} = 5V, I_{RA} = 62.5\mu A$                              | 1                    |          | ±65                   | μΑ    |  |

|                                        | np PHP, speed-up mode <sup>NO TAG, 4, 7</sup> V <sub>RF</sub>   |                                                                 |                      |          | ±05                   |       |  |

| Charge pun                             | T                                                               | $I_{RN} = -62.5\mu A; V_{PHP} = V_{DDA}/2^{13}$                 | 2.20                 | 2.75     | 3.30                  |       |  |

| I <sub>PHP_S</sub>                     | Output current PHP                                              | $I_{RN} = -02.5\mu A$ , $V_{PHP} = V_{DDA}/2$                   | 0.85                 | 1.1      | 1.35                  | mΑ    |  |

| A.I.                                   |                                                                 | $I_{RN} = -25\mu A$ , $V_{PHP} = V_{DDA}/2$                     | 0.83                 | 1.1      | 1.55                  |       |  |

| $\frac{\Delta I_{PHP\_S}}{I}$          | Relative output current variation PHP                           | $I_{RN} = -62.5 \mu A^{2, 13}$                                  |                      | 2        | 6                     | %     |  |

| I <sub>PHP_S</sub>                     |                                                                 | V 0V 1 05 A                                                     |                      |          | 1050                  |       |  |

| $\Delta I_{PHP\_S\_M}$                 | Output current matching PHP speed-up mode                       | $V_{DDA} = 3V, I_{RA} = 25\mu A$                                |                      |          | ±250                  | μΑ    |  |

|                                        | 1                                                               | $V_{DDA} = 5V, I_{RA} = 62.5\mu A$                              |                      |          | ±300                  | ·     |  |

| Charge pun                             | p PHI, speed-up mode NO TAG, 4, 8 V <sub>RF</sub>               |                                                                 |                      |          | ,                     |       |  |

| l <sub>PHI</sub>                       | Output current PHI                                              | $I_{RN} = -62.5 \mu A; V_{PHI} = V_{DDA}/2^{13}$                | 4.4                  | 5.5      | 6.6                   | mA    |  |

|                                        | ·                                                               | $I_{RN} = -25\mu A; V_{PHI} = V_{DDA}/2$                        | 1.75                 | 2.2      | 2.65                  |       |  |

| $rac{\Delta I_{PHI}}{I_{PHI}}$        | Relative output current variation PHI                           | $I_{RN} = -62.5 \mu A^{2, 13}$                                  |                      | 2        | 8                     | %     |  |

|                                        | 0.45.4                                                          | V <sub>DDA</sub> = 3V, I <sub>RA</sub> = 25μA                   |                      |          | ±500                  |       |  |

| $\Delta I_{	ext{PHI\_M}}$              | Output current matching PHI pump                                | V <sub>DDA</sub> = 5V, I <sub>RA</sub> = 62.5μA                 | 1 1                  |          | ±600                  | μΑ    |  |

|                                        | <u> </u>                                                        |                                                                 |                      |          |                       |       |  |

| Fractional c                           | compensation PHP, normal mode NO TAG                            | $V_{\rm N} = V_{\rm DDA}, V_{\rm PHP} = V_{\rm DDA}/2$          |                      |          |                       |       |  |

| Fractional c                           | Fractional compensation output current                          | $I_{RF} = -62.5\mu A; F_{RD} = 1 \text{ to } 7^{13}$            | -625                 | -400     | -250                  | nA    |  |

# 1.8GHz low-voltage Fractional-N synthesizer

SA8025A

#### DC ELECTRICAL CHARACTERISTICS (Continued)

| CVMDOL             | DADAMETED                                                 | TEST COMPITIONS                                                                     |       | LIMITS |      |       |  |

|--------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------|-------|--------|------|-------|--|

| SYMBOL             | PARAMETER                                                 | TEST CONDITIONS                                                                     | MIN   | TYP    | MAX  | UNITS |  |

| Fractional of      | compensation PHP, speed up mode NO TA                     | $^{\text{G, 10}}$ $V_{\text{PHP}} = V_{\text{DDA}}, V_{\text{RN}} = V_{\text{DDA}}$ |       |        |      |       |  |

|                    | Fractional compensation output current                    | $I_{RF} = -62.5\mu A; F_{RD} = 1 \text{ to } 7^{13}$                                | -3.35 | -2     | -1.1 |       |  |

| PHP_F_S            | PHP vs F <sub>RD</sub> <sup>3</sup>                       | $I_{RF} = -25\mu A; F_{RD} = 1 \text{ to } 7$                                       | -1.35 | -1.0   | -0.5 | μΑ    |  |

|                    | Pump leakage                                              |                                                                                     | -20   |        | 20   | nA    |  |

| Charge pun         | np leakage currents, charge pump not ac                   | tive                                                                                |       |        |      | -     |  |

| I <sub>PHP_L</sub> | Output leakage current PHP; normal mode <sup>NO TAG</sup> | $V_{PHP} = 0.7 \text{ to } V_{DDA} - 0.8$                                           |       | 0.1    | 20   | nA    |  |

| I <sub>PHI_L</sub> | Output leakage current PHI; normal mode <sup>NO TAG</sup> | $V_{PHI} = 0.7$ to $V_{DDA} - 0.8$                                                  |       | 0.1    | 20   | nA    |  |

| I <sub>PHA_L</sub> | Output leakage current PHA                                | $V_{PHA} = 0.7 \text{ to } V_{DDA} - 0.8$                                           |       | 0.1    | 20   | nA    |  |

#### **AC ELECTRICAL CHARACTERISTICS**

$V_{DD} = V_{DDA} = V_{CCP} = 3V$ ;  $T_A = 25^{\circ}$ C; unless otherwise specified. Test Circuit, Figure 4. The parameters listed below are tested using automatic test equipment to assure consistent electrical characteristics. The limits do not represent the ultimate performance limits of the device. Use of an optimized RF layout will improve many of the listed parameters.

| 0)/440.01           | DADAMETED                                                              | TEST SOUDITIONS                                   |            | LIMITS       |             | 1                 |

|---------------------|------------------------------------------------------------------------|---------------------------------------------------|------------|--------------|-------------|-------------------|

| SYMBOL              | PARAMETER                                                              | TEST CONDITIONS                                   | MIN        | TYP          | MAX         | UNITS             |

| Main divid          | er guaranteed and tested on an automatic tester.                       | Some performance parameters may be                | improved b | y using opti | mized layou | ıt.               |

| <b>4</b>            | Input signal frequency                                                 | Pin = -20dBm, Direct coupled input <sup>14</sup>  | 0          |              | 1.8         | GHz               |

| f <sub>RF_IN</sub>  | Imput signal frequency                                                 | Pin = -20dBm, 1000pF input coupling               |            |              | 1.8         | GHZ               |

| $V_{RF\_IN}$        | Input sensitivity                                                      | f <sub>IN</sub> = 1800MHz                         | -20        |              | 0           | dBm               |

| Reference           | divider ( $V_{DD} = V_{DDA} = 3V$ or $V_{DD} = 3V / V_{DDA} =$         | 5V)                                               |            |              |             |                   |

| fore w              | Input signal frequency                                                 | 2.7 < V <sub>DD</sub> and V <sub>DDA</sub> < 5.5V |            |              | 25          | MHz               |

| f <sub>REF_IN</sub> | input signal frequency                                                 | 2.7 < V <sub>DD</sub> and V <sub>DDA</sub> < 4.5V |            |              | 30          | IVII IZ           |

| V                   | Input signal range, AC coupled                                         | 2.7 < V <sub>DD</sub> and V <sub>DDA</sub> < 5.5V | 500        |              |             | mV <sub>P-P</sub> |

| $V_{REF\_IN}$       | Imput signal range, AC coupled                                         | $2.7 < V_{DD}$ and $V_{DDA} < 4.5V$               | 300        |              |             | IIIVP-P           |

| 7                   | Reference divider input impedance <sup>15</sup>                        |                                                   |            | 100          |             | kΩ                |

| Z <sub>REF_IN</sub> | Reference divider input impedance **                                   |                                                   |            | 3            |             | pF                |

| Auxiliary of        | divider                                                                |                                                   |            |              |             |                   |

|                     | Input signal frequency                                                 |                                                   | 0          |              | 50          |                   |

| ٠                   | PA = "0", prescaler enabled                                            | $4.5V \le V_{DDA} \le 5.5V$                       | 0          |              | 150         | MHz               |

| f <sub>AUX_IN</sub> | Input signal frequency                                                 |                                                   | 0          |              | 30          | ]                 |

|                     | PA = "1", prescaler disabled                                           | $4.5V \le V_{DDA} \le 5.5V$                       | 0          |              | 40          |                   |

| V <sub>AUX_IN</sub> | Input signal range, AC coupled                                         |                                                   | 200        |              |             | $mV_{P-P}$        |

| 7                   | Auxiliary divider input impedance <sup>15</sup>                        |                                                   |            | 100          |             | kΩ                |

| Z <sub>AUX_IN</sub> | , , ,                                                                  |                                                   |            | 3            |             | pF                |

| Serial inte         | rface <sup>15</sup>                                                    |                                                   |            |              |             |                   |

| f <sub>CLOCK</sub>  | Clock frequency                                                        |                                                   |            |              | 10          | MHz               |

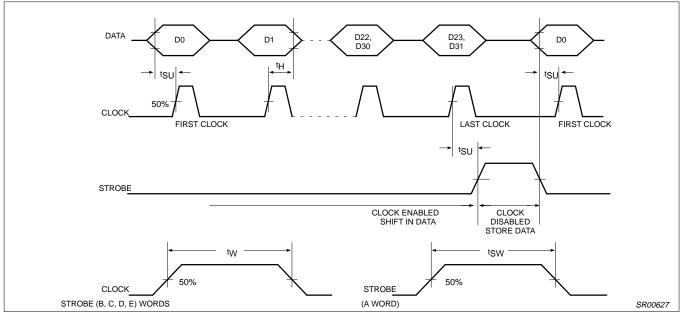

| t <sub>SU</sub>     | Set-up time: DATA to CLOCK,<br>CLOCK to STROBE                         |                                                   | 30         |              |             | ns                |

| t <sub>H</sub>      | Hold time; CLOCK to DATA                                               |                                                   | 30         |              |             | ns                |

| 4                   | Pulse width; CLOCK                                                     |                                                   | 30         |              |             | no                |

| t <sub>W</sub>      | Pulse width; STROBE                                                    | B, C, D, E words                                  | 30         |              |             | ns                |

| In-Loop Po          | erformance <sup>16</sup> V <sub>DDA</sub> = 5V, V <sub>DD</sub> = 2.7V |                                                   |            |              |             |                   |

| RF <sub>MM</sub>    | Main loop residual FM                                                  | F <sub>VCO</sub> = 1780MHz                        |            | 600          | 900         | Hz                |

### 1.8GHz low-voltage Fractional-N synthesizer

SA8025A

#### AC ELECTRICAL CHARACTERISTICS (Continued)

| SYMBOL          | PARAMETER           | TEST CONDITIONS   |                                 | UNITS          |                             |       |

|-----------------|---------------------|-------------------|---------------------------------|----------------|-----------------------------|-------|

| STWIBUL         | PARAMETER           | TEST CONDITIONS   | MIN                             | TYP            | MAX                         | UNITS |

|                 |                     | A word, PR = '01' | $\frac{1}{f_{VCO}}$ · (N        | IM2 · 65) ·    | + t <sub>W</sub>            |       |

|                 |                     | A word, PR = '10' | 'vco                            |                | + 1) · 68] + t <sub>W</sub> |       |

| t <sub>SW</sub> | Pulse width; STROBE | A word, PR = '11' | 1<br>f <sub>VCO</sub> + (NM4 +  | 12 · 65 + (NM3 |                             | ns    |

|                 |                     | A word, PR = '00' | $\frac{1}{f_{VCO}} \cdot [(NM2$ | · 65) + (NM4 · | + 1) · 73] + t <sub>W</sub> |       |

#### NOTES:

When a serial input "A" word is programmed, the main charge pumps on PHP and PHI are in the "speed up mode" as long as STROBE = H. When this is not the case, the main charge pumps are in the "normal mode".

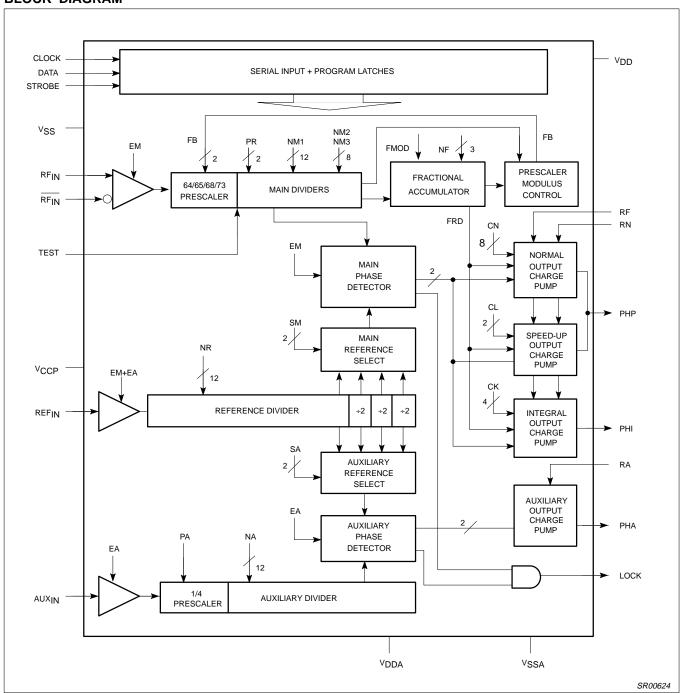

2. The relative output current variation is defined thus:

$$\frac{\Delta I_{OUT}}{I_{OUT}} = 2 \cdot \frac{(I_2 - I_1)}{|(I_2 + I_1)|} \text{ with } V_1 = 0.7V, V_2 = V_{DDA} - 0.8V \text{ (see Figure 3)}.$$

- 3. F<sub>RD</sub> is the value of the 3 bit fractional accumulator.

4. Monotonicity is guaranteed with C<sub>N</sub> = 0 to 255.

- Power supply current measured with  $f_{RF\_IN}$  = 1667.4MHz, NM1 = 0, NM2 = 1, NM3 = 1, NM4 = 4, FMOD = 8, N = 694 6/8, main phase detector frequency = 2.4MHz,  $f_{REF\ IN}$  = 19.2MHz, NR = 8, SM = 1,  $f_{AUX\_IN}$  = 150MHz, NA = 125, SA = 1, PA = 0, auxiliary phase detector frequency = 300kHz, IRN = IRA = IRF = 25 $\mu$ A, CN = 160, CL = 0, CK = 0, lock condition, normal mode,  $V_{CCP}$  =  $V_{DD}$  =  $V_{DDA}$  = 3V. Operational supply current =  $I_{DDA} + I_{DD} + I_{CCP}$ . Specification condition: CN = 255

- 7. Specification conditions:

8. Typical output current |  $I_{PHI}$  | =  $-I_{RN}$  x CN x 2<sup>(CL+1)</sup> x CK/32: 1) CN = 160; CL = 3; CK = 1, or

4) CN = 160; CL = 0; CK = 8

- 9. Any RFD, CL = 1 for speed-up pump. The integral pump is intended for switching only and the fractional compensation is not guaranteed. 10. Specification conditions: F<sub>RD</sub> = 1 to 7; CL = 1.

- 11. Specification conditions:

1)

$$F_{RD} = 1$$

to 7;  $CL = 1$ ;  $CK = 2$ , or

- 1) F<sub>RD</sub> = 1 to 7; CL = 1; CK = 2, or

2) F<sub>RD</sub> = 1 to 7; CL = 2; CK = 1.

12. The matching is defined by the sum of the P and the N pump for a given output voltage.

- 13. Limited analog supply voltage range 4.5 to 5.5V.

- 14. For f<sub>IN</sub> < 50MHz, low frequency operation requires DC-coupling and a minimum input slew rate of 32V/μs.

- 15. Guaranteed by design.

- 16. F<sub>XTAL</sub> = 14.4MHz, V<sub>XTAL</sub> = 500mV<sub>P-P</sub>, comparison Freq. = 200kHz, Loop bandwidth = 5kHz, Audio filter = 300Hz to 15kHz.

# 1.8GHz low-voltage Fractional-N synthesizer

SA8025A

Figure 3. Relative Output Current Variation

Figure 4. Test Circuit

### 1.8GHz low-voltage Fractional-N synthesizer

SA8025A

#### AC TIMING CHARACTERISTICS

Figure 5. Serial Input Timing Sequence

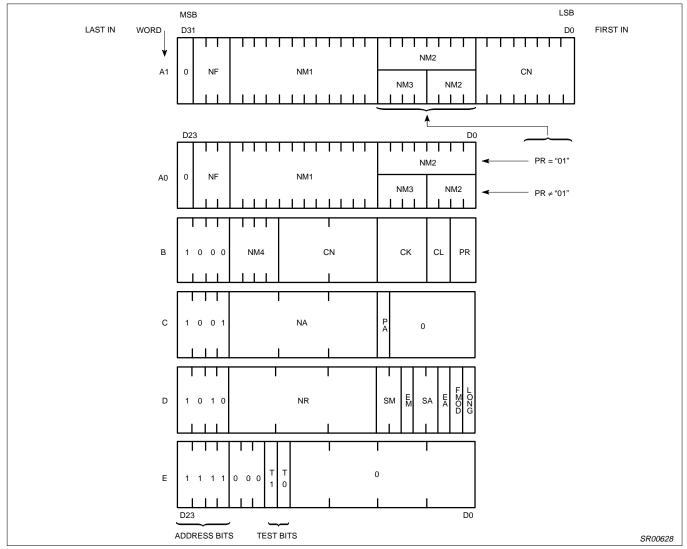

#### FUNCTIONAL DESCRIPTION Serial Input Programming

The serial input is a 3-wire input (CLOCK, STROBE, DATA) to program all counter ratios, DACs, selection and enable bits. The programming data is structured into 24 or 32 bit words; each word includes 1 or 4 address bits. Figure 5 shows the timing diagram of the serial input. When the STROBE = L, the clock driver is enabled and on the positive edges of the CLOCK the signal on DATA input is clocked into a shift register. When the STROBE = H, the clock is disabled and the data in the shift register remains stable. Depending on the 1 or 4 address bits the data is latched into different working registers or temporary registers. In order to fully program the synthesizer, 4 words must be sent: D, C, B and A. Figure 6 and Table 1 shows the format and the contents of each word. The E word is for testing purposes only. The E (test) word is reset when programming the D word. The data for CN and PR is stored by the B word in temporary registers. When the A word is loaded, the data of these temporary registers is loaded together with the A word into the work registers which avoids false temporary main divider input. CN is only loaded from the temporary registers when a short 24 bit A0 word is used. CN will be directly loaded by programming a long 32 bit A1 word. The flag LONG in the D word determines whether A0 (LONG = "0") or A1 (LONG = "1") format is applicable. The A word contains new data for the main divider.

#### Main Divider Synchronization

The A word is loaded only when a main divider synchronization signal is also active in order to avoid phase jumps when reprogramming the main divider. The synchronization signal is generated by the main divider. The signal is active while the NM1 divider is counting down from the programmed value. The new A word will be loaded after the NM1 divider has reached its terminal count; also, at this time a main divider output pulse will be sent to the main phase detector. The loading of the A word is disabled while the other dividers are counting up to their programmed values.

Therefore, the new A word will be correctly loaded provided that the STROBE signal has been at an active high value for at least a minimum number of VCO input cycles at  $RF_{IN}$  or  $\overline{RF_{IN}}$ .

For PR = '01'

$$t\_strobe\_min = \frac{1}{f_{VCO}}(NM2 \cdot 65) + t_W$$

For PR = '10'

$$t\_strobe\_min = \frac{1}{f_{VCO}}[NM2 \cdot 65 + (NM3 + 1) \cdot 68] + t_W$$

For PR = '11'

$$t\_strobe\_min = \frac{1}{f_{VCO}} \cdot [(NM2 \cdot 65 + (NM3 + 1) \cdot 73)] + t_W$$

For PR = '00'

$$t\_strobe\_min = \frac{1}{f_{VCO}} \cdot [(NM2 \cdot 65) + (NM4 + 1) \cdot 73] + t_W$$

Programming the A word means also that the main charge pumps on output PHP and PHI are set into the speed-up mode as long as the STROBE is H.

#### **Auxiliary Divider**

The input signal on AUX\_IN is amplified to logic level by a single-ended CMOS input buffer, which accepts low level AC coupled input signals. This input stage is enabled if the serial control bit EA = "1". Disabling means that all currents in the input stage are switched off. A fixed divide by 4 is enabled if PA = "0". This divider has been optimized to accept a high frequency input signal. If PA = "1", this divider is disabled and the input signal is fed directly to the second stage, which is a 12-bit programmable divider with standard input frequency (40MHz). The division ratio can be expressed as:

### 1.8GHz low-voltage Fractional-N synthesizer

SA8025A

if PA = "1": N = NA; with NA = 4 to 4095

#### Reference Divider

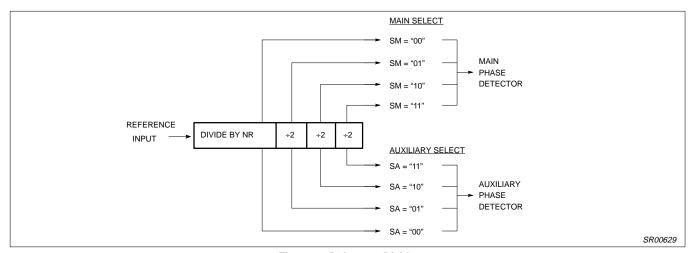

The input signal on REF\_IN is amplified to logic level by a single-ended CMOS input buffer, which accepts low level AC coupled input signals. This input stage is enabled by the OR function of the serial input bits EA and EM. Disabling means that all currents in the input stage are switched off. The reference divider consists of a programmable divider by NR (NR = 4 to 4095) followed by a three bit binary counter. The 2 bit SM register (see Figure 7) determines which of the 4 output pulses is selected as the main phase detector input. The 2 bit SA register determines the selection of the auxiliary phase detector signal.

#### Main Divider

The differential inputs are amplified (to internal ECL logic levels) and provide excellent sensitivity (–20dBm at 1.7GHz) making the prescaler ideally suited to directly interface to a VCO as integrated on the Philips front-end devices including RF gain stage, VCO and mixer. The internal four modulus prescaler feedback loop FB controls the selection of the divide by ratios 64/65/68/73, and reduces the minimum system division ratio below the typical value required by standard dual modulus (64/65) devices.

This input stage is enabled when serial control bit EM = "1". Disabling means that all currents in the prescaler are switched off.

The main divider is built up by a 12 bit counter plus a sign bit. Depending on the serial input values NM1, NM2, NM3, NM4 and the

prescaler select PR, the counter will select a prescaler ratio during a number of input cycles according to Table 2 and Table 3.

The loading of the work registers NM1, NM2, NM3, NM4 and PR is synchronized with the state of the main counter, to avoid extra phase disturbance when switching over to another main divider ratio as explained in the Serial Input Programming section.

At the completion of a main divider cycle, a main divider output pulse is generated which will drive the main phase comparator. Also, the fractional accumulator is incremented with NF. The accumulator works modulo Q. Q is preset by the serial control bit FMOD to 8 when FMOD = "1". Each time the accumulator overflows, the feedback to the prescaler will select one cycle using prescaler ratio R2 instead of R1.

As shown above, this will increase the overall division ratio by 1 if R2=R1+1. The mean division ratio over Q main divider will then be

$$NQ = N + \frac{NF}{Q}$$

Programming a fraction means the prescaler with main divider will divide by N or N + 1. The output of the main divider will be modulated with a fractional phase ripple. This phase ripple is proportional to the contents of the fractional accumulator FRD, which is used for fractional current compensation.

# 1.8GHz low-voltage Fractional-N synthesizer

### SA8025A

Figure 6. Serial Input Word Format

Figure 7. Reference Divider

# 1.8GHz low-voltage Fractional-N synthesizer

SA8025A

**Table 1. Function Table**

| Symbol | Bits                             | Function                                                                                                                                                                                      |

|--------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NM1    | 12                               | Number of main divider cycles when prescaler modulus = 64*                                                                                                                                    |

| NM2    | 8 if PR = "01"<br>4 if PR = "10" | Number of main divider cycles when prescaler modulus = 65*                                                                                                                                    |

| NM3    | 4 if PR = "10"                   | Number of main divider cycles when prescaler modulus = 68*                                                                                                                                    |

| NM4    | 4 if PR = "11" or<br>"00"        | Number of main divider cycles when prescaler modulus = 73*                                                                                                                                    |

| PR     | 2                                | Prescaler type in use PR = "01": modulus 2 prescaler (64/65) PR = "10": modulus 3 prescaler (64/65/68) PR = "11": modulus 4 prescaler (64/65/68/73) PR = "00": modulus 3 prescaler (64/65/73) |

| NF     | 3                                | Fractional-N increment                                                                                                                                                                        |

| FMOD   | 1                                | Fractional-N modulus selection flag "1": modulo 8 "0": modulo 5                                                                                                                               |

| LONG   | 1                                | A word format selection flag "0": 24 bit A0 format "1": 32 bit A1 format                                                                                                                      |

| CN     | 8                                | Binary current setting factor for main charge pumps                                                                                                                                           |

| CL     | 2                                | Binary acceleration factor for proportional charge pump current                                                                                                                               |

| CK     | 4                                | Binary acceleration factor for integral charge pump current                                                                                                                                   |

| EM     | 1                                | Main divider enable flag                                                                                                                                                                      |

| EA     | 1                                | Auxiliary divider enable flag                                                                                                                                                                 |

| SM     | 2                                | Reference select for main phase detector                                                                                                                                                      |

| SA     | 2                                | Reference select for auxiliary phase detector                                                                                                                                                 |

| NR     | 12                               | Reference divider ratio                                                                                                                                                                       |

| NA     | 12                               | Auxiliary divider ratio                                                                                                                                                                       |

| PA     | 1                                | Auxiliary prescaler mode: PA = "0": divide by 4 PA = "1": divide by 1                                                                                                                         |

#### Table 2. Prescaler Ratio

| The total division ratio f | rom prescaler to the phase detector may be expressed as:                                         |

|----------------------------|--------------------------------------------------------------------------------------------------|

| if PR = "01"               | $N = (NM1 + 2) \times 64 + NM2 \times 65$                                                        |

|                            | $N' = (NM1 + 1) \times 64 + (NM2 + 1) \times 65 (*)$                                             |

| if PR = "10"               | $N = (NM1 + 2) \times 64 + NM2 \times 65 + (NM3 + 1) \times 68$                                  |

|                            | N' = (NM1 + 1) x 64 + (NM2 + 1) x 65 + (NM3 + 1) x 68 (*)                                        |

| if PR = "11"               | $N = (NM1 + 2) \times 64 + NM2 \times 65 + (NM3 + 1) \times 68 + (NM4 + 1) \times 73$            |

|                            | $N' = (NM1 + 1) \times 64 + (NM2 + 1) \times 65 + (NM3 + 1) \times 68 + (NM4 + 1) \times 73$ (*) |

| if PR = "00"               | $N = (NM1 + 2) \times 64 + NM2 \times 65 + (NM4 + 1) \times 73$                                  |

|                            | $N' = (NM1 + 1) \times 64 + (NM2 + 1) \times 65 + (NM4 + 1) \times 73 (*)$                       |

| (*) When the fractional    | accumulator overflows the prescaler ratio = 65 (64 + 1) and the total division ratio N' = N + 1  |

#### Table 3. PR Modulus

| PR | Modulus Prescaler |     | Bit Ca | pacity |     |

|----|-------------------|-----|--------|--------|-----|

| FK | Modulus Prescalei | NM1 | NM2    | NM3    | NM4 |

| 01 | 2                 | 12  | 8      | _      | _   |

| 10 | 3                 | 12  | 4      | 4      | _   |

| 11 | 4                 | 12  | 4      | 4      | 4   |

| 00 | 3                 | 12  | 8      | -      | 4   |

### 1.8GHz low-voltage Fractional-N synthesizer

SA8025A

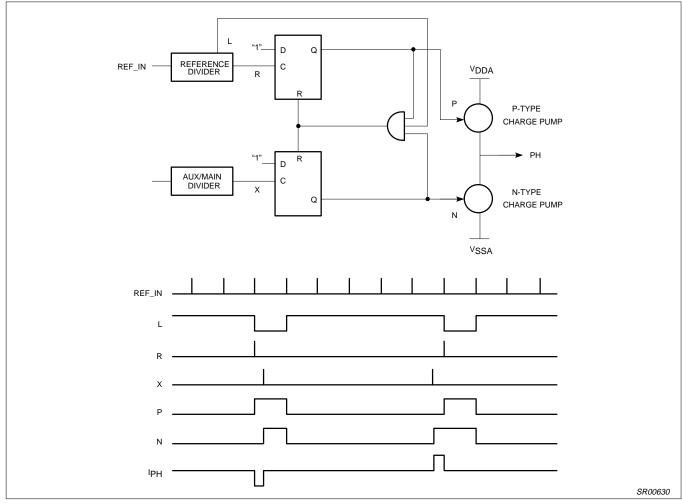

Figure 8. Phase Detector Structure with Timing

#### **Phase Detectors**

The auxiliary and main phase detectors are a two D-type flip-flop phase and frequency detector shown in Figure 8. The flip-flops are set by the negative edges of output signals of the dividers. The rising edge of the signal, L, will reset the flip-flops after both flip-flops have been set. Around zero phase error this has the effect of delaying the reset for 1 reference input cycle. This avoids non-linearity or deadband around zero phase error. The flip-flops drive on-chip charge pumps. A source current from the charge pump indicates the VCO frequency will be increased; a sink current indicates the VCO frequency will be decreased.

#### **Current Settings**

The SA8025A has 3 current setting pins: RA, RN and RF. The active charge pump currents and the fractional compensation currents are linearly dependent on the current connected between the current setting pin and  $V_{SS}$ . The typical value R (current setting resistor) can be calculated with the formula:

$$R = \frac{V_{DDA} - 0.9 - 150}{I_{R}}$$

The current can be set to zero by connecting the corresponding pin to  $V_{\mbox{\scriptsize DDA}}.$

#### **Auxiliary Output Charge Pumps**

The auxiliary charge pumps on pin PHA are driven by the auxiliary phase detector and the current value is determined by the external resistor RA at pin RA. The active charge pump current is typically:

$$|I_{PHA}| = 8 \cdot I_{RA}$$

### 1.8GHz low-voltage Fractional-N synthesizer

### SA8025A

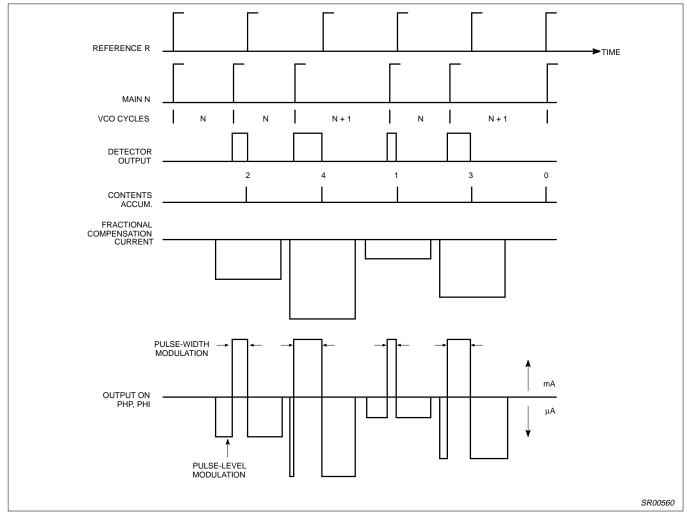

Figure 9. Waveforms for NF = 2, Fraction = 0.4

# Main Output Charge Pumps and Fractional Compensation Currents

The main charge pumps on pin PHP and PHI are driven by the main phase detector and the current value is determined by the current at pin RN and via a number of DACs which are driven by registers of the serial input. The fractional compensation current is determined by the current at pin RF, the contents of the fractional accumulator FRD and a number of DACs driven by registers from the serial input. The timing for the fractional compensation is derived from the reference divider. The current is on during 1 input reference cycle before and 1 cycle after the output signal to the phase comparator. Figure 9 shows the waveforms for a typical case.

When the serial input A word is loaded, the output circuits are in the "speed-up mode" as long as the STROBE is H, else the "normal mode" is active. In the "normal mode" the current output PHP is:

$$I_{PHP_N} = I_{PHP} + I_{PHP_{comp}}$$

where:

$$|I_{PHP}| = \frac{CN \cdot I_{RN}}{32}$$

:charge pump current

$$|I_{PHP\_comp}| = FRD \cdot \frac{I_{RF}}{128}$$

:fractional comp.

The current in PHI is zero in "normal mode".

In "speed-up mode" the current in output PHP is:

$$\mathsf{I}_{\mathsf{PHP\_S}} \ = \ \mathsf{I}_{\mathsf{PHP}} \ + \ \mathsf{I}_{\mathsf{PHP\_comp}}$$

$$|I_{PHP}| = \frac{CN \cdot I_{RN}}{32} (2^{CL+1} + 1)$$

$$|I_{PHP\_comp}| = \frac{FRD \cdot I_{RF}}{128} (2^{CL+1} + 1)$$

In "speed-up mode" the current in output PHI is:

$$I_{PHI S} = I_{PHI} + I_{PHI comp}$$

where

$$|I_{PHI}| = \frac{CN \cdot I_{RN}}{32} (2^{CL+1}) CK$$

### 1.8GHz low-voltage Fractional-N synthesizer

SA8025A

$$|I_{PHI\_comp}| = \frac{FRD \cdot I_{RN}}{128} (2^{CL+1}) CK$$

Figure 9 shows that for proper fractional compensation, the area of the fractional compensation current pulse must be equal to the area of the charge pump ripple output. This means that the current setting on the input RN, RF is approximately:

$$\frac{{\rm I}_{\rm RN}}{{\rm I}_{\rm RF}} \qquad \frac{({\rm Q}\,\cdot\,{\rm f}_{\rm VCO})}{(3\,\cdot\,{\rm CN}\,\cdot\,{\rm F}_{\rm INR})}$$

where:

$\begin{array}{ll} Q & = & \text{fractional-N modulus} \\ f_{VCO} = f_{INM} \times N, & \text{input frequency of the prescaler} \\ F_{INR} = & \text{input frequency of the reference divider} \end{array}$

PHI pump is meant for switching only. Current and compensation are not as accurate as PHP.

#### **Lock Detect**

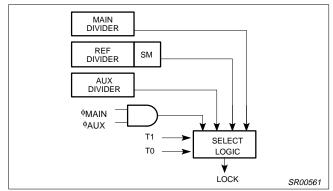

The output LOCK is H when the auxiliary phase detector AND the main phase detector indicates a lock condition. The lock condition is defined as a phase difference of less than +1 cycle on the reference input REF\_IN. The lock condition is also fulfilled when the relative counter is disabled (EM = "0" or respectively EA = "0") for the main, respectively auxiliary counter.

#### **Test Modes**

The lock output is selectable as  $f_{REF}$ ,  $f_{AUX}$ ,  $f_{MAIN}$  and lock. Bits T1 and T0 of the E word control the selection (see Figures 6 and 10).

If T1 = T0 = Low, or if the E-word is not sent, the lock output is configured as the normal lock output described in the Lock Detect section.

If T1 = Low and T0 = High, the lock output is configured as  $f_{REF}$ . The signal is the buffered output of the reference divider NR and the 3-bit binary counter SM. The  $f_{REF}$  signal appears as normally low and pulses high whenever the divider reaches terminal count from the value programmed into the NR and SM registers. The  $f_{REF}$  signal can be used to verify the divide ratio of the Reference divider.

If T1 = High and T0 = Low, the lock output is configured as  $f_{AUX}$ . The signal is normally high and pulses low whenever the divider reaches terminal count from the value programmed into the NA and PA registers. The  $f_{AUX}$  signal can be used to verify the divide ratio of the Auxiliary divider.

If T1 = High and T0 = High, the lock output is configured as  $f_{MAIN}$ . The signal is the buffered output of the MAIN divider. The  $f_{MAIN}$  signal appears as normally high and pulses low whenever the divider reaches terminal count from the value programmed into the NM1, NM2, NM3 or NM4 registers. The  $f_{MAIN}$  signal can be used to verify the divide ratio of the MAIN divider and the prescaler.

#### **Test Pin**

The Test pin, Pin 19, is a buffered logic input which is exclusively ORed with the output of the prescaler. The output of the XOR gate is the input to the MAIN divider. The Test pin must be connected to  $V_{DD}$  during normal operation as a synthesizer. This pin can be used as an input for verifying the divide ratio of the MAIN divider; while in this condition the input to the prescaler,  $RF_{IN}$ , may be connected to  $V_{CCP}$  through a  $10k\Omega$  resistor in order to place prescaler output into a known state.

Figure 10. Test Mode Diagram

# 1.8GHz low-voltage Fractional-N synthesizer

SA8025A

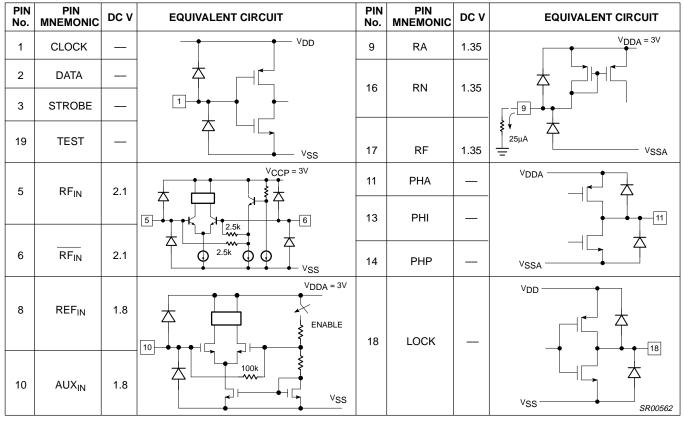

#### **PIN FUNCTIONS**

Figure 11. Pin Functions

# 1.8GHz low-voltage Fractional-N synthesizer

SA8025A

#### TYPICAL PERFORMANCE CHARACTERISTICS

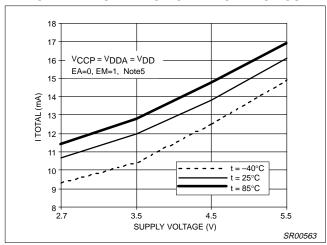

Figure 12. Operational Supply Current vs Supply Voltage and Temperature

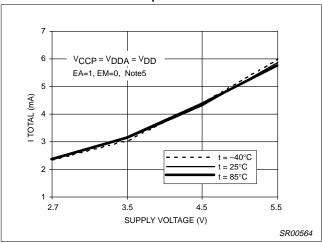

Figure 13. Auxiliary Operational Supply Current vs Supply Voltage and Temperature

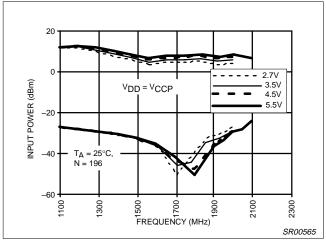

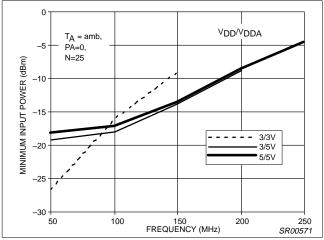

Figure 14. Main Divider Input Power vs Frequency and Supply

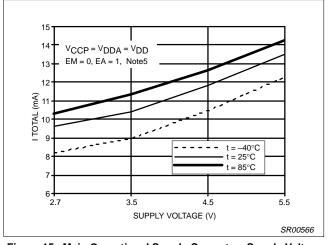

Figure 15. Main Operational Supply Current vs Supply Voltage and Temperature

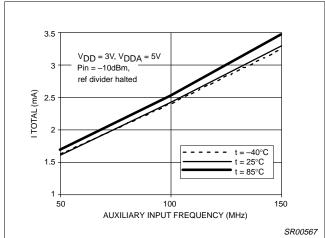

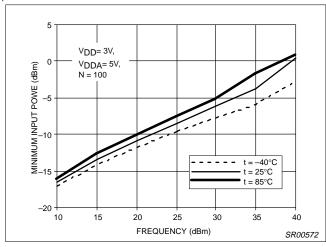

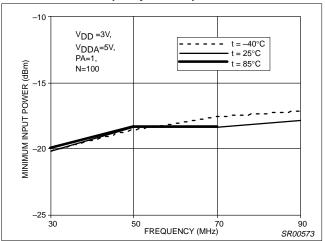

Figure 16. Auxiliary Operational Supply Current vs Frequency and Temperature

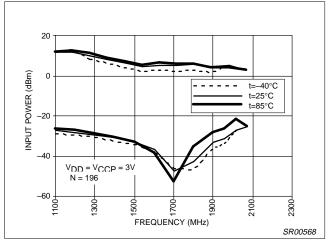

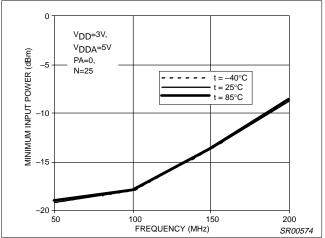

Figure 17. Main Divider Input Power vs Frequency and Temperature

# 1.8GHz low-voltage Fractional-N synthesizer

SA8025A

#### TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

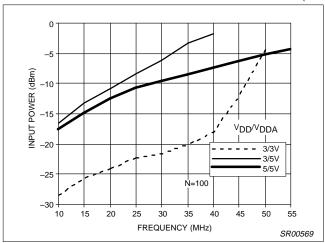

Figure 18. Reference Divider Minimum Input Power vs Frequency and Supply

Figure 19. Auxiliary Divider Minimum Input Power vs Frequency and Supply

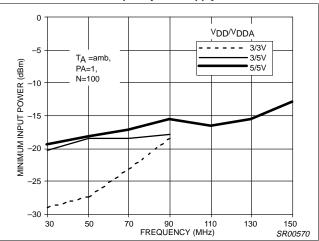

Figure 20. Auxiliary Divider Minimum Input Power vs Frequency and Supply

Figure 21. Reference Divider Minimum Input Power vs Frequency and Temperature

Figure 22. Auxiliary Divider Minimum Input Power vs Frequency and Temperature

Figure 23. Auxiliary Divider Minumum Input Power vs Frequency and Temperature

# 1.8GHz low-voltage Fractional-N synthesizer

# SA8025A

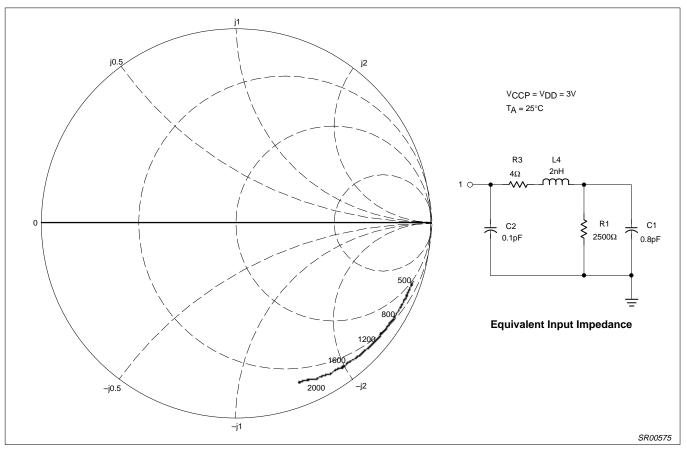

Figure 24. Typical  $RF_{IN}$  Input Impedance

Product specification Philips Semiconductors

# 1.8GHz low-voltage Fractional-N synthesizer

SA8025A

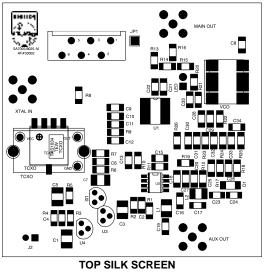

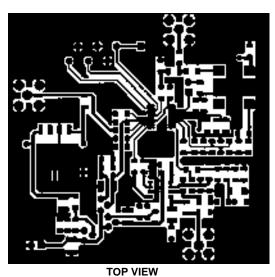

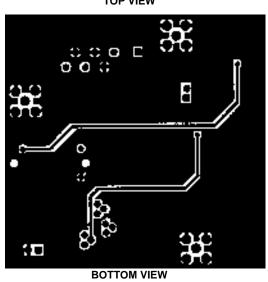

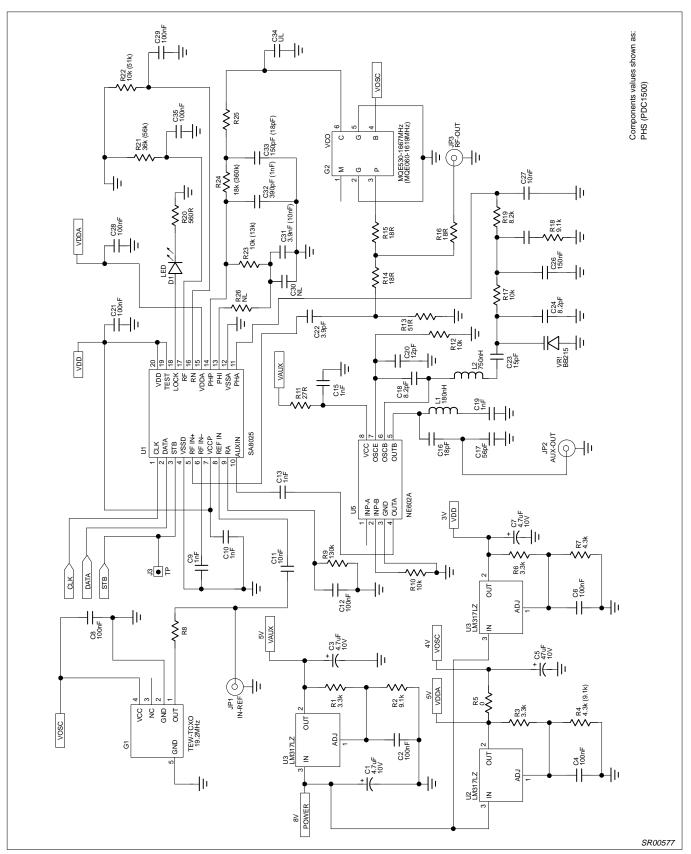

Figure 25. SA8025ADK Demoboard Layout (NOT ACTUAL SIZE)

1996 Oct 15 20 SR00576

# 1.8GHz low-voltage Fractional-N synthesizer

# SA8025A

Figure 26. SA8025ADK Application Circuit

# 1.8GHz low-voltage Fractional-N synthesizer

### **SA8025A**

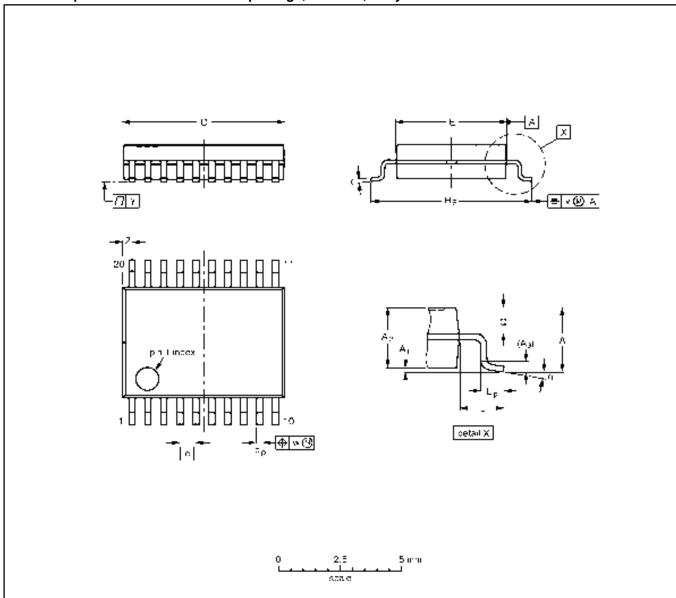

#### SSOP20: plastic shrink small outline package; 20 leads; body width 4.4 mm

SOT266-1

#### DIMENSIONS (mm are the or-ginal dimensions)

| UNIT   | A<br>max. | Aı  | A2         | Аз   | Ьp           | Б            | 011)       | E <sup>(1)</sup> | •    | HE         | L  | Lp           | a            | ν  | <b>"</b> | у  | Z <sup>[1]</sup> |          |

|--------|-----------|-----|------------|------|--------------|--------------|------------|------------------|------|------------|----|--------------|--------------|----|----------|----|------------------|----------|

| ורוורו | 15        | 5 G | 1.4<br>1.2 | 0.25 | 0.32<br>0.25 | 0.20<br>0.13 | 6.6<br>6.4 | 4.3<br>4.3       | 0.65 | 5.5<br>5.2 | 10 | C 75<br>C.45 | 0.68<br>0.48 | cs | û.10     | 0. | 0.48<br>0.18     | 5<br>III |

#### Note

1. Plastic or metal profiusions of 0.25 mm maximum per side are not included

| • | OUTLINE  |     | REFER | ENCES | EUROPEAN   | MEEUE DATE                        |

|---|----------|-----|-------|-------|------------|-----------------------------------|

|   | VERSION  | IEC | JEDEC | EIAJ  | PROJECTION | 155UE DATE                        |

|   | 90T265 T |     |       |       | . €∃�      | <del>-93-04-05-</del><br>95-02-25 |

### 1.8GHz low-voltage Fractional-N synthesizer

**SA8025A**

| DEFINITIONS               |                        |                                                                                                                                                                                                                                                            |

|---------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Sheet Identification | Product Status         | Definition                                                                                                                                                                                                                                                 |

| Objective Specification   | Formative or in Design | This data sheet contains the design target or goal specifications for product development. Specifications may change in any manner without notice.                                                                                                         |

| Preliminary Specification | Preproduction Product  | This data sheet contains preliminary data, and supplementary data will be published at a later date. Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. |

| Product Specification     | Full Production        | This data sheet contains Final Specifications. Philips Semiconductors reserves the right to make changes at any time without notice, in order to improve design and supply the best possible product.                                                      |

Philips Semiconductors and Philips Electronics North America Corporation reserve the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified. Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### LIFE SUPPORT APPLICATIONS

Philips Semiconductors and Philips Electronics North America Corporation Products are not designed for use in life support appliances, devices, or systems where malfunction of a Philips Semiconductors and Philips Electronics North America Corporation Product can reasonably be expected to result in a personal injury. Philips Semiconductors and Philips Electronics North America Corporation customers using or selling Philips Semiconductors and Philips Electronics North America Corporation Products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors and Philips Electronics North America Corporation for any damages resulting from such improper use or sale.

Philips Semiconductors 811 East Arques Avenue P.O. Box 3409 Sunnyvale, California 94088–3409 Telephone 800-234-7381 Philips Semiconductors and Philips Electronics North America Corporation register eligible circuits under the Semiconductor Chip Protection Act.

© Copyright Philips Electronics North America Corporation 1996

All rights reserved. Printed in U.S.A.

Let's make things better.