# 256Kx18 Flow-Through SRAM with NoBL™ Architecture

### **Features**

- Pin compatible and functionally equivalent to ZBT™ devices MCM63Z819 and MT55L256L18F

- Supports 66-MHz bus operations with zero wait states

Data is transferred on every clock

- Internally self-timed output buffer control to eliminate the need to use OE

- · Registered inputs for Flow-Through operation

- Byte Write capability

- 256K x 18 common I/O architecture

- Single 3.3V power supply

- · Fast clock-to-output times

- 11.0 ns (for 66-MHz device)

- -12.0 ns (for 50-MHz device)

- -14.0 ns (for 40-MHz device)

- Clock Enable (CEN) pin to suspend operation

- · Synchronous self-timed writes

- Asynchronous Output Enable

- JEDEC-standard 100 TQFP package

- Burst Capability—linear or interleaved burst order

- Low standby power

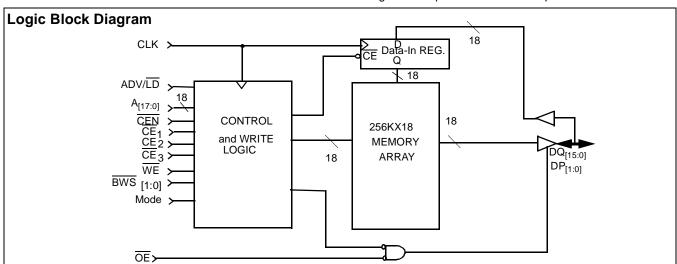

## **Functional Description**

The CY7C1353 is a 3.3V 256K by 18 Synchronous-Flow-Through Burst SRAM designed specifically to support unlimited true back-to-back Read/Write operations without the insertion of wait states. The CY7C1353 is equipped with the advanced No Bus Latency (NoBL™) logic required to enable consecutive Read/Write operations with data being transferred on every clock cycle. This feature dramatically improves the throughput of data through the SRAM, especially in systems that require frequent Write-Read transitions.The CY7C1353 is pin/functionally compatible to ZBT™ SRAMs MCM63Z819 and MT55L256L18F.

All synchronous inputs pass through input registers controlled by the rising edge of the clock. The clock input is qualified by the Clock Enable (CEN) signal, which when deasserted suspends operation and extends the previous clock cycle. Maximum access delay from the clock rise is 9.0 ns (66-MHz device).

<u>Write</u> operations are controlled <u>by</u> the four Byte Write Select  $(\overline{BWS}_{[1:0]})$  and a Write Enable  $(\overline{WE})$  input. All writes are conducted with on-chip synchronous self-timed write circuitry.

Three synchronous Chip Enables  $(\overline{CE}_1, CE_2, \overline{CE}_3)$  and an asynchronous Output Enable  $(\overline{OE})$  provide for easy bank selection and output three-state control. In order to avoid bus contention, the output drivers are synchronously three-stated during the data portion of a write sequence.

### Selection Guide

|                                   |            | 7C1353-66 | 7C1353-50 | 7C1353-40 |

|-----------------------------------|------------|-----------|-----------|-----------|

| Maximum Access Time (ns)          |            | 11        | 12.0      | 14.0      |

| Maximum Operating Current (mA)    | Commercial | 250 mA    | 200 mA    | 175 mA    |

| Maximum CMOS Standby Current (mA) | Commercial | 5 mA      | 5 mA      | 5 mA      |

NoBL is a trademark of Cypress Semiconductor Corporation. ZBT is a trademark of Integrated Device Technology.

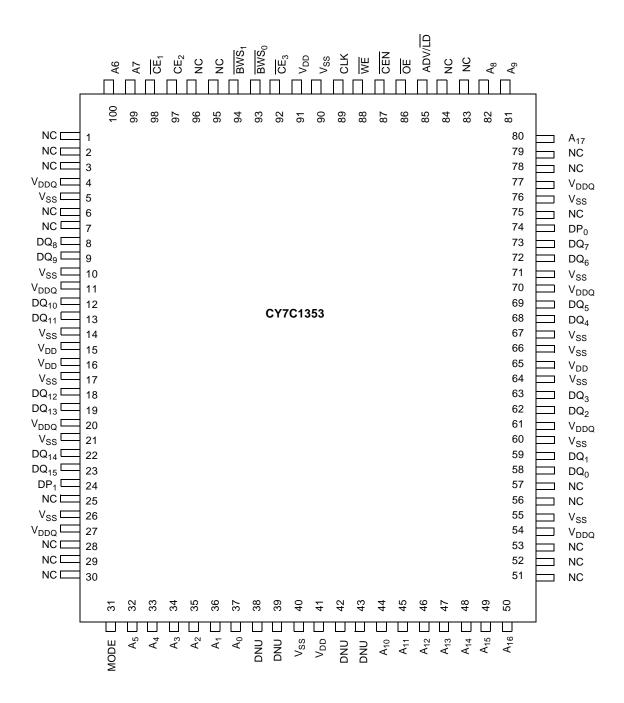

# **Pin Configuration**

## 100-Pin TQFP

# **Pin Definitions**

| Pin Number                                                           | Name                 | I/O                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------|----------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 80, 50–44,<br>81–82, 99–<br>100, 32–37                               | A <sub>[17:0]</sub>  | Input-<br>Synchronous  | Address Inputs used to select one of the 262,144 address locations. Sampled at the rising edge of the CLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 94, 93                                                               | BWS <sub>[1:0]</sub> | Input-<br>Synchronous  | Byte Write Select Inputs, active LOW. Qualified with $\overline{\text{WE}}$ to conduct writes to the SRAM. Sampled on the rising edge of CLK. BWS $_0$ controls DQ $_{[7:0]}$ and DP $_0$ , BWS $_1$ controls DQ $_{[15:8]}$ and DP $_1$ . See Write Cycle Description Table for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 88                                                                   | WE                   | Input-<br>Synchronous  | Write Enable Input, active LOW. Sampled on the rising edge of CLK if CEN is active LOW. This signal must be asserted LOW to initiate a write sequence.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 85                                                                   | ADV/LD               | Input-<br>Synchronous  | Advance/Load Input used to advance the on-chip address counter or load a new address. When HIGH (and CEN is asserted LOW) the internal burst counter is advanced. When LOW, a new address can be loaded into the device for an access. After being deselected, ADV/LD should be driven LOW in order to load a new address.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 89                                                                   | CLK                  | Input-Clock            | Clock Input. Used to capture all synchronous inputs to the device. CLK is qualified with CEN. CLK is only recognized if CEN is active LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 98                                                                   | Œ <sub>1</sub>       | Input-<br>Synchronous  | Chip Enable 1 Input, active LOW. Sampled on the rising edge of CLK. Used in conjunction with CE <sub>2</sub> , and CE <sub>3</sub> to select/deselect the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 97                                                                   | CE <sub>2</sub>      | Input-<br>Synchronous  | Chip Enable 2 Input, active HIGH. Sampled on the rising edge of CLK. Used in conjunction with CE <sub>1</sub> and CE <sub>3</sub> to select/deselect the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 92                                                                   | CE <sub>3</sub>      | Input-<br>Synchronous  | Chip Enable 3 Input, active LOW. Sampled on the rising edge of CLK. Used in conjunction with CE and CE <sub>2</sub> to select/deselect the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 86                                                                   | ŌĒ                   | Input-<br>Asynchronous | Output Enable, active LOW. Combined with the synchronous logic block inside the device to control the direction of the I/O pins. When LOW, the I/O pins are allowed to behave as outputs. When deasserted HIGH, I/O pins are three-stated, and act as input data pins. $\overline{OE}$ is masked during the data portion of a write sequence, during the first clock when emerging from a deselected state, when the device has been deselected.                                                                                                                                                                                                                                                                                                    |

| 87                                                                   | CEN                  | Input-<br>Synchronous  | Clock Enable Input, active LOW. When asserted LOW the Clock signal is recognized by the <u>SRAM</u> . When deasserted HIGH the <u>Clock</u> signal is masked. Since deasserting <u>CEN</u> does not deselect the device, <u>CEN</u> can be used to extend the previous cycle when required.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 23–22,<br>19–18,<br>13–12, 9–8,<br>73–72,<br>69–68,<br>63–62, 59–58  | DQ <sub>[15:0]</sub> | I/O-<br>Synchronous    | Bidirectional Data I/O Lines. As inputs, they feed into an on-chip data register that is triggered by the rising edge of CLK. As outputs, they deliver the data contained in the memory location specified by $A_{[17:0]}$ during the previous clock rise of the read cycle. The direction of the pins is controlled by $\overline{OE}$ and the internal control logic. When $\overline{OE}$ is asserted LOW, the pins can behave as outputs. When HIGH, $DQ_{[15:0]}$ are placed in a three-state condition. The outputs are automatically three-stated during the data portion of a write sequence, during the first clock when emerging from a deselected state, and when the device is deselected, regardless of the state of $\overline{OE}$ . |

| 24, 74                                                               | DP <sub>[1:0]</sub>  | I/O-<br>Synchronous    | Bidirectional Data Parity I/O Lines. Functionally, these signals are identical to DQ <sub>[15:0]</sub> . During write sequences, DP <sub>0</sub> is controlled by BWS <sub>0</sub> and DP <sub>1</sub> is controlled by BWS <sub>1</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 31                                                                   | Mode                 | Input<br>Strap pin     | Mode Input. Selects the burst order of the device. Tied HIGH selects the interleaved burst order. Pulled LOW selects the linear burst order. MODE should not change states during operation. When left floating MODE will default HIGH, to an interleaved burst order.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 15, 16, 41, 65,<br>91                                                | V <sub>DD</sub>      | Power Supply           | Power supply inputs to the core of the device. Should be connected to 3.3V power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4, 11, 20, 27,<br>54, 61, 70, 77                                     | $V_{DDQ}$            | I/O Power<br>Supply    | Power supply for the I/O circuitry. Should be connected to a 3.3V power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5, 10, 14, 17,<br>21, 26, 40, 55,<br>60, 64,<br>66–67, 71,<br>76, 90 | V <sub>SS</sub>      | Ground                 | Ground for the device. Should be connected to ground of the system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

### Pin Definitions (continued)

| Pin Number                                                  | Name | I/O | Description                                                                                                                              |

|-------------------------------------------------------------|------|-----|------------------------------------------------------------------------------------------------------------------------------------------|

| 1–3, 6–7, 25,<br>28–30,51–53,<br>56–57, 75,<br>78–79, 95–96 | NC   | -   | No Connects. These pins are not connected to the internal device.                                                                        |

| 83, 84                                                      | NC   | -   | No Connects. Reserved for address inputs for depth expansion. Pin 83 will be used for 512K depth and pin 84 will be used for 1-Mb depth. |

| 38, 39, 42, 43                                              | DNU  | -   | Do Not Use Pins. These pins should be left floating or tied to V <sub>SS</sub> .                                                         |

### Introduction

### **Functional Overview**

The CY7C1353 is a Synchronous Flow-Through Burst SRAM designed specifically to eliminate wait states during Write-Read transitions. All synchronous inputs pass through input registers controlled by the rising edge of the clock. The clock signal is qualified with the Clock Enable input signal (CEN). If CEN is HIGH, the clock signal is not recognized and all internal states are maintained. All synchronous operations are qualified with CEN. Maximum access delay from the clock rise (t<sub>CDV</sub>) is 9.0 ns (66-MHz device).

Accesses can be initiated by asserting all three Chip Enables (CE<sub>1</sub>, CE<sub>2</sub>, CE<sub>3</sub>) active at the rising edge of the clock. If clock enable (CEN) is active LOW and ADV/LD is asserted LOW, the address presented to the device will be latched. The access can either be a read or write operation, depending on the status of the Write Enable (WE). BWS<sub>[1:0]</sub> can be used to conduct byte write operations.

Write operations are qualified by the Write Enable ( $\overline{WE}$ ). All writes are simplified with on-chip synchronous self-timed write circuitry.

Three synchronous Chip Enables ( $\overline{CE}_1$ ,  $\overline{CE}_2$ ,  $\overline{CE}_3$ ) and an asynchronous Output Enable ( $\overline{OE}$ ) simplify depth expansion. All operations (Reads, Writes, and Deselects) are pipelined. ADV/ $\overline{LD}$  should be driven LOW once the device has been deselected in order to load a new address for the next operation.

### Single Read Accesses

A read access is initiated when the following conditions are satisfied at clock rise: (1) CEN is asserted LOW, (2) CE<sub>1</sub>, CE<sub>2</sub>, and  $\overline{\text{CE}_3}$  are ALL asserted active, (3) the Write Enable input signal WE is deasserted HIGH, and 4) ADV/LD is asserted LOW. The address presented to the address inputs (A<sub>[17:0]</sub>) is latched into the Address Register and presented to the memory core and control logic. The control logic determines that a read access is in progress and allows the requested data to propagate to the output buffers. The data is available within 9.0 ns (66-MHz device) provided OE is active LOW. After the first clock of the read access the output buffers are controlled by OE and the internal control logic. OE must be driven LOW in order for the device to drive out the requested data. On the subsequent clock, another operation (Read/Write/Deselect) can be initiated. When the SRAM is deselected at clock rise by one of the chip enable signals, its output will be three-stated immediately.

### Burst Read Accesses

The CY7C1353 has an on-chip burst counter that allows the user the ability to supply a single address and conduct up to four Reads without reasserting the address inputs. ADV/LD

must be driven LOW in order to load a new address into the SRAM, as described in the Single Read Access section above. The sequence of the burst counter is determined by the MODE input signal. A LOW input on MODE selects a linear burst mode, a HIGH selects an interleaved burst sequence. Both burst counters use A0 and A1 in the burst sequence, and will wrap around when incremented sufficiently. A HIGH input on ADV/LD will increment the internal burst counter regardless of the state of chip enable inputs or WE. WE is latched at the beginning of a burst cycle. Therefore, the type of access (Read or Write) is maintained throughout the burst sequence.

### Single Write Accesses

Write access are initiated when the following conditions are satisfied at clock rise: (1) CEN is asserted LOW, (2) CE<sub>1</sub>, CE<sub>2</sub>, and CE<sub>3</sub> are ALL asserted active, and (3) the write signal WE is asserted LOW. The address presented to  $A_{[17:0]}$  is loaded into the Address Register. The write signals are latched into the Control Logic block. The data lines are automatically three-stated regardless of the state of the OE input signal. This allows the external logic to present the data on DQ<sub>[15:0]</sub> and DP<sub>[1:0]</sub>.

On the next clock rise the data presented to  $DQ_{[15:0]}$  and  $DP_{[1:0]}$  (or a subset for byte write operations, see Write Cycle Description table for details) inputs is latched into the device and the write is complete. Additional accesses (Read/Write/Deselect) can be initiated on this cycle.

The data written during the Write operation is controlled by  $\overline{BWS}_{[1:0]}$  signals. The CY7C1353 provides byte write capability that is described in the Write Cycle Description Table. Asserting the Write Enable input (WE) with the selected Byte Write Select  $(\overline{BWS}_{[1:0]})$  input will selectively write to only the desired bytes. Bytes not selected during a byte write operation will remain unaltered. A synchronous self-timed write mechanism has been provided to simplify the write operations. Byte write capability has been included in order to greatly simplify Read/Modify/Write sequences, which can be reduced to simple byte write operations.

Because the CY7C1353 is a common I/O device, data should not be driven into the device while the outputs are active. The Output Enable ( $\overline{\text{OE}}$ ) can be deasserted HIGH before presenting data to the  $DQ_{[15:0]}$  and  $DP_{[1:0]}$  inputs. Doing so will three-state the output drivers. As a safety precaution,  $DQ_{[15:0]}$  and  $DP_{[1:0]}$  are automatically three-stated during the data portion of a write cycle, regardless of the state of  $\overline{\text{OE}}$ .

### Burst Write Accesses

The CY7C1353 has an On-Chip Burst Counter that allows the user the ability to supply a single address and conduct up to four <u>Wri</u>te operations without reasserting the address inputs. ADV/LD must be driven LOW in order to load the initial ad-

dress, as described in the Single Write Access section above. When ADV/LD is driven HIGH on the subsequent clock rise, the chip enables ( $\overline{CE_1}$ ,  $\overline{CE_2}$ , and  $\overline{CE_3}$ ) and  $\overline{WE}$  inputs are ignored and the burst counter is incremented. The correct  $\overline{BWS}_{[1:0]}$  inputs must be driven in each cycle of the burst write in order to write the correct bytes of data.

# Cycle Description Truth Table<sup>[1, 2, 3, 4, 5, 6]</sup>

| Operation                | Address<br>used | CE | CEN | ADV/<br>LD | WE | BWS <sub>x</sub> | CLK | Comments                                                                                                                                                                         |

|--------------------------|-----------------|----|-----|------------|----|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Deselected               | External        | 1  | 0   | L          | Х  | Х                | L-H | I/Os three-state following next recognized clock.                                                                                                                                |

| Suspend                  | -               | Х  | 1   | Х          | Х  | Х                | L-H | Clock Ignored, all operations suspended.                                                                                                                                         |

| Begin Read               | External        | 0  | 0   | 0          | 1  | Х                | L-H | Address Latched.                                                                                                                                                                 |

| Begin Write              | External        | 0  | 0   | 0          | 0  | Valid            | L-H | Address Latched, data presented two valid clocks later.                                                                                                                          |

| Burst READ<br>Operation  | Internal        | Х  | 0   | 1          | Х  | Х                | L-H | Burst Read Operation. Previous access was a Read operation. Addresses incremented internally in conjunction with the state of Mode.                                              |

| Burst WRITE<br>Operation | Internal        | Х  | 0   | 1          | Х  | Valid            | L-H | Burst Write Operation. Previous access was a Write operation. Addresses incremented internally in conjunction with the state of Mode.  Bytes written are determined by BWS[1:0]. |

### Note:

- X=Don't Care, 1=Logic HIGH, 0=Logic LOW,  $\overline{\text{CE}}$  stands for ALL Chip Enables active.  $\overline{\text{BWS}}_{\chi}$  = 0 signifies at least one Byte Write Select is active,  $\overline{\text{BWS}}_{\chi}$  = Valid signifies that the desired byte write selects are asserted, see Write Cycle Description table for details. Write is defined by WE and BWS<sub>[1:0]</sub>. See Write Cycle Description table for details. The DQ and DP pins are controlled by the current cycle and the  $\overline{\text{OE}}$  signal. CEN=1 inserts wait states.

Device will power-up deselected and the I/Os in a three-state condition, regardless of  $\overline{\text{OE}}$ . OE assumed LOW.

# **Interleaved Burst Sequence**

| First<br>Address | Second<br>Address | Third<br>Address | Fourth<br>Address |

|------------------|-------------------|------------------|-------------------|

| Ax+1, Ax         | Ax+1, Ax          | Ax+1, Ax         | Ax+1, Ax          |

| 00               | 01                | 10               | 11                |

| 01               | 00                | 11               | 10                |

| 10               | 11                | 00               | 01                |

| 11               | 10                | 01               | 00                |

# **Linear Burst Sequence**

| First<br>Address | Second<br>Address | Third<br>Address | Fourth<br>Address |

|------------------|-------------------|------------------|-------------------|

| Ax+1, Ax         | Ax+1, Ax          | Ax+1, Ax         | Ax+1, Ax          |

| 00               | 01                | 10               | 11                |

| 01               | 10                | 11               | 00                |

| 10               | 11                | 00               | 01                |

| 11               | 00                | 01               | 10                |

# Write Cycle Description[1, 2]

| Function                                                 | WE | BWS <sub>1</sub> | BWS <sub>0</sub> |

|----------------------------------------------------------|----|------------------|------------------|

| Read                                                     | 1  | X                | Х                |

| Write - No bytes written                                 | 0  | 1                | 1                |

| Write Byte 0-(DQ <sub>[7:0]</sub> and DP <sub>0</sub> )  | 0  | 1                | 0                |

| Write Byte 1-(DQ <sub>[15:8]</sub> and DP <sub>1</sub> ) | 0  | 0                | 1                |

| Write All Bytes                                          | 0  | 0                | 0                |

# **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.)

Storage Temperature .....-65°C to +150°C

Ambient Temperature with

Power Applied .......55°C to +125°C

Supply Voltage on  $V_{\mbox{\scriptsize DD}}$  Relative to GND ......  $-0.5\mbox{\scriptsize V}$  to  $+4.6\mbox{\scriptsize V}$

DC Input Voltage<sup>[7]</sup>.....-0.5V to V<sub>DDQ</sub> + 0.5V

- 7. Minimum voltage equals -2.0V for pulse duration less than 20 ns.

- T<sub>A</sub> is the case temperature.

| Current into Outputs (LOW)                             | 20 mA   |

|--------------------------------------------------------|---------|

| Static Discharge Voltage(per MIL-STD-883, Method 3015) | >2001V  |

| (per MIL-31D-003, Method 3013)                         |         |

| Latch-Up Current                                       | >200 mA |

# **Operating Range**

| Range | Ambient<br>Temperature <sup>[8]</sup> | V <sub>DD</sub> /V <sub>DDQ</sub> |

|-------|---------------------------------------|-----------------------------------|

| Com'l | 0°C to +70°C                          | 3.3V ±5%                          |

# **Electrical Characteristics** Over the Operating Range

| Parameter        | Description                                       | Test Condition                                                                                    | ons                 | Min.  | Max.                  | Unit |

|------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------|---------------------|-------|-----------------------|------|

| V <sub>DD</sub>  | Power Supply Voltage                              |                                                                                                   |                     | 3.135 | 3.465                 | V    |

| $V_{DDQ}$        | I/O Supply Voltage                                |                                                                                                   |                     | 3.135 | 3.465                 | V    |

| V <sub>OH</sub>  | Output HIGH Voltage                               | $V_{DD} = Min., I_{OH} = -4.0 \text{ mA}^{[9]}$                                                   |                     | 2.4   |                       | V    |

| V <sub>OL</sub>  | Output LOW Voltage                                | V <sub>DD</sub> = Min., I <sub>OL</sub> = 8.0 mA <sup>[9]</sup>                                   |                     |       | 0.4                   | V    |

| V <sub>IH</sub>  | Input HIGH Voltage                                |                                                                                                   |                     | 2.0   | V <sub>DD</sub> +0.3V | V    |

| V <sub>IL</sub>  | Input LOW Voltage <sup>[7]</sup>                  |                                                                                                   |                     | -0.3  | 0.8                   | V    |

| lχ               | Input Load Current                                | $GND \leq V_I \leq V_{DDQ}$                                                                       |                     | -5    | 5                     | mA   |

|                  | Input Current of MODE                             |                                                                                                   |                     | -30   | 30                    | mA   |

| I <sub>OZ</sub>  | Output Leakage<br>Current                         | $GND \le V_I \le V_{DDQ}$ , Output Disable                                                        | d                   | -5    | 5                     | mA   |

| I <sub>CC</sub>  | V <sub>DD</sub> Operating Supply                  | $V_{DD} = Max., I_{OUT} = 0 mA,$                                                                  | 15-ns cycle, 66 MHz |       | 250                   | mA   |

|                  |                                                   | $f = f_{MAX} = 1/t_{CYC}$                                                                         | 20-ns cycle, 50 MHz |       | 200                   | mA   |

|                  |                                                   |                                                                                                   | 25-ns cycle, 40 MHz |       | 175                   | mA   |

| I <sub>SB1</sub> | Automatic CE                                      | Max. V <sub>DD</sub> , Device Deselected,                                                         | 15-ns cycle, 66 MHz |       | 60                    | mA   |

|                  | Power-Down Current-TTL Inputs                     | $V_{IN} \ge V_{IH} \text{ or } V_{IN} \le V_{IL}$<br>$f = f_{MAX} = 1/t_{CYC}$                    | 20-ns cycle, 50 MHz |       | 40                    | mA   |

|                  |                                                   | 117.00                                                                                            | 25-ns cycle, 40 MHz |       | 30                    | mA   |

| I <sub>SB2</sub> | Automatic CE<br>Power-Down<br>Current-CMOS Inputs | Max. $V_{DD}$ , Device Deselected, $V_{IN} \leq 0.3 V$ or $V_{IN} \geq V_{DDQ} - 0.3 V$ , $f = 0$ | All speed grades    |       | 5                     | mA   |

| I <sub>SB3</sub> | Automatic CE                                      | Max. V <sub>DD</sub> , Device Deselected, or                                                      | 15-ns cycle, 66 MHz |       | 50                    | mA   |

|                  | Power-Down Current-CMOS Inputs                    | $V_{IN} \le 0.3V$ or $V_{IN} \ge V_{DDQ} - 0.3V$<br>$f = f_{MAX} = 1/t_{CYC}$                     | 20-ns cycle, 50 MHz |       | 40                    | mA   |

|                  |                                                   | WWW. OIO                                                                                          | 25-ns cycle, 40 MHz |       | 30                    | mA   |

Note:

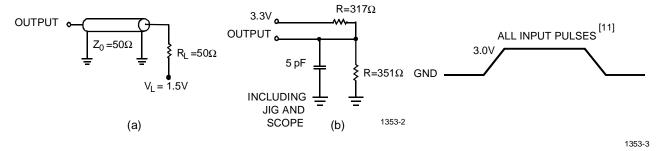

9. The load used for V<sub>OH</sub> and V<sub>OL</sub> testing is shown in figure (b) of the A/C test conditions.

# Capacitance<sup>[10]</sup>

| Parameter        | Description              | Test Conditions                         | Max. | Unit |

|------------------|--------------------------|-----------------------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance        | $T_A = 25^{\circ}C, f = 1 \text{ MHz},$ | 4    | pF   |

| C <sub>CLK</sub> | Clock Input Capacitance  | $V_{DD} = 3.3V$ $V_{DDQ} = 3.3V$        | 4    | pF   |

| C <sub>I/O</sub> | Input/Output Capacitance |                                         | 4    | pF   |

## **AC Test Loads and Waveforms**

## **Thermal Resistance**

| Description                              | Test Conditions                                                            | Symbol            | TQFP Typ. | Units | Notes |

|------------------------------------------|----------------------------------------------------------------------------|-------------------|-----------|-------|-------|

| Thermal Resistance (Junction to Ambient) | Still Air, soldered on a 4.25 x 1.125 inch, 4-layer printed circuit board. | $\Theta_{JA}$     | 28        | °C/W  | 10    |

| Thermal Resistance<br>(Junction to Case) |                                                                            | $\Theta_{\sf JC}$ | 4         | °C/W  | 10    |

### Note:

<sup>10.</sup> Tested initially and after any design or process change that may affect these parameters.

11. Unless otherwise noted, test conditions assume signal transition time of 2 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V, and output loading shown in (a) of AC Test Loads.

# Switching Characteristics Over the Operating Range $^{[11,\ 12,\ 13]}$

|                   |                                                   | -    | -66  |      | -50  |      | -40  |      |

|-------------------|---------------------------------------------------|------|------|------|------|------|------|------|

| Parameter         | Description                                       | Min. | Max. | Min. | Max. | Min. | Max. | Unit |

| t <sub>CYC</sub>  | Clock Cycle Time                                  | 15.0 |      | 20.0 |      | 25.0 |      | ns   |

| t <sub>CH</sub>   | Clock HIGH                                        | 5.0  |      | 6.0  |      | 7.0  |      | ns   |

| t <sub>CL</sub>   | Clock LOW                                         | 5.0  |      | 6.0  |      | 7.0  |      | ns   |

| t <sub>AS</sub>   | Address Set-Up Before CLK Rise                    | 2.0  |      | 2.0  |      | 2.5  |      | ns   |

| t <sub>AH</sub>   | Address Hold After CLK Rise                       | 0.5  |      | 1.0  |      | 1.0  |      | ns   |

| t <sub>CO</sub>   | Data Output Valid After CLK Rise                  |      | 11   |      | 12.0 |      | 14.0 | ns   |

| t <sub>DOH</sub>  | Data Output Hold After CLK Rise                   | 1.5  |      | 1.5  |      | 1.5  |      | ns   |

| t <sub>CENS</sub> | CEN Set-Up Before CLK Rise                        | 2.0  |      | 2.0  |      | 2.5  |      | ns   |

| t <sub>CENH</sub> | CEN Hold After CLK Rise                           | 0.5  |      | 1.0  |      | 1.0  |      | ns   |

| t <sub>WES</sub>  | WE, BWS <sub>[1:0]</sub> Set-Up Before CLK Rise   | 2.0  |      | 2.0  |      | 2.5  |      | ns   |

| t <sub>WEH</sub>  | WE, BWS <sub>[1:0]</sub> Hold After CLK Rise      | 0.5  |      | 1.0  |      | 1.0  |      | ns   |

| t <sub>ALS</sub>  | ADV/LD Set-Up Before CLK Rise                     | 2.0  |      | 2.0  |      | 2.5  |      | ns   |

| t <sub>ALH</sub>  | ADV/LD Hold after CLK Rise                        | 0.5  |      | 1.0  |      | 1.0  |      | ns   |

| t <sub>DS</sub>   | Data Input Set-Up Before CLK Rise                 | 1.7  |      | 2.0  |      | 2.5  |      | ns   |

| t <sub>DH</sub>   | Data Input Hold After CLK Rise                    | 0.5  |      | 1.0  |      | 1.0  |      | ns   |

| t <sub>CES</sub>  | Chip Select Set-Up                                | 2.0  |      | 2.0  |      | 2.5  |      | ns   |

| t <sub>CEH</sub>  | Chip Select Hold After CLK Rise                   | 0.5  |      | 1.0  |      | 1.0  |      | ns   |

| t <sub>CHZ</sub>  | Clock to High-Z <sup>[10,12,13,14]</sup>          |      | 5.0  |      | 5.0  |      | 5.0  | ns   |

| t <sub>CLZ</sub>  | Clock to Low-Z <sup>[10,12,13,14]</sup>           | 2.0  |      | 2.0  |      | 2.0  |      | ns   |

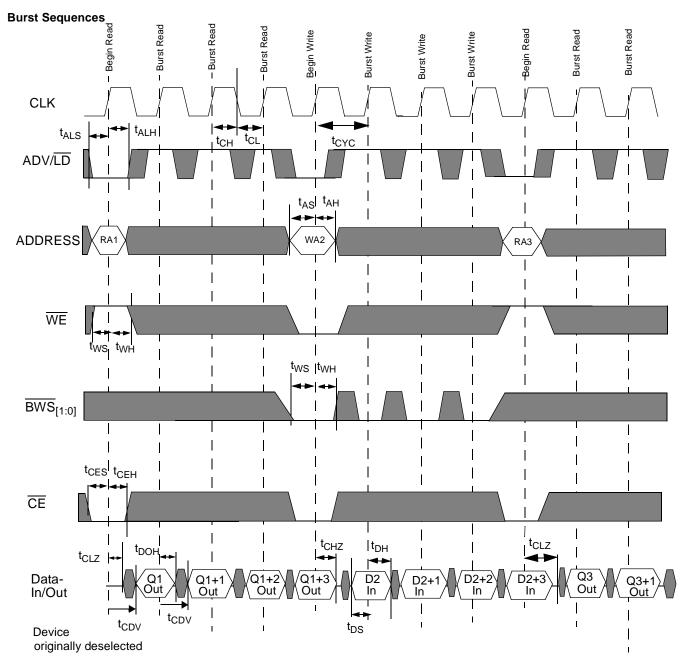

| t <sub>EOHZ</sub> | OE HIGH to Output High-Z <sup>[10,12,13,14]</sup> |      | 6.0  |      | 7.0  |      | 8.0  | ns   |

| t <sub>EOLZ</sub> | OE LOW to Output Low-Z <sup>[10,12,13,14]</sup>   | 0    |      | 0    |      | 0    |      | ns   |

| t <sub>EOV</sub>  | OE LOW to Output Valid <sup>[12]</sup>            |      | 6.0  |      | 7.0  |      | 8.0  | ns   |

### Note:

<sup>12.</sup>  $t_{CHZ}$ ,  $t_{CLZ}$ ,  $t_{OEV}$ ,  $t_{EOLZ}$ , and  $t_{EOHZ}$  are specified with A/C test conditions shown in part (a) of AC Test Loads. Transition is measured  $\pm$  200 mV from steady-state

voltage.

At any given voltage and temperature, t<sub>EOHZ</sub> is less than t<sub>EOLZ</sub> and t<sub>CHZ</sub> is less than t<sub>CLZ</sub> to eliminate bus contention between SRAMs when sharing the same data bus. These specifications do not imply a bus contention condition, but reflect parameters guaranteed over worstcase user conditions. Device is designed to achieve High-Z prior to Low-Z under the same system conditions.

This parameter is sampled and not 100% tested.

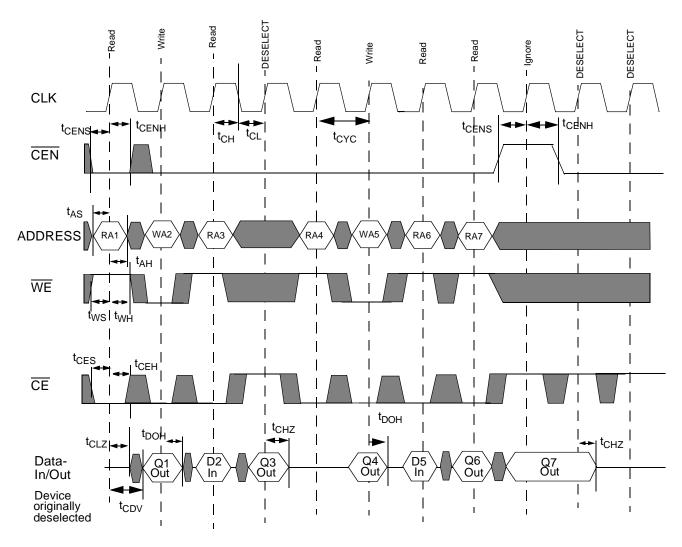

# **Switching Waveforms**

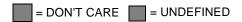

### **Read/Write Waveforms**

$\overline{\text{WE}}$  is the combination of  $\overline{\text{WE}}$  &  $\overline{\text{BWS}}_{\text{X}}$  to define a Write Cycle (see Write Cycle Description Table).  $\overline{\text{CE}}$  is the combination of  $\overline{\text{CE}}_1$ ,  $\overline{\text{CE}}_2$ , and  $\overline{\text{CE}}_3$ . All Chip Selects need to be active in order to select the device. Any Chip Select can deselect the device. RAx stands for Read Address X, WAx stands for Write Address X, Dx stands for Data-in X, Qx stands for Data-out X.

# **Switching Waveforms**

The combination of  $\overline{WE}$  &  $\overline{BWS}_{[1:0]}$  defines a write cycle (see Write Cycle Description Table).  $\overline{CE}$  is the combination of  $\overline{CE}_1$ ,  $CE_2$ , and  $\overline{CE}_3$ . All Chip Enables need to be active in order to select the device. Any Chip Enable can deselect the device. RAx stands for Read Address X, WAx stands for Write Address X, Dx stands for Data-in for location X, Qx stands for Data-out for location X.  $\overline{CEN}$  held LOW. During burst writes, byte writes can be conducted by asserting the appropriate  $\overline{BWS}_{[1:0]}$  input signals. Burst order determined by the state of the MODE input.  $\overline{CEN}$  held LOW.  $\overline{OE}$  held LOW.

# **Switching Waveforms**

# OE Timing

# **Ordering Information**

| Speed<br>(MHz) | Ordering Code | Package<br>Name | Package Type                                  | Operating<br>Range |

|----------------|---------------|-----------------|-----------------------------------------------|--------------------|

| 66             | CY7C1353-66AC | A101            | 100-Lead 14 x 20 x 1.4 mm Thin Quad Flat Pack | Commercial         |

| 50             | CY7C1353-50AC | A101            | 100-Lead 14 x 20 x 1.4 mm Thin Quad Flat Pack | Commercial         |

| 40             | CY7C1353-40AC | A101            | 100-Lead 14 x 20 x 1.4 mm Thin Quad Flat Pack | Commercial         |

Document #: 38-00689-B

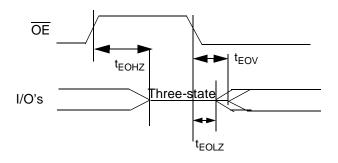

# **Package Diagram**

## 100-Pin Thin Plastic Quad Flatpack (14 x 20 x 1.4 mm) A101

DIMENSIONS ARE IN MILLIMETERS.

51-85050-A

<sup>©</sup> Cypress Semiconductor Corporation, 1999. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges.