#### **Features**

- 3.3V operation (3.0V-3.6V)

- · High speed

- $-t_{AA} = 10/12/15 \text{ ns}$

- CMOS for optimum speed/power

- Low Active Power (L version)

- —576 mW (max.)

- Low CMOS Standby Power (L version)

- -1.80 mW (max.)

- · Automatic power-down when deselected

- Independent control of upper and lower bits

- Available in 44-pin TSOP II and 400-mil SOJ

- Available in a 48-Ball Mini BGA package

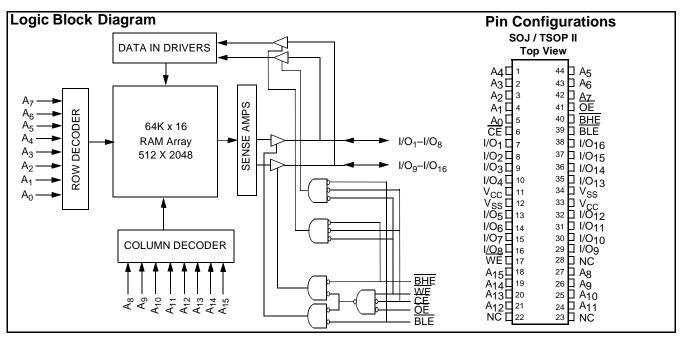

## Functional Description<sup>[1]</sup>

The CY7C1021BV is a high-performance CMOS static RAM organized as 65,536 words by 16 bits. This device has an automatic power-down feature that significantly reduces power consumption when deselected.

## 64K x 16 Static RAM

Writing to the device is accomplished by taking Chip Enable  $(\overline{CE})$  and Write Enable  $(\overline{WE})$  inputs LOW. If Byte Low Enable (BLE) is LOW, then data from I/O pins (I/O $_1$  through I/O $_8$ ), is written into the location specified on the address pins (A $_0$  through A $_{15}$ ). If Byte High Enable (BHE) is LOW, then data from I/O pins (I/O $_9$  through I/O $_{16}$ ) is written into the location specified on the address pins (A $_0$  through A $_{15}$ ).

Reading from the device is accomplished by taking Chip Enable ( $\overline{\text{CE}}$ ) and Output Enable ( $\overline{\text{OE}}$ ) LOW while forcing the Write Enable ( $\overline{\text{WE}}$ ) HIGH. If Byte Low Enable ( $\overline{\text{BLE}}$ ) is LOW, then data from the memory location specified by the address pins will appear on I/O<sub>1</sub> to I/O<sub>8</sub>. If Byte High Enable ( $\overline{\text{BHE}}$ ) is LOW, then data from memory will appear on I/O<sub>9</sub> to I/O<sub>16</sub>. See the truth table at the back of this data sheet for a complete description of read and write modes.

The input/output pins (I/O<sub>1</sub> through I/O<sub>16</sub>) are placed in a high-impedance state when the device is deselected  $(\overline{CE} \ HIGH)$ , the outputs are disabled ( $\overline{OE} \ HIGH)$ , the  $\overline{BHE}$  and  $\overline{BLE}$  are disabled ( $\overline{BHE}$ ,  $\overline{BLE} \ HIGH)$ , or during a write operation ( $\overline{CE} \ LOW$ , and  $\overline{WE} \ LOW$ ).

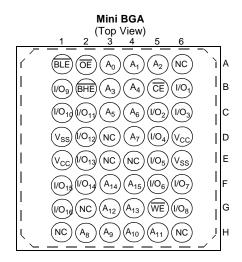

The CY7C1021BV is available in 400-mil-wide SOJ, standard 44-pin TSOP Type II, and 48-ball mini BGA packages.

### **Selection Guide**

|                                |            |   | 7C1021BV-8 | 7C1021BV-10 | 7C1021BV-12 | 7C1021BV-15 |

|--------------------------------|------------|---|------------|-------------|-------------|-------------|

| Maximum Access Time (ns)       |            |   | 8          | 10          | 12          | 15          |

| Maximum Operating Current (mA) | Commercial |   | 170        | 160         | 150         | 140         |

|                                | Industrial |   | 190        | 180         | 170         | 160         |

| Maximum CMOS Standby Current   | Commercial |   | 5          | 5           | 5           | 5           |

| (mA)                           |            | L | 0.500      | 0.500       | 0.500       | 0.500       |

Shaded areas contain advance information.

Note:

1. For guidelines on SRAM system design, please refer to the 'System Design Guidelines' Cypress application note, available on the internet at www.cypress.com.

**Cypress Semiconductor Corporation** • Document #: 38-05148 Rev. \*A

3901 North First Street •

San Jose

CA 95134 • 408-943-2600 Revised September 13, 2002

## **Pin Configurations**

## **Maximum Ratings**

| (Above which the useful life may be impaired. For user guidelines, not tested.) |

|---------------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                               |

| Ambient Temperature with Power Applied–55°C to +125°C                           |

| Supply Voltage on $\rm V_{CC}$ to Relative $\rm GND^{[2]}$ –0.5V to +4.6V       |

| DC Voltage Applied to Outputs in High Z State $^{[2]}$ 0.5V to $V_{CC}$ +0.5V   |

| in High Z State <sup>[2]</sup> –0.5V to V <sub>CC</sub> +0.5V                   |

| DC Input Voltage $^{[2]}$ 0.5V to $V_{CC}$ +0.5V                                |

### Note:

| Current into Outputs (LOW)                             | 20 mA   |

|--------------------------------------------------------|---------|

| Static Discharge Voltage(per MIL-STD-883, Method 3015) | .>2001V |

| Latch-Up Current                                       | >200 mA |

## **Operating Range**

| Range      | Ambient Temperature | V <sub>CC</sub> |

|------------|---------------------|-----------------|

| Commercial | 0°C to +70°C        | 3.3V ± 10%      |

| Industrial | -40°C to +85°C      | 3.3V ± 10%      |

<sup>2.</sup> Mimimum voltage is-2.0V for pulse durations of less than 20 ns.

## **Electrical Characteristics** Over the Operating Range

|                  |                                                      |                                                                                                                                                                                     |       | 7C1021BV-8 |                           | 7C1021BV-10 |                           | 7C1021BV-12 |                           | 7C1021BV-15 |                           |      |

|------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|---------------------------|-------------|---------------------------|-------------|---------------------------|-------------|---------------------------|------|

| Parameter        | Description                                          | Test Condition                                                                                                                                                                      | ns    | Min.       | Max.                      | Min.        | Max.                      | Min.        | Max.                      | Min.        | Max.                      | Unit |

| V <sub>OH</sub>  | Output HIGH<br>Voltage                               | $V_{CC} = Min.,$<br>$I_{OH} = -4.0 \text{ mA}$                                                                                                                                      |       | 2.4        |                           | 2.4         |                           | 2.4         |                           | 2.4         |                           | V    |

| V <sub>OL</sub>  | Output LOW<br>Voltage                                | $V_{CC} = Min., I_{OL} = 8$                                                                                                                                                         | .0 mA |            | 0.4                       |             | 0.4                       |             | 0.4                       |             | 0.4                       | V    |

| V <sub>IH</sub>  | Input HIGH<br>Voltage                                |                                                                                                                                                                                     |       | 2.2        | V <sub>CC</sub> +<br>0.3V | 2.2         | V <sub>CC</sub> +<br>0.3V | 2.2         | V <sub>CC</sub> +<br>0.3V | 2.2         | V <sub>CC</sub> +<br>0.3V | V    |

| V <sub>IL</sub>  | Input LOW<br>Voltage <sup>[2]</sup>                  |                                                                                                                                                                                     |       | -0.3       | 0.8                       | -0.3        | 0.8                       | -0.3        | 0.8                       | -0.3        | 0.8                       | V    |

| I <sub>IX</sub>  | Input Load<br>Current                                | $GND \leq V_I \leq V_CC$                                                                                                                                                            |       | -1         | +1                        | -1          | +1                        | <b>–1</b>   | +1                        | -1          | +1                        | μА   |

| I <sub>OZ</sub>  | Output Leakage<br>Current                            | GND ≤ V <sub>I</sub> ≤ V <sub>CC</sub> ,<br>Output Disabled                                                                                                                         |       | -1         | +1                        | -1          | +1                        | <b>-1</b>   | +1                        | -1          | +1                        | μА   |

| I <sub>CC</sub>  | V <sub>CC</sub> Operating                            |                                                                                                                                                                                     | Com   |            | 170                       |             | 160                       |             | 150                       |             | 140                       | mA   |

|                  | Supply Current                                       | $I_{OUT} = 0 \text{ mA},$<br>$f = f_{MAX} = 1/t_{RC}$                                                                                                                               | Ind   |            | 190                       |             | 120                       |             | 170                       |             | 160                       | mA   |

| I <sub>SB1</sub> | Automatic CE<br>Power-Down<br>Current<br>—TTL Inputs | $\label{eq:local_max} \begin{split} & \underline{\text{Max}}. \ V_{CC}, \\ & CE \geq V_{IH} \\ & V_{IN} \geq V_{IH} \ \text{or} \\ & V_{IN} \leq V_{IL}, \ f = f_{MAX} \end{split}$ |       |            | 40                        |             | 40                        |             | 40                        |             | 40                        | mA   |

| I <sub>SB2</sub> | Automatic CE                                         | Max. V <sub>CC</sub> ,                                                                                                                                                              |       |            | 5                         |             | 5                         |             | 5                         |             | 5                         | mA   |

|                  | Power-Down<br>Current<br>—CMOS Inputs                | rent $V_{IN} \ge V_{CC} - 0.3V$ ,                                                                                                                                                   | L     |            | 500                       |             | 500                       |             | 500                       |             | 500                       | μА   |

Shaded areas contain advance information.

## Capacitance<sup>[3]</sup>

| Parameter        | Description        | Test Conditions                  | Max. | Unit |

|------------------|--------------------|----------------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | T <sub>A</sub> = 25°C, f = 1 MHz | 6    | pF   |

| C <sub>OUT</sub> | Output Capacitance |                                  | 8    | pF   |

#### Note:

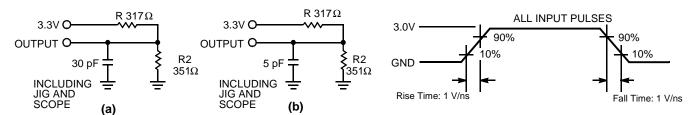

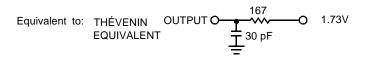

### **AC Test Loads and Waveforms**

Document #: 38-05148 Rev. \*A

<sup>3.</sup> Tested initially and after any design or process changes that may affect these parameters.

## Switching Characteristics<sup>[4]</sup> Over the Operating Range

|                   |                                     | 7C102 | 21BV-8 | 7C1021BV-10 |      | 7C1021BV-12 |      | 7C102 | 1BV-15 |      |

|-------------------|-------------------------------------|-------|--------|-------------|------|-------------|------|-------|--------|------|

| Parameter         | Parameter Description               |       | Max.   | Min.        | Max. | Min.        | Max. | Min.  | Max.   | Unit |

| READ CYC          | LE .                                |       |        | •           | •    | •           | •    |       | •      |      |

| t <sub>RC</sub>   | Read Cycle Time                     | 8     |        | 10          |      | 12          |      | 15    |        | ns   |

| t <sub>AA</sub>   | Address to Data Valid               |       | 8      |             | 10   |             | 12   |       | 15     | ns   |

| t <sub>OHA</sub>  | Data Hold from Address Change       | 3     |        | 3           |      | 3           |      | 3     |        | ns   |

| t <sub>ACE</sub>  | CE LOW to Data Valid                |       | 8      |             | 10   |             | 12   |       | 15     | ns   |

| t <sub>DOE</sub>  | OE LOW to Data Valid                |       | 4      |             | 4    |             | 6    |       | 7      | ns   |

| t <sub>LZOE</sub> | OE LOW to Low Z                     | 0     |        | 0           |      | 0           |      | 0     |        | ns   |

| t <sub>HZOE</sub> | OE HIGH to High Z <sup>[5, 6]</sup> |       | 4      |             | 5    |             | 6    |       | 7      | ns   |

| t <sub>LZCE</sub> | CE LOW to Low Z <sup>[6]</sup>      | 3     |        | 3           |      | 3           |      | 3     |        | ns   |

| t <sub>HZCE</sub> | CE HIGH to High Z <sup>[5, 6]</sup> |       | 4      |             | 5    |             | 6    |       | 7      | ns   |

| t <sub>PU</sub>   | CE LOW to Power-Up                  | 0     |        | 0           |      | 0           |      | 0     |        | ns   |

| t <sub>PD</sub>   | CE HIGH to Power-Down               |       | 12     |             | 12   |             | 12   |       | 15     | ns   |

| t <sub>DBE</sub>  | Byte Enable to Data Valid           | 4     |        |             | 5    |             | 6    |       | 7      | ns   |

| t <sub>LZBE</sub> | Byte Enable to Low Z                | 0     |        | 0           |      | 0           |      | 0     |        | ns   |

| t <sub>HZBE</sub> | Byte Disable to High Z              |       | 4      |             | 5    |             | 6    |       | 7      | ns   |

| WRITE CYC         | LE <sup>[7]</sup>                   |       |        |             |      |             |      |       |        |      |

| t <sub>WC</sub>   | Write Cycle Time                    | 8     |        | 10          |      | 12          |      | 15    |        | ns   |

| t <sub>SCE</sub>  | CE LOW to Write End                 | 7     |        | 8           |      | 9           |      | 10    |        | ns   |

| t <sub>AW</sub>   | Address Set-Up to Write End         | 6     |        | 7           |      | 8           |      | 10    |        | ns   |

| t <sub>HA</sub>   | Address Hold from Write End         | 0     |        | 0           |      | 0           |      | 0     |        | ns   |

| t <sub>SA</sub>   | Address Set-Up to Write Start       | 0     |        | 0           |      | 0           |      | 0     |        | ns   |

| t <sub>PWE</sub>  | WE Pulse Width                      | 6     |        | 8           |      | 8           |      | 10    |        | ns   |

| t <sub>SD</sub>   | Data Set-Up to Write End            | 4     |        | 6           |      | 6           |      | 8     |        | ns   |

| t <sub>HD</sub>   | Data Hold from Write End            | 0     |        | 0           |      | 0           |      | 0     |        | ns   |

| t <sub>LZWE</sub> | WE HIGH to Low Z <sup>[6]</sup>     | 3     |        | 3           |      | 3           |      | 3     |        | ns   |

| t <sub>HZWE</sub> | WE LOW to High Z <sup>[5, 6]</sup>  |       | 4      |             | 5    |             | 6    |       | 7      | ns   |

| t <sub>BW</sub>   | Byte Enable to End of Write         | 8     |        | 8           |      | 8           |      | 9     |        | ns   |

Shaded areas contain advance information.

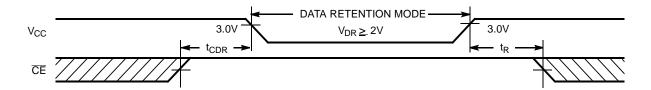

## Data Retention Characteristics Over the Operating Range (L version only)

| Parameter                       | Description                        |          | Conditions <sup>[8]</sup>                                                                                      | Min.            | Max. | Unit |

|---------------------------------|------------------------------------|----------|----------------------------------------------------------------------------------------------------------------|-----------------|------|------|

| $V_{DR}$                        | V <sub>CC</sub> for Data Retention |          |                                                                                                                | 2.0             |      | V    |

| ICCDR                           | Data Retention Current Co          | om'l     | $V_{CC} = V_{DR} = 2.0V,$<br>$CE \ge V_{CC} - 0.3V,$<br>$V_{IN} \ge V_{CC} - 0.3V \text{ or } V_{IN} \le 0.3V$ |                 | 100  | μА   |

| t <sub>CDR</sub> <sup>[9]</sup> | Chip Deselect to Data Retention    | ion Time |                                                                                                                | 0               |      | ns   |

| t <sub>R</sub> <sup>[10]</sup>  | Operation Recovery Time            |          |                                                                                                                | t <sub>RC</sub> |      | ns   |

#### Notes:

- 4. Test conditions assume signal transition time of 3 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V, and output loading of the specified loL/loH and 30-pF load capacitance.

5. tHZDE, tHZBE, tHZDE, and tHZWE are specified with a load capacitance of 5 pF as in part (b) of AC Test Loads. Transition is measured ±500 mV from steady-state voltage.

6. At any given temperature and voltage condition, tHZCE is less than tLZCE, tHZCE is less than tHZCE is less than tHZCE.

7. The internal write time of the memory is defined by the overlap of CE LOW, WE LOW and BHE / BLE LOW. CE, WE and BHE / BLE must be LOW to initiate a write, and the transition of these signals can terminate the write. The input data set-up and hold timing should be referenced to the leading edge of the signal that terminates the write.

8. No input may exceed V<sub>CC</sub> + 0.5V.

9. Tested initially and after any design or process changes that may affect these parameters.

10. t<sub>1</sub> ≤ 3 ns for the -12 and -15 speeds. t<sub>1</sub> ≤ 5 ns for the -20 and slower speeds.

Document #: 38-05148 Rev. \*A

## **Data Retention Waveform**

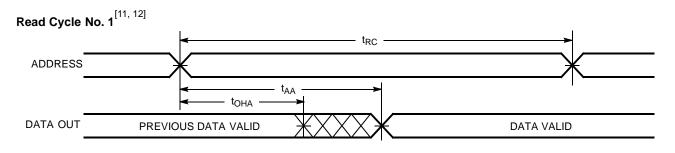

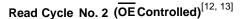

## **Switching Waveforms**

#### Notes:

- 11. Device is continuously selected.  $\overline{OE}$ ,  $\overline{CE}$ ,  $\overline{BHE}$  and/or  $\overline{BHE} = V_{IL}$ .

- 12. WE is HIGH for read cycle.

13. Address valid prior to or coincident with CE transition LOW.

[+] Feedback

## Switching Waveforms (continued)

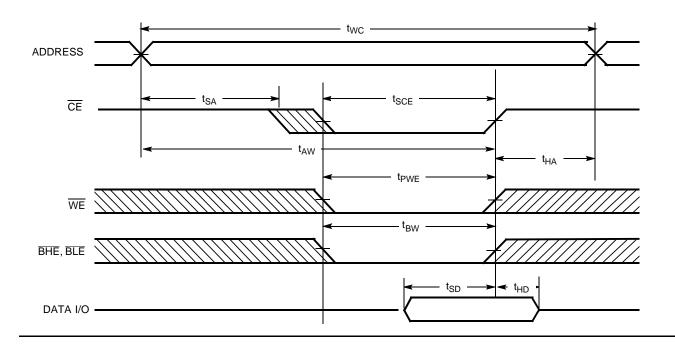

# Write Cycle No. 1 (CE Controlled) [14, 15]

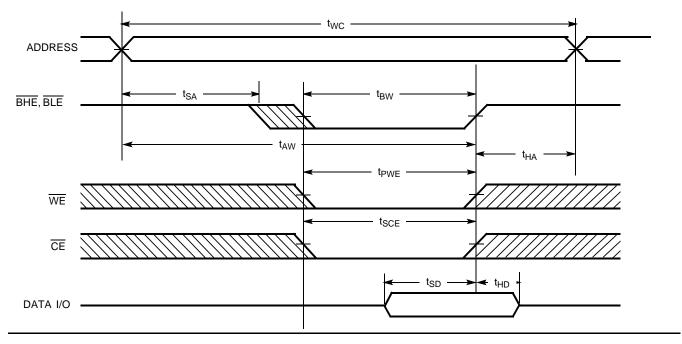

## Write Cycle No. 2 (BLE or BHE Controlled)

- 14. Data I/O is high impedance if OE or BHE and/or BLE= V<sub>IH</sub>.

15. If CE goes HIGH simultaneously with WE going HIGH, the output remains in a high-impedance state.

## Switching Waveforms (continued)

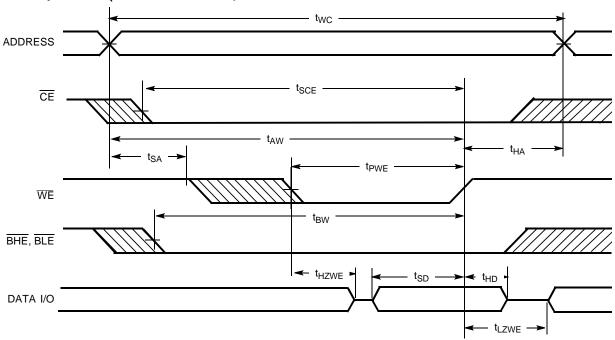

## Write Cycle No. 3 (WE Controlled, LOW)

## **Truth Table**

| CE | OE | WE | BLE | вне | I/O <sub>1</sub> –I/O <sub>8</sub> | I/O <sub>9</sub> -I/O <sub>16</sub> | Mode                       | Power                      |

|----|----|----|-----|-----|------------------------------------|-------------------------------------|----------------------------|----------------------------|

| Н  | Х  | Х  | Χ   | Х   | High Z                             | High Z                              | Power-Down                 | Standby (I <sub>SB</sub> ) |

| L  | L  | Н  | L   | L   | Data Out                           | Data Out                            | Read - All bits            | Active (I <sub>CC</sub> )  |

|    |    |    | L   | Н   | Data Out                           | High Z                              | Read - Lower bits only     | Active (I <sub>CC</sub> )  |

|    |    |    | Н   | L   | High Z                             | Data Out                            | Read - Upper bits only     | Active (I <sub>CC</sub> )  |

| L  | Х  | L  | L   | L   | Data In                            | Data In                             | Write - All bits           | Active (I <sub>CC</sub> )  |

|    |    |    | L   | Н   | Data In                            | High Z                              | Write - Lower bits only    | Active (I <sub>CC</sub> )  |

|    |    |    | Н   | L   | High Z                             | Data In                             | Write - Upper bits only    | Active (I <sub>CC</sub> )  |

| L  | Н  | Н  | Χ   | Х   | High Z                             | High Z                              | Selected, Outputs Disabled | Active (I <sub>CC</sub> )  |

| L  | Х  | Х  | Н   | Н   | High Z                             | High Z                              | Selected, Outputs Disabled | Active (I <sub>CC</sub> )  |

## **Ordering Information**

| Speed (ns) | Ordering Code            | Package<br>Name | Package Type                                     | Operating<br>Range |

|------------|--------------------------|-----------------|--------------------------------------------------|--------------------|

| 8          | CY7C1021BV33-8BAC        | BA48A           | 48-Ball Mini Ball Grid Array (7.00 mm x 7.00 mm) | Commercial         |

|            | CY7C1021BV33-8VC         | V34             | 44-Lead (400-Mil) Molded SOJ                     |                    |

|            | CY7C1021BV33L-8VC        | V34             | 44-Lead (400-Mil) Molded SOJ                     |                    |

|            | CY7C1021BV33-8ZC         | Z44             | 44-Lead TSOP Type II                             |                    |

|            | CY7C1021BV33L-8ZC        | Z44             | 44-Lead TSOP Type II                             |                    |

| 10         | CY7C1021BV33-10BAC       | BA48A           | 48-Ball Mini Ball Grid Array (7.00 mm x 7.00 mm) | Commercial         |

|            | CY7C1021BV33-10VC        | V34             | 44-Lead (400-Mil) Molded SOJ                     |                    |

|            | CY7C1021BV33L-10VC       | V34             | 44-Lead (400-Mil) Molded SOJ                     |                    |

|            | CY7C1021BV33-10ZC        | Z44             | 44-Lead TSOP Type II                             |                    |

|            | CY7C1021BV33L-10ZC       | Z44             | 44-Lead TSOP Type II                             |                    |

| 12         | CY7C1021BV33-12BAC       | BA48A           | 48-Ball Mini Ball Grid Array (7.00 mm x 7.00 mm) | Commercial         |

|            | CY7C1021BV33-12VC        | V34             | 44-Lead (400-Mil) Molded SOJ                     |                    |

|            | CY7C1021BV33L-12VC       | V34             | 44-Lead (400-Mil) Molded SOJ                     |                    |

|            | CY7C1021BV33-12ZC        | Z44             | 44-Lead TSOP Type II                             |                    |

|            | CY7C1021BV33L-12ZC       | Z44             | 44-Lead TSOP Type II                             |                    |

|            | CY7C1021BV33-12BAI BA48A |                 | 48-Ball Mini Ball Grid Array (7.00 mm x 7.00 mm) | Industrial         |

|            | CY7C1021BV33-12VI        | V34             | 44-Lead (400-Mil) Molded SOJ                     |                    |

| 15         | CY7C1021BV33-15BAC       | BA48A           | 48-Ball Mini Ball Grid Array (7.00 mm x 7.00 mm) | Commercial         |

|            | CY7C1021BV33L-15BAC      | BA48A           | 48-Ball Mini Ball Grid Array (7.00 mm x 7.00 mm) |                    |

|            | CY7C1021BV33-15VC        | V34             | 44-Lead (400-Mil) Molded SOJ                     |                    |

|            | CY7C1021BV33L-15VC       | V34             | 44-Lead (400-Mil) Molded SOJ                     |                    |

|            | CY7C1021BV33-15ZC        | Z44             | 44-Lead TSOP Type II                             |                    |

|            | CY7C1021BV33L-15VC       | Z44             | 44-Lead TSOP Type II                             |                    |

|            | CY7C1021BV33-15BAI       | BA48A           | 48-Ball Mini Ball Grid Array (7.00 mm x 7.00 mm) | Industrial         |

|            | CY7C1021BV33L-15BAI      | BA48A           | 48-Ball Mini Ball Grid Array (7.00 mm x 7.00 mm) |                    |

|            | CY7C1021BV33-15VI        | V34             | 44-Lead (400-Mil) Molded SOJ                     |                    |

|            | CY7C1021BV33L-15ZI       | Z44             | 44-Lead TSOP Type II                             |                    |

Shaded areas contain advance information.

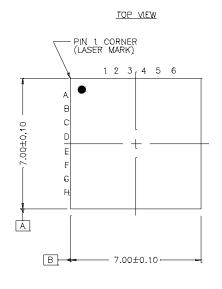

## **Package Diagrams**

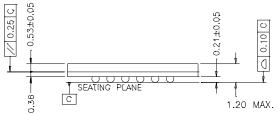

## 48-Ball (7.00 mm x 7.00 mm x 1.2 mm) FBGA BA48A

51-85096-\*E

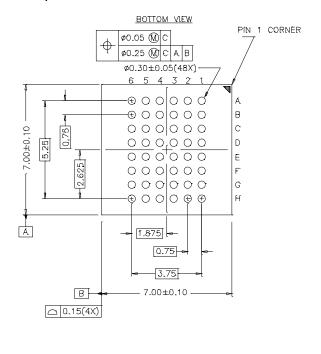

## Package Diagrams (continued)

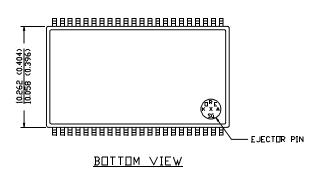

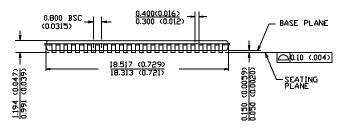

### 44-Lead (400-Mil) Molded SOJ V34

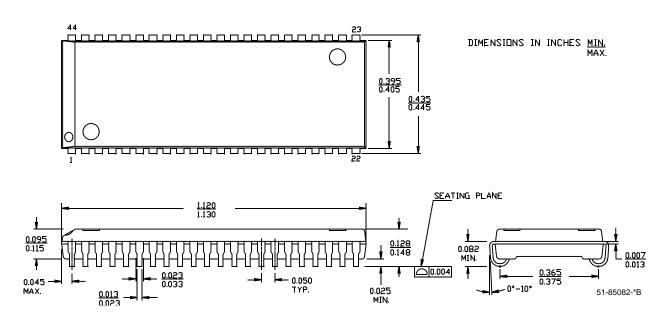

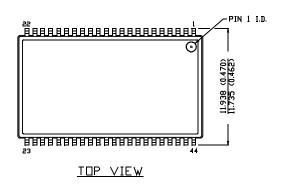

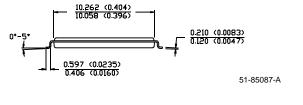

#### 44-Pin TSOP II Z44

DIMENSION IN MM (INCH) MAX MIN.

All product and company names mentioned in this document may be the trademarks of their respective holders.

## **Document History Page**

| Document Title: CY7C1021BV33 64K x 16 Static RAM Document Number: 38-05148 |         |               |                 |                                                   |  |  |  |  |

|----------------------------------------------------------------------------|---------|---------------|-----------------|---------------------------------------------------|--|--|--|--|

| REV.                                                                       | ECN NO. | Issue<br>Date | Orig. of Change | Description of Change                             |  |  |  |  |

| **                                                                         | 109892  | 09/22/01      | SZV             | Change from Spec number: 38-00954 to 38-05148     |  |  |  |  |

| *A                                                                         | 116474  | 09/16/02      | CEA             | Add applications foot note to data sheet, page 1. |  |  |  |  |

Document #: 38-05148 Rev. \*A Page 11 of 11