## **RDS Demodulation IC**

### Overview

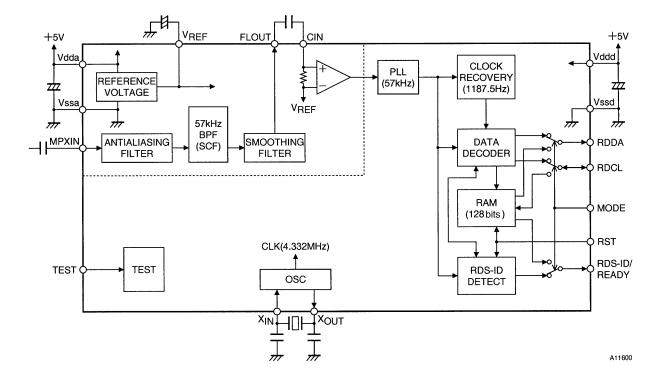

The LC72723 is an RDS (Radio Data System) signal demodulation IC. This IC integrates a bandpass filter, the demodulation circuit, and buffer RAM on a single chip and can read out RDS data in slave mode operation with the provision of an external clock input. It also supports master mode, in which the data is read out in synchronization with an RDS clock output provided by the IC itself.

### **Functions**

- · Bandpass filter: Switched capacitor filter (SCF)

- RDS demodulation: Functions include 57kHz carrier regeneration, clock regeneration, biphase decoding, and differential decoding

- Buffer RAM: Stores 128 bits (about 100 ms) of data.

- Data output: Output can be switched between master mode and slave mode readout.

- RDS ID detection: Supports ID reset

- Standby control: Stops the crystal oscillator.

- Fully adjustment free.

## **Ratings**

- Operating supply voltage: 4.5 to 5.5 V

- Operating temperature: -40 to 85°C

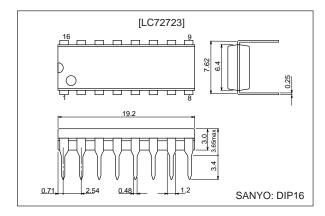

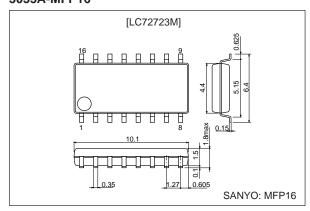

- Packages: DIP16 and MFP16

## **Package Dimensions**

unit: mm

#### 3006B-DIP16

unit: mm

## 3035A-MFP16

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein

SANYO Electric Co.,Ltd. Semiconductor Company

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

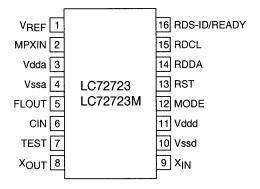

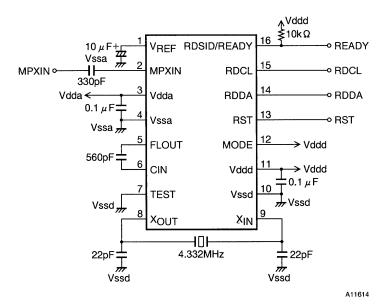

## Pin Assignment (DIP16/MFP16)

## **Block Diagram**

# **Pin Descriptions**

| Pin No. | Pin          | Function                                                    | I/O    | Pin circuit type        |

|---------|--------------|-------------------------------------------------------------|--------|-------------------------|

| 1       | VREF         | Reference voltage output (Vdda/2)                           | Output | Vdda N Vssa             |

| 2       | MPXIN        | Base band (multiplex) signal input                          | Input  | √Vdda<br>↓ W — W — Vssa |

| 5       | FLOUT        | Subcarrier output (filter output)                           | Output |                         |

| 6       | CIN          | Subcarrier input (comparator input)                         | Input  | Vssa WREF               |

| 3       | Vdda         | Analog system power supply (+5 V)                           | _      | _                       |

| 4       | Vssa         | Analog system ground                                        | _      | _                       |

| 8       | XOUT         | Crystal element output (4.332 MHz)                          | Output | X <sub>IN</sub> Vddd W  |

| 9       | XIN          | Crystal element input (or external reference signal input)  |        | X <sub>OUT</sub> Vssd   |

| 7       | TEST         | Test input                                                  | Input  | _                       |

| 12      | MODE         | Readout mode setting (0: master, 1: slave)                  |        | □ <b>↓</b>  \$>         |

| 13      | RST          | RDS ID and RAM reset (Active high logic)                    |        | ∭ Vssd                  |

| 14      | RDDA         | RDS data output                                             | Output | ↑Vddd<br>→ Vssd         |

| 15      | RDCL         | RDS clock output (master mode) RDS clock input (slave mode) | I/O    | Vddd<br>Vssd            |

| 16      | RDS-ID/READY | RDS ID/ready output (Active low)                            | Output | Vssd ,,,                |

| 11      | Vddd         | Digital system power supply (+5 V)                          | _      | _                       |

| 10      | Vssd         | Digital system ground                                       | _      | _                       |

# **Specifications**

# Absolute Maximum Ratings at $Ta = 25^{\circ}C$ , Vssd = Vssa = 0 V

| Parameter                   | Symbol                | Conditions              | Ratings            | Unit |

|-----------------------------|-----------------------|-------------------------|--------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max   | Vddd, Vdda *            | -0.3 to 7.0        | V    |

|                             | V <sub>IN</sub> 1 max | TEST, MODE, RST         | -0.3 to +7.0       | V    |

| Maximum input voltage       | V <sub>IN</sub> 2 max | XIN, RDCL               | -0.3 to Vddd + 0.3 | V    |

|                             | V <sub>IN</sub> 3 max | MPXIN, CIN              | -0.3 to Vdda + 0.3 | V    |

|                             | Vo1 max               | RDS-ID (READY)          | -0.3 to +7.0       | V    |

| Maximum output voltage      | Vo2 max               | XOUT, RDDA, RDCL        | -0.3 to Vddd + 0.3 | V    |

|                             | Vo3 max               | FLOUT                   | -0.3 to Vdda + 0.3 | V    |

| Maximum autout aurrant      | lo1 max               | XOUT, FLOUT, RDDA, RDCL | +3.0               | mA   |

| Maximum output current      | lo2 max               | RDS-ID (READY)          | +20.0              | mA   |

| Allowable power dissipation | Pd max                | (Ta ≤ 85°C)             | DIP16: 300         | mW   |

| Allowable power dissipation | Pamax                 | (1a ≤ 85°C)             | MFP16 : 140        | mW   |

| Operating temperature       | Topr                  |                         | -40 to +85         | °C   |

| Storage temperature         | Tstg                  |                         | -55 to +125        | °C   |

<sup>\*:</sup> Note that Vdda must be less than or equal to Vddd + 0.3 V

## Allowable Operating Ranges at Ta = -40 to $+85^{\circ}C$ , Vssd = Vssa = 0 V, Vddd = Vdda

| Parameter                              | Symbol            | Conditions                |                            |          | Ratings |          |       |

|----------------------------------------|-------------------|---------------------------|----------------------------|----------|---------|----------|-------|

| Parameter                              | Symbol            |                           |                            | min      | typ     | max      | Unit  |

| Supply voltage                         | V <sub>DD</sub>   | Vddd, Vd                  | da: Vddd = Vdda            | 4.5      | 5.0     | 5.5      | V     |

| High level input value                 | V <sub>IH</sub> 1 | TEST, MO                  | TEST, MODE, RST            |          |         | 6.5      | V     |

| High-level input voltage               | V <sub>IH</sub> 2 | RDCL                      |                            | 0.7 Vddd |         | Vddd     | V     |

| Low-level input voltage                | V <sub>IL</sub>   | TEST, MO                  | DDE, RST, RDCL             | 0        |         | 0.3 Vddd | V     |

| Output valta sa                        | Vo1               | RDDA, R                   | DCL                        |          |         | Vddd     | V     |

| Output voltage                         | Vo2               | RDS-ID (                  | RDS-ID (READY)             |          |         | 6.5      | V     |

|                                        | V <sub>IN</sub> 1 | MPXIN                     | f = 57 ±2 KHz              |          |         | 50       | mVrms |

| Input amplitude                        | V <sub>IN</sub> 2 |                           | 100% modulation, composite | 100      |         |          | mVrms |

|                                        | VX <sub>IN</sub>  | XIN                       |                            | 400      |         | 1500     | mVrms |

| Guaranteed oscillator operating range  | Xtal              | XIN, XOUT: C1 ≤ 120 Ω     |                            |          | 4.332   |          | MHz   |

| Crystal oscillator frequency deviation | TXtal             | XIN, XOUT: Fo = 4.332 MHz |                            |          |         | ±100     | ppm   |

| RDCL setup time                        | t <sub>CS</sub>   | RDCL, RDDA                |                            | 0        |         |          | μs    |

| RDCL high-level time                   | t <sub>CH</sub>   | RDCL                      |                            | 0.75     |         |          | μs    |

| RDCL low-level time                    | t <sub>CL</sub>   | RDCL                      |                            | 0.75     |         |          | μs    |

| Data output time                       | t <sub>DC</sub>   | RDCL, RDDA                |                            |          |         | 0.75     | μS    |

| READY output time                      | t <sub>RC</sub>   | RDCL, READY               |                            |          |         | 0.75     | μs    |

| READY low-level time                   | t <sub>RL</sub>   | READY                     |                            |          |         | 107      | ms    |

## Electrical Characteristics at Ta = -40 to $+85^{\circ}C$ , Vssd = Vssa = 0 V, Vddd = Vdda

| Parameter                    | Symbol            | Conditions                                     |            | Ratings  |      |      |

|------------------------------|-------------------|------------------------------------------------|------------|----------|------|------|

| Parameter                    | Symbol            | Conditions                                     | min        | typ      | max  | Unit |

| Input registeres             | Rmpxin            | MPXIN-Vssa: f = 57 KHz                         |            | 23       |      | ΚΩ   |

| Input resistance             | Rcin              | CIN-Vssa: f = 57 KHz                           |            | 100      |      | ΚΩ   |

| Internal feedback resistance | Rf                | XIN                                            |            | 1.0      |      | МΩ   |

| Center frequency             | fc                | FLOUT                                          | 56.5       | 57.0     | 57.5 | KHz  |

| -3dB bandwidth               | BW-3dB            | FLOUT                                          | 2.5        | 3.0      | 3.5  | KHz  |

| Gain                         | Gain              | MPXIN-FLOUT: f = 57 KHz                        | 28         | 31       | 34   | dB   |

|                              | Att1              | FLOUT: Δf = ±7 KHz                             | 30         |          |      | dB   |

| Stop band attenuation        | Att2              | FLOUT: f < 45 KHz, f > 70 KHz                  | 40         |          |      | dB   |

|                              | Att3              | FLOUT: f < 20 KHz                              | 50         |          |      | dB   |

| Reference voltage output     | Vref              | Vref: Vdda = 5 V                               |            | 2.5      |      | V    |

| Hysteresis                   | V <sub>HIS</sub>  | TEST, MODE, RST, RDCL                          |            | 0.1 Vddd |      | V    |

| Low-level output voltage     | V <sub>OL1</sub>  | RDDA, RDCL : I = 2 mA                          |            |          | 0.4  | V    |

| Low-level output voltage     | V <sub>OL2</sub>  | RDS-ID (READY): I = 8 mA                       |            |          | 0.4  | V    |

| High-level output voltage    | V <sub>OH</sub>   | RDDA, RDCL : I = 2 mA                          | Vddd - 0.4 |          |      | V    |

| High-level input current     | I <sub>IH</sub> 1 | TEST, MODE, RST, RDCL : V <sub>I</sub> = 6.5 V |            |          | 5.0  | μA   |

| nigri-level input current    | I <sub>IH</sub> 2 | XIN: V <sub>I</sub> = Vddd                     | 2.0        |          | 11   | μA   |

| Low lovel input ourrent      | I <sub>IL</sub> 1 | TEST, MODE, RST, RDCL : V <sub>I</sub> = 0 V   |            |          | 5.0  | μA   |

| Low-level input current      | I <sub>IL</sub> 2 | XIN: V <sub>I</sub> = 0 V                      | 2.0        |          | 11   | μA   |

| Output off leakage current   | I <sub>OFF</sub>  | RDS-ID (READY): V <sub>O</sub> = 6.5 V         |            |          | 5.0  | μA   |

| Current drain                | ldd               | Vddd + Vdda                                    |            | 8        |      | mA   |

# **Inputs and Outputs**

| TE | ST | MODE | Circuit operating mode                    | RDCL pin     | RDS-ID/READY pin |

|----|----|------|-------------------------------------------|--------------|------------------|

| -  | 0  | 0    | Master mode                               | Clock output | RDS-ID output    |

| (  | 0  | 1    | Slave mode                                | Clock input  | READY output     |

|    | 1  | 0    | Standby mode (crystal oscillator stopped) | _            | _                |

|    | 1  | 1    | IC test mode (Cannot be set by users.)    | _            | _                |

|         | RST pin                                                                                                       |

|---------|---------------------------------------------------------------------------------------------------------------|

| RST = 0 | Normal operation                                                                                              |

| RST = 1 | The RDS-ID and demodulation circuits are cleared, and (in slave mode) the READY state and memory are cleared. |

|                                        | RDS ID/READY pin                       |  |  |  |

|----------------------------------------|----------------------------------------|--|--|--|

| Master mode RDS-ID output (active low) |                                        |  |  |  |

| Slave mode                             | Readout data ready output (active low) |  |  |  |

Note: The RDS-ID (READY) pin is an n-channel open-drain output, and data is read out by connecting a pull-up resistor.

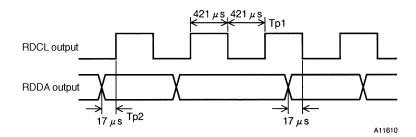

### **RDCL/RDDA Output Timing**

Master mode

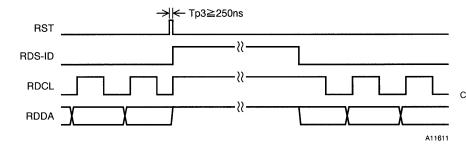

### **RST Operation**

• Master mode

Caution: After an RST input, the RDCL and RDDA outputs stop at the high level until the first RDS ID detection.

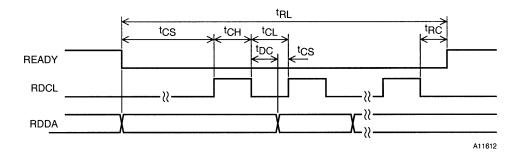

#### **RDCL Control in Slave Mode**

| Parameter            | Symbol          | Conditions  |      | Unit |      |      |

|----------------------|-----------------|-------------|------|------|------|------|

| Parameter            | Symbol          | Conditions  | min  | typ  | max  | Onit |

| RDCL setup time      | t <sub>CS</sub> | RDCL, RDDA  | 0    |      |      | μs   |

| RDCL high-level time | t <sub>CH</sub> | RDCL        | 0.75 |      |      | μs   |

| RDCL low-level time  | t <sub>CL</sub> | RDCL        | 0.75 |      |      | μs   |

| Data output time     | t <sub>DC</sub> | RDCL, RDDA  |      |      | 0.75 | μs   |

| READY output time    | t <sub>RC</sub> | RDCL, READY |      |      | 0.75 | μs   |

| Ready low-level time | t <sub>RL</sub> | READY       |      |      | 107  | ms   |

Notes:1. Start RDCL clock input after the READY signal goes low. Applications must stand by with RDCL held low when the READY pin is high.

- 2. Each time the RDCL input is switched from low to high to low, the application must check the READY signal level after the period t<sub>RC</sub> has elapsed once RDCL has been set low. If READY is at the low level, the application may apply the next RDCL clock cycle. If READY is high, the application must stop RDCL input at that point.

- 3. When the above timing conditions are met, RDDA can be read at either the rise or fall of the RDCL signal.

- 4. After the last data from memory has been read, READY will be high once the period t<sub>RC</sub> has elapsed after the fall of the RDCL signal. If even 1 bit of data has been written to memory, READY will be low and the application will be able to read that data.

- 5. When switching channels, it is desirable to immediately reset memory and the READY pin with an RST input. If this is not done, data received on the previous channel may remain in memory. When the IC is reset, data is not written until the RDS-ID is detected, and therefore, the READY signal will go low after the RDS-ID is detected. (Although the RDS-ID is not output in slave mode, it is detected internally in the IC.) After an RST input, once an RDS-ID has been detected, all received data will be written to memory regardless of the RDS-ID detection state.

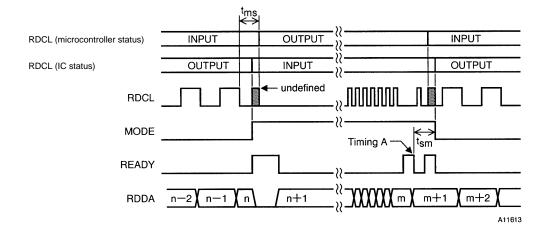

- 6. The readout mode may be switched between master and slave modes during readout. Applications must observe the following points to assure data continuity during this operation.

- Data acquisition timing in master mode

Data must be read on the falling edge of RDCL.

- Timing of the switch from master mode to slave mode

After the RDCL output goes low and the RDDA data has been acquired, the application must set MODE high immediately. Then, the microcontroller starts output by setting the RDCL signal low. The microcontroller RDCL output must start within 840 µs (tms) after RDCL went low. In this case, if the last data read in master mode was data item n, then data starting with item n+1 will be written to memory.

- Timing of the switch from slave mode to master mode

After all data has been read from memory and READY has gone high, the application must then wait until READY goes low once again the next time (timing A in the figure), immediately read out one bit of data and input the RDCL clock. Then, at the point READY goes high, the microcontroller must terminate RDCL output and then set MODE low. The application must switch MODE to low within 840 µs (tms) after READY goes low (timing A in the figure).

### LC72723 Sample Application Connection Circuit (for slave mode operation)

Caution: If the RST pin is unused, it must be connected to ground.

- Specifications of any and all SANYO products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO products (including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Electric Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of April, 1999. Specifications and information herein are subject to change without notice.