CY244/45ZXC

# Factory Programmable Quad PLL Clock Generator with VCXC

#### Features

- · Fully integrated phase-locked loops (PLLs)

- Selectable Output Frequency

- Programmable Output Frequencies

- Output Frequency Range of 5–166 MHz

- Input Frequency Range

- Crystal: 10-30 MHz

- External Reference: 1–100 MHz

- Analog VCXO

- 16-/20-pin TSSOP packages

- 3.3V operation

# **Benefits**

- Meets most Digital Set Top Box, DVD Recorder and DTV application requirements

- · Multiple high-performance PLLs allow synthesis of unrelated frequencies

- · Integration eliminates the need for external loop filter components

- · Meets critical timing requirements in complex system designs

- · Enables application compatibility

- Complete VCXO solution with ±120 ppm (minimum pull range)

**Cypress Semiconductor Corporation** Document #: 38-07748 Rev. \*

3901 North First Street

San Jose, CA 95134 • 408-943-2600 Revised March 7, 2005

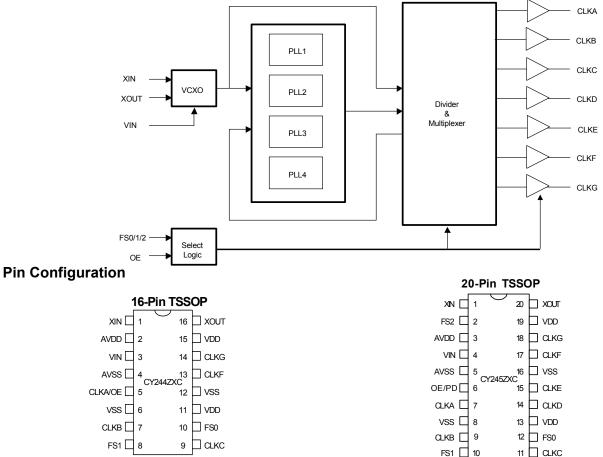

# **Block Diagram**

### **Pin Description**

|          | Pin Number       |              |                                                       |  |  |

|----------|------------------|--------------|-------------------------------------------------------|--|--|

| Pin Name | 16-pin TSSOP     | 20-pin TSSOP | Pin Description                                       |  |  |

| XIN      | 1                | 1            | Crystal Input or Reference Clock Input                |  |  |

| XOUT     | 16               | 20           | Crystal Output (No connect if external clock is used) |  |  |

| CLKA     | 5 <sup>[1]</sup> | 7            | Clock Output                                          |  |  |

| CLKB     | 7                | 9            | Clock Output                                          |  |  |

| CLKC     | 9                | 11           | Clock Output                                          |  |  |

| CLKD     | N/A              | 14           | Clock Output                                          |  |  |

| CLKE     | N/A              | 15           | Clock Output                                          |  |  |

| CLKF     | 13               | 17           | Clock Output                                          |  |  |

| CLKG     | 14               | 18           | Clock Output                                          |  |  |

| FS0      | 10               | 12           | Frequency Select 0                                    |  |  |

| FS1      | 8                | 10           | Frequency Select 1                                    |  |  |

| FS2      | N/A              | 2            | Frequency Select 2                                    |  |  |

| OE/PD    | 5 <sup>[1]</sup> | 6            | Output Enable Control/Power Down                      |  |  |

| VIN      | 3                | 4            | Analog Control Input for VCXO                         |  |  |

| VDD      | 11,15            | 13,19        | Voltage Supply                                        |  |  |

| VSS      | 6,12             | 8,16         | Ground                                                |  |  |

| AVDD     | 2                | 3            | Analog Voltage Supply                                 |  |  |

| AVSS     | 4                | 5            | Analog Ground                                         |  |  |

#### **General Description**

The CY24xZXC family of devices has an Analog VCXO (Voltage Controlled Crystal Oscillator), 4 PLLs, up to 7 clock outputs, and frequency selection capabilities. The frequency selects do not modify any PLL frequency. Instead, they allow the user to choose between up to 8 different output divider selections depending on the clock and package configuration. This is illustrated in Frequency Selection tables 1 and 2.

There is one programmable OE/PDWN. The OE/PDWN pin can be programmed as either an output enable pin or a power down pin. The OE function can be programmed to disable a selected set of outputs when low, leaving the remaining outputs running. Full chip power-down will disable all outputs as well as the PLLs and most of the active circuitry when low.

#### Factory-Programmable CY24xZXC

Factory programming is available for high or low volume manufacturing by Cypress. All requests must be submitted to the local Cypress Field Application Engineer (FAE) or sales representative. Once the request has been processed, you will receive a new part number, samples, and data sheet with the programmed values. This part number will be used for additional sample requests and production orders. Please refer to the CY223388/89/91 data sheet for up to 8 clock outputs and compatibility with most SMD type crystals.

#### PLLs

The advantage of having 4 PLLs is that a single device can generate up to 4 independent frequencies from a single

Note: 1. Pin 5 16-pin TSSOP (choice between clock output or OE/PD) crystal. Generally a design may require up to 4 oscillators to accomplish what could be done with a single CY24xZXC.

Each PLL is independent and can be configured to generate a VCO (Voltage Controlled Oscillator) frequency between 62.5 MHz and 250 MHz. Each PLL can then in turn be divided down with post dividers to generate the clock output frequency of the user's choice. The output divider allows each clock output to be divided by 1,2,3,4,6,8,9,10,12,15. The PLL maximum is reduced to 166 MHz in divide by 1 mode due to output buffer limitations.

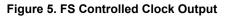

Outputs that allow frequency switching perform the transition free of glitches. A glitch is defined as a high or low time shorter than half the smaller of the two periods being switched between. Extended low time (even many cycles in duration) is acceptable. Please refer to *Figure 5*.

In order to minimize PPM (Parts Per Million) error on the clock outputs, a user should try and choose a crystal reference frequency that is a common multiple of the desired PLL frequencies. While this would be the ideal situation, this is not always the case and the PLLs have high resolution counters internally to help minimize frequency deviation from the desired frequency.

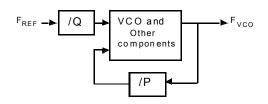

PLL VCO frequencies are generated by the following equation:  $F_{VCO} = F_{REF} * (P / Q)$

Where  $F_{REF}$  is the reference input frequency, P is the PLL feedback divider and Q is the reference input divider. A PLL is a feedback system where the VCO frequency divided by P and reference frequency divided by Q are constantly being compared and the VCO frequency is adjusted to achieve a locked state. *Figure 1* is a simplified drawing of a PLL.

Figure 1. Simplified PLL

# **Frequency Select Pin Operation**

#### Table 1. CY244ZXC 16-pin TSSOP

| Output Signal     | Frequency Selection<br>Lines |

|-------------------|------------------------------|

| CLOCK B & CLOCK C | FS1 FS0                      |

| CLOCK A & CLOCK F | FS0                          |

| CLOCK G           | FIXED                        |

#### Table 2. CY245ZXC 20-pin TSSOP

| Output Signal               | Frequency Selection<br>Lines |

|-----------------------------|------------------------------|

| CLOCK C                     | FS2 FS1 FS0                  |

| CLOCK B & CLOCK D           | FS1 FS0                      |

| CLOCK A, CLOCK E, & CLOCK F | FS0                          |

| CLOCK G                     | FIXED                        |

# Analog VCXO

There are three programmable reference operating modes for the CY24xZXC family of devices. The first mode utilizes an external pullable crystal and incorporates an internal Analog VCXO.

The second mode configures the internal crystal oscillator to accept an external driven reference source from 1 to 100 MHz. The input capacitance on the XIN pin when driven in this mode is typically 15pF.

The third mode disables the VCXO input control and sets the internal oscillator to a fixed frequency operation. The load capacitance seen by the external crystal when connected to pins XIN and XOUT is typically equal to 10pF.

One of the key components to the CY24xZXC family of devices is the analog VCXO. The VCXO is used to "pull" the reference crystal higher or lower in order to lock the system frequency to an external source. This is ideal for applications where the output frequency needs to track along with an external reference frequency that is constantly shifting.

The VCXO is completely analog, so there is infinite resolution on the VCXO pull curve. The Analog to Digital Converter steps that are normally associated with a digital VCXO input are not present in this device. A special pullable crystal must be used in order to have adequate VCXO pull range. Pullable Crystal specifications are included in this data sheet.

Please contact the local Cypress Field Application Engineer (FAE) or sales representative for pullable crystal recommendations outside of the standard industry frequencies given in the Pullable Crystal Specifications.

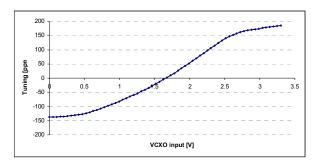

# VCXO Profile

*Figure 2* shows an example of what a VCXO profile looks like. The analog voltage input is on the X-axis and the PPM range is on the Y-axis. An increase in the VCXO input voltage results in a corresponding increase in the output frequency. This has the effect of moving the PPM from a negative to positive offset.

Figure 2. VCXO Profile

#### **Absolute Maximum Conditions**

| Parameter                                           | Description                       | Condition                   | Min. | Max.                  | Unit  |

|-----------------------------------------------------|-----------------------------------|-----------------------------|------|-----------------------|-------|

| V <sub>DD</sub> /AV <sub>DD</sub> /V <sub>DDL</sub> | Core Supply Voltage               |                             | -0.5 | 4.6                   | V     |

| V <sub>IN</sub>                                     | Input Voltage                     | Relative to V <sub>SS</sub> | -0.5 | V <sub>DD</sub> + 0.5 | VDC   |

| Τ <sub>S</sub>                                      | Temperature, Storage              | Non-Functional              | -65  | +125                  | °C    |

| ESD <sub>HBM</sub>                                  | ESD Protection (Human Body Model) | MIL-STD-883, Method 3015    | 2000 | -                     | Volts |

| UL-94                                               | Flammability Rating               | V-0 @1/8 in.                | -    | 10                    | ppm   |

| MSL                                                 | Moisture Sensitivity Level        |                             |      | •                     |       |

|                                                     |                                   | 16 and 20 pin TSSOP         |      | 1                     |       |

# Pullable Crystal Specifications<sup>[2, 4]</sup>

| Parameter                          | Description                                       | Comments                                            | Min. | Тур.     | Max. | Unit |

|------------------------------------|---------------------------------------------------|-----------------------------------------------------|------|----------|------|------|

| F <sub>NOM</sub>                   | 10 to 30 MHz Crystal AT-Cut                       | Parallel resonance, Fundamental mode                | 5    | See Note | 4    |      |

| C <sub>LNOM</sub>                  | Nominal load capacitance                          | C <sub>LNOM</sub> =14 pF (0 ppm)                    | 13.5 | 14       | 14.5 | pF   |

| R <sub>1</sub>                     | Equivalent series resistance (ESR)                | Fundamental mode (CL = Series)                      | -    | -        | 25   | Ω    |

| DL                                 | Crystal drive level                               | No external series resistor assumed                 | -    | -        | 500  | μW   |

| C <sub>0</sub> <sup>[3]</sup>      | Crystal shunt capacitance                         |                                                     | —    | -        | 7    | pF   |

| C <sub>1</sub> <sup>[3]</sup>      | Crystal motional capacitance                      |                                                     | 14.4 | 18       | 21.6 | fF   |

| F <sub>3SEPHI</sub> <sup>[4]</sup> | Third overtone separation from 3*F <sub>NOM</sub> | Mechanical Third (High side of 3*F <sub>NOM</sub> ) | 380  | -        | -    | ppm  |

| F <sub>3SEPLO</sub> <sup>[4]</sup> | Third overtone separation from 3*F <sub>NOM</sub> | Mechanical Third (Low side of 3*F <sub>NOM</sub> )  | —    | -        | -170 | ppm  |

| C <sub>0</sub> /C <sub>1</sub>     | Ratio of shunt to motional capacitance            |                                                     | -    | -        | 250  |      |

#### **Recommended Operating Conditions**

| Parameter                                           | Description                                                                                      | Min. | Тур. | Max. | Unit |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>DD</sub> /AV <sub>DD</sub> /V <sub>DDL</sub> | Operating Voltage                                                                                | 3.0  | 3.3  | 3.6  | V    |

| T <sub>A</sub>                                      | Ambient Temperature                                                                              | 0    | _    | 70   | °C   |

| C <sub>LOAD</sub>                                   | Maximum Load Capacitance                                                                         | -    | _    | 15   | pF   |

|                                                     | Power-up time for all $V_{DD}$ s reach minimum specified voltage (power ramps must be monotonic) | 0.05 | _    | 500  | ms   |

## **DC** Parameters

| Parameter                      | Description              | Conditions                                                      | Min.                   | Тур. | Max.                 | Unit |

|--------------------------------|--------------------------|-----------------------------------------------------------------|------------------------|------|----------------------|------|

| I <sub>OH</sub> <sup>[5]</sup> | Output High Current      | V <sub>OH</sub> = V <sub>DD</sub> – 0.5, V <sub>DD</sub> = 3.3V | -                      | 12   | -                    | mA   |

| I <sub>OL</sub> <sup>[5]</sup> | Output Low Current       | V <sub>OL</sub> = 0.5, V <sub>DD</sub> = 3.3V                   | -                      | 12   | -                    | mA   |

| I <sub>IH</sub>                | Input High Current       | $V_{IH} = V_{DD}$ , excluding Vin, Xin                          | -                      | 5    | 10                   | μA   |

| IIL                            | Input Low Current        | V <sub>IL</sub> = 0V, excluding Vin, Xin                        | -                      | 5    | 10                   | μA   |

| V <sub>IH</sub>                | Input High Voltage       | FS0/1/2 OE input CMOS levels                                    | 0.7xA <sub>VDD</sub> - |      | -                    | V    |

| V <sub>IL</sub>                | Input Low Voltage        | FS0/1/2 OE input CMOS levels                                    |                        |      | 0.3xA <sub>VDD</sub> | V    |

| V <sub>VCXO</sub>              | VIN Input Range          |                                                                 | 0                      | _    | A <sub>VDD</sub>     | V    |

| C <sub>IN</sub>                | Input Capacitance        | FS0/1/2 and OE Pins only                                        | -                      | _    | 7                    | pF   |

| I <sub>VDD</sub>               | Supply Current           | V <sub>DD</sub> /AV <sub>DD</sub> /V <sub>DDL</sub> Current     | - 85                   |      | -                    | mA   |

| C <sub>INXIN</sub>             | Input Capacitance at XIN | VCXO Disabled External Reference                                | -                      | 15   | -                    | pF   |

| Crystal Load                   | Crystal Load Capacitance | VCXO Disabled Fixed Freq. Crystal                               | _                      | 10   | _                    | pF   |

Notes:

2. Device operates to the following specs, which are guaranteed by design.

Increased tolerance available from pull range less than ±120 ppm.

ECX-5953 Series crystal orderable from Ecliptek Corporation. Please refer to the CY22388/89/91 data sheet for compatibility with most SMD type crystals.

Parameters are guaranteed by design and characterization. Not 100% tested in production. All parameters specified with fully loaded outputs.

# **AC Parameters**

| Parameter <sup>[4]</sup>      | Description                    | Conditions                                                                                                                                                                                       | Min. | Тур. | Max. | Units |

|-------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| 1/t1                          | Output Frequency               | PLL <sub>minmax</sub> /Divider <sub>maximum</sub>                                                                                                                                                | 4.2  | —    | 166  | MHz   |

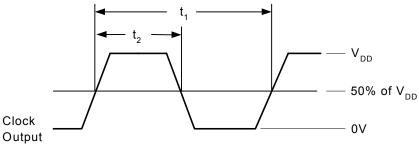

| DC1 <sup>[6]</sup>            | Output Duty Cycle              | Duty Cycle is defined in <i>Figure</i> 3; $t_2/t_1$ , 50% of V <sub>DD</sub><br>External reference duty cycle between 40% and 60% measured at V <sub>DD</sub> /2 (Clock output is $\leq$ 125MHz) | 45   | 50   | 55   | %     |

| DC2                           | Output Duty Cycle              | Duty Cycle is defined in <i>Figure</i> 3; $t_2/t_1$ , 50% of V <sub>DD</sub><br>External reference duty cycle between 40% and 60% measured at V <sub>DD</sub> /2 (Clock output is > 125MHz)      | 40   | 50   | 60   | %     |

| DC <sub>REFOUT</sub>          | Reference Output Duty<br>Cycle | Duty Cycle is defined in <i>Figure 3</i> ; t <sub>2</sub> /t <sub>1</sub> , 50% of V <sub>DD</sub><br>(XIN Duty Cycle = 45/55%)                                                                  | 40   | 50   | 60   | %     |

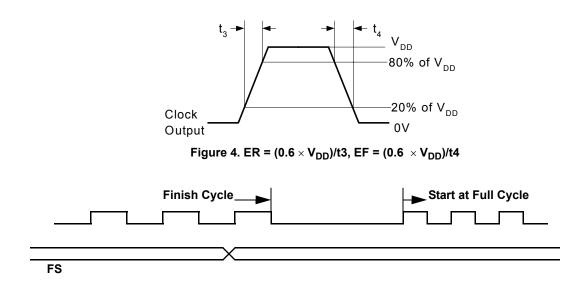

| ER                            | Rising Edge Rate               | Output Clock Edge Rate. Measured from 20% to 80% of $V_{DD}$ . $C_{LOAD}$ = 15 pF. See <i>Figure 4</i> .                                                                                         |      | 1.2  | _    | V/ns  |

| EF                            | Falling Edge Rate              | Output Clock Edge Rate. Measured from 80% to 20% of $V_{DD}$ . $C_{LOAD}$ = 15pF See <i>Figure 4</i> .                                                                                           |      | 1.2  | _    | V/ns  |

| Т <sub>9</sub> <sup>[7]</sup> | Clock Jitter                   | Period Jitter                                                                                                                                                                                    |      | ±250 | -    | ps    |

| T <sub>10</sub>               | PLL Lock Time                  |                                                                                                                                                                                                  |      | 1    | 5    | ms    |

| $f_{\Delta XO}$               | VCXO Crystal Pull<br>Range     | Using Crystal specified in "Pullable Crystal Specifications" table.<br>Nominal Crystal Frequency Input assumed (0ppm)@25°C and 3.3V                                                              | ±120 | -    | -    | ppm   |

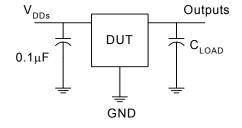

# **Test and Measurement Set-up**

# **Voltage and Timing Definitions**

Figure 3. Duty Cycle Definition

#### Note:

6. Excluding any output configured as a reference.

7. Jitter measurement will vary. Actually jitter is dependent on XIN jitter and edge rate, number of active outputs, output frequencies, and device programming.

# **Ordering Information**

| Part Number <sup>[8]</sup> | Туре                         | Production Flow          |

|----------------------------|------------------------------|--------------------------|

| Lead-free                  |                              |                          |

| CY244ZXC-XXX               | 16-pin TSSOP                 | Commercial, 0°C to +70°C |

| CY244ZXC-XXXT              | 16-pin TSSOP - Tape and Reel | Commercial, 0°C to +70°C |

| CY245ZXC-XXX               | 20-pin TSSOP                 | Commercial, 0°C to +70°C |

| CY245ZXC-XXXT              | 20-pin TSSOP - Tape and Reel | Commercial, 0°C to +70°C |

#### Note:

8. The CY244ZXC-xxx, CY245ZXC-xxx are factory programmed configurations. For more details, contact your local Cypress FAE or Cypress Sales Representative.

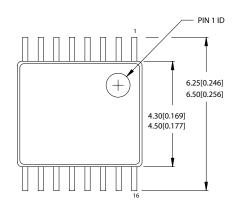

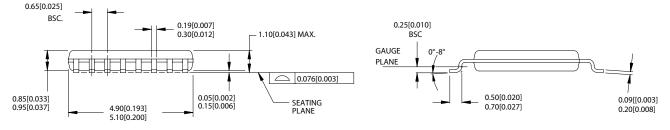

# **Package Drawing and Dimensions**

#### 16-lead TSSOP 4.40 mm Body Z16.173

DIMENSIONS IN MM[INCHES] MIN. MAX.

**REFERENCE JEDEC MO-153**

PACKAGE WEIGHT 0.05 gms

| PART #   |                |  |

|----------|----------------|--|

| Z16.173  | STANDARD PKG.  |  |

| ZZ16.173 | LEAD FREE PKG. |  |

51-85091-\*A

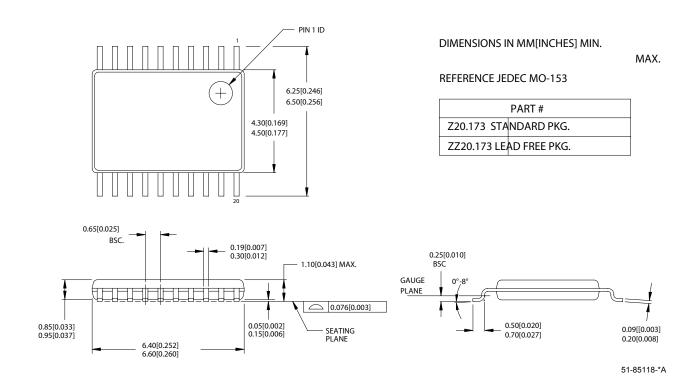

#### Package Drawing and Dimensions (continued)

#### 20-Lead Thin Shrunk Small Outline Package (4.40-mm Body) Z20

All product and company names mentioned in this document are trademarks of their respective holder.

© Cypress Semiconductor Corporation, 2005. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in fife-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges. Downloaded from Elecodis.com electronic components distributor

# Document History Page

| Document Title: CY244/45ZXC Factory Programmable Quad PLL Clock Generator with VCXO<br>Document Number: 38-07748 |         |            |                    |                       |  |  |

|------------------------------------------------------------------------------------------------------------------|---------|------------|--------------------|-----------------------|--|--|

| REV.                                                                                                             | ECN NO. | Issue Date | Orig. of<br>Change | Description of Change |  |  |

| **                                                                                                               | 330814  | See ECN    | RGL                | New data sheet        |  |  |