This document contains information on a product under development. The parametric information contains target parameters that are subject to change.

# CN8478/CN8474A/CN8472A/CN8471A

# Multichannel Synchronous Communications Controller (MUSYCC<sup>TM</sup>)

### Product Description

The CN8478, CN8474A, CN8472A, and CN8471A are advanced Multichannel Synchronous Communication Controllers (MUSYCCs) that format and deformat up to 256 (CN8478), 128 (CN8474A), 64 (CN8472A), or 32 (CN8471A) HDLC channels in a single CMOS integrated circuit. MUSYCC operates at Layer 2 of the Open Systems Interconnection (OSI) protocol reference model, MUSYCC provides a comprehensive, high-density solution for processing HDLC channels for internetworking applications such as Frame Relay, ISDN D-channel signaling. X.25, Signaling System 7 (SS7), DXI, ISUP, and LAN/WAN data transport. Under minimal host supervision, MUSYCC manages a linked list of channel data buffers in host memory by performing Direct Memory Access (DMA) of the HDLC channels.

MUSYCC interfaces with eight independent serial data streams, such as T1/E1 signals, and then transfers data across the popular 32-bit Peripheral Component Interface (PCI) bus to system memory at a rate of up to 66 MHz. Each serial interface can be operated at up to 8.192 MHz. Logical channels can be mapped as any combination of DS0 time slots to support ISDN hyperchannels (Nx64 kbps) or as any number of bits in a DS0 for subchanneling applications (Nx8 kbps). MUSYCC also includes a 32-bit expansion port for bridging the PCI bus to local microprocessors or peripherals. A JTAG port enables boundary-scan testing to replace bed-of-nails board testing.

Device drivers for Linux, VxWorks<sup>®</sup>, and pSOS<sup>™</sup> operating systems are available under a no-fee license agreement from Conexant. The device drivers include C source code and supporting software documents.

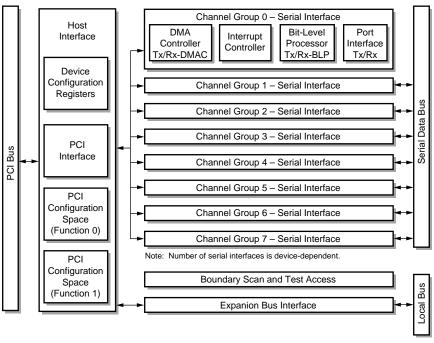

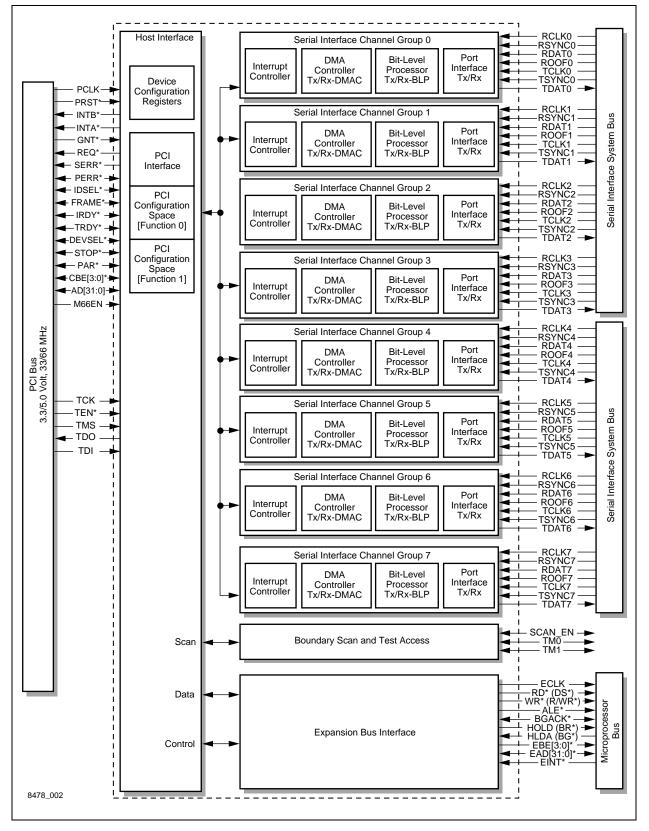

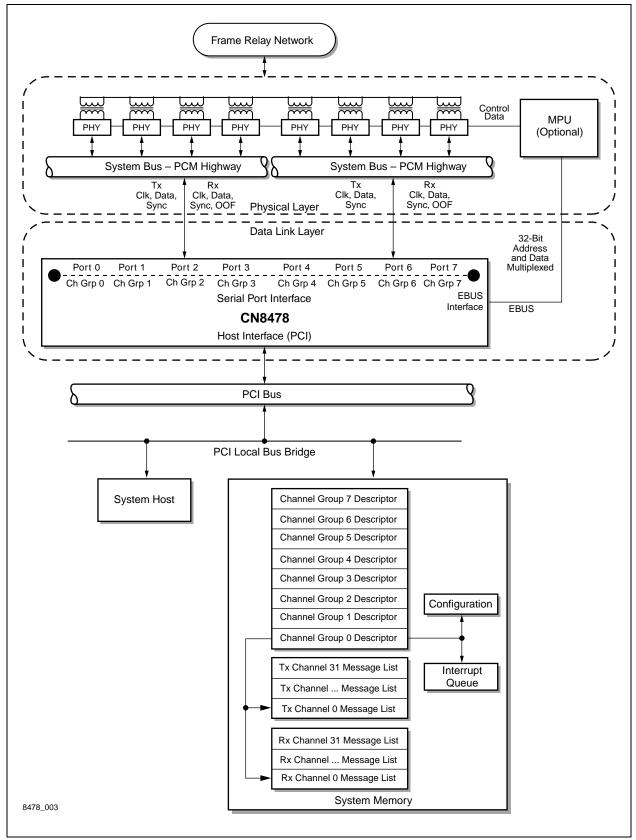

# **Functional Block Diagram**

### **Distinguishing Features**

- 256-, 128-, 64-, or 32-channel HDLC controller

- OSI Layer 2 protocol support

- General purpose HDLC (ISO 3309)

- X.25 (LAPB)

- Frame relay (LAPF/ANSI T1.618)

- ISDN D-channel (LAPD/Q.921)

- SS7 support

- 8, 4, 2, or 1 independent serial interfaces • which support

- T1/E1 data streams \_

- DC to 8.192 Mbps TDM busses

- Configurable logical channels

- Standard DS0 (56, 64 kbps)

- \_ Hyperchannel (Nx64)

- Subchannel (Nx8)

- Per-channel protocol mode selection ٠

- 16-bit FCS mode

- \_ 32-bit FCS mode

- SS7 mode (16-bit FCS) \_

- Transparent mode (unformatted data) \_

- Per-channel DMA buffer management Linked list data structures

- Variable size transmit/receive FIFO Per-channel message length check

- Select no length checking

- Select from two 12-bit registers to \_ compare message length

- Maximum length 16,384 Bytes

- Direct PCI bus interface

- 32-bit. 66 or 33 MHz operation

- Bus master and slave operation

- PCI Version 2.1

- Local Expansion Bus interface (EBUS)

- 32-bit multiplexed address/data bus Burst access up to 64 Bytes

- Low power, 3.3/2.5 V CMOS operation

- JTAG boundary scan access port

- 208-pin PQFP/surface-mount package •

- BGA

- Applications

- ISDN basic-rate or primary-rate interfaces

- ISDN D-channel controller

- Routers

•

- Cellular base station switch controller •

- CSU/DSU •

- Protocol converter

- Packet data switch

- Frame relay switches/Frame Relay Access . Devices (FRAD)

- DXI network interface •

- Distributed packet-based communications system

- Access multiplexer/concentrator

#### Conexant

# **Ordering Information**

| Model Number | Version     | Package                               | Temperature Range |

|--------------|-------------|---------------------------------------|-------------------|

| CN8471AEPF   | 32-Channel  | 208-Pin Plastic Quad Flat Pack (PQFP) | –40 °C to +85 °C  |

| CN8472AEPF   | 64-Channel  | 208-Pin Plastic Quad Flat Pack (PQFP) | –40 °C to +85 °C  |

| CN8474AEPF   | 128-Channel | 208-Pin Plastic Quad Flat Pack (PQFP) | –40 °C to +85 °C  |

| CN8478EPF    | 256-Channel | 208-Pin Plastic Quad Flat Pack (PQFP) | –40 °C to +85 °C  |

| CN8471AEBG   | 32-Channel  | 208-Pin Plastic Ball Grid Array       | –40 °C to +85 °C  |

| CN8472AEBG   | 64-Channel  | 208-Pin Plastic Ball Grid Array       | –40 °C to +85 °C  |

| CN8474AEBG   | 128-Channel | 208-Pin Plastic Ball Grid Array       | –40 °C to +85 °C  |

| CN8478EBG    | 256-Channel | 208-Pin Plastic Ball Grid Array       | –40 °C to +85 °C  |

© 2000, Conexant Systems, Inc. All Rights Reserved.

Information in this document is provided in connection with Conexant Systems, Inc. ("Conexant") products. These materials are provided by Conexant as a service to its customers and may be used for informational purposes only. Conexant assumes no responsibility for errors or omissions in these materials. Conexant may make changes to specifications and product descriptions at any time, without notice. Conexant makes no commitment to update the information and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to its specifications and product descriptions.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Conexant's Terms and Conditions of Sale for such products, Conexant assumes no liability whatsoever.

THESE MATERIALS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF CONEXANT PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, CONSEQUENTIAL OR INCIDENTAL DAMAGES, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. CONEXANT FURTHER DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. CONEXANT SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS, WHICH MAY RESULT FROM THE USE OF THESE MATERIALS.

Conexant products are not intended for use in medical, lifesaving or life sustaining applications. Conexant customers using or selling Conexant products for use in such applications do so at their own risk and agree to fully indemnify Conexant for any damages resulting from such improper use or sale.

The following are trademarks of Conexant Systems, Inc.: Conexant<sup>TM</sup>, the Conexant C symbol, and "What's Next in Communications Technologies"<sup>TM</sup>. Product names or services listed in this publication are for identification purposes only, and may be trademarks of third parties. Third-party brands and names are the property of their respective owners.

For additional disclaimer information, please consult Conexant's Legal Information posted at www.conexant.com, which is incorporated by reference.

**Reader Response:** Conexant strives to produce quality documentation and welcomes your feedback. Please send comments and suggestions to tech.pubs@conexant.com. For technical questions, contact your local Conexant sales office or field applications engineer.

#### 100660E

# **Table of Contents**

|     | List | of Figu   | Ires                                                | ix   |

|-----|------|-----------|-----------------------------------------------------|------|

|     | List | of Table  | es                                                  | xi   |

| 1.0 | Syst | tem Des   | scription                                           | 1-1  |

|     | 1.1  | Pin Des   | scriptions                                          | 1-5  |

| 2.0 | Hos  | t Interfa | ace                                                 | 2-1  |

|     | 2.1  | PCI Inte  | erface                                              | 2-2  |

|     |      | 2.1.1     | PCI Initialization                                  |      |

|     |      | 2.1.2     | PCI Bus Operations                                  |      |

|     |      | 2.1.3     | PCI Configuration Space.                            |      |

|     | 2.2  | PCI Cor   | nfiguration Registers                               |      |

|     |      | 2.2.1     | Function 0 Network Controller—PCI Master and Slave. |      |

|     |      | 2.2.2     | Function 1 Expansion Bus Bridge, PCI Slave          |      |

|     |      | 2.2.3     | PCI Reset.                                          |      |

|     |      | 2.2.4     | Host Interface                                      |      |

|     |      | 2.2.5     | PCI Bus Parity                                      | 2-18 |

|     |      | 2.2.6     | PCI Throughput and Latency Considerations           | 2-18 |

|     |      |           | 2.2.6.1 PCI Bus Latency                             | 2-19 |

|     |      |           | 2.2.6.2 Latency Computation—Single Dword Access     | 2-21 |

|     |      |           | 2.2.6.3 Latency Computation—Burst Access            | 2-22 |

| 3.0 | Expa | ansion E  | Bus (EBUS)                                          | 3-1  |

|     | 3.1  | Operati   | ion                                                 | 3-2  |

|     |      | 3.1.1     | Initialization                                      |      |

|     |      | 3.1.2     | Address and Data                                    |      |

|     |      | 3.1.3     | Clock                                               |      |

|     |      | 3.1.4     | Interrupt                                           | 3-4  |

|     |      | 3.1.5     | Address Duration                                    |      |

|     |      | 3.1.6     | Data Duration                                       | 3-4  |

|     |      | 3.1.7     | Bus Access Interval                                 | 3-5  |

|     |      | 3.1.8     | PCI to EBUS Interaction                             | 3-5  |

|     |      | 3.1.9     | Microprocessor Interface                            | 3-6  |

|     |      | 3.1.10    | Arbitration                                         | 3-7  |

|     |      | 3.1.11    | Connection                                          | 3-8  |

Downloaded from  $\underline{Elcodis.com}$  electronic components distributor

| 4.0 | Seri | al Inter | face               |                                              |

|-----|------|----------|--------------------|----------------------------------------------|

|     | 4.1  | Serial I | Port Interfa       | <b>ce</b>                                    |

|     | 4.2  | Bit Lev  | el Processo        | r                                            |

|     | 4.3  | DMA Co   | ontroller          |                                              |

|     | 4.4  | Interru  | pt Controlle       | r                                            |

|     | 4.5  | Channe   | lized Port I       | Aode                                         |

|     |      | 4.5.1    |                    | nnels (Nx64)                                 |

|     |      | 4.5.2    |                    | els (Nx8)                                    |

|     |      | 4.5.3    |                    | nchronization Flywheel                       |

|     |      | 4.5.4    | -                  | f-Frame Alignment                            |

|     |      | 4.5.5    |                    | 1me                                          |

|     | 4.6  | Serial I | Port Mappin        | ıg 4-9                                       |

|     | 4.7  | Tx and   | Rx FIFO Bu         | ffer Allocation and Management    4-11       |

|     |      | 4.7.1    |                    | Channel BUFFLOC and BUFFLEN Specification    |

|     |      | 4.7.2    |                    | Bit Stream                                   |

|     |      | 4.7.3    |                    | ng Bit Stream                                |

|     |      |          | 4.7.3.1            | Transmit Data Bit Output Value Determination |

| 5.0 | Men  | nory Or  | ganizatio          | 1                                            |

|     | 5.1  | Memor    | y Architecti       | ıre                                          |

|     |      | 5.1.1    | Register M         | Map Access and Shared Memory Access    5-3   |

|     |      | 5.1.2    | Memory A           | Access Illustration                          |

|     | 5.2  | Descrip  | otors              |                                              |

|     |      | 5.2.1    | Host Inter         | face Level Descriptors                       |

|     |      |          | 5.2.1.1            | Global Configuration Descriptor              |

|     |      |          | 5.2.1.2            | Dual Address Cycle Base Pointer    5-12      |

|     |      | 5.2.2    |                    | roup Level Descriptors                       |

|     |      |          | 5.2.2.1            | Group Base Pointer                           |

|     |      |          | 5.2.2.2            | Service Request                              |

|     |      |          | 5.2.2.3            | Group Configuration Descriptor               |

|     |      |          | 5.2.2.4            | Memory Protection Descriptor                 |

|     |      |          | 5.2.2.5<br>5.2.2.6 | Port Configuration Descriptor                |

|     |      |          | 5.2.2.0            | Time Slot Map                                |

|     |      |          | 5.2.2.7            | Subchannel Map                               |

|     |      | 5.2.3    |                    | evel Descriptors                             |

|     |      | 0.2.0    | 5.2.3.1            | Channel Configuration Descriptor             |

|     |      | 5.2.4    |                    | Level Descriptor                             |

|     |      |          | 5.2.4.1            | Using Message Descriptors                    |

|     |      |          | 5.2.4.2            | Note for Interrupt Driven Drivers            |

|     |      |          | 5.2.4.3            | Head Pointer                                 |

|     |      |          | 5.2.4.4            | Message Pointer                              |

|     |      |          | 5.2.4.5            | Message Descriptor                           |

|     |      |          | 5.2.4.6            | Buffer Descriptor                            |

|     |      | 5.2.5                                                                                                                                     | 5.2.4.7Buffer Status Descriptor5-345.2.4.8Next Message Pointer5-375.2.4.9Data Buffer Pointer5-375.2.4.10Message Descriptor Handling5-37Interrupt Level Descriptors5-385.2.5.1Interrupt Queue Descriptor5-385.2.5.2Interrupt Descriptor5-395.2.5.3Interrupt Status Descriptor5-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |      | 5.2.6                                                                                                                                     | 5.2.5.3       Interrupt Status Descriptor       5-44         Interrupt Handling       5-45         5.2.6.1       Initialization       5-45         5.2.6.2       Interrupt Descriptor Generation       5-45         5.2.6.3       INTA* Signal Line       5-46         5.2.6.4       INTB* Signal Line       5-46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6.0 | Basi | i <mark>c Oper</mark> a                                                                                                                   | tion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | 6.1  | <b>Reset</b> .<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4                                                                                        | Hard PCI Reset       6-1         Soft Chip Reset       6-2         Soft Group Reset       6-3         Initialization Sequence Example       6-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     | 6.2  | Configu                                                                                                                                   | ration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |      | 6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6                                                                                        | PCI Configuration.6-4Global Configuration.6-5Interrupt Queue Configuration.6-5Channel Group(s) Configuration6-5Service Request Mechanism.6-5MUSYCC Internal Memory6-66.2.6.1Memory Operations—Inactive Channels6-66.2.6.2Memory Operations—Active Channels6-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     | 6.3  |                                                                                                                                           | l Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |      | 6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.3.5<br>6.3.6<br>6.3.7<br>6.3.8<br>6.3.9<br>6.3.10<br>6.3.11<br>6.3.12<br>6.3.13<br>6.3.14<br>6.3.15 | Group Structure6-8Group Base Pointer6-10Global Configuration Descriptor6-11Interrupt Queue Descriptor6-12Group Configuration Descriptor6-13Memory Protection Descriptor6-14Port Configuration Descriptor6-14Message Length Descriptor6-15Transmit Time Slot Map6-16Transmit Subchannel Map6-16Transmit Channel Configuration Descriptor6-19Receive Subchannel Map6-19Receive Channel Configuration Descriptor6-19Receive Channel Configuration Descriptor6-19 |

|     |      | 6.3.14<br>6.3.15                                                                                                                          | Receive Channel Configuration Descriptor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     | 6.3.16  | Channel Activation                             | -21 |

|-----|---------|------------------------------------------------|-----|

|     |         | 6.3.16.1 Transmit Channel Activation           | -21 |

|     |         | 6.3.16.2 Receive Channel Activation            | -22 |

|     | 6.3.17  | Channel Deactivation                           | -23 |

|     |         | 6.3.17.1 Transmit Channel Deactivation         | -23 |

|     |         | 6.3.17.2 Receive Channel Deactivation          | -23 |

|     | 6.3.18  | Channel Jump                                   |     |

|     | 6.3.19  | Frame Alignment                                |     |

|     | 6.3.20  | Descriptor Polling                             |     |

|     | 6.3.21  | Repeat Message Transmission                    | -26 |

| 6.4 | Protoco | I Support                                      | -28 |

|     | 6.4.1   | Frame Check Sequence                           | -28 |

|     | 6.4.2   | Opening/Closing Flags                          | -28 |

|     | 6.4.3   | Abort Codes                                    | -28 |

|     | 6.4.4   | Zero-Bit Insertion/Deletion                    | -29 |

|     | 6.4.5   | Message Configuration Bits                     | -29 |

|     |         | 6.4.5.1 Idle Code                              | -29 |

|     |         | 6.4.5.2 Inter-message Pad Fill                 | -29 |

|     |         | 6.4.5.3 Repeat Message Transmission            |     |

|     | 6.4.6   | Message Configuration Bits Copy Enable/Disable |     |

|     | 6.4.7   | Bit-Level Operation                            |     |

|     |         | 6.4.7.1 Transmit                               |     |

|     |         | 6.4.7.2 Receive                                |     |

|     | 6.4.8   | HDLC Mode                                      |     |

|     |         | 6.4.8.1 Transmit Events                        |     |

|     |         | 6.4.8.2 Receive Events                         |     |

|     |         | 6.4.8.3 Transmit Errors                        |     |

|     |         | 6.4.8.4 Receive Errors                         |     |

|     | 6.4.9   | Transparent Mode                               |     |

|     |         | 6.4.9.1 Transmit Events                        |     |

|     |         | 6.4.9.2 Receive Events                         |     |

|     |         | 6.4.9.3 Transmit Errors                        |     |

|     | 6.4.10  | 6.4.9.4 Receive Errors                         |     |

|     |         |                                                |     |

| 6.5 | -       |                                                | -49 |

|     | 6.5.1   | SS7 Repeat Message Transmission                |     |

|     | 6.5.2   | Message Filtering                              |     |

|     | 6.5.3   | Signal Unit Error Rate Monitoring              |     |

|     | 6.5.4   | SUERM Counter Incrementing                     |     |

|     | 6.5.5   | SUERM Octet Counting                           |     |

|     | 6.5.6   | SUERM Counter Decrementing                     | -50 |

| 6.6 | Self-Se | rvicing Buffers                                | -51 |

vi

| 7.0   | Elec   | trical a       | nd Mechanical Specifications                                                          |

|-------|--------|----------------|---------------------------------------------------------------------------------------|

|       | 7.1    | Electric       | al and Environmental Specifications                                                   |

|       |        | 7.1.1          | Absolute Maximum Ratings                                                              |

|       |        | 7.1.2          | Recommended Operating Conditions                                                      |

|       |        | 7.1.3          | Electrical Characteristics                                                            |

|       | 7.2    | Timing         | and Switching Specifications. 7-3                                                     |

|       |        | 7.2.1          | Overview                                                                              |

|       |        | 7.2.2          | Host Interface (PCI) Timing and Switching Characteristic                              |

|       |        | 7.2.3          | Expansion Bus (EBUS) Timing and Switching Characteristic                              |

|       |        | 7.2.4          | EBUS Arbitration Timing                                                               |

|       |        | 7.2.5          | Serial Interface Timing and Switching Characteristics                                 |

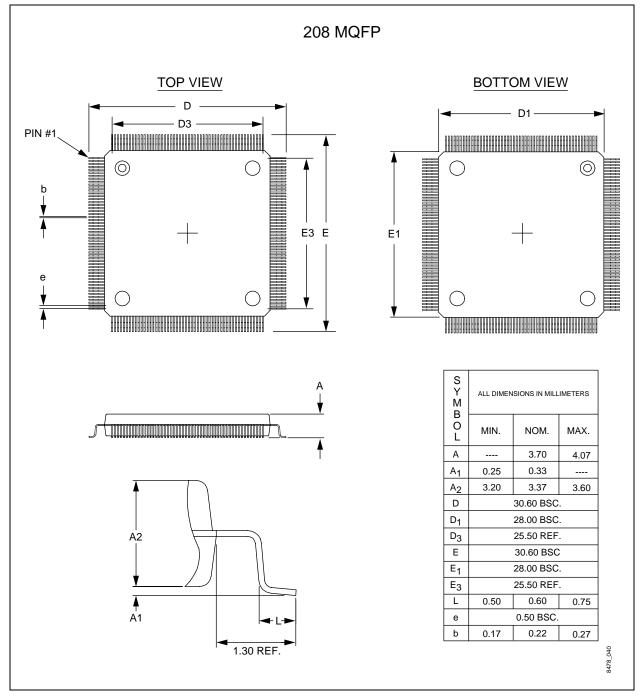

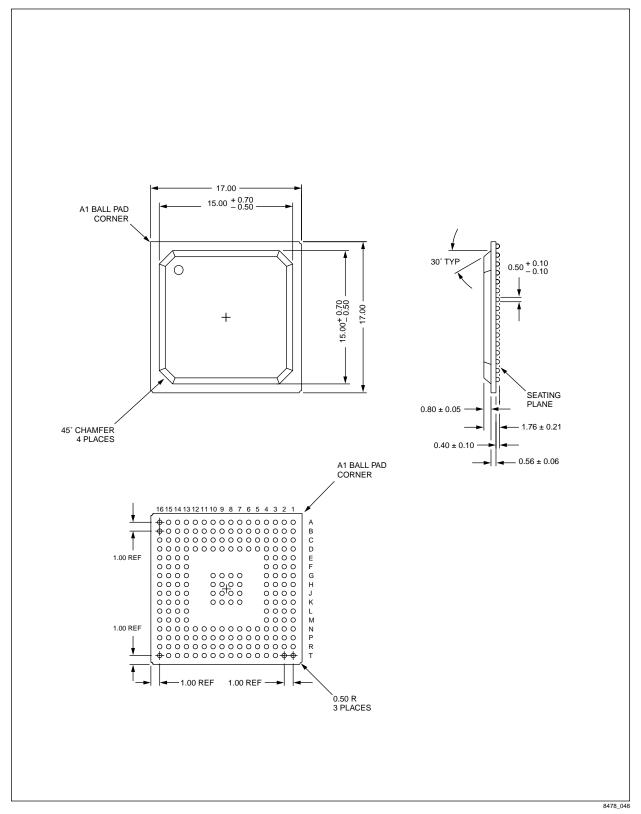

|       |        | 7.2.6<br>7.2.7 | Package Thermal Specification       7-18         Mechanical Specifications       7-19 |

|       |        | 1.2.1          |                                                                                       |

| 8.0   | Tern   | ns, Defi       | nitions, and Conventions                                                              |

|       | 8.1    | Applica        | ible Specifications                                                                   |

|       | 8.2    | Numer          | ic Notation                                                                           |

|       | 8.3    | Bit Stre       | am Transmission Convention                                                            |

|       | 8.4    | Bit Stre       | am Storage Convention                                                                 |

|       | 8.5    | Acrony         | ms                                                                                    |

|       | 8.6    | Definit        | ions                                                                                  |

|       | 8.7    | Revisio        | on History                                                                            |

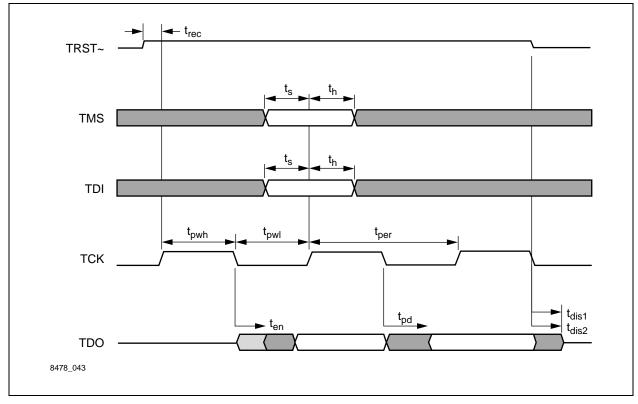

| Apper | ndix A | JTAG II        | nterface A-1                                                                          |

|       | A.1    | Instruc        | tion Register                                                                         |

|       | A.2    | BYPAS          | S Register A-2                                                                        |

Downloaded from Elcodis.com electronic components distributor

# **List of Figures**

| Figure 1-1.  | System Block Diagram                                              | . 1-1 |

|--------------|-------------------------------------------------------------------|-------|

| Figure 1-2.  | Detailed System Block Diagram                                     | . 1-3 |

| Figure 1-3.  | MUSYCC Application Example—Frame Relay Switch                     | . 1-4 |

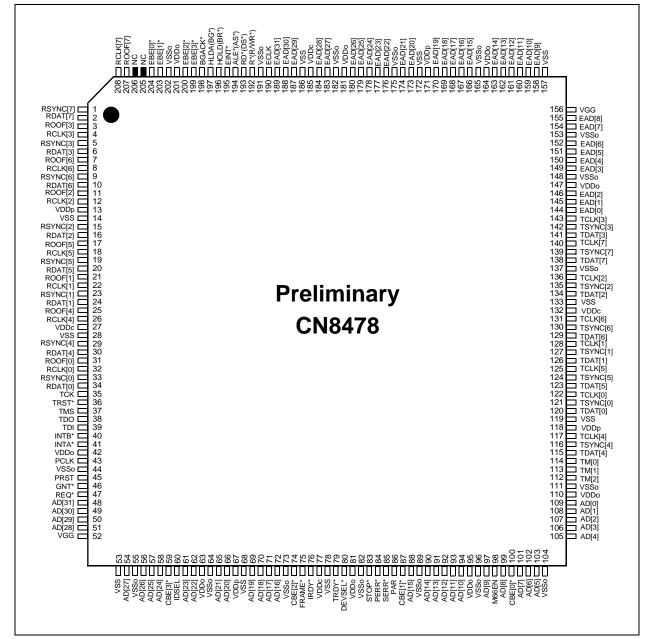

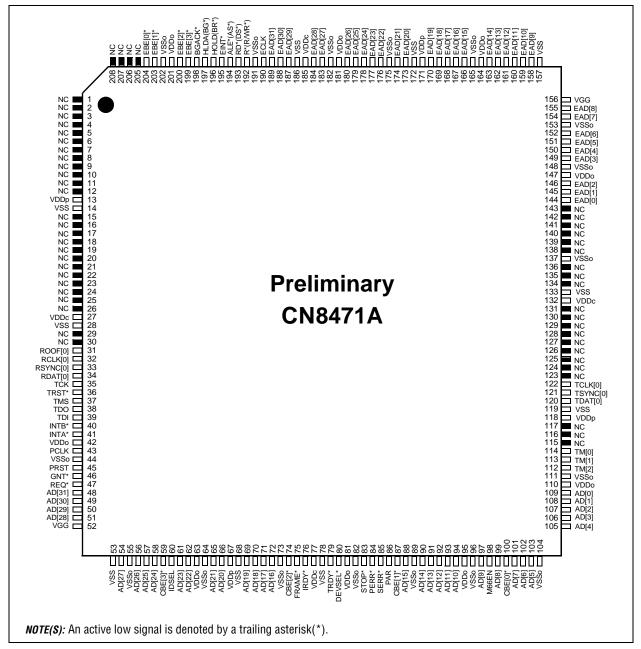

| Figure 1-4.  | CN8478 MQFP Pinout Configuration                                  | . 1-5 |

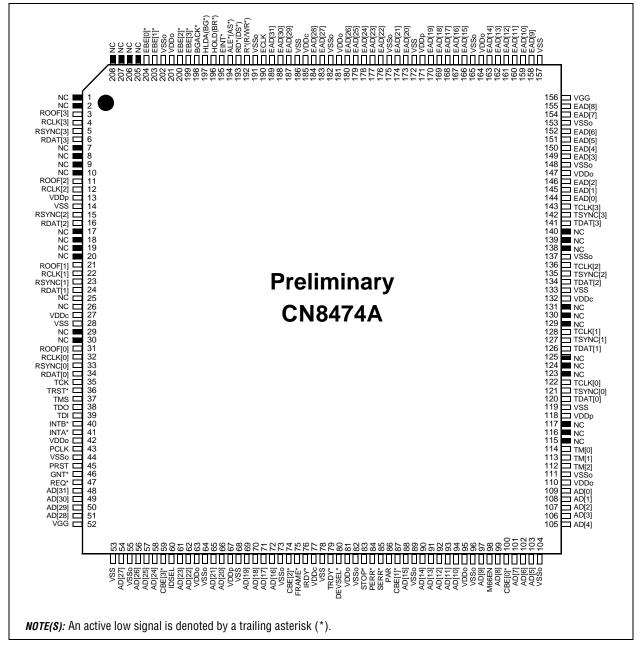

| Figure 1-5.  | CN8474A MPQF Pinout Configuration                                 | . 1-8 |

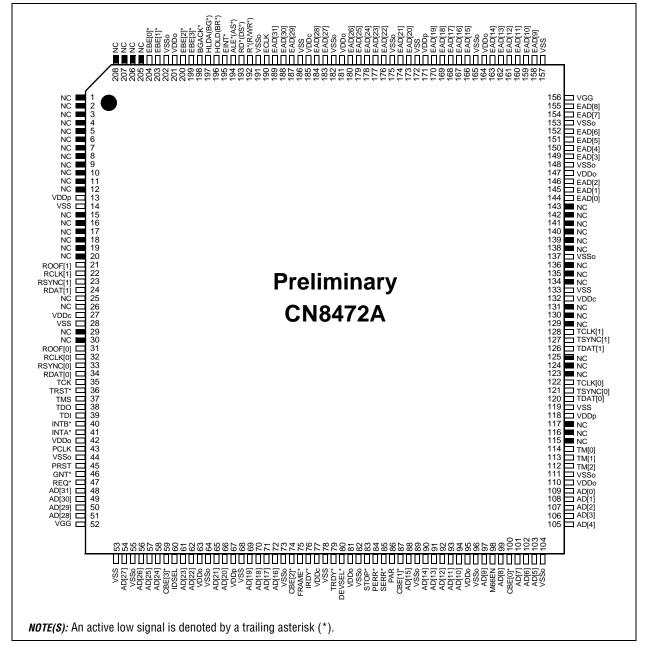

| Figure 1-6.  | CN8472A MQFP Pinout Configuration                                 | . 1-9 |

| Figure 1-7.  | CN8471A MQFP Pinout Configuration                                 | 1-10  |

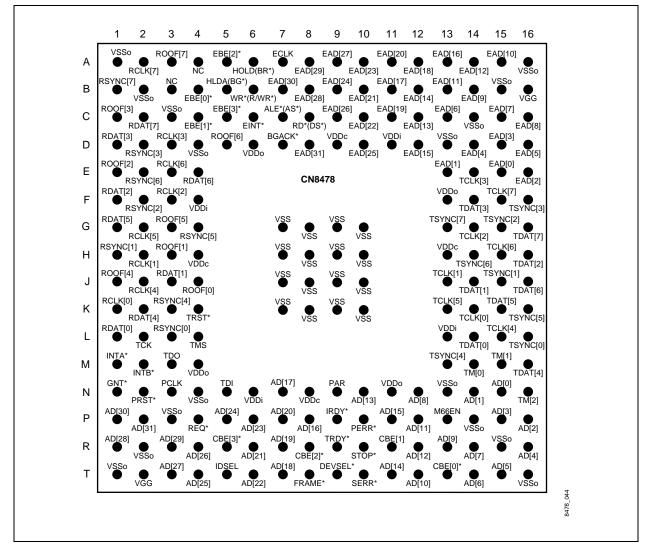

| Figure 1-8.  | CN8478 PBGA Pinout Configuration (Top View)                       | 1-11  |

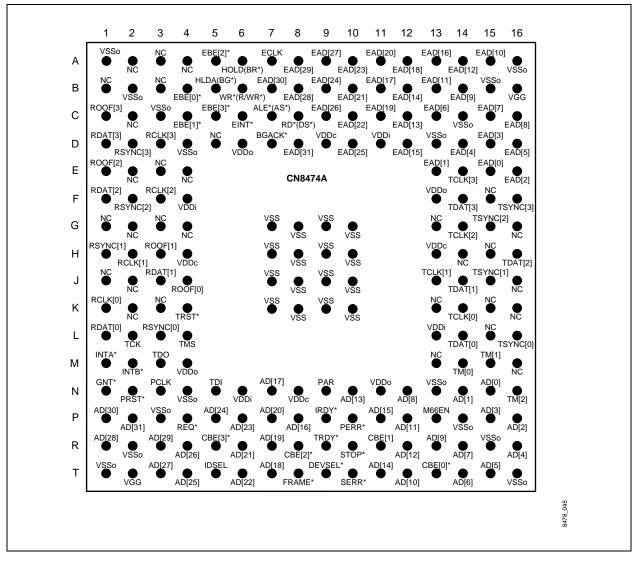

| Figure 1-9.  | CN8474A PBGA Pinout Configuration (Top View)                      | 1-14  |

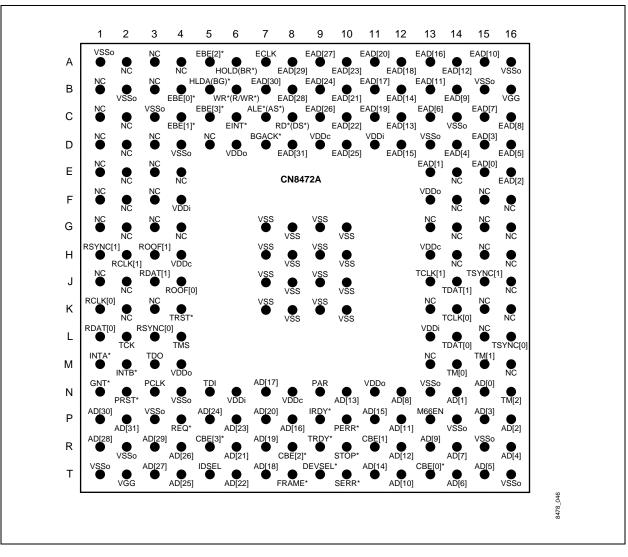

| Figure 1-10. | CN8472A PBGA Pinout Configuration (Top View)                      | 1-15  |

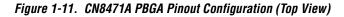

| Figure 1-11. | CN8471A PBGA Pinout Configuration (Top View)                      | 1-16  |

| Figure 1-12. | CN8478 Logic Diagram                                              | 1-17  |

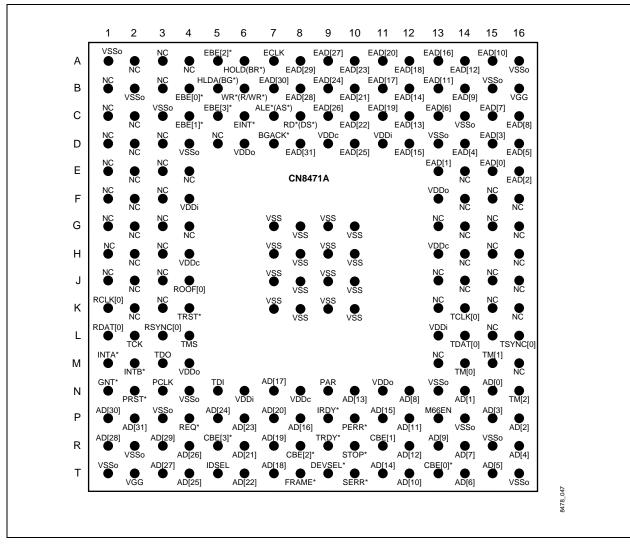

| Figure 2-1.  | Host Interface Functional Block Diagram.                          | . 2-1 |

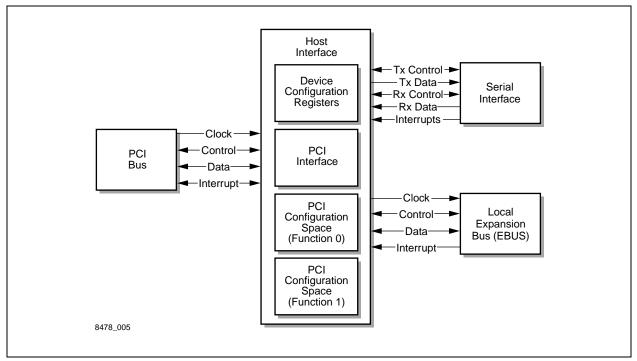

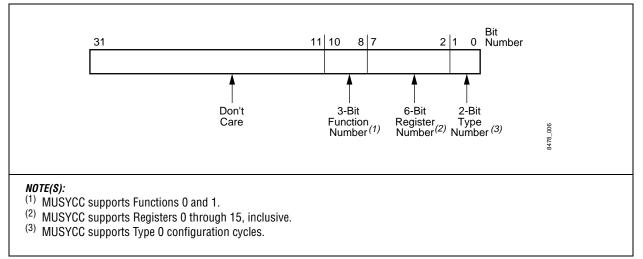

| Figure 2-2.  | Address Lines During Configuration Cycle                          | . 2-4 |

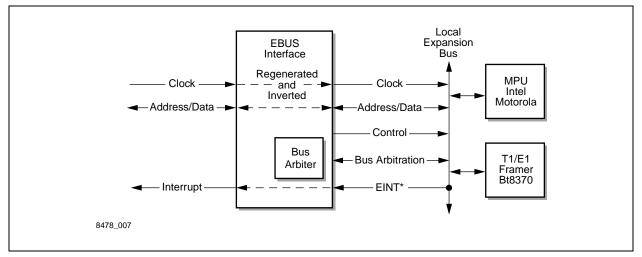

| Figure 3-1.  | EBUS Functional Block Diagram with Local MPU                      | . 3-1 |

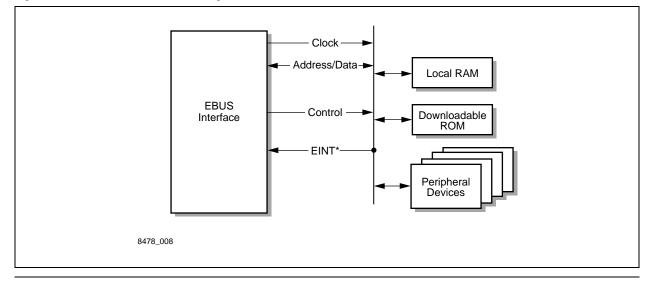

| Figure 3-2.  | EBUS Functional Block Diagram without Local MPU.                  | . 3-1 |

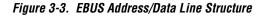

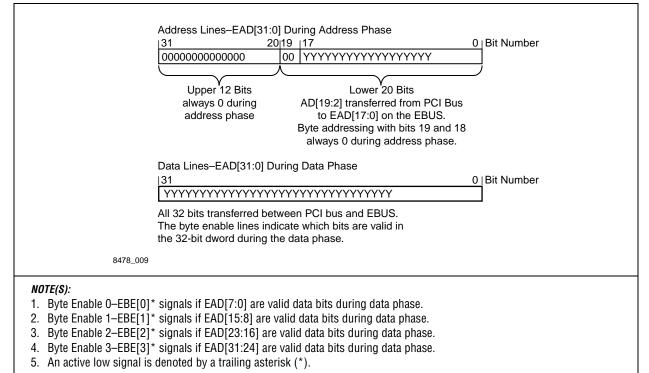

| Figure 3-3.  | EBUS Address/Data Line Structure                                  | . 3-3 |

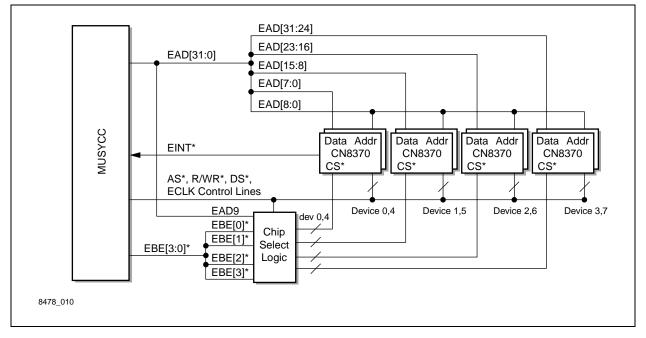

| Figure 3-4.  | EBUS Connection, Non-multiplexed Address/Data, 8 Framers, No MPU  | . 3-8 |

| Figure 3-5.  | EBUS Connection, Non-multiplexed Address/Data, 61 Framers, No MPU | . 3-9 |

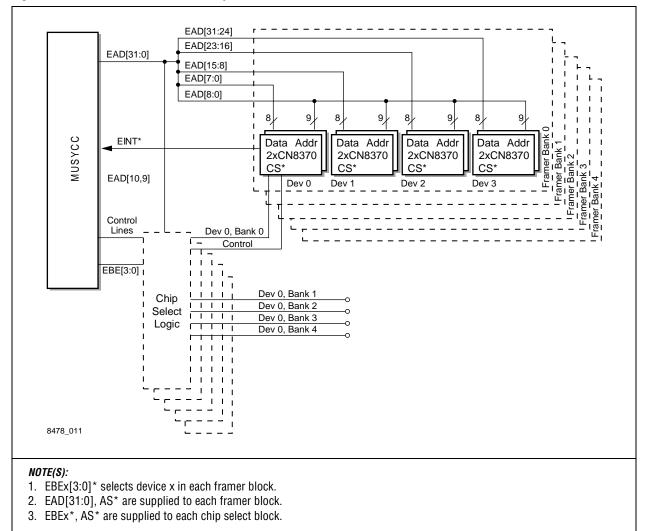

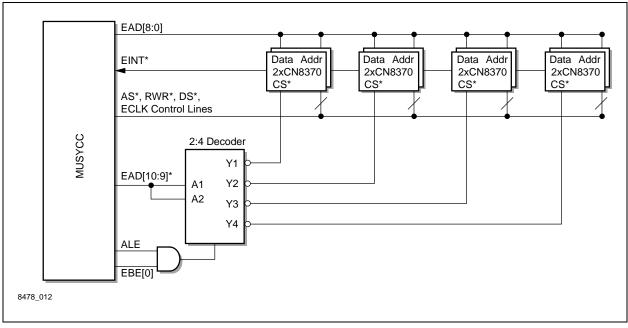

| Figure 3-6.  | EBUS Connection, Multiplexed Address/Data, 8 Framers, No MPU      | 3-10  |

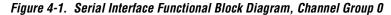

| Figure 4-1.  | Serial Interface Functional Block Diagram, Channel Group 0        | . 4-1 |

| Figure 4-2.  | Transmit and Receive T1 Mode                                      | . 4-5 |

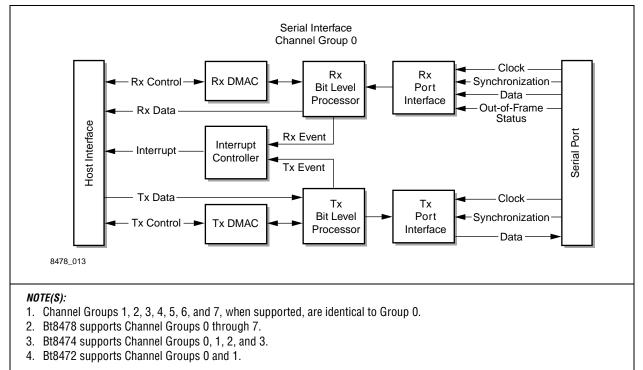

| Figure 4-3.  | Transmit and Receive E1 (also 2xE1, 4xE1) Mode                    | . 4-6 |

| Figure 4-4.  | Transmit and Receive Nx64 Mode                                    | . 4-7 |

| Figure 4-5.  | Serial Port Mapping Options                                       | . 4-9 |

| Figure 4-6.  | Receive Data Flow                                                 | 4-11  |

| Figure 4-7.  | Transmit Data Flow                                                | 4-12  |

| Figure 4-8.  | Transmit Data Bit Output Value Determination                      | 4-16  |

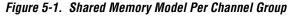

| Figure 5-1.  | Shared Memory Model Per Channel Group                             | . 5-2 |

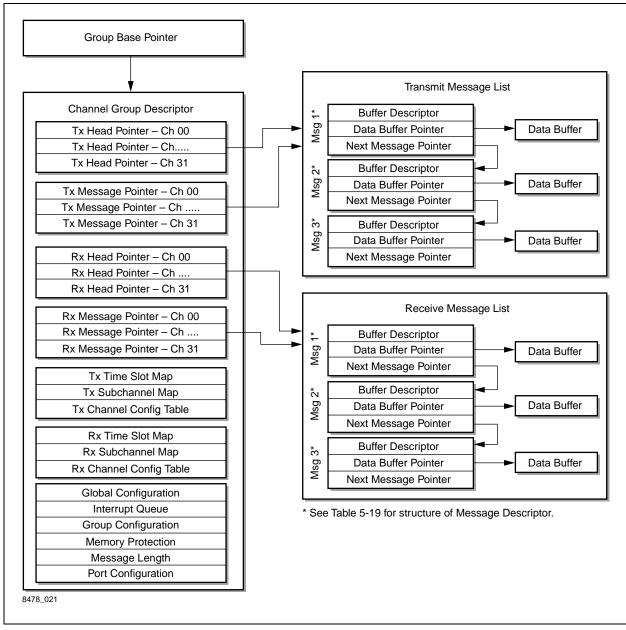

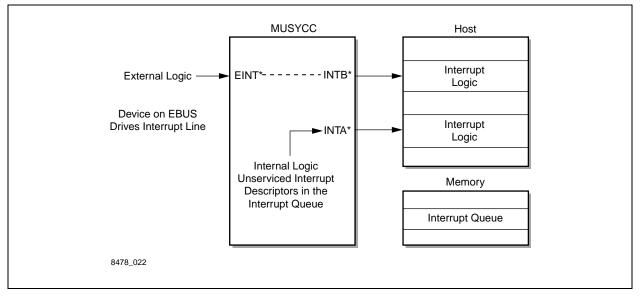

| Figure 5-2.  | Interrupt Notification To Host                                    | 5-47  |

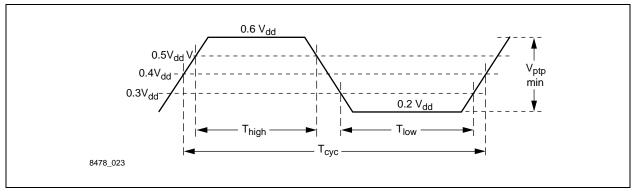

| Figure 7-1.  | PCI Clock (PCLK) Waveform                                         | . 7-5 |

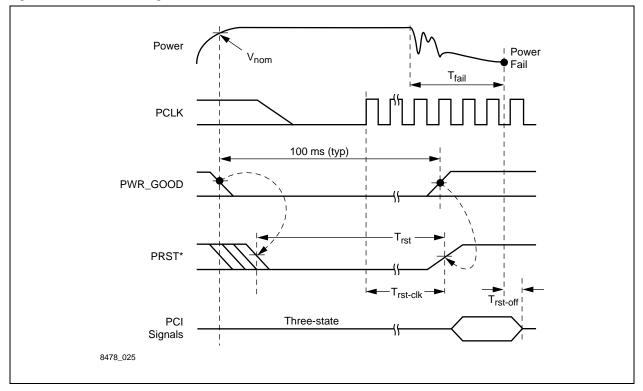

| Figure 7-2.  | PCI Reset Timing                                                  | . 7-6 |

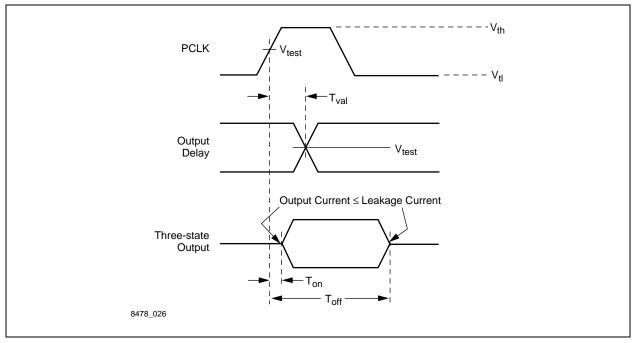

| Figure 7-3.  | PCI Output Timing Waveform                                        | . 7-8 |

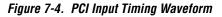

| Figure 7-4.  | PCI Input Timing Waveform                                         | . 7-9 |

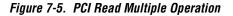

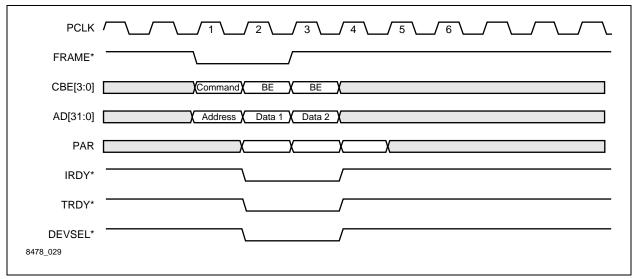

| Figure 7-5.  | PCI Read Multiple Operation                                       | . 7-9 |

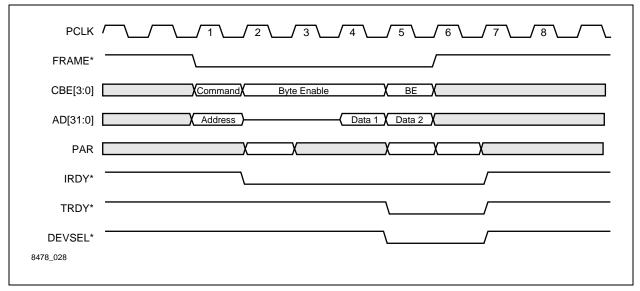

| Figure 7-6.  | PCI Write Multiple Operation                                      | 7-10  |

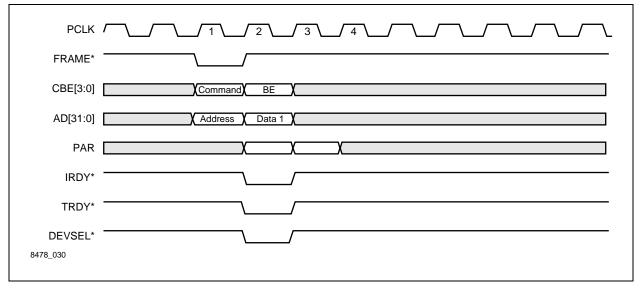

| Figure 7-7.  | PCI Write Single Operation                                        | 7-10  |

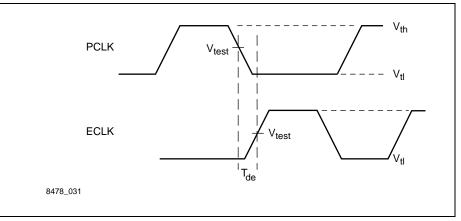

| Figure 7-8.  | ECLK to PCLK Relationship (M66EN = 0)                             | 7-11  |

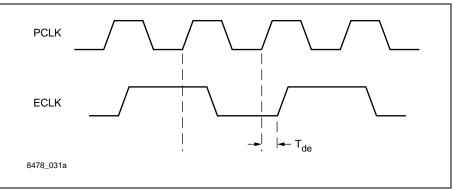

| Figure 7-9.  | ECLK to PCKL Relationship (M66EN = 1)                             | 7-11  |

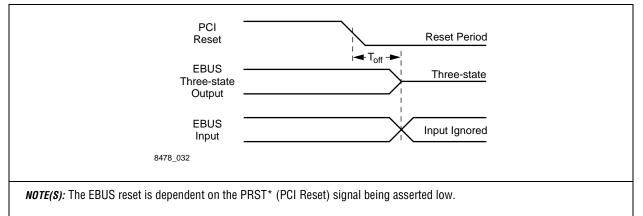

| Figure 7-10. | EBUS Reset Timing                            | 7-12 |

|--------------|----------------------------------------------|------|

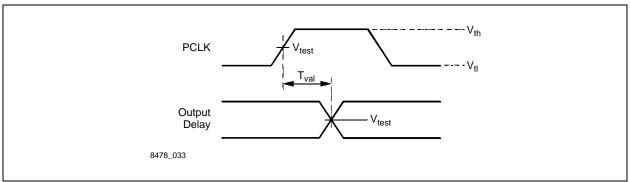

| Figure 7-11. | EBUS Output Timing Waveform                  | 7-13 |

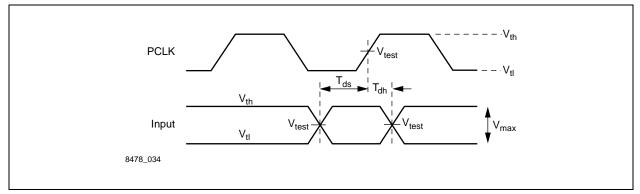

| Figure 7-12. | EBUS Input Timing Waveform                   | 7-13 |

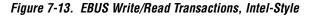

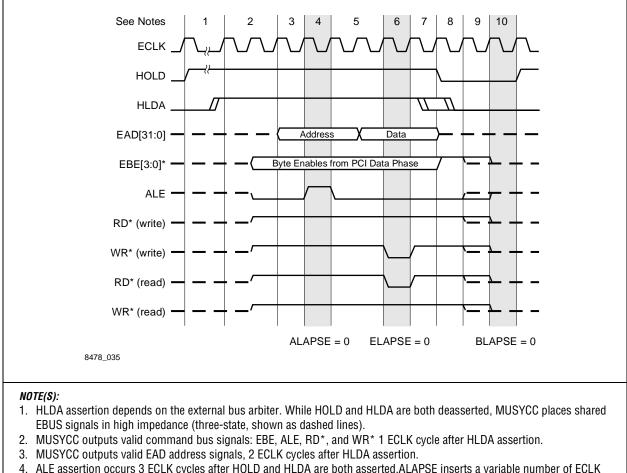

| Figure 7-13. | EBUS Write/Read Transactions, Intel-Style    | 7-14 |

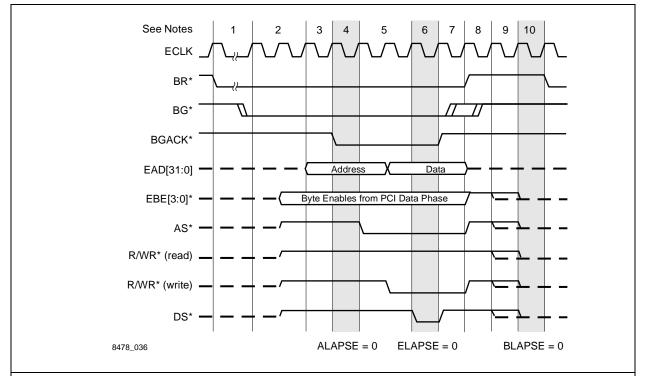

| Figure 7-14. | EBUS Write/Read Transactions, Motorola-Style | 7-15 |

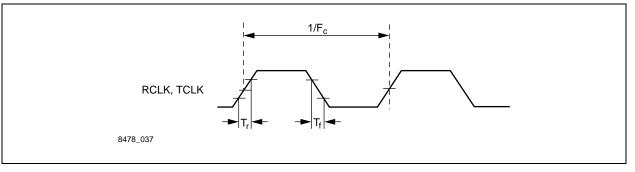

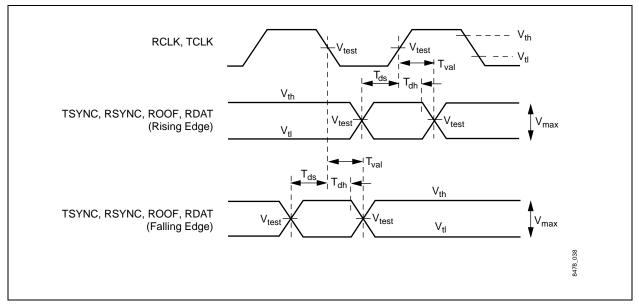

| Figure 7-15. | Serial Interface Clock (RCLK,TCLK) Waveform  | 7-16 |

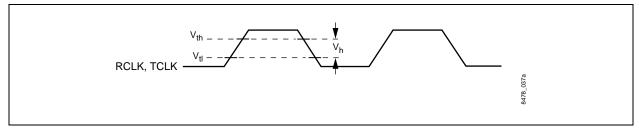

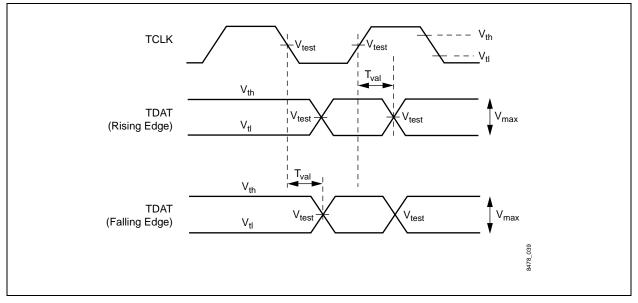

| Figure 7-16. | Serial Interface Clock (RCLK,TCLK) Waveform  | 7-17 |

| Figure 7-17. | Serial Interface Data Input Waveform         | 7-17 |

| Figure 7-18. | Serial Interface Data Delay Output Waveform  | 7-18 |

| Figure 7-19. | 208-Pin Metric Quad Flatpack (MQFP)          | 7-19 |

| Figure 7-20. | 208-Pin Plastic Ball Grid Array (PBGA)       | 7-20 |

| Figure A-1.  | JTAG Timing Diagram                          | A-3  |

# **List of Tables**

| Table 1-1.  | CN8478 MQFP Pin List                                                                  | 1-6    |

|-------------|---------------------------------------------------------------------------------------|--------|

| Table 1-2.  | CN8478 PBGA Pin List                                                                  | . 1-12 |

| Table 1-3.  | I/O Pin Types                                                                         | . 1-18 |

| Table 1-4.  | CN8478 Hardware Signal Definitions                                                    | . 1-19 |

| Table 2-1.  | Function 0 Configuration Space                                                        | 2-5    |

| Table 2-2.  | Function 1 Configuration Space                                                        | 2-5    |

| Table 2-3.  | Register 0, Address 00h                                                               | 2-7    |

| Table 2-4.  | Register 1, Address 04h                                                               | 2-8    |

| Table 2-5.  | Register 2, Address 08h                                                               | . 2-10 |

| Table 2-6.  | Register 3, Address 0Ch                                                               | . 2-11 |

| Table 2-7.  | Register 4, Address 10h                                                               | . 2-12 |

| Table 2-8.  | Registers 5–14, Addresses 14h–38h                                                     | . 2-12 |

| Table 2-9.  | Register 15, Address 3Ch                                                              | . 2-13 |

| Table 2-10. | Register 0, Address 00h                                                               | . 2-14 |

| Table 2-11. | Register 1, Address 04h                                                               | . 2-14 |

| Table 2-12. | Register 2, Address 08h                                                               | . 2-15 |

| Table 2-13. | Register 3, Address 0Ch                                                               | . 2-16 |

| Table 2-14. | Register 4, Address 10h                                                               | . 2-16 |

| Table 2-15. | Registers 5 through 14-Addresses 14h through 38h                                      | . 2-16 |

| Table 2-16. | Register 15, Address 3Ch                                                              | . 2-17 |

| Table 2-17. | PCI Latency Example                                                                   | . 2-20 |

| Table 3-1.  | Intel Protocol Signals                                                                | 3-6    |

| Table 3-2.  | Motorola Protocol Signal                                                              | 3-7    |

| Table 4-1.  | Channelized Serial Port Modes                                                         | 4-3    |

| Table 4-2.  | Internal Buffer Memory Layout                                                         | . 4-11 |

| Table 4-3.  | Example of 32-Channel with Subchanneling Buffer Allocation (Receive or Transmit)      | . 4-13 |

| Table 4-4.  | Example of 32-Channel without Subchanneling Buffer Allocation (Receive or Transmit) . | . 4-14 |

| Table 4-5.  | Example of 16-Channel without Subchanneling Buffer Allocation (Receive or Transmit) . | . 4-14 |

| Table 5-1.  | MUSYCC Register Map                                                                   | 5-4    |

| Table 5-2.  | Group Structure Memory Map                                                            | 5-6    |

| Table 5-3.  | MUSYCC PCI Function Memory Allocation                                                 | 5-6    |

| Table 5-4.  | Shared Memory Allocation—Group Descriptors                                            | 5-7    |

| Table 5-5.  | Host Assigns Group Base Pointers                                                      | 5-7    |

| Table 5-6.  | Global Configuration Descriptor                                                       | . 5-10 |

| Table 5-7.  | Dual Address Cycle Base Pointer                                                       | . 5-12 |

| Table 5-8.  | Group Base Pointer                                                                    | . 5-12 |

| Table 5-9.  | Service Request Descriptor                                                            | . 5-14 |

| Table 5-10. | Group Configuration Descriptor                                                        | . 5-16 |

| Table 5-11. | Memory Protection Descriptor                                                          | . 5-18 |

| Table 5-12. | Port Configuration Descriptor                            | 5-19  |

|-------------|----------------------------------------------------------|-------|

| Table 5-13. | Message Length Descriptor                                |       |

| Table 5-14. | Transmit or Receive Time Slot Map.                       |       |

| Table 5-15. | Time Slot Descriptor                                     |       |

| Table 5-16. | Transmit or Receive Subchannel Map                       |       |

| Table 5-17. | Subchannel Descriptor                                    |       |

| Table 5-18. | Channel Configuration Descriptor                         |       |

| Table 5-19. | Message Descriptor                                       |       |

| Table 5-20. | Head Pointer                                             |       |

| Table 5-21. | Message Pointer                                          | 5-31  |

| Table 5-22. | Transmit Buffer Descriptor                               |       |

| Table 5-23. | Receive Buffer Descriptor                                |       |

| Table 5-24. | Transmit Buffer Status Descriptor                        | 5-35  |

| Table 5-25. | Receive Buffer Status Descriptor.                        |       |

| Table 5-26. | Next Descriptor Pointer                                  |       |

| Table 5-27. | Data Buffer Pointer                                      | 5-37  |

| Table 5-28. | Interrupt Queue Descriptor                               | 5-38  |

| Table 5-29. | Interrupt Queue Pointer.                                 |       |

| Table 5-30. | Interrupt Queue Length                                   | 5-38  |

| Table 5-31. | Interrupt Descriptor.                                    |       |

| Table 5-32. | Interrupt Status Descriptor                              |       |

| Table 6-1.  | Example—Components of Group Base Pointer                 | 6-10  |

| Table 6-2.  | Example—Components of Global Configuration Descriptor    |       |

| Table 6-3.  | Example—Components of Interrupt Queue Descriptor         | 6-12  |

| Table 6-4.  | Example—Components of Group Configuration Descriptor     |       |

| Table 6-5.  | Example—Components of Memory Protection Descriptor       | 6-14  |

| Table 6-6.  | Example—Components of Port Configuration Descriptor      | 6-14  |

| Table 6-7.  | Example—Components of Message Length Descriptor          | 6-15  |

| Table 6-8.  | Example—Components of Transmit Time Slot Map – Channel 0 | 6-16  |

| Table 6-9.  | Example—Components of Transmit Subchannel Map            | 6-17  |

| Table 6-10. | Example—Components of Channel Configuration Descriptor   | 6-18  |

| Table 6-11. | Polling Frequency Using a Time Slot Counter Method       | 6-26  |

| Table 6-12. | Memory Map for Message Configuration Descriptor Table    |       |

| Table 6-13. | Message Configuration Descriptor                         | 6-30  |

| Table 7-1.  | Absolute Maximum Ratings                                 | . 7-1 |

| Table 7-2.  | Recommended Operating Conditions                         | . 7-2 |

| Table 7-3.  | Electrical Operating Characteristics                     | . 7-2 |

| Table 7-4.  | PCI Interface DC Specifications                          | . 7-3 |

| Table 7-5.  | PCI Clock (PCLK) Waveform Parameters, 33 MHz PCI Clock   | . 7-4 |

| Table 7-6.  | PCI Clock (PCLK) Waveform Parameters, 66 MHz PCI Clock   | . 7-5 |

| Table 7-7.  | PCI Reset Parameters                                     | . 7-6 |

| Table 7-8.  | PCI I/O Timing Parameters, 33 MHz PCI Clock              | . 7-7 |

| Table 7-9.  | PCI I/O Timing Parameters, 66 MHz PCI Clock              | . 7-7 |

| Table 7-10. | PCI I/O Measure Conditions                               | . 7-8 |

| Table 7-11. | EBUS Reset Parameters                                    | 7-11  |

| Table 7-12. | EBUS I/O Timing Parameters                               | 7-12  |

| Table 7-13. | EBUS I/O Measure Conditions                                          | -13 |

|-------------|----------------------------------------------------------------------|-----|

| Table 7-14. | Serial Interface Clock (RCLK, TCLK) Parameters                       | -16 |

| Table 7-15. | Serial Interface I/O Timing Parameters 7                             | -16 |

| Table 7-16. | Serial Interface Clock Hysteresis (RCLK, TCLK, with Schmitt Trigger) | -16 |

| Table 7-17. | Serial Interface I/O Measure Conditions for 3.3 V Signaling          | -17 |

| Table 7-18. | MUSYCC Package Thermal Resistance Characteristics                    | -18 |

| Table 8-1.  | Number Representation                                                | 8-2 |

| Table 8-2.  | Digitized Voice Transmission Convention                              | 8-3 |

| Table 8-3.  | Digital Data Transmission Convention                                 | 8-3 |

| Table 8-4.  | MUSYCC Byte Transmission Convention.                                 | 8-3 |

| Table 8-5.  | Little-Endian Storage Convention (Intel-style)                       | 8-4 |

| Table 8-6.  | Big-Endian Storage Convention (Motorola-style)                       | 8-4 |

| Table 8-7.  | CN8478 Data Sheet Revisions.                                         |     |

| Table A-1.  | IEEE Std. 1149.1 Instructions                                        | A-1 |

| Table A-2.  | JTAG Timing Table.                                                   | A-2 |

# **1.0 System Description**

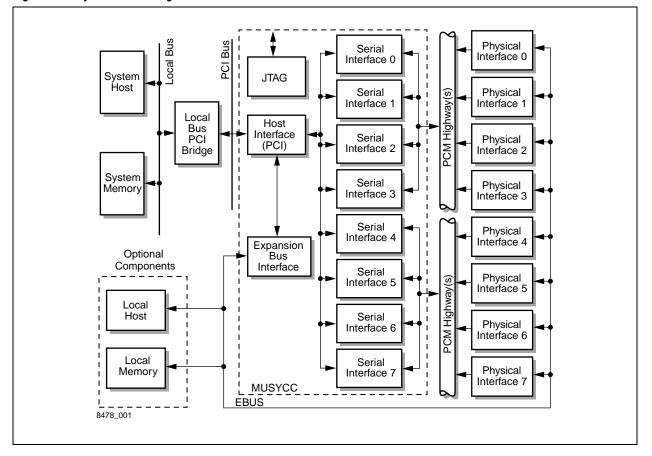

The Conexant MUSYCC is a high-throughput communications controller for synchronous, link-layer applications that multiplexes and demultiplexes up to 256 data channels. Each channel can be configured to support HDLC, Transparent, or SS7 applications. MUSYCC operates at the Layer 2 (the data link protocol level) reference of the International Organization for Standardization (ISO) Open Systems Interconnection (OSI). MUSYCC is installed between the multiple serial interface devices and the shared buffer memory of one or more host processors.

MUSYCC's serial ports interface to a standard Pulse Code Modulation (PCM) highway, which operates at T1, E1, 2xE1, or 4xE1 rates. Data can be formatted in the HDLC protocol or left unformatted. The protocol is specified on a per-channel and direction basis.

An on-device Peripheral Components Interface (PCI) controller, known as the host interface, is provided. Access to MUSYCC is available through PCI read, write, and configuration cycles (see Figure 1-1).

MUSYCC also provides an on-device, 32-bit local expansion bus (EBUS) controller which allows a host processor to access local memory and physical interface devices directly through MUSYCC over the PCI using configurable memory mapping features.

MUSYCC manages buffer memory for each active data channel with common list-processing structures. The on-device features allow data transmission between buffer memory and the serial interfaces with minimum host processor intervention. This allows the host processor to concentrate on managing the higher layers of the protocol stack.

Figures 1-2 and 1-3 illustrate detailed system block diagrams and a sample application.

Multichannel Synchronous Communications Controller (MUSYCC™)

1.1 Pin Descriptions

# 1.1 Pin Descriptions

Figures 1-4 through 1-7 illustrate the pinouts for CN8478, CN8474A, CN8472A, and CN8471A. Signals marked with black are NCs. Tables 1-1 and 1-2 summarize the pin assignments for the CN8478 in the MQFP and PBGA packages, respectively. Table 1-3 lists the pin input and output functions. Table 1-4 lists the hardware signal definitions.

# Multichannel Synchronous Communications Controller (MUSYCC<sup>TM</sup>)

# Table 1-1. CN8478 MQFP Pin List

| Pin<br>Number | Pin Label |

|---------------|-----------|

| 1             | RSYNC[7]  |

| 2             | RDAT[7]   |

| 3             | R00F[3]   |

| 4             | RCLK[3]   |

| 5             | RSYNC[3]  |

| 6             | RDAT[3]   |

| 7             | R00F[6]   |

| 8             | RCLK[6]   |

| 9             | RSYNC[6]  |

| 10            | RDAT[6]   |

| 11            | R00F[2]   |

| 12            | RCLK[2]   |

| 13            | VDDi      |

| 14            | VSS       |

| 15            | RSYNC[2]  |

| 16            | RDAT[2]   |

| 17            | R00F[5]   |

| 18            | RCLK[5]   |

| 19            | RSYNC[5]  |

| 20            | RDAT[5]   |

| 21            | R00F[1]   |

| 22            | RCLK[1]   |

| 23            | RSYNC[1]  |

| 24            | RDAT[1]   |

| 25            | R00F[4]   |

| 26            | RCLK[4]   |

| 27            | VDDc      |

| 28            | VSS       |

| 29            | RSYNC[4]  |

| 30            | RDAT[4]   |

| 31            | R00F[0]   |

| 32            | RCLK[0]   |

| 33            | RSYNC[0]  |

| 34            | RDAT[0]   |

| 35            | ТСК       |

| Pin<br>Number | Pin Label |  |  |  |  |  |

|---------------|-----------|--|--|--|--|--|

| 36            | TRST*     |  |  |  |  |  |

| 37            | TMS       |  |  |  |  |  |

| 38            | TDO       |  |  |  |  |  |

| 39            | TDI       |  |  |  |  |  |

| 40            | INTB*     |  |  |  |  |  |

| 41            | INTA*     |  |  |  |  |  |

| 42            | VDDo      |  |  |  |  |  |

| 43            | PCLK      |  |  |  |  |  |

| 44            | VSSo      |  |  |  |  |  |

| 45            | PRST*     |  |  |  |  |  |

| 46            | GNT*      |  |  |  |  |  |

| 47            | REQ*      |  |  |  |  |  |

| 48            | AD[31]    |  |  |  |  |  |

| 49            | AD[30]    |  |  |  |  |  |

| 50            | AD[29]    |  |  |  |  |  |

| 51            | AD[28]    |  |  |  |  |  |

| 52            | VGG       |  |  |  |  |  |

| 53            | VSS       |  |  |  |  |  |

| 54            | AD[27]    |  |  |  |  |  |

| 55            | VSSo      |  |  |  |  |  |

| 56            | AD[26]    |  |  |  |  |  |

| 57            | AD[25]    |  |  |  |  |  |

| 58            | AD[24]    |  |  |  |  |  |

| 59            | CBE[3]*   |  |  |  |  |  |

| 60            | IDSEL     |  |  |  |  |  |

| 61            | AD[23]    |  |  |  |  |  |

| 62            | AD[22]    |  |  |  |  |  |

| 63            | VDDo      |  |  |  |  |  |

| 64            | VSSo      |  |  |  |  |  |

| 65            | AD[21]    |  |  |  |  |  |

| 66            | AD[20]    |  |  |  |  |  |

| 67            | VDDi      |  |  |  |  |  |

| 68            | VSS       |  |  |  |  |  |

| 69            | AD[19]    |  |  |  |  |  |

| 70            | AD[18]    |  |  |  |  |  |

| Pin<br>Number | Pin Label |  |  |  |  |  |

|---------------|-----------|--|--|--|--|--|

| 71            | AD[17]    |  |  |  |  |  |

| 72            | AD[16]    |  |  |  |  |  |

| 73            | VSSo      |  |  |  |  |  |

| 74            | CBE[2]*   |  |  |  |  |  |

| 75            | FRAME*    |  |  |  |  |  |

| 76            | IRDY*     |  |  |  |  |  |

| 77            | VDDc      |  |  |  |  |  |

| 78            | VSS       |  |  |  |  |  |

| 79            | TRDY*     |  |  |  |  |  |

| 80            | DEVSEL*   |  |  |  |  |  |

| 81            | VDDo      |  |  |  |  |  |

| 82            | VSSo      |  |  |  |  |  |

| 83            | STOP*     |  |  |  |  |  |

| 84            | PERR*     |  |  |  |  |  |

| 85            | SERR*     |  |  |  |  |  |

| 86            | PAR       |  |  |  |  |  |

| 87            | CBE[1]    |  |  |  |  |  |

| 88            | AD[15]    |  |  |  |  |  |

| 89            | VSSo      |  |  |  |  |  |

| 90            | AD[14]    |  |  |  |  |  |

| 91            | AD[13]    |  |  |  |  |  |

| 92            | AD[12]    |  |  |  |  |  |

| 93            | AD[11]    |  |  |  |  |  |

| 94            | AD[10]    |  |  |  |  |  |

| 95            | VDDo      |  |  |  |  |  |

| 96            | VSSo      |  |  |  |  |  |

| 97            | AD[9]     |  |  |  |  |  |

| 98            | M66EN     |  |  |  |  |  |

| 99            | AD[8]     |  |  |  |  |  |

| 100           | CBE[0]*   |  |  |  |  |  |

| 101           | AD[7]     |  |  |  |  |  |

| 102           | AD[6]     |  |  |  |  |  |

| 103           | AD[5]     |  |  |  |  |  |

| 104           | VSSo      |  |  |  |  |  |

| 105           | AD[4]     |  |  |  |  |  |

# CN8478/CN8474A/CN8472A/CN8471A

# Multichannel Synchronous Communications Controller (MUSYCC<sup>TM</sup>)

1.1 Pin Descriptions

| Pin<br>Number | Pin Label |  |  |  |  |  |

|---------------|-----------|--|--|--|--|--|

| 106           | AD[3]     |  |  |  |  |  |

| 107           | AD[2]     |  |  |  |  |  |

| 108           | AD[1]     |  |  |  |  |  |

| 109           | AD[0]     |  |  |  |  |  |

| 110           | VDDo      |  |  |  |  |  |

| 111           | VSSo      |  |  |  |  |  |

| 112           | TM[2]     |  |  |  |  |  |

| 113           | TM[1]     |  |  |  |  |  |

| 114           | TM[0]     |  |  |  |  |  |

| 115           | TDAT[4]   |  |  |  |  |  |

| 116           | TSYNC[4]  |  |  |  |  |  |

| 117           | TCLK[4]   |  |  |  |  |  |

| 118           | VDDi      |  |  |  |  |  |

| 119           | VSS       |  |  |  |  |  |

| 120           | TDAT[0]   |  |  |  |  |  |

| 121           | TSYNC[0]  |  |  |  |  |  |

| 122           | TCLK[0]   |  |  |  |  |  |

| 123           | TDAT[5]   |  |  |  |  |  |

| 124           | TSYNC[5]  |  |  |  |  |  |

| 125           | TCLK[5]   |  |  |  |  |  |

| 126           | TDAT[1]   |  |  |  |  |  |

| 127           | TSYNC[1]  |  |  |  |  |  |

| 128           | TCLK[1]   |  |  |  |  |  |

| 129           | TDAT[6]   |  |  |  |  |  |

| 130           | TSYNC[6]  |  |  |  |  |  |

| 131           | TCLK[6]   |  |  |  |  |  |

| 132           | VDDc      |  |  |  |  |  |

| 133           | VSS       |  |  |  |  |  |

| 134           | TDAT[2]   |  |  |  |  |  |

| 135           | TSYNC[2]  |  |  |  |  |  |

| 136           | TCLK[2]   |  |  |  |  |  |

| 137           | VSSo      |  |  |  |  |  |

| 138           | TDAT[7]   |  |  |  |  |  |

| 139           | TSYNC[7]  |  |  |  |  |  |

| 140           | TCLK[7]   |  |  |  |  |  |

| 141           | TDAT[3]   |  |  |  |  |  |

| 142         TSYNC[3]           143         TCLK[3]           144         EAD[0]           145         EAD[1]           146         EAD[2]           147         VDDo           148         VSSo           149         EAD[3]           150         EAD[4]           151         EAD[5]           152         EAD[6]           153         VSSo           154         EAD[7]           155         EAD[8]           156         VGG           157         VSS           158         EAD[9]           159         EAD[10]           160         EAD[11]           161         EAD[12]           162         EAD[13]           163         EAD[14]           164         VDDo           165         VSSo           166         EAD[15]           167         EAD[16]           168         EAD[17]           169         EAD[18]           170         EAD[18]           171         VDDi           172         VSSo           173         EAD[20] | Pin<br>Number | Pin Label |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------|--|--|--|

| 144       EAD[0]         145       EAD[1]         146       EAD[2]         147       VDDo         148       VSSo         149       EAD[3]         150       EAD[4]         151       EAD[5]         152       EAD[6]         153       VSSo         154       EAD[7]         155       EAD[8]         156       VGG         157       VSS         158       EAD[10]         160       EAD[11]         161       EAD[12]         162       EAD[13]         163       EAD[14]         164       VDDo         165       VSSo         166       EAD[15]         167       EAD[16]         168       EAD[17]         169       EAD[18]         170       EAD[19]         171       VDDi         172       VSS         173       EAD[20]         174       EAD[21]         175       VSSo                                                                                                                                                             | 142           | TSYNC[3]  |  |  |  |

| 145         EAD[1]           146         EAD[2]           147         VDDo           148         VSSo           149         EAD[3]           150         EAD[4]           151         EAD[5]           152         EAD[6]           153         VSSo           154         EAD[7]           155         EAD[8]           156         VGG           157         VSS           158         EAD[10]           160         EAD[11]           161         EAD[12]           162         EAD[13]           163         EAD[14]           164         VDDo           165         VSSo           166         EAD[15]           167         EAD[16]           168         EAD[17]           169         EAD[18]           170         EAD[18]           171         VDDi           172         VSS           173         EAD[20]           174         EAD[21]           175         VSSo                                                                | 143           | TCLK[3]   |  |  |  |

| 146         EAD[2]           147         VDDo           148         VSSo           149         EAD[3]           150         EAD[4]           151         EAD[5]           152         EAD[6]           153         VSSo           154         EAD[7]           155         EAD[8]           156         VGG           157         VSS           158         EAD[9]           159         EAD[10]           160         EAD[11]           161         EAD[12]           162         EAD[13]           163         EAD[14]           164         VDDo           165         VSSo           166         EAD[15]           167         EAD[16]           168         EAD[17]           169         EAD[18]           170         EAD[18]           171         VDDi           172         VSS           173         EAD[20]           174         EAD[21]           175         VSSo                                                                | 144           | EAD[0]    |  |  |  |

| 147         VDDo           148         VSSo           149         EAD[3]           150         EAD[4]           151         EAD[5]           152         EAD[6]           153         VSSo           154         EAD[7]           155         EAD[8]           156         VGG           157         VSS           158         EAD[9]           159         EAD[10]           160         EAD[11]           161         EAD[12]           162         EAD[13]           163         EAD[14]           164         VDDo           165         VSSo           166         EAD[15]           167         EAD[16]           168         EAD[17]           169         EAD[18]           170         EAD[19]           171         VDDi           172         VSS           173         EAD[20]           174         EAD[21]           175         VSSo                                                                                             | 145           | EAD[1]    |  |  |  |

| 148         VSSo           149         EAD[3]           150         EAD[4]           151         EAD[5]           152         EAD[6]           153         VSSo           154         EAD[7]           155         EAD[8]           156         VGG           157         VSS           158         EAD[10]           160         EAD[11]           161         EAD[12]           162         EAD[13]           163         EAD[14]           164         VDDo           165         VSSo           166         EAD[15]           167         EAD[16]           168         EAD[17]           169         EAD[18]           170         EAD[19]           171         VDDi           172         VSS           173         EAD[20]           174         EAD[21]           175         VSSo           176         EAD[22]                                                                                                                       | 146           | EAD[2]    |  |  |  |

| 149         EAD[3]           150         EAD[4]           151         EAD[5]           152         EAD[6]           153         VSS0           154         EAD[7]           155         EAD[8]           156         VGG           157         VSS           158         EAD[10]           160         EAD[11]           161         EAD[12]           162         EAD[14]           163         EAD[14]           164         VDD0           165         VSS0           166         EAD[17]           167         EAD[16]           168         EAD[17]           169         EAD[18]           170         EAD[18]           171         VDDi           172         VSS           173         EAD[20]           174         EAD[21]           175         VSS0                                                                                                                                                                                | 147           | VDDo      |  |  |  |

| 150       EAD[4]         151       EAD[5]         152       EAD[6]         153       VSSo         154       EAD[7]         155       EAD[8]         156       VGG         157       VSS         158       EAD[10]         160       EAD[11]         161       EAD[12]         162       EAD[13]         163       EAD[14]         164       VDDo         165       VSSo         166       EAD[15]         167       EAD[16]         168       EAD[17]         169       EAD[18]         170       EAD[19]         171       VDDi         172       VSS         173       EAD[20]         174       EAD[21]         175       VSSo                                                                                                                                                                                                                                                                                                               | 148           | VSSo      |  |  |  |

| 151         EAD[5]           152         EAD[6]           153         VSSo           154         EAD[7]           155         EAD[8]           156         VGG           157         VSS           158         EAD[9]           159         EAD[10]           160         EAD[12]           162         EAD[13]           163         EAD[14]           164         VDDo           165         VSSo           166         EAD[15]           167         EAD[16]           168         EAD[17]           169         EAD[18]           170         EAD[19]           171         VDDi           172         VSS           173         EAD[20]           174         EAD[21]           175         VSSo                                                                                                                                                                                                                                           | 149           | EAD[3]    |  |  |  |

| 152         EAD[6]           153         VSSo           154         EAD[7]           155         EAD[8]           156         VGG           157         VSS           158         EAD[9]           159         EAD[10]           160         EAD[11]           161         EAD[12]           162         EAD[13]           163         EAD[14]           164         VDDo           165         VSSo           166         EAD[15]           167         EAD[16]           168         EAD[17]           169         EAD[18]           170         EAD[19]           171         VDDi           172         VSS           173         EAD[20]           174         EAD[21]           175         VSSo                                                                                                                                                                                                                                          | 150           | EAD[4]    |  |  |  |

| 153         VSSo           153         VSSo           154         EAD[7]           155         EAD[8]           156         VGG           157         VSS           158         EAD[9]           159         EAD[10]           160         EAD[11]           161         EAD[12]           162         EAD[13]           163         EAD[14]           164         VDDo           165         VSSo           166         EAD[15]           167         EAD[16]           168         EAD[17]           169         EAD[18]           170         EAD[19]           171         VDDi           172         VSS           173         EAD[20]           174         EAD[21]           175         VSSo <td>151</td> <td>EAD[5]</td>                                                                                                                                                                                                               | 151           | EAD[5]    |  |  |  |

| Instant         Instant           154         EAD[7]           155         EAD[8]           156         VGG           157         VSS           158         EAD[9]           159         EAD[10]           160         EAD[11]           161         EAD[12]           162         EAD[13]           163         EAD[14]           164         VDDo           165         VSSo           166         EAD[15]           167         EAD[16]           168         EAD[17]           169         EAD[18]           170         EAD[19]           171         VDDi           172         VSS           173         EAD[20]           174         EAD[22]                                                                                                                                                                                                                                                                                           | 152           | EAD[6]    |  |  |  |

| 155         EAD[8]           156         VGG           157         VSS           158         EAD[9]           159         EAD[10]           160         EAD[11]           161         EAD[12]           162         EAD[14]           163         EAD[14]           164         VDDo           165         VSSo           166         EAD[15]           167         EAD[16]           168         EAD[17]           169         EAD[18]           170         EAD[19]           171         VDDi           172         VSS           173         EAD[20]           174         EAD[21]           175         VSSo                                                                                                                                                                                                                                                                                                                               | 153           | VSSo      |  |  |  |

| 156         VGG           157         VSS           158         EAD[9]           159         EAD[10]           160         EAD[11]           161         EAD[12]           162         EAD[14]           163         EAD[14]           164         VDDo           165         VSSo           166         EAD[15]           167         EAD[16]           168         EAD[17]           169         EAD[18]           170         EAD[19]           171         VDDi           172         VSS           173         EAD[20]           174         EAD[21]           175         VSSo                                                                                                                                                                                                                                                                                                                                                            | 154           | EAD[7]    |  |  |  |

| 157         VSS           158         EAD[9]           159         EAD[10]           160         EAD[11]           161         EAD[12]           162         EAD[13]           163         EAD[14]           164         VDDo           165         VSSo           166         EAD[15]           167         EAD[16]           168         EAD[17]           169         EAD[18]           170         EAD[19]           171         VDDi           172         VSS           173         EAD[20]           174         EAD[21]           176         EAD[22]                                                                                                                                                                                                                                                                                                                                                                                   | 155           | EAD[8]    |  |  |  |

| 158         EAD[9]           159         EAD[10]           160         EAD[11]           161         EAD[12]           162         EAD[13]           163         EAD[14]           164         VDDo           165         VSSo           166         EAD[15]           167         EAD[16]           168         EAD[17]           169         EAD[18]           170         EAD[19]           171         VDDi           172         VSS           173         EAD[20]           174         EAD[22]                                                                                                                                                                                                                                                                                                                                                                                                                                           | 156           | VGG       |  |  |  |

| 159       EAD[10]         160       EAD[11]         161       EAD[12]         162       EAD[13]         163       EAD[14]         164       VDDo         165       VSSo         166       EAD[15]         167       EAD[16]         168       EAD[17]         169       EAD[18]         170       EAD[19]         171       VDDi         172       VSS         173       EAD[20]         174       EAD[22]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 157           | VSS       |  |  |  |

| 160         EAD[11]           161         EAD[12]           162         EAD[13]           163         EAD[14]           164         VDDo           165         VSSo           166         EAD[15]           167         EAD[16]           168         EAD[17]           169         EAD[18]           170         EAD[19]           171         VDDi           172         VSS           173         EAD[20]           174         EAD[21]           176         EAD[22]                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 158           | EAD[9]    |  |  |  |

| 161       EAD[12]         162       EAD[13]         163       EAD[14]         164       VDDo         165       VSSo         166       EAD[15]         167       EAD[16]         168       EAD[17]         169       EAD[18]         170       EAD[19]         171       VDDi         172       VSS         173       EAD[20]         174       EAD[21]         176       EAD[22]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 159           | EAD[10]   |  |  |  |

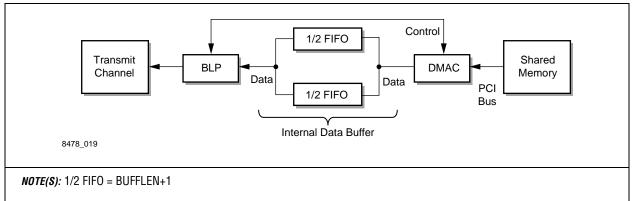

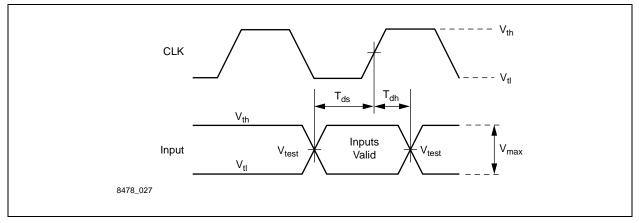

| 162       EAD[13]         163       EAD[14]         164       VDDo         165       VSSo         166       EAD[15]         167       EAD[16]         168       EAD[17]         169       EAD[18]         170       EAD[19]         171       VDDi         172       VSS         173       EAD[20]         174       EAD[22]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 160           | EAD[11]   |  |  |  |