# LC89210

# High-speed fax modem data pump

# **Preliminaly**

#### Overview

The LC89210 is a highly integrated modem engine that can be used in products that support transmission rates up to the 14,400 bps rate used in contemporary group III fax equipment. The LC89210 is compatible with V.21, V.23 and Bell 103 full-duplex modems.

### **Features**

- Supports the ITU-T V.17, V.29, and V.27ter fax standards

- ITU-T V.23, V.21, and Bell 103

- V.17, V.29 (T104), and V.27ter short training

- V.33 half duplex

- 1800-Hz or 1700-Hz carrier

- The LC89210 is a complete data pump on a single chip.

- 5 V single-voltage power supply

- Operating power dissipation: 375 mW (typical)

- Low power mode: 5 mW (typical)

- · Expanded operating modes

- Full implementation of V.17, V.33, V.29, and V.27ter handshaking

- Autodial and autoanswer functions

- Programmable tone detection and FSK V.21 flag pattern detection during high-speed reception

- Programmable call progresss and call waiting tone detection, including DTMF

- Support for programmable CLASS<sup>TM</sup> detection

- Wide dynamic range (better than 48 dB)

- A-law voice PCM mode

- · Multiple interfaces

- Parallel 64 ×8-bit dual-port RAM

- Synchronous/HDLC parallel data processing

- Support for HDLC framing

- V.24 interface

- Can monitor all operating states in real time.

- Includes all diagnostic functions.

- Dual 8-bit D/A converter for eye pattern display

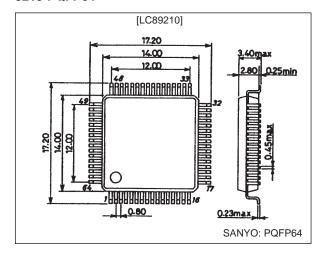

# **Package Dimensions**

unit: mm

#### 3213-PQFP64

# **Specifications**

# Electrical Specifications at Ta = $25^{\circ}$ C, $V_{DD}$ = 5 V (unless otherwise specified) Absolute Maximum Ratings with respect to ground

| Parameter                       | Symbol                           | Conditions | Ratings                         | Unit |

|---------------------------------|----------------------------------|------------|---------------------------------|------|

| DC supply voltage               | V <sub>DD</sub>                  |            | -0.3 to +7.0                    | V    |

| Digital or analog input voltage | V <sub>I</sub> , V <sub>IN</sub> |            | -0.3 to (V <sub>DD</sub> + 0.3) | V    |

| Digital or analog input current | I <sub>I</sub> , I <sub>IN</sub> |            | ±1                              | mA   |

| Digital output current          | Io                               |            | ±20                             | mA   |

| Analog output current           | l <sub>OUT</sub>                 |            | ±10                             | mA   |

| Allowable power dissipation     | Pd max                           |            | 1000                            | mW   |

| Operating temperature           | Topr                             |            | 0 to +70                        | °C   |

| Storage temperature (plastic)   | Tstg                             |            | -40 to +125                     | °C   |

# Electrical Characteristics at Ta = 0 to +70 $^{\circ}$ C, $V_{DD}$ = 5.0 V $\pm$ 5%, GND = 0 V (unless otherwise specified)

| Parameter                               | Symbol              | Conditions                                             | min                     | typ                | max                     | Unit |

|-----------------------------------------|---------------------|--------------------------------------------------------|-------------------------|--------------------|-------------------------|------|

| [Power Supply and Common-Mode           | Voltages]           |                                                        |                         |                    |                         |      |

| Supply voltage                          | V <sub>DD</sub>     |                                                        | 4.75                    | 5                  | 5.25                    | V    |

| Current drain                           | I <sub>DD</sub>     |                                                        |                         | 75                 | 100                     | mA   |

| Current drain in lower power mode       | I <sub>DD-ip</sub>  |                                                        |                         | 1                  |                         | mA   |

| Common-mode voltage                     | V <sub>CM</sub>     |                                                        | V <sub>DD</sub> /2 – 5% | V <sub>DD</sub> /2 | V <sub>DD</sub> /2 + 5% | V    |

| [Crystal Oscillator Interface] XTAL     | and EXTAL           |                                                        |                         |                    |                         |      |

| Input low-level voltage                 | V <sub>IL</sub>     |                                                        |                         |                    | 1.5                     | V    |

| Input high-level voltage                | V <sub>IH</sub>     |                                                        | 3.5                     |                    |                         | V    |

| Input low-level current                 | ΙL                  | GND < V <sub>I</sub> < V <sub>IL</sub> max             | -15                     |                    |                         | μA   |

| Input high-level current                | I <sub>H</sub>      | V <sub>IH</sub> min < V <sub>I</sub> < V <sub>DD</sub> |                         |                    | 15                      | μA   |

| [Digital Interface] All digital pins ex | cept the XTAI       | pin                                                    |                         |                    |                         |      |

| Input low-level voltage                 | V <sub>IL</sub>     |                                                        | -0.3                    |                    | +0.8                    | V    |

| Input high-level voltage                | V <sub>IH</sub>     |                                                        | 2.2                     |                    |                         | V    |

| Input current                           | II                  | $V_I = V_{DD}$ or $V_I = GND$                          | -10                     | 0                  | +10                     | μΑ   |

| Output high-level voltage               | V <sub>OH</sub>     | I <sub>lord</sub> = 2 mA                               | 2.4                     |                    |                         | V    |

| Output low-level voltage                | V <sub>OL</sub>     | I <sub>lord</sub> = 2 mA                               |                         |                    | 0.4                     | V    |

| 3-state input leakage current           | l <sub>OZ</sub>     | GND < V <sub>O</sub> < V <sub>DD</sub>                 | -50                     | 0                  | +50                     | μΑ   |

| Input capacitance                       | C <sub>IN</sub>     |                                                        |                         | 5                  |                         | pF   |

| [Analog Interface]                      |                     |                                                        |                         |                    |                         |      |

| Differential reference voltage input    | $V_{REF}$           | V <sub>REFP</sub> – V <sub>REFN</sub>                  | 2.40                    | 2.50               | 2.60                    | V    |

| Input common-mode offset                | $V_{CMOin}$         | $V = (RXA1 + RXA2)/2 - V_{CM}$                         | -300                    |                    | +300                    | mV   |

| Differential input voltage              | $V_{DIFin}$         | RXA1 – RXA2                                            |                         |                    | $2 \times V_{REF}$      | Vp-p |

| Output common-mode voltage offset       | V <sub>CMOout</sub> | (TXA1 + TXA2)/2 – V <sub>CM</sub>                      | -200                    |                    | +200                    | mV   |

| Differential output voltage             | V <sub>DIFout</sub> | TXA1 – TXA2                                            |                         |                    | $2 \times V_{REF}$      | Vp-p |

| Differential output DC offset           | V <sub>OFFout</sub> | (TXA1 – TXA2)                                          | -100                    |                    | +100                    | mV   |

| Input resistance                        | Rin                 | RXA <sub>X</sub>                                       | 100                     |                    |                         | kΩ   |

| Output resistance                       | Rout                | TXA <sub>X</sub>                                       |                         |                    | 20                      | Ω    |

| Load resistance                         | R <sub>L</sub>      | TXA <sub>X</sub>                                       | 10                      |                    |                         | kΩ   |

| Load capacitance                        | C <sub>L</sub>      | TXA <sub>X</sub>                                       |                         |                    | 50                      | pF   |

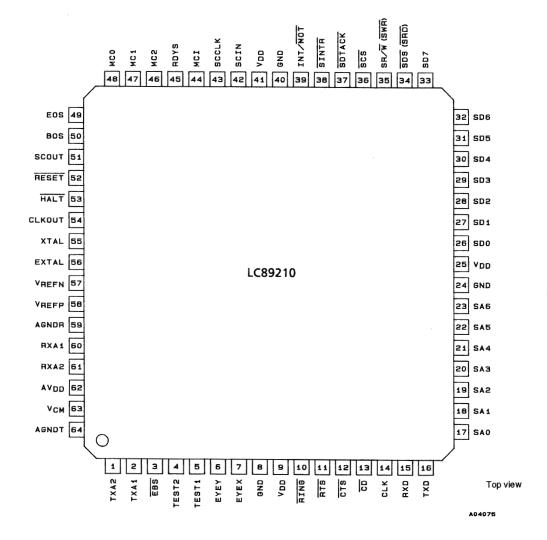

## **Pin Assignment**

#### **Host Interface**

The LC89210 is interfaced to the control processor through a 64-byte dual-port RAM that is shared by the LC89210 and the host.

| Pin        | Туре | Function                             |

|------------|------|--------------------------------------|

| SD0 to SD7 | I/O  | System data bus                      |

| SA0 to SA6 | ı    | System address bus                   |

| SDS (SDR)  | ı    | System data strobe                   |

| SR/W (SWR) | ı    | System read/write                    |

| SCS        | ı    | System chip select                   |

| SDTACK     | OD*  | System bus data acknowledge          |

| SINTR      | OD*  | System interrupt request             |

| RESET      | ı    | Reset. This is an active-low signal. |

| RING       | I    | Ring detect signal                   |

| INT/MOT    | I    | Intel/Motorola interface             |

Note: \* Open-drain output

#### LC89210

## **Analog Interface**

| Pin               | Туре | Function                                                       |

|-------------------|------|----------------------------------------------------------------|

| TXA1              | 0    | Transmission analog output 1                                   |

| TXA2              | 0    | Transmission analog output 2                                   |

| RXA1              | I    | Reception analog input 1                                       |

| RXA2              | I    | Reception analog input 2                                       |

| V <sub>CM</sub>   | I/O  | Analog common voltage (nominal value: +2.5 V)                  |

| V <sub>REFN</sub> | I    | Analog negative reference voltage (nominal value: CM – 1.25 V) |

| V <sub>REFP</sub> | I    | Analog positive reference voltage (nominal value: CM + 1.25 V) |

## V.24 Interface

| Pin | Туре | Function                                        |

|-----|------|-------------------------------------------------|

| RTS | ı    | Transfer request. This is an active-low signal. |

| CLK | 0    | Data bit clock                                  |

| CTS | 0    | Clear to send. This is an active-low signal.    |

| RXD | 0    | Reception data                                  |

| TXD | ı    | Transfer data                                   |

| CD  | 0    | Carrier detect. This is an active-low signal.   |

#### Other Interfaces

| Pin   | Туре | Function                                        |

|-------|------|-------------------------------------------------|

| XTAL  | 0    | Internal oscillator output                      |

| EXTAL | I    | Internal oscillator input or external clock     |

| EYEX  | 0    | Constellation X analog coordinate (eye pattern) |

| EYEY  | 0    | Constellation Y analog coordinate (eye pattern) |

| TEST1 |      | This pin must be left open                      |

| TEST2 |      | This pin must be left open                      |

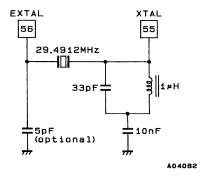

Note: The LC89210 nominal external clock frequency is 29.4912 MHz. This value has a precision of  $\pm 5.10^{-5}$ .

## **Boundary Scan Interface**

The LC89210 provides 13 signals for testing. These signals can be used along with the SGS-Thomson ST18932 boundary scan development tools in the product development process to debug application hardware and software. If this function is not used, all of these input signal must be connected to ground, and all of these output signals must be left open.

| Pin        | Туре | Function                                                               |

|------------|------|------------------------------------------------------------------------|

| SCIN       | I    | Scan data input                                                        |

| SCCLK      | I    | Scan clock                                                             |

| SCOUT      | 0    | Scan data output                                                       |

| BOS        | I    | Scan control start                                                     |

| EOS        | I    | Scan stop                                                              |

| MC0 to MC2 | I    | Mode control                                                           |

| HALT       | I    | LC89210 execution step                                                 |

| MC1        | 0    | Multi-cycle instruction                                                |

| RDYS       | 0    | Scan flag ready                                                        |

| EBS        | I    | Enable boundary scan                                                   |

| CLKOUT     | 0    | LC89210 internal clock (the crystal oscillator frequency divided by 2) |

#### **Power Supply**

| Symbol           | Parameter                                  |

|------------------|--------------------------------------------|

| V <sub>DD</sub>  | Digital +5 V (pins 9, 25, and 41)          |

| GND              | Digital ground (pins 8, 24, and 40)        |

| AV <sub>DD</sub> | Analog +5 V (pin 62)                       |

| AGNDT            | Analog transmission system ground (pin 64) |

| AGNDR            | Analog reception system ground (pin 59)    |

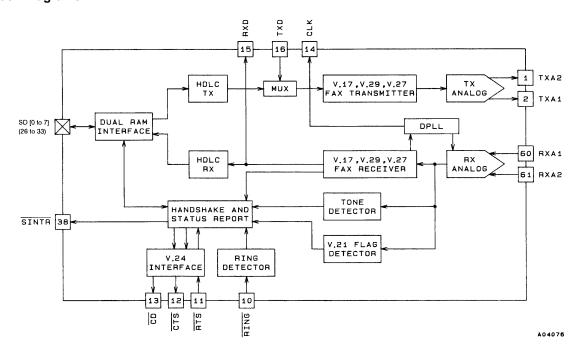

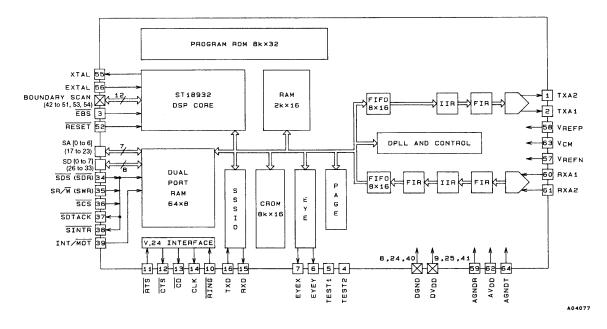

#### **Block Diagrams**

**Function Block Diagram**

**Hardware Block Diagram**

#### **AC Electrical Characteristics**

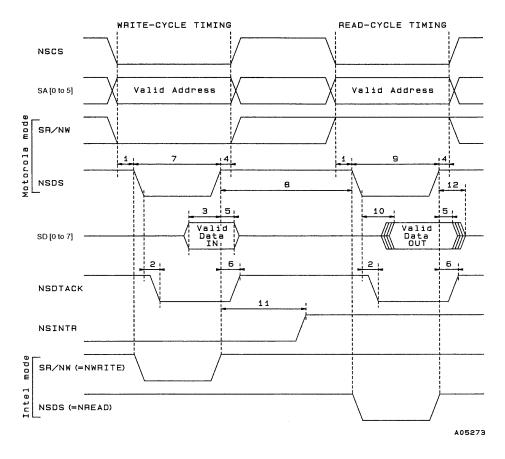

## **Dual-Port RAM Host Timing**

| Parameter                      | Number | Conditions | min | typ | max | Unit |

|--------------------------------|--------|------------|-----|-----|-----|------|

| Address and control setup time | 1      |            | 5   |     |     | ns   |

| SDTACK acknowledge             | 2      |            |     |     | 20  | ns   |

| Data setup time                | 3      |            | 10  |     |     | ns   |

| Address and control hold time  | 4      |            | 0   |     |     | ns   |

| Data hold time                 | 5      |            | 5   |     |     | ns   |

| SDTACK hold time               | 6      |            | 0   |     |     | ns   |

| Write enable low state         | 7      |            | 45  |     |     | ns   |

| Access inhibition high state   | 8      |            | 70* |     |     | ns   |

| Read enable low state          | 9      |            | 45  |     |     | ns   |

| Read data access               | 10     |            |     |     | 35  | ns   |

| SINTR clear delay              | 11     |            |     |     | 50  | ns   |

| Data valid to tristate         | 12     |            |     |     | 15  | ns   |

Note: \* The minimum delay of 70 ns is the time from the rising edge of NWRITE to the next falling edge on either NREAD or NWRITE.

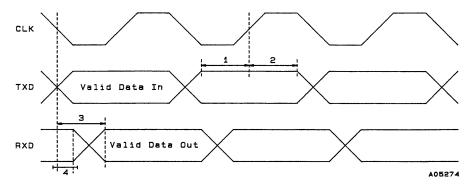

# Serial V.24 Interface Timing

| Parameter                   | Number | Conditions | min | typ | max | Unit |

|-----------------------------|--------|------------|-----|-----|-----|------|

| TXD to CLK setup time       | 1      |            | 30  |     |     | ns   |

| TXD to CLK hold time        | 2      |            | 10  |     |     | ns   |

| RXD valid to CLK delay time | 3      |            |     |     | 100 | ns   |

| RXD valid to CLK hold time  | 4      |            | 0   |     |     | ns   |

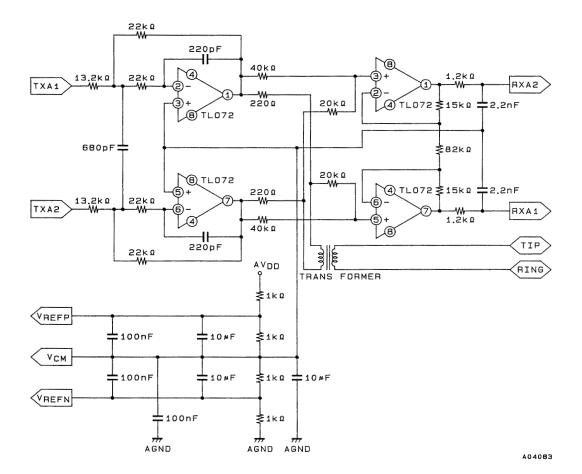

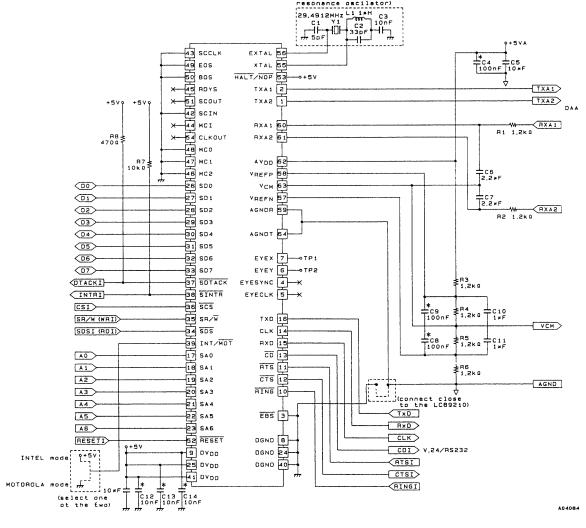

## **Electrical Circuit Diagrams**

#### Oscillator

We recommend the use of the following circuit if an overtone crystal oscillator is used in series resonance mode.

#### **Printed Circuit Board Design Guidelines**

While the two most important factors influencing the performance of this fax modem are the performance of the LC89210 itself and the appropriateness of the design of the printed circuit board, it is not the purpose of this section to describe all aspects of modem printed circuit board design. Rather, this section presents the following few recommendations.

- 1. 4-layer boards

- The digital and analog system grounds should be separated and then connected at a single point (single-point ground). Furthermore, the location of the single-point ground should be as close to the LC89210 as is possible. AGNDR and AGNDT should be connected to the single-point ground location with an extremely low impedance.

- 2. 2-layer boards

Supply the ground grid to all empty spaces and the inner side of component spaces.

- 3. The 2.2 nF capacitors connected to the RXA1 and RXA2 pins should be located as close to the pins as possible.

- 4. The two 100 nF capacitors connected to the V<sub>REFP</sub> and V<sub>REFN</sub> pins should be located as close to the pins as possible.

- 5. To prevent latchup due to differences in power on timing between the analog and digital power supplies, insert two diodes with reverse polarities in parallel between the  $V_{DD}$  (digital) and  $AV_{DD}$  (analog) power supplies.

### **Application Example**

Note: The capacitors marked with asterisks (\*) must be connected as close as possible to the LC89210 pins. Signal names ending in "I" are active low signals.

If it is necessary to supply current to V<sub>CM</sub>, add the resistors R3, R4, R5, and R6.

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of December, 1997. Specifications and information herein are subject to change without notice.