# Four-Bit CMOS Microcontrollers for Small-Scale Control Applications

## Overview

The LC651431N/F/L and LC651432N/F/L are the small-scale control models in Sanyo's LC6500 Series of 4-bit microcontrollers and feature the same basic architecture and instruction set. These microcontrollers are appropriate for a wide range of applications, from applications that require only a limited number of circuits and controls and were previously implemented in standard logic to larger application such as audio equipment, including tape decks and disc players, office equipment, communication equipment, automotive equipment, and home appliances. Furthermore, since these products have equivalent basic functions (although there are differences in some functions and characteristics) and are pin compatible with the earlier LC6543N/F/L and LC6546N/F/L products, they can be used to replace those devices.

## **Features**

- Fabricated in a CMOS process for low power operation (Standby mode can be controlled by CPU instructions.)

- ROM/RAM

LC651432N/F/L

—ROM:  $2 \text{ K} \times 8 \text{ bits}$ , RAM:  $128 \times 4 \text{ bits}$

LC651431N/F/L

—ROM: 1 K  $\times$  8 bits, RAM: 64  $\times$  4 bits

- Instruction set: The 80-instruction set common to the whole LC6500 Series

- Wide operating supply voltage range of 2.2 to 6.0 V (L versions)

- Instruction cycle time of 0.92  $\mu s$  (F versions)

- On-chip serial I/O function

Highly flexible I/O ports Number of ports

— 7 ports (Up to 25 pins)

All ports

- Can be used for either input or output

- Voltage handling capability (input and output):

15 V maximum (For open-drain specification ports)

- Output current: 20 mA maximum sink current (Capable of directly driving an LED.)

I/O port options to match application requirements:

- Open-drain output and pull-up resistor specification:

Can be specified for all ports in bit units.

- Output level at reset specification: Either a high or low level can be specified for ports C and D in 4-bit units each.

- Interrupts

Timer overflow vector interrupt (can also be tested by CPU instructions)

INT pin or serial I/O full/empty vector interrupt (can also be tested by CPU instructions)

- Stack levels: 4 levels (also used by interrupts)

- Timers: 8-bit programmable timer with 4-bit prescaler

- Clock oscillator options to match application requirements:

Oscillator circuit option:

- Two-pin RC oscillator (N and L versions)

Two-pin ceramic oscillator or single external clock input pin (N, F, and L versions)

- Divider circuit option: No divider, built-in divideby-three circuit, built-in divide-by-four circuit (N and L versions)

- Continuous square-wave output with a period 64 times the cycle time.

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

SANYO Electric Co.,Ltd. Semiconductor Company

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

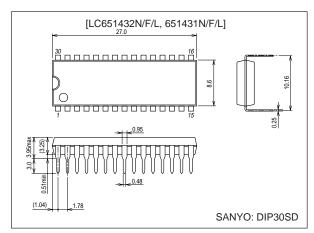

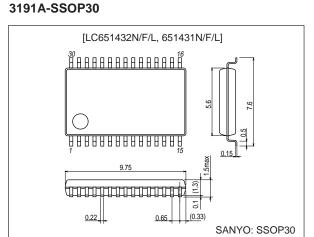

# **Package Dimensions**

unit: mm

## 3196A-DIP30SD

unit: mm

unit: mm

## 3216B-MFP30S

## **Function Overview**

| P                 | arameter               | LC651432N/1431N                                                                                     | LC651432F/1431F                                        | LC651432L/1431L                                                             |  |  |  |  |

|-------------------|------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------|--|--|--|--|

| Memory            | ROM                    |                                                                                                     | 2048 × 8 bits (1432N/F/L)<br>1024 × 8 bits (1431N/F/L) |                                                                             |  |  |  |  |

| wemory            | RAM                    |                                                                                                     | 128 × 4 bits (1432N/F/L)<br>64 × 4 bits (1431N/F/L)    |                                                                             |  |  |  |  |

| Instructions      | Instruction set        |                                                                                                     | 80                                                     |                                                                             |  |  |  |  |

| Instructions      | Table reference        |                                                                                                     | Provided                                               |                                                                             |  |  |  |  |

|                   | Interrupts             |                                                                                                     | One external, one internal                             |                                                                             |  |  |  |  |

|                   | Timers                 |                                                                                                     | 8-bit timer with 4-bit prescaler                       |                                                                             |  |  |  |  |

| On-chip functions | Stack levels           |                                                                                                     | 4                                                      |                                                                             |  |  |  |  |

|                   | Standby function       | HALT instruction based<br>standby function<br>Provided                                              |                                                        |                                                                             |  |  |  |  |

|                   | Number of ports        | Up to 25 I/O pins                                                                                   |                                                        |                                                                             |  |  |  |  |

|                   | Serial ports           | I/O in 4-bit or 8-bit units                                                                         |                                                        |                                                                             |  |  |  |  |

|                   | I/O voltage            | 15 V max.                                                                                           |                                                        |                                                                             |  |  |  |  |

| I/O ports         | Output current         | 10 mA typ. 20 mA max.                                                                               |                                                        |                                                                             |  |  |  |  |

|                   | I/O circuit types      | Open drain (n channel) or built-in pull-up resistor output can be specified in 1-bit units.         |                                                        |                                                                             |  |  |  |  |

|                   | Output level at reset  | High or low can be specified in port units (C and D ports only)                                     |                                                        |                                                                             |  |  |  |  |

|                   | Square-wave output     |                                                                                                     | Possible                                               |                                                                             |  |  |  |  |

|                   | Minimum cycle time     | 2.77 µs (V <sub>DD</sub> ≥ 3 V)                                                                     | 0.92 μs (V <sub>DD</sub> ≥ 3 V)                        | 3.84 µs (V <sub>DD</sub> ≥ 2.2 V)                                           |  |  |  |  |

| Characteristics   | Supply voltage         | 3 to 6 V                                                                                            | 3 to 6 V                                               | 2.2 to 6 V                                                                  |  |  |  |  |

|                   | Supply current         | 1 mA typ.                                                                                           | 1.5 mA typ.                                            | 1 mA typ.                                                                   |  |  |  |  |

| Oscillator        | Oscillator element     | RC oscillator (400 or 800 kHz typical)<br>Ceramic oscillator (400 kHz,<br>800 kHz, 1 MHz, or 4 MHz) | Ceramic oscillator: 4 MHz                              | RC oscillator (400 kHz typical)<br>Ceramic oscillator (400 kHz<br>or 4 MHz) |  |  |  |  |

|                   | Divider circuit option | 1/1, 1/3, 1/4                                                                                       | 1/1                                                    | 1/1, 1/3, 1/4                                                               |  |  |  |  |

| Other features    | Package                |                                                                                                     | DIP30S-D, MFP30S,<br>SSOP30                            |                                                                             |  |  |  |  |

Note: Sanyo will be providing details on oscillator elements and oscillator circuit constants as recommended circuits are developed. Contact your Sanyo representative for more information.

## Differences between the LC651432N/LC651431N and the LC6543N/LC6546N

This table lists the points that require care when replacing the LC6543N/LC6546N with the LC651432N/LC651431N in completes end products.

| Parameter                                                                                                   |                                    | LC651432N/1431N                                                                                                                                | LC6543N/46N                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                             | Pdmax(1) : DIP                     | 310 mW                                                                                                                                         | 250 mW                                                                                                                                                    |

| Allowable power dissipation                                                                                 | Pdmax(2) : MFP                     | 220 mW                                                                                                                                         | 150 mW                                                                                                                                                    |

|                                                                                                             | Pdmax(3) : SSOP                    | 160 mW                                                                                                                                         | (This package not available.)                                                                                                                             |

| I/O voltage (PIO)                                                                                           | V <sub>IO</sub> (3) added          | -0.3 to V <sub>DD</sub> + 0.3                                                                                                                  | -0.3 to +15 V (When open-drain output is used.)                                                                                                           |

| 1/O voltage (FIO)                                                                                           | V <sub>IO</sub> (3) added          | -0.3 to V <sub>DD</sub> + 0.3                                                                                                                  | -0.3 to V <sub>DD</sub> + 0.3 (When a pull-up resistor is used.)                                                                                          |

| High-level input voltage                                                                                    | V <sub>IH</sub> (n)                | V <sub>IH</sub> (1) to V <sub>IH</sub> (7) (Associated with the I/O voltage (PI0) changes mentioned above.)                                    | V <sub>IH</sub> (1) to V <sub>IH</sub> (6)                                                                                                                |

| High-level input current I <sub>IH</sub> (n)                                                                |                                    | I <sub>IH</sub> (1) to I <sub>IH</sub> (3)<br>(Associated with the I/O voltage (PI0)<br>changes mentioned above.)                              | I <sub>IH</sub> (1) to I <sub>IH</sub> (2)                                                                                                                |

|                                                                                                             | f <sub>CFOSC</sub><br>[OSC1, OSC2] | Oscillator frequency precision: ±2%<br>Recommended oscillator circuit constants<br>(under evaluation)                                          | Oscillator frequency precision: ±4%                                                                                                                       |

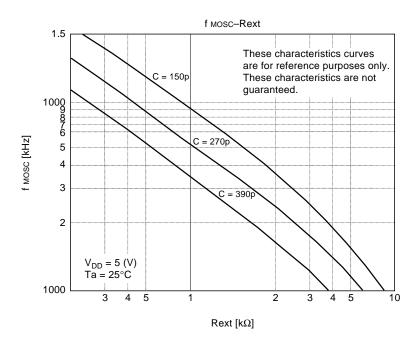

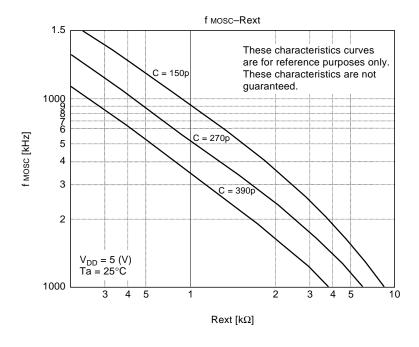

| Oscillator characteristics Ceramic oscillator Oscillator frequency 2-pin RC oscillator Oscillator frequency | f <sub>MOSC</sub>                  | 800 kHz typical (V <sub>DD</sub> = 3 to 6 V) Circuit constant changes: Rext = 6.8 kΩ ±1% Sample-to-sample frequency variation: 595 to 1274 kHz | 850 kHz typical ( $V_{DD}$ = 4 to 6 V)<br>Circuit constant changes: Rext = 4.7 k $\Omega$ ±1%<br>Sample-to-sample frequency variation:<br>619 to 1144 kHz |

| Oscillator frequency                                                                                        | [0301, 0302]                       | 400 kHz typical (V <sub>DD</sub> = 3 to 6 V)<br>Sample-to-sample frequency variation:<br>284 to 790 kHz                                        | 400 kHz typical (V <sub>DD</sub> = 3 to 6 V)<br>Sample-to-sample frequency variation:<br>305 to 546 kHz                                                   |

| Current drain                                                                                               | I <sub>DD</sub>                    | 1 mA typ.                                                                                                                                      | 2 mA typ.                                                                                                                                                 |

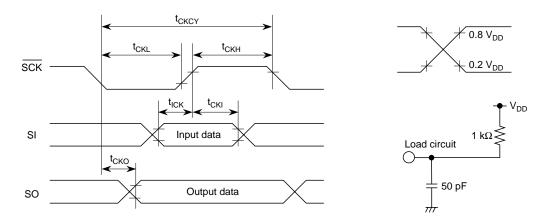

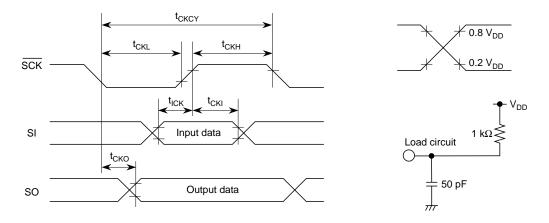

| Serial clock input clock cycle time                                                                         | t <sub>CKCY</sub> (1)[SCK]         | min. 2.0 μs                                                                                                                                    | min 3.0 μs                                                                                                                                                |

| Package                                                                                                     |                                    | DIP30S-D, MFP30S,<br>SSOP30 added                                                                                                              | DIP30S-D, MFP30S                                                                                                                                          |

## Differences between the LC651432F/LC651431F and the LC6543F/LC6546F

This table lists the points that require care when replacing the LC6543F/LC6546F with the LC651432F/LC651431F in completes end products.

| Parameter                                                                                |                                                                                                                                                              | LC651432F/1431F                                                                                                       | LC6543F/46F                                                      |  |

|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|

|                                                                                          | Pdmax(1) : DIP                                                                                                                                               | 310 mW                                                                                                                | 250 mW                                                           |  |

| Allowable power dissipation                                                              | Pdmax(2) : MFP                                                                                                                                               | 220 mW                                                                                                                | 150 mW                                                           |  |

|                                                                                          | Pdmax(3) : SSOP                                                                                                                                              | 160 mW                                                                                                                | (This package not available.)                                    |  |

| Operating supply voltage V <sub>DD</sub>                                                 |                                                                                                                                                              | 3 to 6 V                                                                                                              | 4.5 to 6 V                                                       |  |

| I/O voltage (PI0)                                                                        | V <sub>IO</sub> (3) added                                                                                                                                    | -0.3 to V <sub>DD</sub> + 0.3                                                                                         | -0.3 to +15 V (When open-drain output is used.)                  |  |

| 1/O voltage (F10)                                                                        | V <sub>IO</sub> (3) added                                                                                                                                    | -0.3 to V <sub>DD</sub> + 0.3                                                                                         | -0.3 to V <sub>DD</sub> + 0.3 (When a pull-up resistor is used.) |  |

| High-level input voltage $V_{IH}(n)$                                                     |                                                                                                                                                              | $V_{IH}(1)$ to $V_{IH}(7)$ (Associated with the I/O voltage (PI0) changes mentioned above.)                           | V <sub>IH</sub> (1) to V <sub>IH</sub> (6)                       |  |

| High-level input current                                                                 | $I_{IH}(1) \text{ to } I_{IH}(3)$ ligh-level input current $I_{IH}(n) \qquad \qquad \text{(Associated with the I/O voltage (PI0)}$ changes mentioned above.) |                                                                                                                       | I <sub>IH</sub> (1) to I <sub>IH</sub> (2)                       |  |

| Low-level input voltage V <sub>IL</sub> (n)                                              |                                                                                                                                                              | $I_{IH}(1)$ to $I_{IH}(3)$<br>Specifications when $V_{DD} = 4$ to 6 V<br>Specifications added for $V_{DD} = 3$ to 6 V | Specifications when V <sub>DD</sub> = 4 to 6 V                   |  |

| Oscillator characteristics Ceramic oscillator Oscillator frequency   fcFosc [OSC1, OSC2] |                                                                                                                                                              | Oscillator frequency precision: ±2%                                                                                   | Oscillator frequency precision: ±4%                              |  |

| Current drain I <sub>DD</sub>                                                            |                                                                                                                                                              | 1.5 mA typ.                                                                                                           | 2.5 mA typ.                                                      |  |

| Serial clock input clock cycle time t <sub>CKCY</sub> (1)[SCK]                           |                                                                                                                                                              | min. 2.0 μs                                                                                                           | min 3.0 μs                                                       |  |

| Package                                                                                  |                                                                                                                                                              | DIP30S-D, MFP30S,<br>SSOP30 added                                                                                     | DIP30S-D, MFP30S                                                 |  |

## Differences between the LC651432L/LC651431L and the LC6543L/LC6546L

This table lists the points that require care when replacing the LC6543L/LC6546L with the LC651432L/LC651431L in completes end products.

| Parameter                                                           | r                                                                                                            | LC651432L/1431L                                                                                                                                   | LC6543L/46L                                                                                                                                               |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                     | Pdmax(1) : DIP                                                                                               | 310 mW                                                                                                                                            | 250 mW                                                                                                                                                    |

| Allowable power dissipation                                         | Pdmax(2) : MFP                                                                                               | 220 mW                                                                                                                                            | 150 mW                                                                                                                                                    |

|                                                                     | Pdmax(3) : SSOP                                                                                              | 160 mW                                                                                                                                            | (This package not available.)                                                                                                                             |

| I/O voltago (PIO)                                                   | V(2) addad                                                                                                   | 0.2 to V 1.0.2                                                                                                                                    | -0.3 to +15 V (When open-drain output is used.)                                                                                                           |

| I/O voltage (PI0)                                                   | V <sub>IO</sub> (3) added                                                                                    | -0.3 to V <sub>DD</sub> + 0.3                                                                                                                     | -0.3 to V <sub>DD</sub> + 0.3 (When a pull-up resistor is used.)                                                                                          |

| High-level input voltage                                            | V <sub>IH</sub> (1) to V <sub>IH</sub> (7)  (Associated with the I/O voltage (PI0) changes mentioned above.) |                                                                                                                                                   | V <sub>IH</sub> (1) to V <sub>IH</sub> (6)                                                                                                                |

| High-level input current                                            | I <sub>IH</sub> (n)                                                                                          | I <sub>IH</sub> (1) to I <sub>IH</sub> (3) (Associated with the I/O voltage (PI0) changes mentioned above.)                                       | I <sub>IH</sub> (1) to I <sub>IH</sub> (2)                                                                                                                |

| Oscillator characteristics Ceramic oscillator                       | f <sub>CFOSC</sub> [OSC1, OSC2]                                                                              | Oscillator frequency precision: ±2%<br>Recommended oscillator circuit constants<br>(under evaluation)                                             | Oscillator frequency precision: ±4%                                                                                                                       |

| Oscillator frequency<br>2-pin RC oscillator<br>Oscillator frequency | f <sub>MOSC</sub><br>[OSC1, OSC2]                                                                            | 400 kHz typical ( $V_{DD}$ = 2.2 to 6 V)<br>Circuit constant changes: Rext = 15 kΩ ±1%<br>Sample-to-sample frequency variation:<br>200 to 790 kHz | 400 kHz typical ( $V_{DD}$ = 2.2 to 6 V)<br>Circuit constant changes: Rext = 12 k $\Omega$ ±1%<br>Sample-to-sample frequency variation:<br>284 to 546 kHz |

| Current drain                                                       | I <sub>DD</sub>                                                                                              | 1 mA typ.                                                                                                                                         | 2 mA typ.                                                                                                                                                 |

| Package                                                             |                                                                                                              | DIP30S-D, MFP30S,<br>SSOP30 added                                                                                                                 | DIP30S-D, MFP30S                                                                                                                                          |

Caution: Always test the end product thoroughly after changing the microcontroller used.

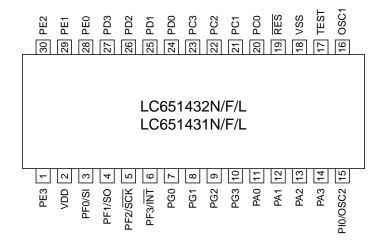

## **Pin Assignment**

The same pin assignment is used for the DIP, MFP, and SSOP packages.

#### Pin Nomenclature

OSC1, OSC2: Connections for capacitor and resistor oscillator components or a ceramic oscillator element.

PG0 to 3: Shared-function I/O port G0 to 3 PI0: Shared-function I/O port IO

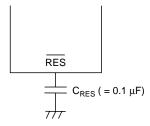

RES: Reset TEST: Test

PA0 to 3: Shared-function I/O port A0 to 3

PC0 to 3: Shared-function I/O port C0 to 3

PD0 to 3: Shared-function I/O port D0 to 3

SI: Serial input

SO: Serial output

PE0 to 3: Shared-function I/O port E0 to 3 SCK: Serial clock input or output pin

PF0 to 3: Shared-function I/O port F0 to 3

Notes: 1. The SI, SO, SCK, and INT pins are shared-function pins also used as PF0 to 3.

2. OSC2 and PIO are a single pin set exclusively to one or the other function as a user option.

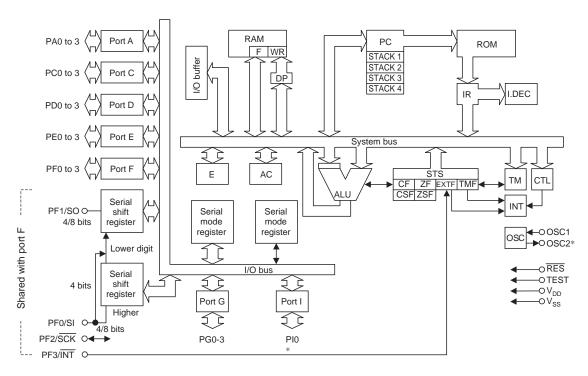

## System Block Diagram

#### LC651432N/F/L, LC651431N/F/L

Note: \* OSC2 and PIO are a single pin set exclusively to one or the other function as a user option.

RAM: Data memory ROM: Program memory F: Flags PC: Program counter WR: Working register INT: Interrupt control AC: Accumulator IR: Instruction register ALU: Arithmetic and logic unit Instruction decoder I.DEC: DP: Data pointer CF, CSF: Carry flag, carry save flag E register E: ZF, ZSF: Zero flag, zero save flag CTL: Control register EXTF: External interrupt request flag OSC: Oscillator circuit TMF: Internal interrupt request flag

TM: Timer

STS: Status register

## **Development Support**

The following are available to support the development of LC651431 and LC651432 applications.

• User's manual

"LC6543/46 User's Manual" No. E71

• Development tool manual

See the "EVA86000 Development Tool Manual for 4-Bit Microcontrollers."

• Software manual

"LC65/66 Series Software Manual"

• Development tools

Program development: EVA86000 System

Program evaluation: LC65E43 on-chip EPROM microcontroller

## **Pins Functions**

| Count | Pin             | I/O   | Function                                                                                                                                                                                                                                                                                                                                                                                                                       | Options                                                                                                                                                                                                               | Reset state                                                               | Handling when unused                                                                     |

|-------|-----------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| 1     | V <sub>DD</sub> | _     | Power supply                                                                                                                                                                                                                                                                                                                                                                                                                   | _                                                                                                                                                                                                                     | _                                                                         | _                                                                                        |

| 1     | V <sub>SS</sub> | _     |                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                       |                                                                           |                                                                                          |

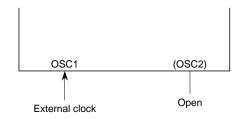

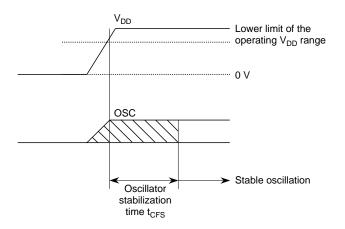

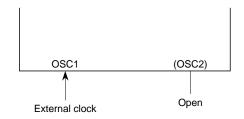

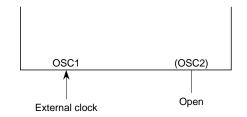

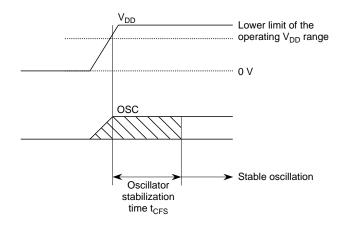

| 1     | OSC1            | Input | Connection for the external system clock RC or ceramic oscillator element  Mhen a single pin is used for external clock input, the PI0/OSC2 pin is used as the PI0 I/O port.  Mhen a 2-pin RC oscillator or a 2-pin ceramic oscillator is used, the PI0/OSC2 pin is used as the OSC2 oscillator pin.                                                                                                                           | Single-pin external clock input     Z-pin RC oscillator     Z-pin ceramic oscillator     Divider circuit option     No divider     Divide-by-three circuit     Divide-by-four circuit                                 |                                                                           |                                                                                          |

| 4     | PA0 to PA3      | I/O   | I/O port A0 to 3 Input in 4-bit units (IP instruction) Output in 4-bit units (OP instruction) Test in single-bit units (BP and BNP instructions) Set/reset in single-bit units (SPB and RPB instructions) PA3 (Any one of PA0 to 3 can be selected) is used for standby mode control. Applications must assure that key bounce or similar noise does not occur on PA3 (or PA0 to 3) during a HALT instruction execution cycle. | Open-drain output     Built-in pull-up resistor     Options 1 and 2 may be specified in bit units.                                                                                                                    | High-level<br>output (with<br>the output n-<br>channel<br>transistor off) | The open-drain output option must be selected and the pin connected to V <sub>SS</sub> . |

| 4     | PC0 to PC3      | I/O   | I/O port C0 to 3     Provides the same functions as PA0 to 3.     (See note.)     The output level at reset can be specified to be either high or low.     Note: This port does not have the standby mode control function.                                                                                                                                                                                                    | 1. Open-drain output 2. Built-in pull-up resistor 3. High-level output at reset 4. Low-level output at reset • Options 1 and 2 may be specified in bit units. • Options 3 and 4 are specified in a single 4-bit group | High-level output     Low-level output     (Specified as a user option.)  | The same as that for PC0 to 3                                                            |

| 4     | PD0 to PD3      | I/O   | I/O port D0 to 3     Provides the same functions as PC0 to 3.                                                                                                                                                                                                                                                                                                                                                                  | The same as those for PC0 to 3.                                                                                                                                                                                       | The same as those for PC0 to 3.                                           | The same as those for PC0 to 3.                                                          |

## Continued from preceding page.

| Count | Pin                                    | I/O           | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Options                                                                                            | Reset state                                                                                 | Handling when<br>unused                         |

|-------|----------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------|

| 4     | PE0 to PE3                             | I/O           | I/O port E0 to 3 Input in 4-bit units (IP instruction) Output in 4-bit units (OP instruction) Set/reset in single-bit units (SPB and RPB instructions) Test in single-bit units (BP and BNP instructions) PE0 also has a continuous pulse (64Tcyc) output function.                                                                                                                                                                                                            | Open-drain output     Built-in pull-up resistor     Options 1 and 2 may be specified in bit units. | High-level<br>output (with<br>the output n-<br>channel<br>transistor off)                   | The same as that for PA0 to 3.                  |

| 4     | PF0/SI<br>PF1/SO<br>PF2/SCK<br>PF3/INT | I/O           | I/O port F0 to 3 Functions and options identical to PE0 to 3. (See note.) PF0 to 3 have shared functions as the serial interface pins and the INT input. Either function can be selected under program control. SI Serial input port SO Serial output port SCK Serial clock input or output INT Interrupt request input Serial input/output is switched between 4-bit and 8-bit units under program control. Note: This port does not have a continuous pulse output function. | The same as those for PE0 to 3.                                                                    | The same as that for PE0 to 3. The serial port is disabled and INT is the interrupt source. | The same as that for PA0 to 3.                  |

| 4     | PG0 to PG3                             | I/O           | I/O port G0 to 3     Functions and options identical to PE0 to 3.     (See note.)     Note: This port does not have a continuous pulse output function.                                                                                                                                                                                                                                                                                                                        | The same as those for PE0 to 3.                                                                    | The same as those for PE0 to 3.                                                             | The same as that for PA0 to 3.                  |

| 1     | PI0/OSC2                               | I/O<br>Output | I/O port IO     Functions and options identical to PG0 to 3.     However, consists of a single bit.     When a 2-pins oscillator is used, this pin functions as the OSC2 pin, and the I/O port function is not available.                                                                                                                                                                                                                                                      | The same as those for PG0 to 3.                                                                    | The same as those for PG0 to 3.                                                             | The same as that for PA0 to 3.                  |

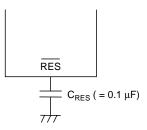

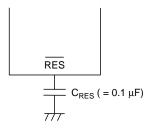

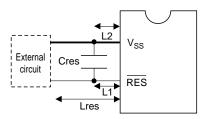

| 1     | RES                                    | Input         | System reset input     Connect an external capacitor to implement a power-on reset.     The reset start operation requires that a low level be held for at least 4 clock cycles.                                                                                                                                                                                                                                                                                               | _                                                                                                  | _                                                                                           | _                                               |

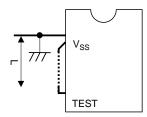

| 1     | TEST                                   | Input         | IC test pin     This pin must be connected to V <sub>SS</sub> during normal operation.                                                                                                                                                                                                                                                                                                                                                                                         | _                                                                                                  | _                                                                                           | This pin must be connected to V <sub>SS</sub> . |

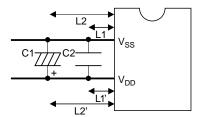

## **Oscillator Circuit Options**

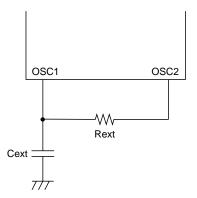

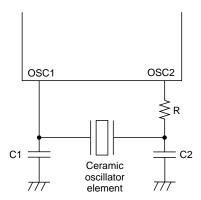

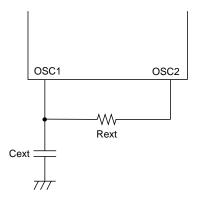

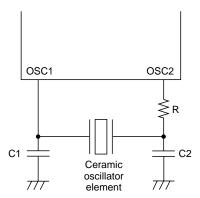

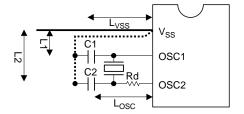

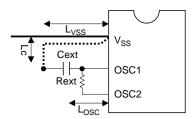

| Option                | Circuit                                   | Conditions and notes                                                           |

|-----------------------|-------------------------------------------|--------------------------------------------------------------------------------|

| External clock        | OSC1 CONTRACTOR OSC1                      | The PI0/OSC2 pin is used as the PI0 pin.                                       |

| Two-pin RC oscillator | Cext OSC1 PI0/OSC Rext                    | The PI0/OSC2 pin is used as the OSC2 pin and the port function is unavailable. |

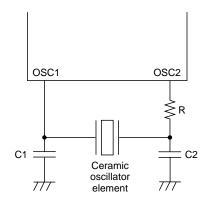

| Ceramic oscillator    | C1 OSC1  Ceramic oscillator element  C2 R | The PI0/OSC2 pin is used as the OSC2 pin and the port function is unavailable. |

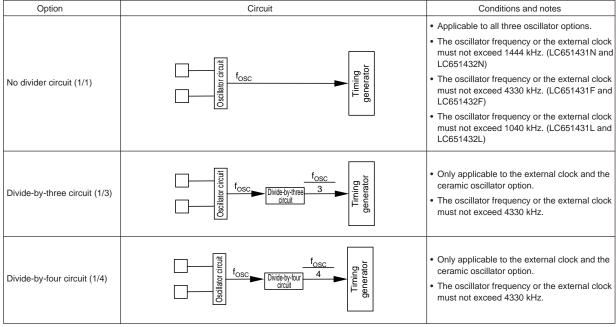

## **Divider Circuit Options**

Caution: The following table summarizes the oscillator and divider option combinations. Use care when selecting these options.

# Oscillator Divider Options for the LC651431N/LC651432N, LC651431F/LC651432F, and LC651431L/LC651432L

## LC651432N, LC651431N

| Oscillator type                                          | Frequency                                                   | Divider option (cycle time)                                                                                                                                                   | V <sub>DD</sub> range | Notes                                                           |  |

|----------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------|--|

| Ceramic oscillator                                       | 400 kHz                                                     | 1/1 (10 μs)                                                                                                                                                                   | 3 to 6 V              | The divide-by-three and divide-by-four circuits cannot be used. |  |

|                                                          | 800 kHz                                                     | 1/1 (5 µs)                                                                                                                                                                    | 3 to 6 V              |                                                                 |  |

|                                                          |                                                             | 1/3 (15 µs)                                                                                                                                                                   | 3 to 6 V              |                                                                 |  |

|                                                          |                                                             | 1/4 (20 µs)                                                                                                                                                                   | 3 to 6 V              |                                                                 |  |

|                                                          | 1 MHz                                                       | 1/1 (4 µs)                                                                                                                                                                    | 3 to 6 V              |                                                                 |  |

|                                                          |                                                             | 1/3 (12 µs)                                                                                                                                                                   | 3 to 6 V              |                                                                 |  |

|                                                          |                                                             | 1/4 (16 µs)                                                                                                                                                                   | 3 to 6 V              |                                                                 |  |

|                                                          | 4 MHz                                                       | 1/3 (3 µs)                                                                                                                                                                    | 3 to 6 V              | The no-divider (1/1) option cannot be used.                     |  |

|                                                          |                                                             | 1/4 (4 µs)                                                                                                                                                                    | 3 to 6 V              |                                                                 |  |

| Single-pin external clock input                          | 200 to 1444 kHz                                             | 1/1 (20 to 2.77 µs)                                                                                                                                                           | 3 to 6 V              |                                                                 |  |

|                                                          | 600 to 4330 kHz                                             | 1/3 (20 to 2.77 µs)                                                                                                                                                           | 3 to 6 V              |                                                                 |  |

|                                                          | 800 to 4330 kHz                                             | 1/4 (20 to 3.70 µs)                                                                                                                                                           | 3 to 6 V              |                                                                 |  |

| External clock provided by a 2-pin RC oscillator circuit | As above                                                    |                                                                                                                                                                               |                       |                                                                 |  |

| 2-pin RC oscillator                                      | recommended circu values other than th frequencies, divider | (1/1) option and the it constants. If the use of circuit e recommended values is unavoi options, and V <sub>DD</sub> ranges specifie lock input option must be strictly       |                       |                                                                 |  |

| External clock used with the ceramic oscillator option   |                                                             | The IC cannot be driven by an external clock with this option. If external clock drive is required, select either the external clock option or the 2-pin RC oscillator option |                       |                                                                 |  |

## LC651432F, LC651431F

| Oscillator type                                         | Frequency                    | Divider option (cycle time)        | V <sub>DD</sub> range | Notes                                              |

|---------------------------------------------------------|------------------------------|------------------------------------|-----------------------|----------------------------------------------------|

| Ceramic oscillator                                      | 4 MHz                        | 1/1 (1 µs)                         | 3 to 6 V              |                                                    |

| Single-pin external clock input                         | 200 to 4330 kHz              | 1/1 (20 to 0.92 µs)                | 3 to 6 V              |                                                    |

| External clock used with the ceramic oscillator circuit | The IC cannot be drivoption. | ven by an external clock with this | option. If external   | clock drive is required, select the external clock |

## LC651432L, LC651431L

| Oscillator type                                          | Frequency                                                           | Divider option (cycle time)                                                                                                                                             | V <sub>DD</sub> range | Notes                                                           |

|----------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------|

| Ceramic oscillator                                       | 400 kHz                                                             | 1/1 (10 µs)                                                                                                                                                             | 2.2 to 6 V            | The divide-by-three and divide-by-four circuits cannot be used. |

|                                                          | 4 MHz                                                               | 1/4 (4 µs)                                                                                                                                                              | 2.2 to 6 V            | The no-divider (1/1) and divide-by-three option cannot be used. |

| Single-pin external clock input                          | 200 to 1040 kHz                                                     | 1/1 (20 to 3.84 µs)                                                                                                                                                     | 2.2 to 6 V            |                                                                 |

|                                                          | 600 to 3120 kHz                                                     | 1/3 (20 to 3.84 µs)                                                                                                                                                     | 2.2 to 6 V            |                                                                 |

|                                                          | 800 to 4160 kHz                                                     | 1/4 (20 to 3.84 µs)                                                                                                                                                     | 2.2 to 6 V            |                                                                 |

| External clock provided by a 2-pin RC oscillator circuit | As above                                                            |                                                                                                                                                                         |                       |                                                                 |

| 2-pin RC oscillator                                      | recommended circui<br>values other than the<br>frequencies, divider | (1/1) option and the it constants. If the use of circuit e recommended values is unavoi options, and V <sub>DD</sub> ranges specifie lock input option must be strictly |                       |                                                                 |

| External clock used with the ceramic oscillator option   |                                                                     | iven by an external clock with this -pin RC oscillator option                                                                                                           | s option. If external | clock drive is required, select either the external             |

## Port C and D Output Level at Reset Option

One of the following two options for the output level at reset may be chosen for the I/O ports C and D in 4-bit group units.

| Option                     | Conditions and notes         |

|----------------------------|------------------------------|

| High-level output at reset | Ports C and D in 4-bit units |

| Low-level output at reset  | Ports C and D in 4-bit units |

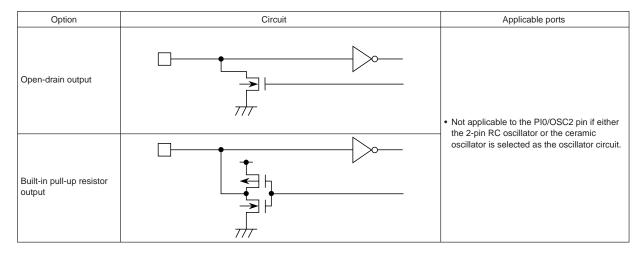

## **Port Output Circuit Type Option**

One of the following two options for the circuit type can be selected for the I/O ports in bit units.

# **Specifications**

# LC651432N, 651431N

Absolute Maximum Ratings at  $Ta=25^{\circ}C,\,V_{SS}=0~V$

| Parameter                   | Symbol               | Conditions                                                    | Applicable pins                            | Ratings                                           | Unit |

|-----------------------------|----------------------|---------------------------------------------------------------|--------------------------------------------|---------------------------------------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max  |                                                               | V <sub>DD</sub>                            | -0.3 to +7.0                                      | V    |

| Output voltage              | Vo                   |                                                               | OSC2                                       | Voltages up to the voltage generated are allowed. | V    |

| Input voltage               | V <sub>I</sub> (1)   |                                                               | OSC1 *1                                    | -0.3 to V <sub>DD</sub> +0.3                      | V    |

| Input voltage               | V <sub>I</sub> (2)   |                                                               | TEST, RES                                  | -0.3 to V <sub>DD</sub> +0.3                      | V    |

|                             | V <sub>IO</sub> (1)  |                                                               | Ports with open-drain specifications       | -0.3 to +15                                       | V    |

| I/O voltage                 | V <sub>IO</sub> (2)  |                                                               | Ports with pull-up resistor specifications | -0.3 to V <sub>DD</sub> +0.3                      | V    |

|                             | V <sub>IO</sub> (3)  |                                                               | PI0                                        | -0.3 to V <sub>DD</sub> +0.3                      | V    |

| Peak output current         | I <sub>OP</sub>      |                                                               | I/O ports                                  | -2 to +20                                         | mA   |

|                             | I <sub>OA</sub>      | Per single pin, the average over a 100 ms period              | I/O ports                                  | -2 to +20                                         | mA   |

| Average output current      | Σl <sub>OA</sub> (1) | The total current for PC0 to 3,<br>PD0 to 3, and PE0 to 3*2   | PC0 to 3<br>PD0 to 3<br>PE0 to 3           | -15 to +100                                       | mA   |

|                             | Σl <sub>OA</sub> (2) | The total current for PF0 to 3, PG0 to 3, PA0 to 3, and PI0*2 | PF0 to 3, PI0<br>PG0 to 3<br>PA0 to 3      | -15 to +100                                       | mA   |

|                             | Pd max(1)            | Ta = -40 to +85°C (DIP package)                               |                                            | 310                                               | mW   |

| Allowable power dissipation | Pd max(2)            | Ta = -40 to +85°C (MFP package)                               |                                            | 220                                               | mW   |

|                             | Pd max(3)            | Ta = -40 to +85°C (SSOP package)                              |                                            | 160                                               | mW   |

| Operating temperature       | Topr                 |                                                               |                                            | -40 to +85                                        | ℃    |

| Storage temperature         | Tstg                 |                                                               |                                            | -55 to 125                                        | ℃    |

## Allowable Operating Ranges at Ta = -40 to $+85^{\circ}C$ , $V_{SS} = 0$ V, $V_{DD} = 3.0$ to 6.0 V (unless otherwise specified)

| Parameter                | Symbol              | Conditions                                | Applicable pins                                                | Ratings             |     |          | Unit  |

|--------------------------|---------------------|-------------------------------------------|----------------------------------------------------------------|---------------------|-----|----------|-------|

| Farameter                | Syllibol            | Conditions                                | Applicable piris                                               | min                 | typ | max      | Offic |

| Operating supply voltage | V <sub>DD</sub>     |                                           | V <sub>DD</sub>                                                | 3.0                 |     | 6.0      | V     |

| Standby supply voltage   | V <sub>ST</sub>     | RAM and register contents retained. *3    | V <sub>DD</sub>                                                | 1.8                 |     | 6.0      | V     |

|                          | V <sub>IH</sub> (1) | With the n-channel output transistors off | Ports with open-drain specifications (except for I0)           | 0.7 V <sub>DD</sub> |     | 13.5     | V     |

|                          | V <sub>IH</sub> (2) | With the n-channel output transistors off | Ports with pull-up resistor specifications (except for I0)     | 0.7 V <sub>DD</sub> |     | $V_{DD}$ | V     |

|                          | V <sub>IH</sub> (3) | With the n-channel output transistors off | Port I0                                                        | 0.7 V <sub>DD</sub> |     | $V_{DD}$ | V     |

| High-level input voltage | V <sub>IH</sub> (4) | With the n-channel output transistors off | The INT, SCK, and SI pins with open-drain specifications       | 0.8 V <sub>DD</sub> |     | 13.5     | V     |

|                          | V <sub>IH</sub> (5) | With the n-channel output transistors off | The INT, SCK, and SI pins with pull-up resistor specifications | 0.8 V <sub>DD</sub> |     | $V_{DD}$ | V     |

|                          | V <sub>IH</sub> (6) | V <sub>DD</sub> = 1.8 to 6 V              | RES                                                            | 0.8 V <sub>DD</sub> |     | $V_{DD}$ | V     |

|                          | V <sub>IH</sub> (7) | External clock specifications             | OSC1                                                           | 0.8 V <sub>DD</sub> |     | $V_{DD}$ | V     |

## Continued from preceding page.

| Б                                        | 0 1 1                | 0 1111                                                                                                                                     | A P 11 .        |                 | Ratings            |                      | Unit        |

|------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|--------------------|----------------------|-------------|

| Parameter                                | Symbol               | Conditions                                                                                                                                 | Applicable pins | min             | typ                | max                  | Unit        |

|                                          | V <sub>IL</sub> (1)  | With the n-channel output transistors off VDD = 4 to 6 V                                                                                   | Port            | V <sub>SS</sub> |                    | 0.3 V <sub>DD</sub>  | V           |

|                                          | V <sub>IL</sub> (2)  | With the n-channel output transistors off 3 to 6 V                                                                                         | Port            | V <sub>SS</sub> |                    | 0.25 V <sub>DD</sub> | V           |

|                                          | V <sub>IL</sub> (3)  | With the n-channel output transistors off VDD = 4 to 6 V                                                                                   | ĪNT, SCK, SI    | V <sub>SS</sub> |                    | 0.25 V <sub>DD</sub> | V           |

| Low-level input voltage                  | V <sub>IL</sub> (4)  | With the n-channel output transistors off 3 to 6 V                                                                                         | ĪNT, SCK, SI    | V <sub>SS</sub> |                    | 0.2 V <sub>DD</sub>  | V           |

|                                          | V <sub>IL</sub> (5)  | External clock specifications V <sub>DD</sub> = 4 to 6 V                                                                                   | OSC1            | V <sub>SS</sub> |                    | 0.25 V <sub>DD</sub> | V           |

|                                          | V <sub>IL</sub> (6)  | External clock specifications 3 to 6 V                                                                                                     | OSC1            | V <sub>SS</sub> |                    | 0.2 V <sub>DD</sub>  | V           |

|                                          | V <sub>IL</sub> (7)  | V <sub>DD</sub> = 4 to 6 V                                                                                                                 | TEST            | V <sub>SS</sub> |                    | 0.3 V <sub>DD</sub>  | V           |

|                                          | V <sub>IL</sub> (8)  | 3 to 6 V                                                                                                                                   | TEST            | V <sub>SS</sub> |                    | 0.25 V <sub>DD</sub> | V           |

|                                          | V <sub>IL</sub> (9)  | V <sub>DD</sub> = 4 to 6 V                                                                                                                 | RES             | V <sub>SS</sub> |                    | 0.25 V <sub>DD</sub> | V           |

|                                          | V <sub>IL</sub> (10) | 3 to 6 V                                                                                                                                   | RES             | V <sub>SS</sub> |                    | 0.2 V <sub>DD</sub>  | V           |

| Operating frequency (cycle time)         | fop (Tcyc)           | A clock frequency of up to<br>4.33 MHz may be used when<br>either the divide-by-three<br>circuit or the divide-by-four<br>circuit is used. |                 | 200<br>(20)     |                    | 1444<br>(2.77)       | kHz<br>(µs) |

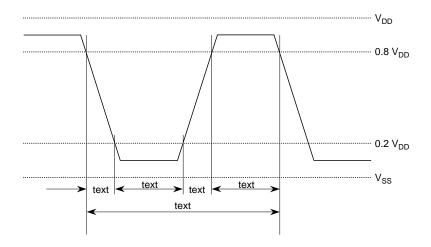

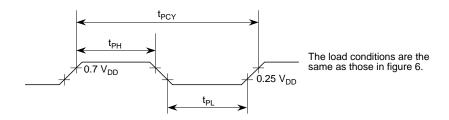

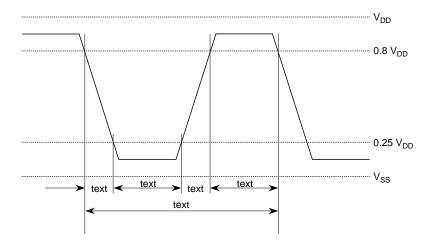

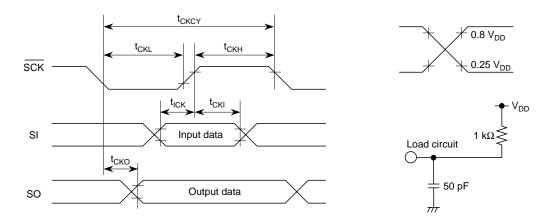

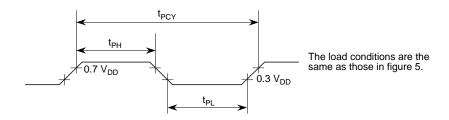

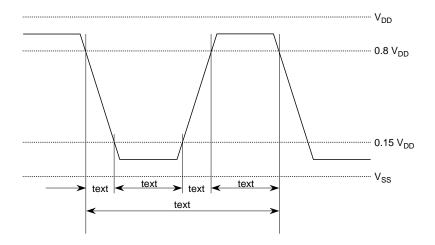

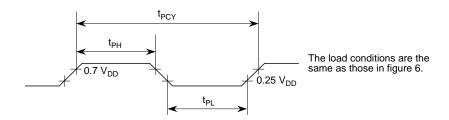

| External clock conditions                |                      | See figure 1.                                                                                                                              |                 |                 |                    |                      |             |

| Frequency                                | text                 | The divide-by-three circuit or                                                                                                             | OSC1            | 200             |                    | 4330                 | kHz         |

| Pulse width                              | textH, textL         | the divide-by-four circuit must be used if the clock                                                                                       | OSC1            | 69              |                    |                      | ns          |

| Rise and fall time                       | textR, textF         | frequency exceeds 1.444<br>MHz.                                                                                                            | OSC1            |                 |                    | 50                   | ns          |

| Recommended oscillator circuit constants |                      |                                                                                                                                            |                 |                 |                    |                      |             |

| Two-pin RC oscillator                    | Cext<br>Rext         | See figure 2.                                                                                                                              | OSC1, OSC2      |                 | 220 ± 5%<br>12 ±1% |                      | pF<br>kΩ    |

|                                          | Cext                 | See figure 2.                                                                                                                              | OSC1, OSC2      |                 | 220 ±5%<br>6.8 ±1% |                      | pF<br>kΩ    |

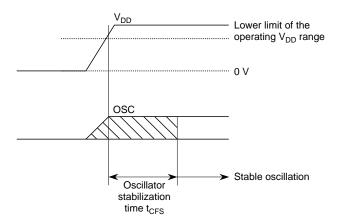

| Ceramic oscillator*4                     |                      | See figure 3.                                                                                                                              |                 |                 | See table 1.       |                      |             |

# $\textbf{Electrical Characteristics at Ta} = -40 \ to \ +85^{\circ}C, \ V_{SS} = 0 \ V, \ V_{DD} = 3.0 \ to \ 6.0 \ V \ (unless \ otherwise \ specified)$

|                          | Parameter                             | Symbol                                                                            | Conditions                                                                                                                                | Applicable pins                                                   |                       | Ratings             |                     | Unit |

|--------------------------|---------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------|---------------------|---------------------|------|

|                          |                                       | -,                                                                                |                                                                                                                                           | ''' '                                                             | min                   | typ                 | max                 |      |

|                          |                                       | I <sub>IH</sub> (1)                                                               | With the output n-channel transistors off (Including the n-channel transistor off leakage current.)     V <sub>IN</sub> = 13.5 V          | Open-drain specification ports<br>(except I0)                     |                       |                     | 5.0                 | μА   |

| High-level input current |                                       | I <sub>IH</sub> (2)                                                               | With the output n-channel transistors off (Including the n-channel transistor off leakage current.)     V <sub>IN</sub> = V <sub>DD</sub> | The I0 port with open-drain specifications                        |                       |                     | 1.0                 | μА   |

|                          |                                       | I <sub>IH</sub> (3)                                                               | External clock mode     V <sub>IN</sub> = V <sub>DD</sub>                                                                                 | OSC1                                                              |                       |                     | 1.0                 | μA   |

|                          |                                       | I <sub>IL</sub> (1)                                                               | With the output n-channel transistors off     V <sub>IN</sub> = V <sub>SS</sub>                                                           | Open-drain specification ports                                    | -1.0                  |                     |                     | μA   |

| Lov                      | v-level input current                 | I <sub>IL</sub> (2)                                                               | With the output n-channel transistors off     V <sub>IN</sub> = V <sub>SS</sub>                                                           | Built-in pull-up resistor specification ports                     | -1.3                  | -0.35               |                     | mA   |

|                          |                                       | I <sub>IL</sub> (3)                                                               | V <sub>IN</sub> = V <sub>SS</sub>                                                                                                         | RES                                                               | -45                   | -10                 |                     | μA   |

|                          |                                       | I <sub>IL</sub> (4)                                                               | External clock mode     V <sub>IN</sub> = V <sub>SS</sub>                                                                                 | OSC1                                                              | -1.0                  |                     |                     | μА   |

| Hin                      | h-level output voltage                | V <sub>OH</sub> (1)                                                               | • I <sub>OH</sub> = -50 μA<br>• V <sub>DD</sub> =4.0 to 6.0 V                                                                             | Built-in pull-up resistor specification ports                     | V <sub>DD</sub> – 1.2 |                     |                     | V    |

|                          |                                       | V <sub>OH</sub> (2)                                                               | • I <sub>OH</sub> = -10 μA                                                                                                                | Built-in pull-up resistor specification ports                     | V <sub>DD</sub> – 0.5 |                     |                     | V    |