Monolithic Linear IC

LA3246

## **Stereo Preamplifier for Compact Double Cassette Playback-only Use**

## **Overview**

The LA3246 is a stereo preamplifier IC for double cassette tape playback-only use. The LA3246 is intended for use in portable radio-cassette tape recorders and tape decks.

## **Applications**

- · Stereo compact cassette player for playback-only use

- · Stereo cassette deck player

# **Functions**

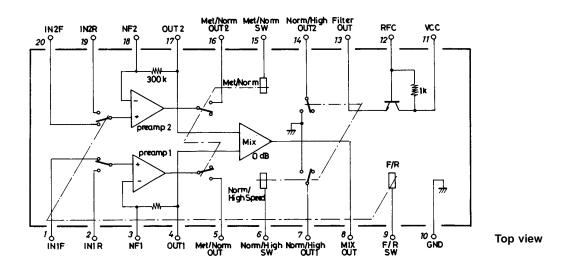

• Preamplifier  $\times 2$ , Mixing amplifier  $\times 1$ , Electronic switch  $\times 6$

## Features

- · On-chip electronic switch for input select (auto reverse or A deck/B deck select)

- · On-chip electronic switch for normal/higher dubbing select and electronic switch for metal/normal tape select

- Wide operating voltage range (V<sub>CC</sub> op = 3.5 to 14 V)

- With output MIX pin (for music select control)

- + Low noise voltage range (V\_{NI} = 0.9 \,\mu\text{V} typ, Rg = 2.2  $k\Omega$ NAB)

- Can be used in conjunction with the LA3240, 3241, 3242 to easily make up a doublecassette dubbing system.

# **Specifications**

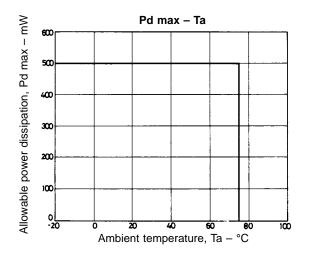

#### Maximum Ratings at $Ta = 25^{\circ}C$

| Parameter                   | Symbol              | Conditions | Ratings     | Unit |

|-----------------------------|---------------------|------------|-------------|------|

| Maximum supply voltage      | V <sub>CC</sub> max |            | 16          | V    |

| Allowable power dissipation | Pd max              |            | 500         | mW   |

| Operating temperature       | Topr                |            | -20 to +75  | °C   |

| Storage temperature         | Tstg                |            | -40 to +125 | °C   |

#### Maxiumum Ratings at $Ta = 25^{\circ}C$

| Parameter                  | Symbol             | Conditions | Ratings   | Unit |

|----------------------------|--------------------|------------|-----------|------|

| Recommended supply voltage | V <sub>CC</sub>    |            | 6         | V    |

| Operating voltage range    | V <sub>CC</sub> op |            | 3.5 to 14 | V    |

SANYO Electric Co., Ltd. Semiconductor Bussiness Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

D3097HA(II)/41594HK/N107TA, TS No.2651-1/13

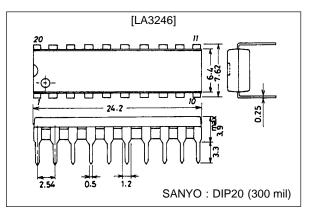

## Package Dimensions

unit : mm

### 3021B-DIP20

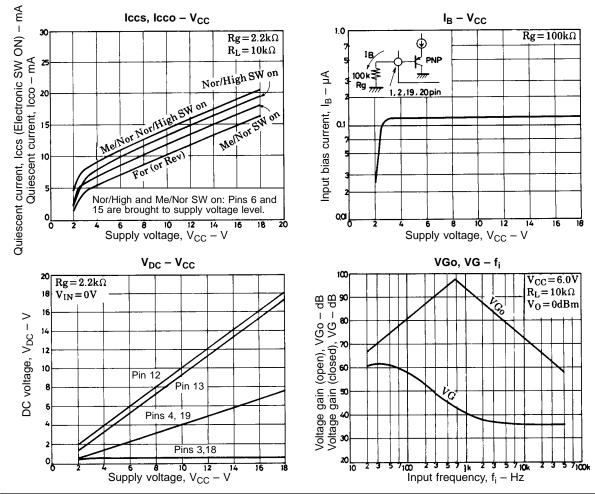

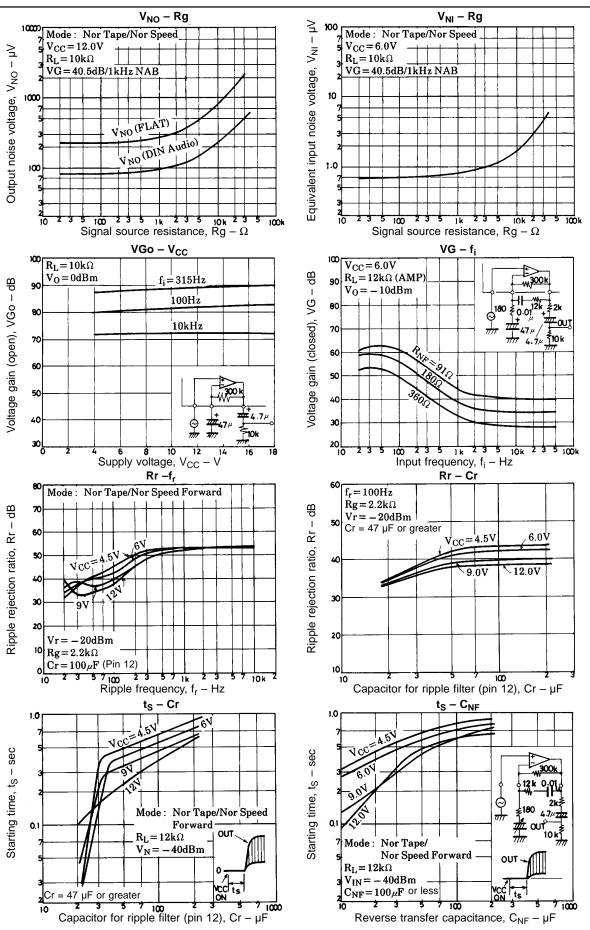

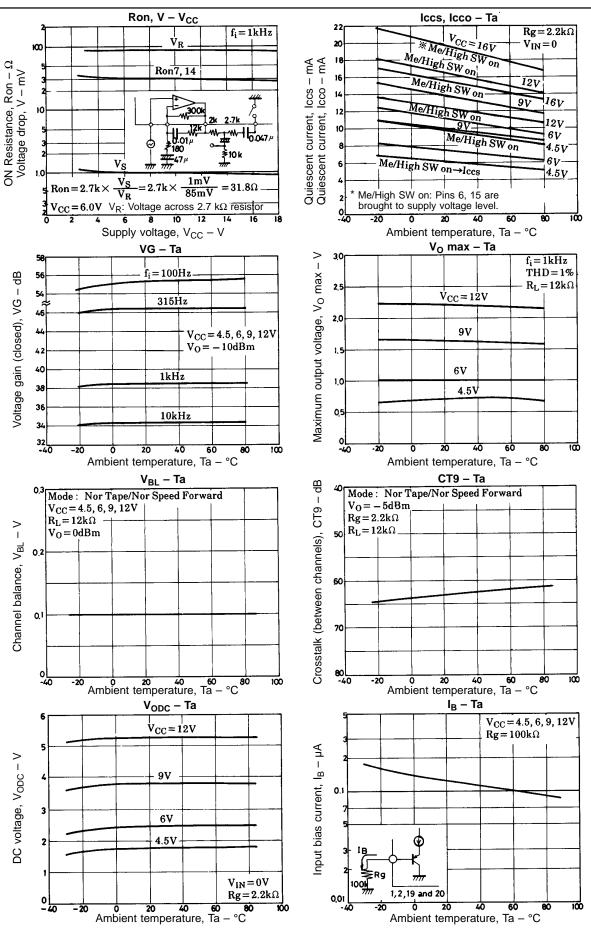

## Operating Characteristics at Ta = 25°C, $V_{CC}$ = 6.0 V, $R_L$ = 10 k $\Omega$ , f = 1 kHz, 0 dB = 0.775 V

| Parameter                      | Symbol             | Conditions                                                                      | min  | typ  | max  | Unit |

|--------------------------------|--------------------|---------------------------------------------------------------------------------|------|------|------|------|

| Quiescent current              | lcco               | Nor/Nor speed forward                                                           | 5    | 7    | 12   | mA   |

| Quescent current               | lccs               | Metal/High speed forward                                                        | 7    | 10   | 17   | mA   |

| Voltage gain (Open)            | VGo                |                                                                                 | 75   | 85   |      | dB   |

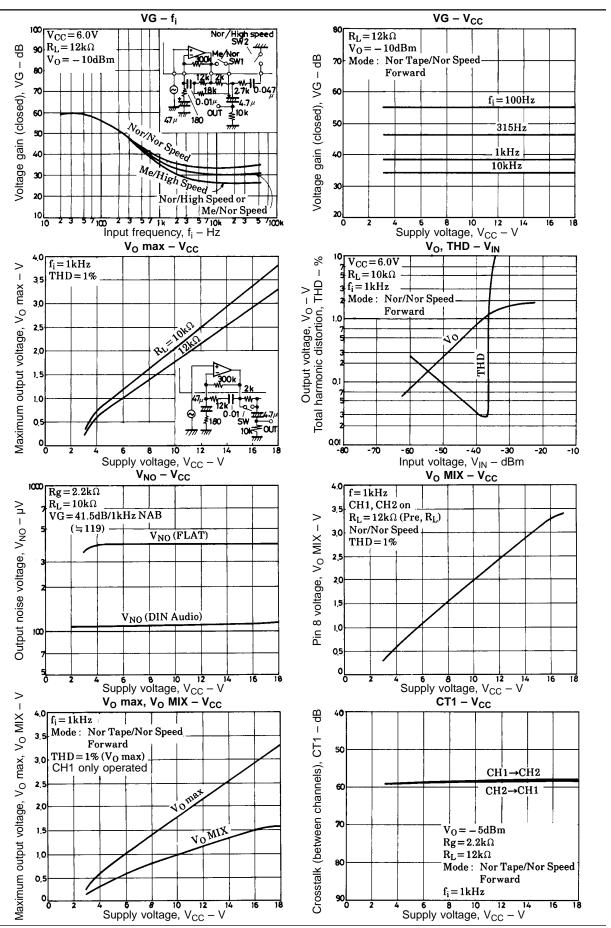

| Voltage gain (Closed)          | VG                 | Nor/Nor speed, NAB                                                              | 39.5 | 40.5 | 41.5 | dB   |

| Total harmonic distortion      | THD                | V <sub>O</sub> = 0.65 V, Nor/Nor speed                                          |      | 0.03 | 0.2  | %    |

| Maximum output voltage         | V <sub>O</sub> max | THD = 1%, Nor/Nor speed                                                         | 0.7  | 1.2  |      | V    |

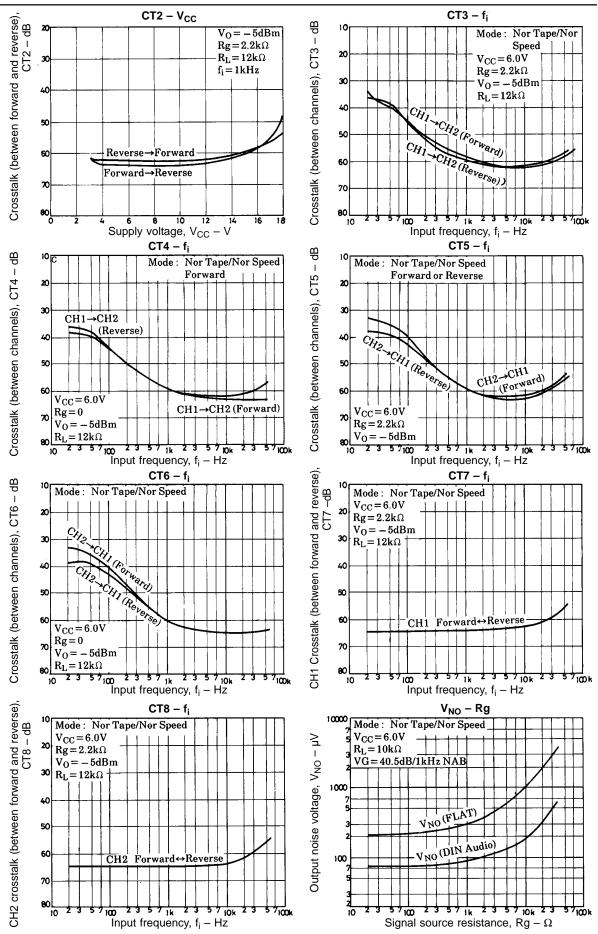

| Crosstalk (between channels)   | CT1                | $V_0 = -5 \text{ dBm}, \text{ Rg} = 2.2 \text{ k}\Omega, \text{ Nor/Nor speed}$ | 50   | 65   |      | dB   |

| Crosstalk (between F/R)        | CT2                | $V_0 = -5 \text{ dBm}, \text{ Rg} = 2.2 \text{ k}\Omega, \text{ Nor/Nor speed}$ | 50   | 65   |      | dB   |

| Channel balance                | V <sub>BL</sub>    | $V_{IN} = -50 \text{ dBm}$                                                      |      | 0    | 2    | dB   |

| Equivalent input noise voltage | V <sub>NI</sub>    | Rg = 2.2 kΩ, B.P.F 20 Hz to 20 kHz, Nor/Nor speed                               |      | 0.9  | 1.7  | μV   |

| MIX output voltage             | V <sub>O</sub> MIX | $V_01, V_02 = 0 \text{ dBm}$                                                    | -3   | 0    | +3   | dB   |

| Ripple filter output current   | I <sub>F OUT</sub> |                                                                                 |      | 10   | 15   | mA   |

| Electronic switch ON-state     | Ron                | Between P1 to P4 and 5, between pin 16 and 17                                   |      | 100  | 250  | Ω    |

| resistance                     | RON                | Between P1 to P7 and 10, between pin 10 and 14                                  |      | 30   | 70   | Ω    |

| DC feedback resistance         | R <sub>F</sub>     |                                                                                 | 240  | 300  | 360  | Ω    |

| Input bias current             | ١ <sub>F</sub>     |                                                                                 |      | 0.5  | 3.0  | μA   |

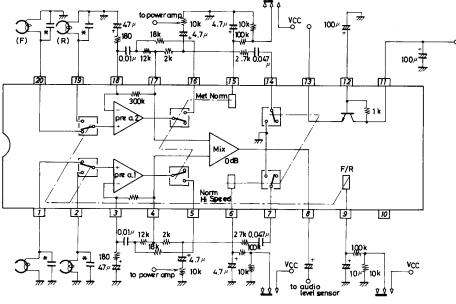

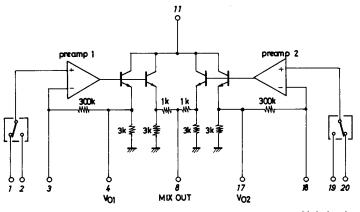

Equivalent Circuit Block Diagram

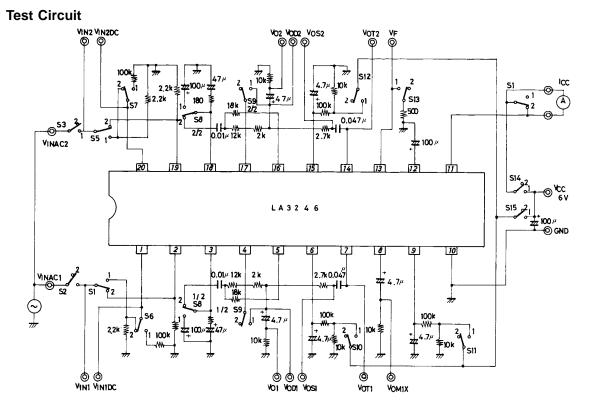

#### **Sample Application Circuit**

Unit (resistance: Ω, capacitance: F)

- Note 1. The output frequency characteristic for Nor Tape/High speed mode (pin 6: High, pin 15: Low) and that for Metal Tape/Nor speed mode (pin 6: Low, pin 15: Low) are set to be the same.

- 2. Since the input bias current flows out of pins 1, 2 and pins 19, 20, a resistor (recommended value:  $30 \text{ k}\Omega$  to  $350 \text{ k}\Omega$ , maximum value:  $500 \text{ k}\Omega$ ) must be connected a coupling capacitor in series with these pins.

- 3. \*: A capacitor must be connected to the input to absorb a surge.

- 4. The electronic select switching level is approximately  $1/2 \times (V_{CC}{-}0.9).$

- 5. The value of the capacitor connected to pin 12 can be increased/decreased to adjust starting time  $t_s$  at the time of application of V<sub>CC</sub>. (C = 100  $\mu$ F,  $t_s$  = 0.4 s.) If the capacitor value is made less than 47  $\mu$ F, the ripple rejection will get worse.

- 6. No capacitor is connected to pin 13. (Even if connected, the ripple can not be rejected.)

- 7. Extreme caution should be exercised when handling the IC as it is subject to dielectric breakdown.

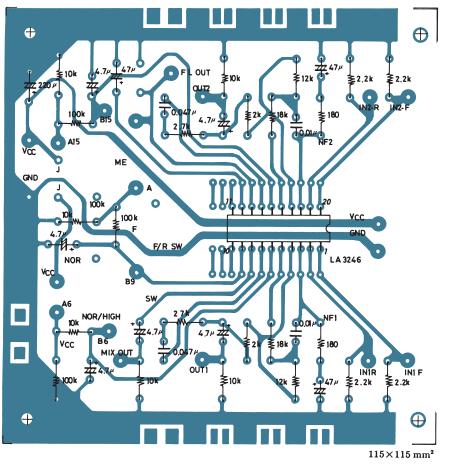

## Sample Printed Circuit Pattern (Cu-foiled area)

Unit (resistance:  $\Omega$ , capacitance: F)

## **IC Usage Notes**

- (1) It is recommended to connect a surge absorbing capacitor across input pins 1, 2 and GND and across input pins 19, 20 and GND.

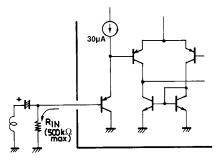

- (2) The base of a PNP transistor is connected to input pins 1, 2 and 19, 20. If an electrolytic capacitor is connected in series with the input pins, connect input resistor  $R_{IN}$  must not exceed 500 k $\Omega$ . (Reason: To minimize the variation in output DC voltage at the time of input switching)

If a resistor of more than 500 k $\Omega$  is connected across input pin and GND, the noise (output) caused by amp 1 and amp 2 select is liable to increase at the time of F/R switching.

(3) When an electrolytic capacitor is connected to input pins 1, 2 (or 23, 24), make the value of  $R_{IN}1$  as equal to that of  $R_{IN}2$  as possible.

The difference in the value between  $R_{IN}1$  and  $R_{IN}2$  causes the variation in amp output DC voltage at the time of F/R switching. Therefore, the input DC voltage (voltage across  $R_{IN}$ ) must be made as equal as possible.

- (4) The amplifier output characteristics are designed to be the same in the Nor Tape/High Speed (pin 15 GND/pin 6 V<sub>CC</sub>) and Me Tape/Nor Speed (pin 15 V<sub>CC</sub>/pin 6 GND) modes. (Refer to sample application circuit, external constants.)

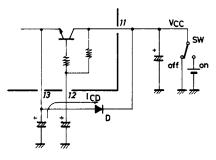

- (5) When externally turning ON/OFF power supply pin 11 (by bringing pin 11 to +V<sub>CC</sub>/GND level) with a capacitor connected to pin 13, connect external diode D, as shown below, so that no breakdown (or deterioration) of the IC system is caused by I<sub>CD</sub> when the switch is turned OFF. When no capacitor is connected to pin 13, diode D is not required.

(6) The output MIX circuit is of the emitter follower configuration as shown below.

Unit (resistance:  $\Omega$ )

The MIX OUT output level V<sub>O</sub> MIX at the time a signal is applied to preamp1 (or preamp2) only is 1/2 as compared with output levels V<sub>O</sub>1, V<sub>O</sub>2 at the time the same input signal is applied to both channels.  $V_O MIX = 1/2$   $V_O 1(= 1/2 \times V_O 2)$ where  $V_O 1 = V_O 2$

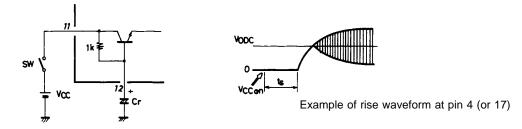

(7) Output waveform starting time

When supply voltage  $V_{CC}$  is switched ON, the amplifier output (pins 4, 17) will rise. Output waveform ON time  $t_s$  can be varied by capacitor Cr connected to pin 12.

Refer to Data Cr – t<sub>s</sub>.

The minimum value of Cr is 47  $\mu$ F.

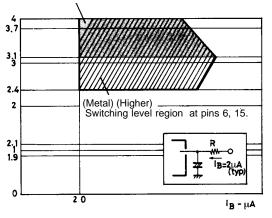

(8) Electronic select switching level

• The switch level at  $V_{CC} = 6.0$  V is shown below.

|     | Pin Switch Mode | Switching Level |                     |               | Control Current                           | Mode    |         |

|-----|-----------------|-----------------|---------------------|---------------|-------------------------------------------|---------|---------|

| Pin |                 | Operation Start | Operation<br>Finish | Clamp Voltage | typ (flow-in)<br>(at operation<br>finish) | (+)     | (-)     |

| 6   | Normal/Metal    | 2.1 V           | 2.4 V               | 3.7 V         | 2 µA                                      | Metal   | Normal  |

| 9   | Forward/Reverse | 2.1 V           | 3.1 V               | 3.4 V         | 2 µA                                      | Reverse | Forward |

| 15  | Normal/Higher   | 2.1 V           | 2.4 V               | 3.7 V         | 2 μΑ                                      | Higher  | Normal  |

As shown above, there is a difference in the switching level at three control pins (6, 9, 15) between operation start and operation finish.

• Switching level and mode at each pin (experimental value)

Switching level (reverse) on pin 9 at  $V_{CC}$  = 6.0 V, Ta = 25°C

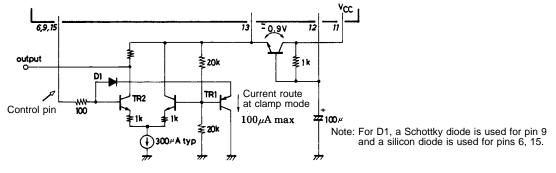

· Control circuit

The control circuit for each CONT pin is configured as shown below. When a voltage more than a given value is applied, the level on the pin is fixed by clamp diode D1.

Unit (resistance: Ω, capacitance: F)

#### Description

• Switching level  $V_{SW}$  of the control circuit is fixed by voltage V13 which is 1/2 of the voltage on pin 13.

$V_{SW} = 1/2 V13$

- Clamp voltage  $V_{\mbox{CLP}}$  at the time a voltage is applied to the CONT pin

$$\begin{split} V_{CLP} &= 1/2 \times V13 + V_D 1 + V_{BE} 1 \\ &= 1/2 \times V13 + 0.6 \ (0.3) + 0.6 \\ &= 1/2 \times V13 + (0.9 \ \text{or} \ 1.2) \end{split} \qquad \qquad \text{where } 0.9 \ \text{V is for pin } 9. \\ &1.2 \ \text{V is for pins } 6, \ 15. \end{split}$$

• The maximum voltage at which the CONT pin is brought to GND level is fixed by the level at which the Q2 is completely turned OFF.

This level is:  $1/2 \times V13 - V_{BE}2 = 1/2 \times V13 - 0.6$  [V]

Switching is performed at a level less than this.

• To turn ON/OFF

When turning ON:

To turn ON the control circuit to finish the operation, I<sub>B</sub> is required. Control voltage  $V_{OUT}$  is obtained with I<sub>B</sub> of 4 µA min.

•  $V_{CONT} min = R \times I_B max + Operation finish voltage.$  $I_B = 4 \ \mu A$

Operation finish voltage Pins 6, 15 :=  $1/2 \times V13$ Pin 9 :=  $1/2 \times V13 + V_{BE}$ =  $1/2 \times V13 + 0.6$  [V]

•  $V_{CONT} max = R \times I_B max + Clamp voltage R is restricted by I_B max.$

When the supply voltage is fixed, clamp voltage  $V_{CLP}$  is fixed. When resistor R is fixed based on a balance with capacitor C, resistor R is restricted by  $V_{CONT}$  max. as shown below.

$I_B max = 100 \ \mu A \ge \frac{V_{CONT} max - V_{CLP}}{R}$

The minimum value of resistor R is fixed by this equation.

Example

Assuming  $V_{CC} = 10$  V,  $V_{CONT}$  max = 10 V, Rmin is 50 k $\Omega$ . Therefore, R = 100 k $\Omega$  presents no problem. When turning OFF:

Bring the level on the CONT pin to a level less than:  $1/2\times V13-V_{BE}2=1/2\times V13-0.6~[V]$

#### (9) Example of voltage on each pin

|     | Rg = 2          | .2 kΩ, Ta = 25°C, | V <sub>IN</sub> = 0, pins 6, 9 | and 15 = GND    |      |

|-----|-----------------|-------------------|--------------------------------|-----------------|------|

| Pin |                 |                   | Unit                           |                 |      |

|     | 4.5 V           | 6.0 V             | 9.0 V                          | 12.0 V          | Onit |

| 1   | 0.3             | 0.3               | 0.3                            | 0.3             | mV   |

| 2   | 0.3             | 0.3               | 0.3                            | 0.3             | mV   |

| 3   | 0.59            | 0.58              | 0.57                           | 0.56            | V    |

| 4   | 1.63            | 2.23              | 3.65                           | 5.02            | V    |

| 5   | 1.63            | 2.23              | 3.65                           | 5.02            | V    |

| 6   | (GND) 0         | (GND) 0           | (GND) 0                        | (GND) 0         | V    |

| 7   | 0               | 0                 | 0                              | 0               | V    |

| 8   | 1.63            | 2.29              | 3.64                           | 5.01            | V    |

| 9   | (GND) 0         | (GND) 0           | (GND) 0                        | (GND) 0         | V    |

| 10  | (GND) 0         | (GND) 0           | (GND) 0                        | (GND) 0         | V    |

| 11  | V <sub>CC</sub> | V <sub>CC</sub>   | V <sub>CC</sub>                | V <sub>CC</sub> | V    |

| 12  | 4.48            | 5.96              | 8.97                           | 11.23           | V    |

| 13  | 3.72            | 5.20              | 8.21                           | 11.98           | V    |

| 14  | 0               | 0                 | 0                              | 0               | V    |

| 15  | (GND) 0         | (GND) 0           | (GND) 0                        | (GND) 0         | V    |

| 16  | 1.63            | 2.23              | 3.65                           | 5.02            | V    |

| 17  | 1.63            | 2.23              | 3.65                           | 5.02            | V    |

| 18  | 0.59            | 0.58              | 0.57                           | 0.56            | V    |

| 19  | 0.3             | 0.3               | 0.3                            | 0.3             | mV   |

| 20  | 0.3             | 0.3               | 0.3                            | 0.3             | mV   |

No.2651-8/13

Downloaded from **Elcodis.com** electronic components distributor

No.2651-9/13

No.2651-10/13

Downloaded from Elcodis.com electronic components distributor

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of December, 1997. Specifications and information herein are subject to change without notice.