#### **INTEGRATED CIRCUITS**

### DATA SHEET

For a complete data sheet, please also download:

- The IC04 LOCMOS HE4000B Logic Family Specifications HEF, HEC

- The IC04 LOCMOS HE4000B Logic Package Outlines/Information HEF, HEC

### HEF40163B MSI

4-bit synchronous binary counter with synchronous reset

Product specification

File under Integrated Circuits, IC04

January 1995

HEF40163B MSI

#### **DESCRIPTION**

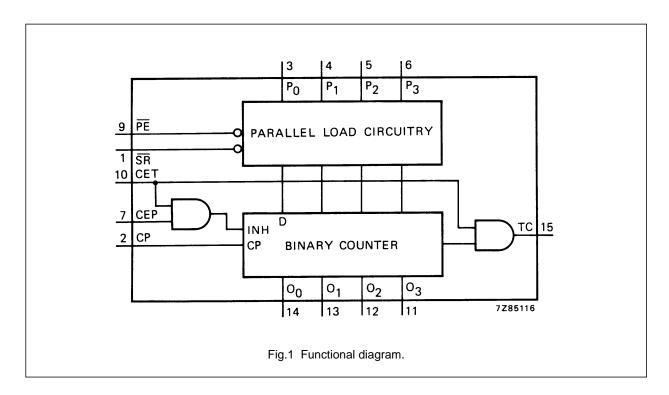

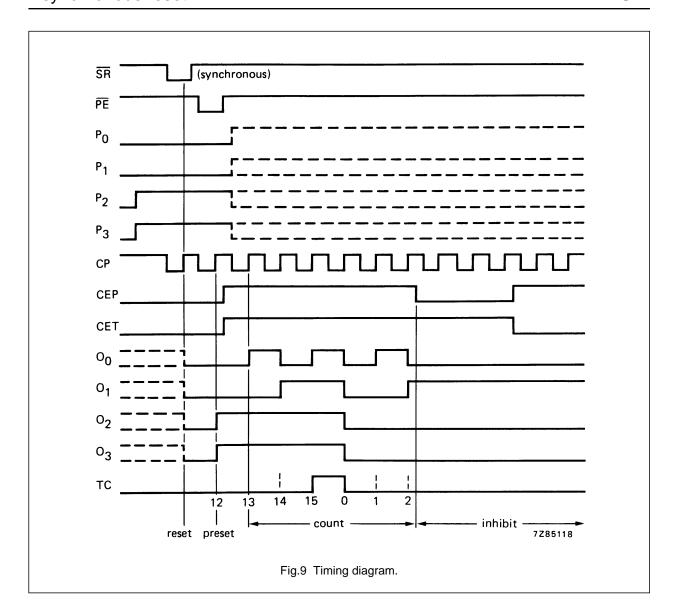

The HEF40163B is a fully synchronous edge-triggered 4-bit binary counter with a clock input (CP), four synchronous parallel data inputs (P $_0$  to P $_3$ ), four synchronous mode control inputs (parallel enable ( $\overline{\text{PE}}$ ), count enable parallel (CEP), count enable trickle (CET) and synchronous reset ( $\overline{\text{SR}}$ )), buffered outputs from all four bit positions (O $_0$  to O $_3$ ) and a terminal count output (TC).

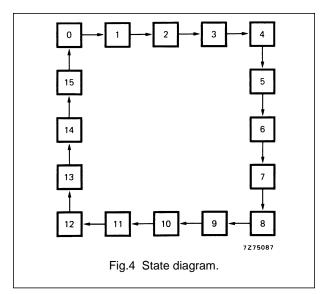

Operation is fully synchronous and occurs on the LOW to HIGH transition of CP. When  $\overline{PE}$  is LOW, the next LOW to HIGH transition of CP loads data into the counter from P<sub>0</sub> to P<sub>3</sub>. When  $\overline{PE}$  is HIGH, the next LOW to HIGH

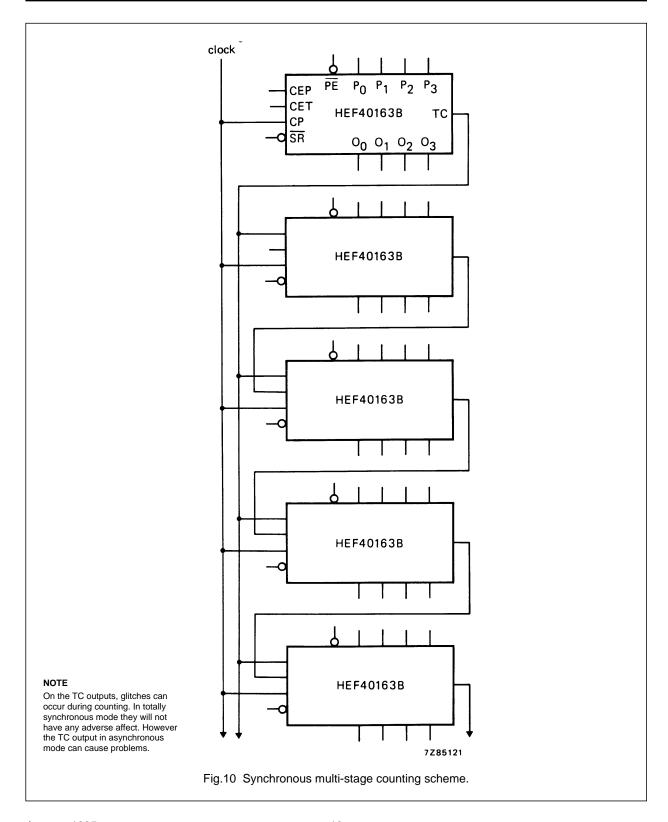

transition of CP advances the counter to its next state only if both CEP and CET are HIGH; otherwise no change occurs in the state of the counter. TC is HIGH when the state of the counter is  $15 \ (O_0 \ to \ O_3 = HIGH)$  and when CET is HIGH. A LOW on  $\overline{SR}$  sets all outputs ( $O_0 \ to \ O_3$  and TC) LOW on the next LOW to HIGH transition of CP, independent of the state of all other synchronous mode control inputs (CEP, CET and  $\overline{PE}$ ). Multistage synchronous counting is possible without additional components by using a carry look-ahead counting technique; in this case, TC is used to enable successive cascaded stages. CEP, CET,  $\overline{PE}$  and  $\overline{SR}$  must be stable only during the set-up time before the LOW to HIGH transition of CP.

#### FAMILY DATA, I<sub>DD</sub> LIMITS category MSI

See Family Specifications

Downloaded from Elcodis.com electronic components distributor

HEF40163B MSI

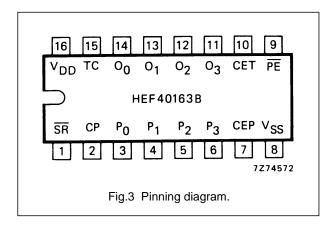

#### **PINNING**

PE parallel enable input

P<sub>0</sub> to P<sub>3</sub> parallel data inputs

CEP count enable parallel input

CET count enable trickle input

CP clock input (LOW to HIGH, edge-triggered)

SR synchronous reset input (active LOW)

O<sub>0</sub> to O<sub>3</sub> parallel outputs

TC terminal count output

HEF40163BP(N): 16-lead DIL; plastic (SOT38-1)

HEF40163BD(F): 16-lead DIL; ceramic (cerdip) (SOT74) HEF40163BT(D): 16-lead SO; plastic (SOT109-1)

(): Package Designator North America

#### SYNCHRONOUS MODE SELECTION

| SR | PE | CEP | CET | MODE      |

|----|----|-----|-----|-----------|

| Н  | L  | Х   | Х   | preset    |

| Н  | Н  | L   | Х   | no change |

| Н  | Н  | Х   | L   | no change |

| Н  | Н  | Н   | Н   | count     |

| L  | X  | Х   | Х   | reset     |

#### **Notes**

- 1. H = HIGH state (the more positive voltage)

- 2. L = LOW state (the less positive voltage)

- 3. X = state is immaterial

#### **TERMINAL COUNT GENERATION**

| CET | $(O_0\cdotO_1\cdotO_2\cdotO_3)$ | TC |

|-----|---------------------------------|----|

| L   | L                               | L  |

| L   | Н                               | L  |

| Н   | L                               | L  |

| Н   | Н                               | Н  |

#### Note

1.  $TC = CET \cdot O_0 \cdot O_1 \cdot O_2 \cdot O_3$

Philips Semiconductors Product specification

## 4-bit synchronous binary counter with synchronous reset

HEF40163B MSI

#### **AC CHARACTERISTICS**

$V_{SS}$  = 0 V;  $T_{amb}$  = 25 °C; input transition times  $\leq$  20 ns

|                 | V <sub>DD</sub><br>V | TYPICAL FORMULA FOR P (μW)                    |                                         |

|-----------------|----------------------|-----------------------------------------------|-----------------------------------------|

| Dynamic power   | 5                    | 1 200 $f_i + \sum (f_o C_L) \times V_{DD}^2$  | where                                   |

| dissipation per | 10                   | 5 600 $f_i + \sum (f_o C_L) \times V_{DD}^2$  | f <sub>i</sub> = input freq. (MHz)      |

| package (P)     | 15                   | 16 000 $f_i + \sum (f_o C_L) \times V_{DD}^2$ | f <sub>o</sub> = output freq. (MHz)     |

|                 |                      |                                               | C <sub>L</sub> = load capacitance (pF)  |

|                 |                      |                                               | $\sum (f_oC_L) = \text{sum of outputs}$ |

|                 |                      |                                               | V <sub>DD</sub> = supply voltage (V)    |

#### **AC CHARACTERISTICS**

$V_{SS}$  = 0 V;  $T_{amb}$  = 25 °C;  $C_L$  = 50 pF; input transition times  $\leq$  20 ns

|                         | V <sub>DD</sub><br>V | SYMBOL           | MIN. | TYP. | MAX. |    | TYPICAL EXTRAPOLATION FORMULA        |

|-------------------------|----------------------|------------------|------|------|------|----|--------------------------------------|

| Propagation delays      |                      |                  |      |      |      |    |                                      |

| $CP \to O_n$            | 5                    |                  |      | 110  | 220  | ns | 83 ns + (0,55 ns/pF) C <sub>L</sub>  |

| HIGH to LOW             | 10                   | t <sub>PHL</sub> |      | 45   | 90   | ns | 34 ns + (0,23 ns/pF) C <sub>L</sub>  |

|                         | 15                   |                  |      | 30   | 60   | ns | 22 ns + (0,16 ns/pF) C <sub>L</sub>  |

|                         | 5                    |                  |      | 115  | 230  | ns | 88 ns + (0,55 ns/pF) C <sub>L</sub>  |

| LOW to HIGH             | 10                   | t <sub>PLH</sub> |      | 45   | 95   | ns | 34 ns + (0,23 ns/pF) C <sub>L</sub>  |

|                         | 15                   |                  |      | 35   | 65   | ns | 27 ns + (0,16 ns/pF) C <sub>L</sub>  |

| $CP \to TC$             | 5                    |                  |      | 130  | 260  | ns | 103 ns + (0,55 ns/pF) C <sub>L</sub> |

| HIGH to LOW             | 10                   | t <sub>PHL</sub> |      | 55   | 105  | ns | 44 ns + (0,23 ns/pF) C <sub>L</sub>  |

|                         | 15                   |                  |      | 35   | 75   | ns | 27 ns + (0,16 ns/pF) C <sub>L</sub>  |

|                         | 5                    |                  |      | 140  | 280  | ns | 113 ns + (0,55 ns/pF) C <sub>L</sub> |

| LOW to HIGH             | 10                   | t <sub>PLH</sub> |      | 55   | 115  | ns | 44 ns + (0,23 ns/pF) C <sub>L</sub>  |

|                         | 15                   |                  |      | 40   | 80   | ns | 32 ns + (0,16 ns/pF) C <sub>L</sub>  |

| $CET \to TC$            | 5                    |                  |      | 105  | 210  | ns | 78 ns + (0,55 ns/pF) C <sub>L</sub>  |

| HIGH to LOW             | 10                   | t <sub>PHL</sub> |      | 50   | 100  | ns | 39 ns + (0,23 ns/pF) C <sub>L</sub>  |

|                         | 15                   |                  |      | 35   | 75   | ns | 27 ns + (0,16 ns/pF) C <sub>L</sub>  |

|                         | 5                    |                  |      | 90   | 185  | ns | 63 ns + (0,55 ns/pF) C <sub>L</sub>  |

| LOW to HIGH             | 10                   | t <sub>PLH</sub> |      | 35   | 70   | ns | 24 ns + (0,23 ns/pF) C <sub>L</sub>  |

|                         | 15                   |                  |      | 25   | 50   | ns | 17 ns + (0,16 ns/pF) C <sub>L</sub>  |

| Output transition times | 5                    |                  |      | 60   | 120  | ns | 10 ns + (1,0 ns/pF) C <sub>L</sub>   |

| HIGH to LOW             | 10                   | t <sub>THL</sub> |      | 30   | 60   | ns | 9 ns + (0,42 ns/pF) C <sub>L</sub>   |

|                         | 15                   |                  |      | 20   | 40   | ns | 6 ns + (0,28 ns/pF) C <sub>L</sub>   |

|                         | 5                    |                  |      | 60   | 120  | ns | 10 ns + (1,0 ns/pF) C <sub>L</sub>   |

| LOW to HIGH             | 10                   | t <sub>TLH</sub> |      | 30   | 60   | ns | 9 ns + (0,42 ns/pF) C <sub>L</sub>   |

|                         | 15                   |                  |      | 20   | 40   | ns | 6 ns + (0,28 ns/pF) C <sub>L</sub>   |

HEF40163B MSI

#### **AC CHARACTERISTICS**

$V_{SS}$  = 0 V;  $T_{amb}$  = 25 °C;  $C_L$  = 50 pF; input transition times  $\leq$  20 ns

|                           | V <sub>DD</sub> | SYMBOL            | MIN. | TYP. | MAX. |                                          |

|---------------------------|-----------------|-------------------|------|------|------|------------------------------------------|

| Minimum clock             | 5               |                   | 100  | 50   | ns   |                                          |

| pulse width; LOW          | 10              | t <sub>WCPL</sub> | 40   | 20   | ns   |                                          |

|                           | 15              |                   | 30   | 15   | ns   |                                          |

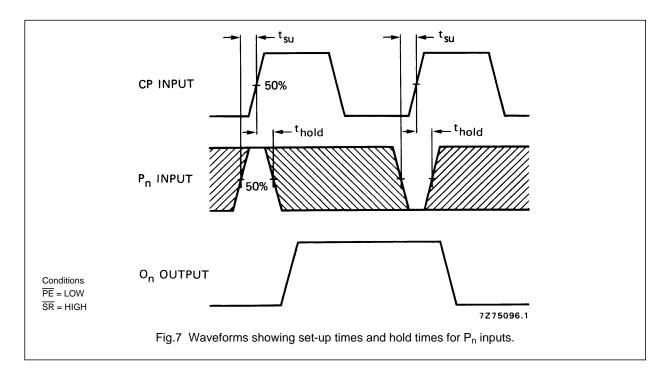

| Set-up times              | 5               |                   | 110  | 55   | ns   |                                          |

| $P_n \rightarrow CP$      | 10              | t <sub>su</sub>   | 40   | 20   | ns   |                                          |

|                           | 15              |                   | 30   | 15   | ns   |                                          |

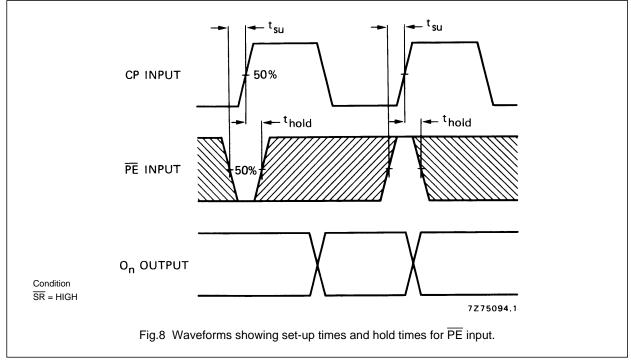

|                           | 5               |                   | 120  | 60   | ns   |                                          |

| $\overline{PE} \to CP$    | 10              | t <sub>su</sub>   | 40   | 20   | ns   |                                          |

|                           | 15              |                   | 25   | 10   | ns   |                                          |

|                           | 5               |                   | 260  | 130  | ns   |                                          |

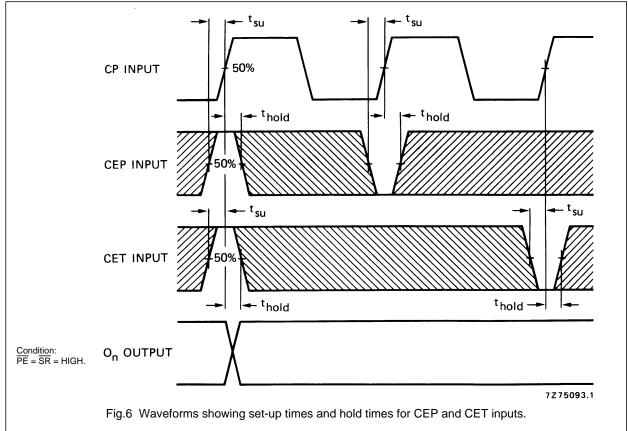

| CEP, CET $\rightarrow$ CP | 10              | t <sub>su</sub>   | 100  | 50   | ns   |                                          |

|                           | 15              |                   | 70   | 35   | ns   |                                          |

|                           | 5               |                   | 50   | 25   | ns   |                                          |

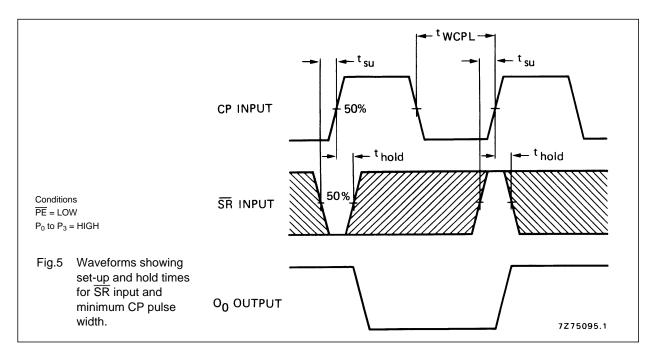

| $\overline{SR} \to CP$    | 10              | t <sub>su</sub>   | 20   | 10   | ns   | see also waveforms<br>Figs 5, 6, 7 and 8 |

|                           | 15              |                   | 15   | 10   | ns   | rigs 5, 6, 7 and 6                       |

| Hold times                | 5               |                   | 20   | -35  | ns   |                                          |

| $P_n \rightarrow CP$      | 10              | t <sub>hold</sub> | 10   | -10  | ns   |                                          |

|                           | 15              |                   | 5    | -10  | ns   |                                          |

|                           | 5               |                   | 15   | -45  | ns   |                                          |

| $\overline{PE} \to CP$    | 10              | t <sub>hold</sub> | 5    | -15  | ns   |                                          |

|                           | 15              |                   | 5    | -10  | ns   |                                          |

|                           | 5               |                   | 25   | -105 | ns   |                                          |

| CEP, CET $\rightarrow$ CP | 10              | t <sub>hold</sub> | 15   | -35  | ns   |                                          |

|                           | 15              |                   | 10   | -25  | ns   |                                          |

|                           | 5               |                   | 15   | -10  | ns   |                                          |

| $\overline{SR} \to CP$    | 10              | t <sub>hold</sub> | 5    | -5   | ns   |                                          |

|                           | 15              |                   | 5    | 0    | ns   |                                          |

| Maximum clock             | 5               |                   | 2,5  | 5    | MHz  |                                          |

| pulse frequency           | 10              | f <sub>max</sub>  | 7    | 14   | MHz  |                                          |

|                           | 15              |                   | 9    | 18   | MHz  |                                          |

January 1995 6

HEF40163B MSI

Philips Semiconductors Product specification

### 4-bit synchronous binary counter with synchronous reset

HEF40163B MSI

#### Note

Set-up and hold times are shown as positive values but may be specified as negative values.

January 1995

HEF40163B MSI

#### **APPLICATION INFORMATION**

An example of an application for the HEF40163B is:

• Programmable binary counter.

### HEF40163B MSI