# High-Speed Multi-Output PLL Clock Buffer

#### **Features**

- 10-MHz 200-MHz output operation

- Output-to-output skews < 350 ps

- 13 LVTTL 50% duty-cycle outputs capable of driving 50Ω terminated lines

- Phase-locked loop (PLL) LOCK indicator

- 3.3V LVTTL/LV differential (LVPECL) hot insertable reference inputs

- Multiply/divide ratios of (4, 6, 8, 10, 12, 16, 20):(2, 4, 6, 8, 10, 12, 16, 20)

- Operation with outputs operating at up to 10x input frequency

- Low cycle-to-cycle jitter (< ±75 ps peak-peak)</li>

- Single 3.3V ± 10% supply

- Pin-compatible with Motorola MPC973

- 52-pin TQFP package

# **Functional Description**

The CY7B9973V Low-Voltage PLL Clock Buffer offers user-selectable frequency control over system clock functions. This twelve output clock driver provides the system integrator selectable frequency ratios of 1:1, 2:1, 3:1, 3:2, 4:3, 5:1, 5:2, 5:3, 6:1 and 6:5 between outputs. An additional output is dedicated to providing feedback information to allow the internal PLL to multiply an external reference frequency by 4, 6, 8, 10, 12, 16 or 20. The completely integrated PLL reduces jitter and simplifies board layout.

The thirteen configurable outputs can each drive terminated transmission lines with impedances as low as  $50\Omega$  while delivering minimal and specified output skews at LVTTL levels.

The CY7B9973V has a flexible reference input scheme with three different hot-insertion capable inputs. These inputs allow the use of either differential LVPECL or single-ended LVTTL inputs which can be dynamically selected to provide the reference frequency.

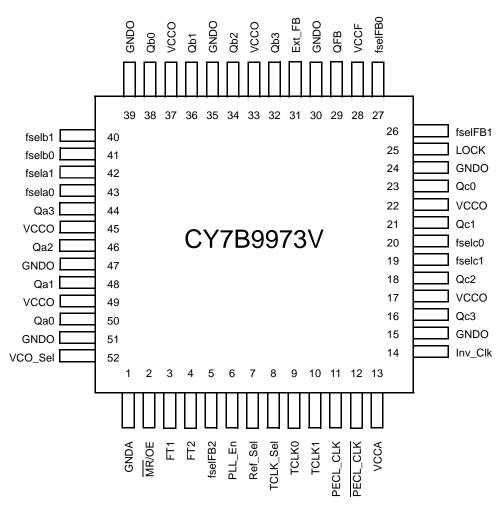

# 52-Lead Pinout (Top View)

Table 1. Divider Function Selects for Qa, Qb, Qc

| fsela1 | fsela0 | Qa  | fselb1 | fselb0 | Qb  | fselc1 | fselc0 | Qc |

|--------|--------|-----|--------|--------|-----|--------|--------|----|

| 0      | 0      | ÷4  | 0      | 0      | ÷4  | 0      | 0      | ÷2 |

| 0      | 1      | ÷6  | 0      | 1      | ÷6  | 0      | 1      | ÷4 |

| 1      | 0      | ÷8  | 1      | 0      | ÷8  | 1      | 0      | ÷6 |

| 1      | 1      | ÷12 | 1      | 1      | ÷10 | 1      | 1      | ÷8 |

Table 2. Divider Function Select for QFB

| fselFB2 | fselFB1 | fselFB0 | QFB |

|---------|---------|---------|-----|

| 0       | 0       | 0       | ÷4  |

| 0       | 0       | 1       | ÷6  |

| 0       | 1       | 0       | ÷8  |

| 0       | 1       | 1       | ÷10 |

| 1       | 0       | 0       | ÷8  |

| 1       | 0       | 1       | ÷12 |

| 1       | 1       | 0       | ÷16 |

| 1       | 1       | 1       | ÷20 |

**Table 3. Control Pin Function Selects**

| Control Pin | Logic '0'                | Logic '1'         |

|-------------|--------------------------|-------------------|

| VCO_Sel     | VCO/2                    | VCO               |

| Ref_Sel     | Controlled by TCLK_Sel   | PECL              |

| TCLK_Sel    | TCLK0                    | TCLK1             |

| PLL_En      | Bypass PLL               | Enable PLL        |

| MR/OE       | Master Reset/Output Hi-Z | Enable Outputs    |

| Inv_Clk     | Noninverted Qc2, Qc3     | Inverted Qc2, Qc3 |

Document #: 38-07430 Rev. \*B

# **Pin Definitions**

| Name                   | Pin#                                            | Туре                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|------------------------|-------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Q[a:c][0:3]<br>QFB     | 50,48,46,44<br>38,36,34,32<br>23,21,18,16<br>29 | LVTTL<br>Output               | Clock Output. These outputs provide numerous divide functions determined by the fsel[a:c][0:1] and the fselFB[0:2] inputs. See <i>Table 1</i> and <i>Table 2</i>                                                                                                                                                                                                                                                                                                                                   |  |

| Ext_FB                 | 31                                              | LVTTL<br>Input <sup>[1]</sup> | <b>LL Feedback Input</b> . This input is used to connect one of the Clock Outputs (usually FB) to the feedback input of the PLL.                                                                                                                                                                                                                                                                                                                                                                   |  |

| Ref_Sel                | 7                                               | LVTTL<br>Input <sup>[1]</sup> | Reference Select Input. The Ref_Sel input controls the reference input to the PLL. NOW the input is selected by the TCLK_Sel input. When HIGH the PECL_CLK is selected by the TCLK is input has an internal pull-up.                                                                                                                                                                                                                                                                               |  |

| TCLK_Sel               | 8                                               | LVTTL<br>Input <sup>[1]</sup> | TTL Clock Select Input. The TCLK_Sel input controls which TCLK[0,1] input will be used as the reference input if Ref_Sel is LOW. When TCLK_Sel is LOW TCLK0 is selected. When TCLK_Sel is HIGH TCLK1 is selected. This input has an internal pull-up.                                                                                                                                                                                                                                              |  |

| TCLK0<br>TCLK1         | 9, 10                                           | LVTTL<br>Input <sup>[1]</sup> | LVTTL Reference Inputs. These inputs provide the Reference frequency for the internal PLL when selected by Ref_Sel and TCLK_Sel.                                                                                                                                                                                                                                                                                                                                                                   |  |

| PECL_CLK<br>PECL_CLK   | 11,12                                           | LV-Diff.<br>PECL<br>Input     | <b>Differential Reference Inputs</b> . This LV-Differential PECL input provides the Reference frequency for the internal PLL when selected by Ref_Sel.                                                                                                                                                                                                                                                                                                                                             |  |

| fsel[a:c][0:1]         | 43, 42, 41,<br>40, 20,19                        | LVTTL<br>Input <sup>[1]</sup> | Output Divider Function Select. Each pair controls the divider function of the respective bank of outputs. See <i>Table 1</i> .                                                                                                                                                                                                                                                                                                                                                                    |  |

| fselFB[0:1]<br>fselFB2 | 27,26 5                                         | LVTTL<br>Input <sup>[1]</sup> | <b>Feedback Output Divider Function Select</b> . These inputs control the divider function of the Feedback output QFB. See <i>Table 2</i> .                                                                                                                                                                                                                                                                                                                                                        |  |

| VCO_Sel                | 52                                              | LVTTL<br>Input <sup>[1]</sup> | <b>VCO Frequency Select Input</b> . This input selects the nominal operating range of the VC used in the PLL. When VCO_Sel is HIGH the VCO range is 200-480 MHz. When VCO_S is LOW the VCO range is 100-240 MHz.                                                                                                                                                                                                                                                                                   |  |

| PLL_En                 | 6                                               | LVTTL<br>Input <sup>[1]</sup> | PLL Bypass Select. When this input is HIGH the internal Phase Locked Loop (PLL provides the internal clocks to operate the part. When this input is LOW the internal is bypassed and the selected reference input provides the clocks to operate the part.                                                                                                                                                                                                                                         |  |

| FT1, FT2               | 3, 4                                            | LVTTL<br>Input <sup>[1]</sup> | PLL Bypass Mode Control Inputs. When PLL_En is HIGH these inputs are ignored and may be set to any logic level or left open. These inputs have an internal pull-up.                                                                                                                                                                                                                                                                                                                                |  |

| Inv_Clk                | 14                                              | LVTTL<br>Input <sup>[1]</sup> | <b>Invert Mode</b> . This input only affects the Qc bank. When this input is HIGH, Qc2 and Qc3 are inverted from the "normal" phase of Qc0 and Qc1. When this input is LOW all outputs of the Qc bank are in the "normal" phase alignment.                                                                                                                                                                                                                                                         |  |

| MR/OE                  | 2                                               | LVTTL<br>Input <sup>[1]</sup> | Master Reset (active LOW) and Output Enable (active HIGH) Input. Note: when MR/OE is deasserted (set to HIGH) the PLL will have been disturbed and the outputs will be at an indeterminate frequency until it is relocked.                                                                                                                                                                                                                                                                         |  |

| VCCA                   | 13                                              | Power                         | PLL Power.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| VCCF                   | 28                                              | Power                         | Feedback Buffer Power.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| VCCO                   | 17, 22, 33,<br>37,45,49                         | Power                         | Output Buffer Power.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| GNDA                   | 1                                               | Ground                        | PLL Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| GNDO                   | 15, 24, 30,<br>35, 39, 47, 51                   | Ground                        | Output Buffer Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| LOCK                   | 25                                              | LVTTL<br>Output               | PLL Lock Indicator. When HIGH this output indicates that the internal PLL is locked to the reference signal. When LOW the PLL is attempting to acquire lock. Note: If there is no activity on the selected reference input LOCK may not accurately reflect the state of the internal PLL. This pin will drive logic, but not Thevenin terminated transmission lines. It is always active and does not go to a high impedance state. This output provides TEST MODE information when PLL_En is LOW. |  |

# Note:

Includes internal PULL-UP. If this pin is left unconnected it will assume a HIGH level.

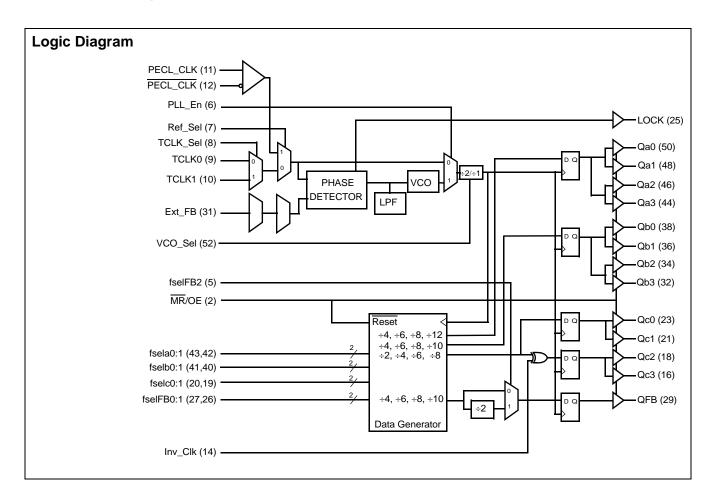

## **Block Diagram Description**

(see figure, page 1)

#### **Phase Frequency Detector and Filter**

These two blocks accept signals from the reference inputs (TCLK0, TCLK1 or PECL\_CLK) and the FB input (Ext\_FB). Correction information is then generated to control the frequency of the Voltage Controlled Oscillator (VCO). These two blocks, along with the VCO, form a (PLL) that tracks the incoming reference signal.

The Robo973 has a flexible reference input scheme. These inputs allow the use of either differential LVPECL or one of two single-ended LVTTL inputs. The reference inputs are tolerant to hot insertion and can be changed dynamically.

#### VCO, Control Logic, and Divider

The VCO accepts analog control inputs from the PLL filter block. The VCO\_Sel control pin setting determines the nominal operational frequency range of the VCO (f<sub>NOM</sub>). When VCO\_Sel is HIGH the VCO operating range is 200–480 MHz. For systems that need lower frequencies, VCO\_Sel can be set LOW, which changes the VCO operating range to 100–240 MHz.

#### **Data Generator**

The Data Generator is comprised of four independent banks: three banks for clock outputs and one bank for feedback. Each clock output bank has four low-skew, high-fanout output buffers (Q[a:c][0:3]), controlled by two divide function select inputs (fsel[a:c][0:1]).

The feedback bank has one high-fanout output buffer (QFB). This output is usually connected to the selected feedback input (Ext\_FB). This feedback output has three divider function selects fselFB[0:2].

#### Inv\_Clk Pin Function

The Qc bank has signal invert capability. The four outputs of the Qc bank will act as two pairs of complementary outputs when the Inv\_Clk pin is driven HIGH. In complementary output mode, Qc0 and Qc1 are noninverting (i.e., in phase with the other banks), Qc2 and Qc3 are inverting outputs (i.e., inverted from the other banks). When the Inv\_Clk pin is driven LOW, the outputs will not invert. Inversion of the outputs are independent of the divide functions. Therefore, clock outputs of Qc bank can be inverted and divided at the same time.

#### **Lock Detect Output Description**

The LOCK detect output indicates the lock condition of the integrated PLL. Lock detection is accomplished by comparing the phase difference between the reference and feedback inputs. An unacceptable phase error is declared when the phase difference between the two inputs is greater than about 700 ps.

When in the locked state, after four or more consecutive feedback clock cycles with phase-errors, the LOCK output will be forced LOW to indicate out-of-lock state.

When in the out-of-lock state, 32 consecutive phase-errorless feedback clock cycles are required to allow the LOCK output to indicate lock condition (LOCK = HIGH).

If the feedback clock is removed after LOCK has gone HIGH, a Watchdog circuit is implemented to indicate the out-of-lock condition after a time-out period by deasserting LOCK LOW. This time-out period is based upon a divided down reference clock.

This assumes that there is activity on the selected reference input. If there is no activity on the selected reference input then the LOCK detect pin may not accurately reflect the state of the internal PLL.

The LOCK pin has been designed with an intentionally reduced output drive capability to minimize noise and power dissipation. This pin will drive logic, but not Thevenin-terminated transmission lines. It is also unaffected by the MR/OE input and is always active.

#### **PLL Bypass Mode Description**

The device will enter PLL bypass mode when the PLL\_En is driven LOW. In factory PLL bypass mode, the device will operate with its internal PLL disconnected; input signals supplied to the reference input will be used in place of the PLL output. In PLL bypass mode the Ext\_FB input is ignored. All functions of the device are still operational in PLL bypass mode.

#### **Factory Test Reset**

When in PLL bypass mode (PLL\_En = LOW), the device can be reset to a deterministic state by driving the MR/OE input LOW. When the MR/OE input is driven LOW in PLL bypass mode, all clock outputs will go to HI-Z; after the selected reference clock pin has 5 positive transitions, all the internal finite state machines (FSM) will be set to a deterministic state. The deterministic state of the state machines will depend on the configurations of the divide selects and frequency select input. All clock outputs will stay in high-impedance mode and all FSMs will stay in the deterministic state until MR/OE is deasserted. When MR/OE is deasserted (with PLL\_En still at LOW), the device will reenter PLL bypass mode.

## Safe Operating Zone

The device will operate below its maximum allowable junction temperature ( $t_J < 150^{\circ}$ C) in any configuration of multiply or divide with all outputs loaded to the data sheet maximum (i.e., with 25-pF load and 0-m/s air flow).

# **Absolute Maximum Conditions**

(Above which the useful life may be impaired. For user guidelines, not tested.) Storage Temperature .....-40°C to +150°C Ambient Temperature with Power Applied .. -40°C to +125°C Supply Voltage to Ground Potential ......-0.5V to +4.6V DC Input Voltage.....-0.3V to  $V_{CC}$  + 0.5V

| Output Current into Outputs (LOW)                      | 40 mA   |

|--------------------------------------------------------|---------|

| Static Discharge Voltage(per MIL-STD-883, Method 3015) | > 2000V |

| Latch-up Current                                       | ±200 mA |

# **Operating Range**

| Range      | Ambient Temperature | V <sub>CC</sub> |

|------------|---------------------|-----------------|

| Commercial | 0°C to +70°C        | 3.3V ±10%       |

# **DC CHARACTERISTICS** Over the Operating Range

| Parameter        | Description                                                     | Test Conditions                                                      | Min. | Тур. | Max.            | Unit |

|------------------|-----------------------------------------------------------------|----------------------------------------------------------------------|------|------|-----------------|------|

| V <sub>IH</sub>  | Input HIGH Voltage                                              |                                                                      | 2.0  | _    | $V_{CC} + 0.3$  | V    |

| V <sub>IL</sub>  | Input LOW Voltage                                               |                                                                      | _    | _    | 0.8             | V    |

| V <sub>PP</sub>  | Peak-to-Peak Input Voltage PECL_CLK                             |                                                                      | 400  | _    | V <sub>cc</sub> | mV   |

| V <sub>CMR</sub> | Common Mode Range (Crossing) PECL_CLK                           | Note 2                                                               | 0.8  | _    | V <sub>cc</sub> | V    |

| V <sub>OH</sub>  | Output HIGH Voltage All "Q" Outputs                             | $I_{OH} = -20 \text{ mA}^{[3]}$                                      | 2.4  | _    | _               | V    |

|                  | Output HIGH Voltage LOCK Output                                 | $I_{OH} = -2 \text{ mA}^{[3]}$                                       | 2.4  | _    | _               | V    |

| V <sub>OL</sub>  | Output LOW Voltage "Q" Output                                   | I <sub>OL</sub> = +20 mA                                             | _    | _    | 0.5             | V    |

|                  | Output LOW Voltage LOCK Output                                  | $I_{OL}$ = +2 mA                                                     | _    | _    | 0.5             | V    |

| I <sub>IN</sub>  | Input Current <sup>[4]</sup>                                    | All control inputs<br>GND < V <sub>IN</sub> < V <sub>CC</sub>        | _    | -    | <u>+</u> 150    | uA   |

|                  |                                                                 | PECL_CLK and<br>TCLK[0:1] GND <<br>V <sub>IN</sub> < V <sub>CC</sub> | -    | _    | <u>+</u> 500    | uA   |

| I <sub>I</sub>   | Hot Insertion Input Current                                     | PECL_CLK and TCLK[0:1] $V_{IN} \le$ 3.63V $V_{CC} = GND$             | -    | _    | 100             | uA   |

| I <sub>CCQ</sub> | Maximum Quiescent Supply Current                                | Sum all V <sub>CC</sub> pins<br>PLL_En=LOW<br>reference off          | -    | 50   | 150             | mA   |

| I <sub>CCD</sub> | Maximum Dynamic Supply Current (Neglecting Output Load Current) | Outputs unloaded fselFB = 010 (÷8) ref = 50 MHz                      | -    | 320  | 400             | mA   |

| C <sub>IN</sub>  | Input Capacitance                                               | Note 5                                                               | _    | _    | 4               | pF   |

# PLL INPUT REFERENCE CHARACTERISTICS Over the Operating Range

| Parameter                      | Description                | Test Conditions | Min. | Max. | Unit |

|--------------------------------|----------------------------|-----------------|------|------|------|

| t <sub>r,</sub> t <sub>f</sub> | TCLK Input Rise/Fall Time  | Note 5          | _    | 3.0  | ns   |

| f <sub>ref</sub>               | Reference Input Frequency  |                 | 14   | 120  | MHz  |

| t <sub>refDC</sub>             | Reference Input Duty Cycle |                 | 25   | 75   | %    |

- V<sub>CMR</sub> is the measured at the point that both inputs achieve the same voltage.

The CY7B9973V clock outputs can drive series or parallel terminated 50Ω (or 50Ω to VCC/2) transmission lines on the incident edge.

- 4. Inputs have pull-up resistors which affect input current.

- 5. Tested initially and after any design or process changes that may affect these parameters.

# AC CHARACTERISTICS Over the Operating Range

| Parameter                           | Description                                                                | Test Conditions                           | Min.                          | Тур.                                  | Max.                          | Unit |

|-------------------------------------|----------------------------------------------------------------------------|-------------------------------------------|-------------------------------|---------------------------------------|-------------------------------|------|

| t <sub>r</sub>                      | Output Rise Time                                                           | 0.8 to 2.0V<br>Note 13                    | 0.15                          | -                                     | 1.2                           | ns.  |

| t <sub>f</sub>                      | Output Fall Time                                                           | 2.0 to 0.8V<br>Note 13                    | 0.15                          | -                                     | 1.2                           | ns.  |

| t <sub>pw</sub>                     | Output Duty Cycle                                                          | f <sub>max</sub> < 125 MHz,<br>Notes 6, 7 | t <sub>CYCLE</sub> /2<br>-400 | t <sub>CYCLE</sub> /2<br><u>+</u> 200 | t <sub>CYCLE</sub> /2<br>+400 | ps   |

|                                     |                                                                            | f <sub>max</sub> > 125 MHz,<br>Notes 6, 7 | t <sub>CYCLE</sub> /2<br>-450 | t <sub>CYCLE</sub> /2<br><u>+</u> 225 | t <sub>CYCLE</sub> /2<br>+450 | ps   |

| t <sub>pd</sub>                     | Propagation Delay (Selected Reference Input Rise to Ext_FB Rise) QFB = ÷ 8 | Notes 7, 8                                | -350                          | _                                     | +350                          | ps   |

| t <sub>os</sub>                     | Output to Output Skew                                                      | Notes 7, 15                               | _                             | _                                     | <u>+</u> 350                  | ps   |

| $f_{VCO}$                           | VCO Lock Range                                                             |                                           | 200                           | _                                     | 480                           | MHz  |

| f <sub>max</sub>                    | Maximum Output Frequency                                                   | Note 12                                   | _                             | _                                     | 200                           | MHz  |

| t <sub>jitter (CC)</sub>            | Cycle to Cycle Jitter (Peak-Peak), 10,000 clocks                           | Note 16                                   | _                             | <u>+</u> 50                           | <u>+</u> 75                   | ps   |

| t <sub>jitter (PER)</sub>           | Period Jitter (Peak-Peak), 10,000 clocks                                   | Note 16                                   | _                             | 120                                   | 168                           | ps   |

|                                     | Period Jitter (Peak-Peak), RMS                                             |                                           | _                             | 12                                    | 15.5                          | ps   |

| t <sub>jitter</sub> (PHASE)         | I/O Phase Jitter (Peak-Peak), 10,000 clocks, ÷ 4 feedback, VCO = 250 MHz   | Note 16                                   | _                             | 175                                   | 280                           | ps   |

|                                     | I/O Phase jitter (Peak-Peak), RMS                                          |                                           | _                             | 24                                    | 46                            | ps   |

| t <sub>OLZ</sub> , t <sub>OHZ</sub> | Output Disable Time                                                        | Note 9                                    | 1                             | _                                     | 10                            | ns   |

| t <sub>OZL</sub> , t <sub>OZH</sub> | Output Enable Time                                                         | Notes 10, 11                              | 0.5                           | -                                     | 14                            | ns   |

| t <sub>lock</sub>                   | Maximum PLL Lock Time                                                      |                                           | _                             | _                                     | 10                            | ms   |

| t <sub>TB</sub>                     | Total Timing Budget window                                                 | Note 14                                   | _                             | _                                     | 775                           | ps   |

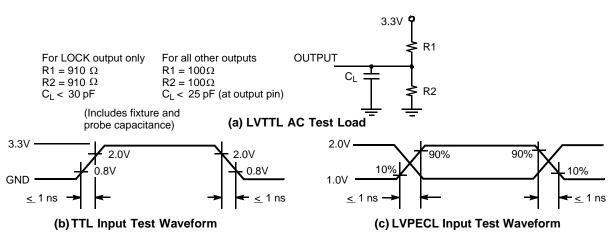

#### AC Test Loads and Waveform[17]

#### Notes:

- 6. t<sub>PW</sub> is measured at Vcc/2.

- 7.  $50\Omega$  transmission line terminated into  $V_{CC}/2$ .

- 8.  $t_{PD}$  is specified for a 50 MHz input reference. The  $t_{PD}$  does not include jitter.

- 9. Measured at 0.5V deviation from starting voltage.

- 10. For  $t_{OZL}$  and  $t_{OZH}$  minimum,  $C_L$  = 0pF,  $R_L$  = 1k (to  $V_{CC}$  for  $t_{OZL}$ , to GND for  $t_{OZH}$ ). For  $t_{OZL}$  and  $t_{OZH}$  maximum, CL = 25pF and RL = 100 $\Omega$  (to  $V_{CC}$  for  $t_{OZL}$ , to GND for  $t_{OZH}$ ).

- 11.  $t_{OZL}$  maximum is measured at 0.5V.  $t_{OZH}$  maximum is measured at 2.4V.

- 12. f<sub>max</sub> measured with CL = 25pF. 13. Measured with no load.

- 14.  $t_{TB} = t_{pd} + t_{OS} + t_{jitter}$ , this parameter is calculated and is the worst case between devices.

- 15. All outputs operating at the same frequency.

- 16. Not a tested parameter. Guaranteed by characterization.

- 17. These figures are for illustrations only. The actual ATE loads may vary.

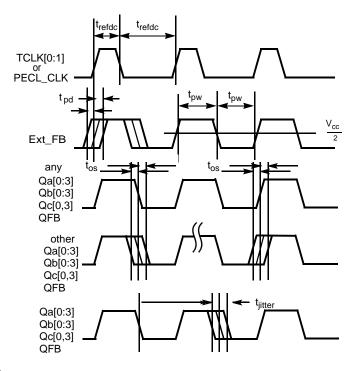

# **AC Timing Diagrams**

# **Ordering Information**

| Ordering Code | Package Name | Package Type                | Operating Range |

|---------------|--------------|-----------------------------|-----------------|

| CY7B9973V-AC  | A52          | 52-Lead Thin Quad Flat Pack | Commercial      |

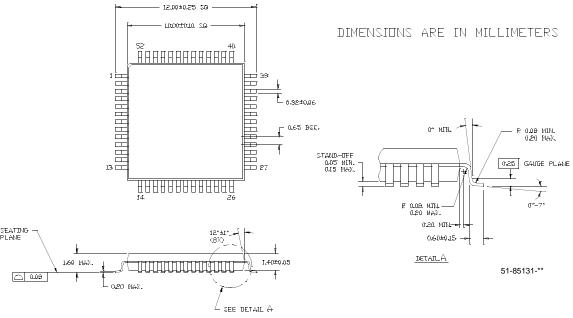

#### **Package Diagrams**

#### 52-Lead Thin Plastic Quad Flat Pack (10 x 10 x 1.4 mm) A52

RoboClock is a registered trademark of Cypress Semiconductor. All product and company names mentioned in this document are the trademarks of their respective holders.

Document #: 38-07430 Rev. \*B

Page 7 of 8

# **Document History Page**

| Document Title: CY7B9973V RoboClock® High-Speed Multi-Output PLL Clock Buffer Document Number: 38-07430 |         |            |                    |                                                                                                                       |  |  |

|---------------------------------------------------------------------------------------------------------|---------|------------|--------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|

| REV.                                                                                                    | ECN No. | Issue Date | Orig. of<br>Change | Description of Change                                                                                                 |  |  |

| **                                                                                                      | 115842  | 06/10/02   | HWT                | New Data Sheet                                                                                                        |  |  |

| *A                                                                                                      | 128182  | 09/15/03   | RGL                | Added phase and period jitter specifications Tightened duty cycle spec and split duty cycle based on output frequency |  |  |

| *B                                                                                                      | 506217  | See ECN    | RGL                | Minor Change: To post on web                                                                                          |  |  |

Document #: 38-07430 Rev. \*B