# **Programmable Timer**

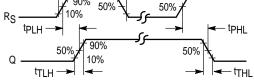

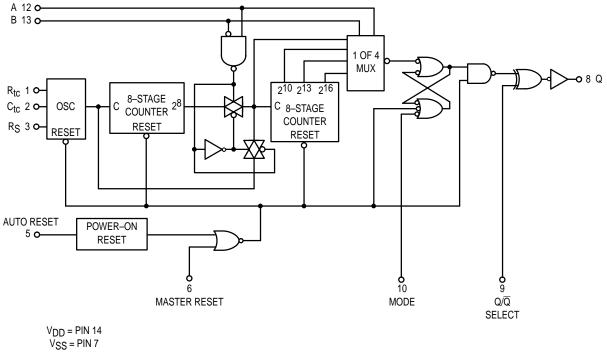

The MC14541B programmable timer consists of a 16–stage binary counter, an integrated oscillator for use with an external capacitor and two resistors, an automatic power–on reset circuit, and output control logic.

Timing is initialized by turning on power, whereupon the power–on reset is enabled and initializes the counter, within the specified V<sub>DD</sub> range. With the power already on, an external reset pulse can be applied. Upon release of the initial reset command, the oscillator will oscillate with a frequency determined by the external RC network. The 16–stage counter divides the oscillator frequency ( $f_{OSC}$ ) with the n<sup>th</sup> stage frequency being  $f_{OSC}/2^n$ .

- Available Outputs 2<sup>8</sup>, 2<sup>10</sup>, 2<sup>13</sup> or 2<sup>16</sup>

- Increments on Positive Edge Clock Transitions

- Built-in Low Power RC Oscillator (± 2% accuracy over temperature range and ± 20% supply and ± 3% over processing at < 10 kHz)</li>

- Oscillator May Be Bypassed if External Clock Is Available (Apply external clock to Pin 3)

- External Master Reset Totally Independent of Automatic Reset

Operation

- Operates as 2<sup>n</sup> Frequency Divider or Single Transition Timer

- Q/Q Select Provides Output Logic Level Flexibility

- Reset (auto or master) Disables Oscillator During Resetting to Provide No Active Power Dissipation

- Clock Conditioning Circuit Permits Operation with Very Slow Clock Rise and Fall Times

- Automatic Reset Initializes All Counters On Power Up

- Supply Voltage Range = 3.0 Vdc to 18 Vdc with Auto Reset

- Disabled (Pin 5 =  $V_{DD}$ )

- 8.5 Vdc to 18 Vdc with Auto Reset Enabled (Pin 5 = V<sub>SS</sub>)

#### MAXIMUM RATINGS\* (Voltages Referenced to VSS)

| Symbol                             | Parameter                                 | Value                          | Unit |

|------------------------------------|-------------------------------------------|--------------------------------|------|

| V <sub>DD</sub>                    | DC Supply Voltage                         | – 0.5 to + 18.0                | V    |

| V <sub>in</sub> , V <sub>out</sub> | Input or Output Voltage (DC or Transient) | – 0.5 to V <sub>DD</sub> + 0.5 | V    |

| l <sub>in</sub>                    | Input Current (DC or Transient), per Pin  | ± 10                           | mA   |

| l <sub>out</sub>                   | Output Current (DC or Transient), per Pin | ± 45                           | mA   |

| PD                                 | Power Dissipation, per Package†           | 500                            | mW   |

| T <sub>stg</sub>                   | Storage Temperature                       | – 65 to + 150                  | °C   |

| ΤL                                 | Lead Temperature (8–Second Soldering)     | 260                            | °C   |

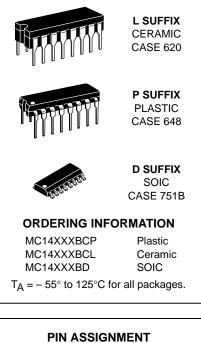

\* Maximum Ratings are those values beyond which damage to the device may occur. †Temperature Derating:

Plastic "P and D/DW" Packages: – 7.0 mW/°C From 65°C To 125°C Ceramic "L" Packages: – 12 mW/°C From 100°C To 125°C

MC14541B

| r <sub>tc</sub> [                      | 1• | 14 | l v <sub>DD</sub> |  |  |

|----------------------------------------|----|----|-------------------|--|--|

| R <sub>tc</sub> [<br>C <sub>tc</sub> [ | 2  | 13 | ]в                |  |  |

| R <sub>S</sub> [                       | 3  | 12 | D A               |  |  |

| NC [                                   | 4  | 11 | ] NC              |  |  |

| ar C                                   | 5  | 10 | MODE              |  |  |

| MR [                                   | 6  | 9  | ] Q/Q SEL         |  |  |

| v <sub>ss</sub> C                      | 7  | 8  | Ια                |  |  |

| NC = NO CONNECTION                     |    |    |                   |  |  |

REV 3 1/94

© Motorola, Inc. 1995

#### ELECTRICAL CHARACTERISTICS (Voltages Referenced to VSS)

|                                                                                                                                                              |                     | VDD             | - 5                        | 5°C                  |                            | 25°C                                            |                      | 125                        | °℃                   |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------|----------------------------|----------------------|----------------------------|-------------------------------------------------|----------------------|----------------------------|----------------------|------|

| Characteristic                                                                                                                                               | Symbol              | Vdc             | Min                        | Max                  | Min                        | Typ #                                           | Мах                  | Min                        | Max                  | Unit |

| Output Voltage "0" Le<br>V <sub>in</sub> = V <sub>DD</sub> or 0                                                                                              | vel V <sub>OL</sub> | 5.0<br>10<br>15 |                            | 0.05<br>0.05<br>0.05 | <br><br>                   | 0<br>0<br>0                                     | 0.05<br>0.05<br>0.05 | _<br>_<br>_                | 0.05<br>0.05<br>0.05 | Vdc  |

| "1" Le<br>V <sub>in</sub> = 0 or V <sub>DD</sub>                                                                                                             | vel V <sub>OH</sub> | 5.0<br>10<br>15 | 4.95<br>9.95<br>14.95      |                      | 4.95<br>9.95<br>14.95      | 5.0<br>10<br>15                                 |                      | 4.95<br>9.95<br>14.95      |                      | Vdc  |

| Input Voltage "0" Le<br>$(V_O = 4.5 \text{ or } 0.5 \text{ Vdc})$<br>$(V_O = 9.0 \text{ or } 1.0 \text{ Vdc})$<br>$(V_O = 13.5 \text{ or } 1.5 \text{ Vdc})$ | vel V <sub>IL</sub> | 5.0<br>10<br>15 |                            | 1.5<br>3.0<br>4.0    |                            | 2.25<br>4.50<br>6.75                            | 1.5<br>3.0<br>4.0    |                            | 1.5<br>3.0<br>4.0    | Vdc  |

| "1" Le<br>(V <sub>O</sub> = 0.5 or 4.5 Vdc)<br>(V <sub>O</sub> = 1.0 or 9.0 Vdc)<br>(V <sub>O</sub> = 1.5 or 13.5 Vdc)                                       | vel VIH             | 5.0<br>10<br>15 | 3.5<br>7.0<br>11           |                      | 3.5<br>7.0<br>11           | 2.75<br>5.50<br>8.25                            |                      | 3.5<br>7.0<br>11           |                      | Vdc  |

| Output Drive Current $(V_{OH} = 2.5 \text{ Vdc})$ Sou $(V_{OH} = 9.5 \text{ Vdc})$ $(V_{OH} = 13.5 \text{ Vdc})$                                             | rce IOH             | 5.0<br>10<br>15 | - 7.96<br>- 4.19<br>- 16.3 |                      | - 6.42<br>- 3.38<br>- 13.2 | - 12.83<br>- 6.75<br>- 26.33                    |                      | - 4.49<br>- 2.37<br>- 9.24 |                      | mAdc |

| $(V_{OL} = 0.4 \text{ Vdc})$ (V <sub>OL</sub> = 0.5 Vdc)<br>(V <sub>OL</sub> = 1.5 Vdc)                                                                      | ink I <sub>OL</sub> | 5.0<br>10<br>15 | 1.93<br>4.96<br>19.3       |                      | 1.56<br>4.0<br>15.6        | 3.12<br>8.0<br>31.2                             |                      | 1.09<br>2.8<br>10.9        |                      | mAdc |

| Input Current                                                                                                                                                | l <sub>in</sub>     | 15              | —                          | ± 0.1                | —                          | ±0.00001                                        | ± 0.1                | —                          | ± 1.0                | μAdc |

| Input Capacitance<br>(V <sub>in</sub> = 0)                                                                                                                   | C <sub>in</sub>     | -               | —                          | -                    | —                          | 5.0                                             | 7.5                  | -                          | _                    | pF   |

| Quiescent Current<br>(Pin 5 is High)<br>Auto Reset Disabled                                                                                                  | IDD                 | 5.0<br>10<br>15 |                            | 5.0<br>10<br>20      |                            | 0.005<br>0.010<br>0.015                         | 5.0<br>10<br>20      |                            | 150<br>300<br>600    | μAdc |

| Auto Reset Quiescent Current<br>(Pin 5 is low)                                                                                                               | IDDR                | 10<br>15        | _<br>_                     | 250<br>500           | _                          | 30<br>82                                        | 250<br>500           | _                          | 1500<br>2000         | μAdc |

| Supply Current**†<br>(Dynamic plus Quiescent)                                                                                                                | ID                  | 5.0<br>10<br>15 |                            | -                    | $I_{D} = (0)$              | ).4 μA/kHz) f<br>).8 μA/kHz) f<br>I.2 μA/kHz) f | + I <sub>DD</sub>    | -                          |                      | μAdc |

#Data labelled "Typ" is not to be used for design purposes but is intended as an indication of the IC's potential performance. \*\*The formulas given are for the typical characteristics only at 25°C.

†When using the on chip oscillator the total supply current (in  $\mu$ Adc) becomes:  $I_T = I_D + 2 C_{tc} V_{DD} f \times 10^{-3}$  where  $I_D$  is in  $\mu$ A,  $C_{tc}$  is in pF,  $V_{DD}$  in Volts DC, and f in kHz. (see Fig. 3) Dissipation during power–on with automatic reset enabled is typically 50  $\mu$ A @  $V_{DD} = 10$  Vdc.

This device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high-impedance circuit. For proper operation,  $V_{in}$  and  $V_{out}$  should be constrained to the range  $V_{SS} \leq (V_{in} \text{ or } V_{out}) \leq V_{DD}$ .

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either V<sub>SS</sub> or V<sub>DD</sub>). Unused outputs must be left open.

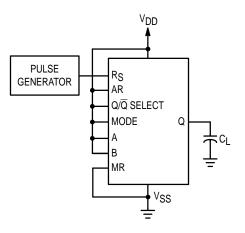

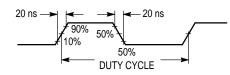

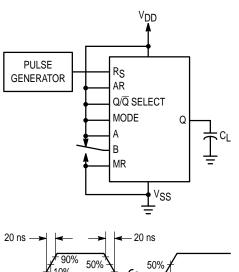

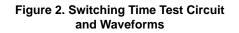

# SWITCHING CHARACTERISTICS\* (CL = 50 pF, TA = $25^{\circ}$ C)

| Characteristic                                                                                                                                                                                                                                                                                    | Symbol                               | V <sub>DD</sub> | Min               | Typ #              | Max                | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------|-------------------|--------------------|--------------------|------|

| Output Rise and Fall Time<br>$t_{TLH}$ , $t_{THL} = (1.5 \text{ ns/pF}) \text{ C}_{L} + 25 \text{ ns}$<br>$t_{TLH}$ , $t_{THL} = (0.75 \text{ ns/pF}) \text{ C}_{L} + 12.5 \text{ ns}$<br>$t_{TLH}$ , $t_{THL} = (0.55 \text{ ns/pF}) \text{ C}_{L} + 9.5 \text{ ns}$                             | <sup>t</sup> т∟н,<br>tтн∟            | 5.0<br>10<br>15 | <br><br>_         | 100<br>50<br>40    | 200<br>100<br>80   | ns   |

| Propagation Delay, Clock to Q (2 <sup>8</sup> Output)<br>tpLH, tpHL = (1.7 ns/pF) CL + 3415 ns<br>tpLH, tpHL = (0.66 ns/pF) CL + 1217 ns<br>tpLH, tpHL = (0.5 ns/pF) CL + 875 ns                                                                                                                  | <sup>t</sup> PLH<br><sup>t</sup> PHL | 5.0<br>10<br>15 |                   | 3.5<br>1.25<br>0.9 | 10.5<br>3.8<br>2.9 | μs   |

| Propagation Delay, Clock to Q (2 <sup>16</sup> Output)<br>tp <sub>HL</sub> , tp <sub>LH</sub> = (1.7 ns/pF) C <sub>L</sub> + 5915 ns<br>tp <sub>HL</sub> , tp <sub>LH</sub> = (0.66 ns/pF) C <sub>L</sub> + 3467 ns<br>tp <sub>HL</sub> , tp <sub>LH</sub> = (0.5 ns/pF) C <sub>L</sub> + 2475 ns | <sup>t</sup> PHL<br><sup>t</sup> PLH | 5.0<br>10<br>15 | <br><br>          | 6.0<br>3.5<br>2.5  | 18<br>10<br>7.5    | μs   |

| Clock Pulse Width                                                                                                                                                                                                                                                                                 | <sup>t</sup> WH(cl)                  | 5.0<br>10<br>15 | 900<br>300<br>225 | 300<br>100<br>85   |                    | ns   |

| Clock Pulse Frequency (50% Duty Cycle)                                                                                                                                                                                                                                                            | fcl                                  | 5.0<br>10<br>15 |                   | 1.5<br>4.0<br>6.0  | 0.75<br>2.0<br>3.0 | MHz  |

| MR Pulse Width                                                                                                                                                                                                                                                                                    | <sup>t</sup> WH(R)                   | 5.0<br>10<br>15 | 900<br>300<br>225 | 300<br>100<br>85   |                    | ns   |

| Master Reset Removal Time                                                                                                                                                                                                                                                                         | trem                                 | 5.0<br>10<br>15 | 420<br>200<br>200 | 210<br>100<br>100  |                    | ns   |

\* The formulas given are for the typical characteristics only at 25°C.

#Data labelled "Typ" is not to be used for design purposes but is intended as an indication of the IC's potential performance.

$(\mathsf{R}_{tc} \text{ AND } \mathsf{C}_{tc} \text{ OUTPUTS } \text{ARE } \mathsf{LEFT} \text{ OPEN})$

# FREQUENCY SELECTION TABLE

| А | В | Number of<br>Counter Stages<br>n | Count<br>2 <sup>n</sup> |

|---|---|----------------------------------|-------------------------|

| 0 | 0 | 13                               | 8192                    |

| 0 | 1 | 10                               | 1024                    |

| 1 | 0 | 8                                | 256                     |

| 1 | 1 | 16                               | 65536                   |

# **TRUTH TABLE**

|                 | State                               |                                      |  |  |

|-----------------|-------------------------------------|--------------------------------------|--|--|

| Pin             | 0                                   | 1                                    |  |  |

| Auto Reset, 5   | Auto Reset Operating                | Auto Reset Disabled                  |  |  |

| Master Reset, 6 | Timer Operational                   | Master Reset On                      |  |  |

| Q/ <u>Q</u> , 9 | Output Initially Low<br>After Reset | Output Initially High<br>After Reset |  |  |

| Mode, 10        | Single Cycle Mode                   | Recycle Mode                         |  |  |

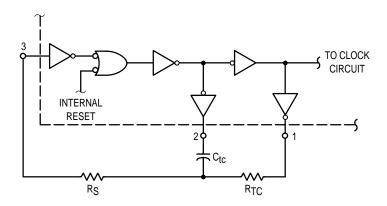

Figure 3. Oscillator Circuit Using RC Configuration

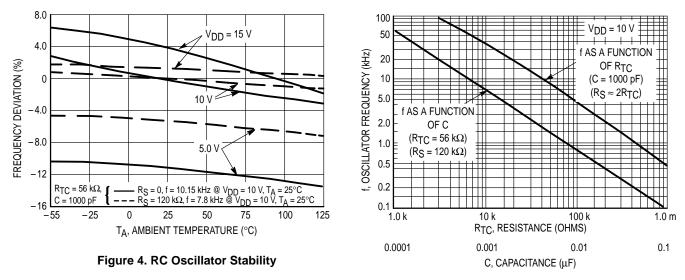

# **TYPICAL RC OSCILLATOR CHARACTERISTICS**

Figure 5. RC Oscillator Frequency as a Function of  $R_{tc}$  and  $C_{tc}$

#### **OPERATING CHARACTERISTICS**

With Auto Reset pin set to a "0" the counter circuit is initialized by turning on power. Or with power already on, the counter circuit is reset when the Master Reset pin is set to a "1". Both types of reset will result in synchronously resetting all counter stages independent of counter state. Auto Reset pin when set to a "1" provides a low power operation.

The RC oscillator as shown in Figure 3 will oscillate with a frequency determined by the external RC network i.e.,

$$\begin{split} f = \frac{1}{2.3 \ R_{tc} C_{tc}} & \text{if } (1 \ \text{kHz} \le f \le 100 \ \text{kHz}) \\ \text{and} & R_S \approx 2 \ R_{tc} & \text{where } R_S \ge 10 \ \text{k}\Omega \end{split}$$

The time select inputs (A and B) provide a two-bit address to output any one of four counter stages  $(2^8, 2^{10}, 2^{13} \text{ and} 2^{16})$ . The  $2^n$  counts as shown in the Frequency Selection Table represents the Q output of the N<sup>th</sup> stage of the counter. When A is "1",  $2^{16}$  is selected for both states of B. However,

The  $Q/\overline{Q}$  select output control pin provides for a choice of output level. When the counter is in a reset condition and  $Q/\overline{Q}$  select pin is set to a "0" the Q output is a "0", correspondingly when  $Q/\overline{Q}$  select pin is set to a "1" the Q output is a "1".

When the mode control pin is set to a "1", the selected count is continually transmitted to the output. But, with mode pin "0" and after a reset condition the R<sub>S</sub> flip–flop (see Expanded Block Diagram) resets, counting commences, and after  $2^{n-1}$  counts the R<sub>S</sub> flip–flop sets which causes the output to change state. Hence, after another  $2^{n-1}$  counts the output will not change. Thus, a Master Reset pulse must be applied or a change in the mode pin level is required to reset the single cycle operation.

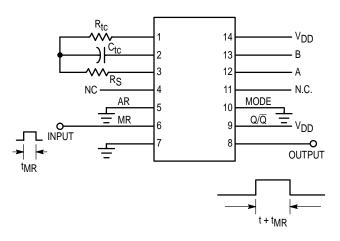

# **DIGITAL TIMER APPLICATION**

When Master Reset (MR) receives a positive pulse, the internal counters and latch are reset. The Q output goes high and remains high until the selected (via A and B) number of clock pulses are counted, the Q output then goes low and remains low until another input pulse is received.

This "one shot" is fully retriggerable and as accurate as the input frequency. An external clock can be used (pin 3 is the clock input, pins 1 and 2 are outputs) if additional accuracy is needed.

Notice that a setup time equal to the desired pulse width output is required immediately following initial power up, during which time Q output will be high.

#### MOTOROLA CMOS LOGIC DATA

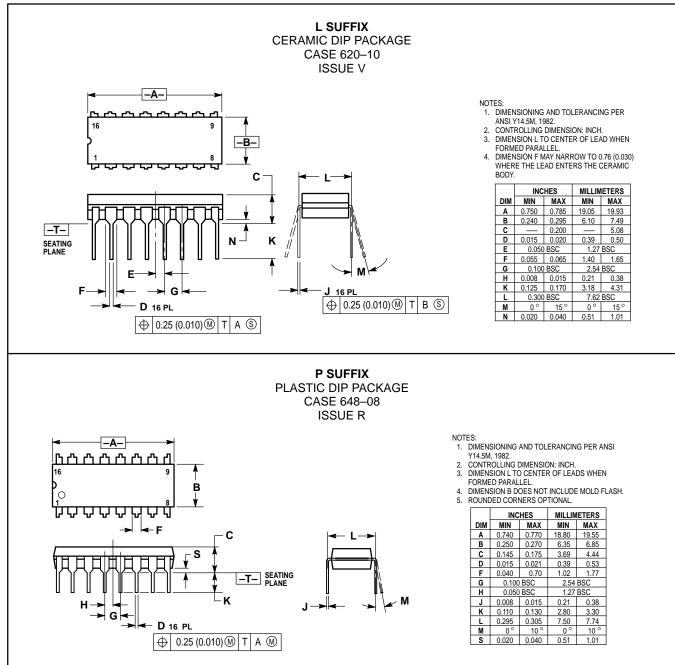

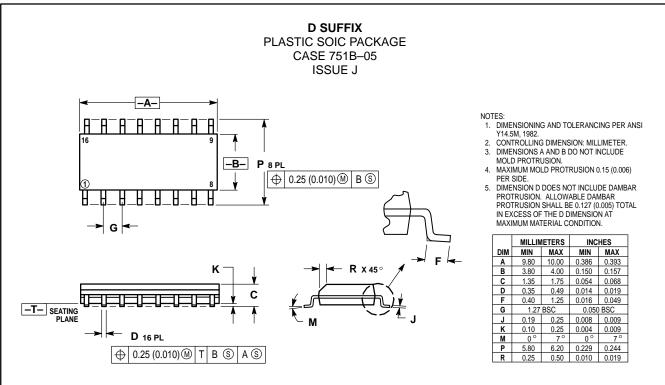

### **OUTLINE DIMENSIONS**

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and **...** are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036. 1–800–441–2447 or 602–303–5454

$\Diamond$

MFAX: RMFAX0@email.sps.mot.com – TOUCHTONE 602–244–6609 INTERNET: http://Design\_NET.com

JAPAN: Nippon Motorola Ltd.; Tatsumi–SPD–JLDC, 6F Seibu–Butsuryu–Center, 3–14–2 Tatsumi Koto–Ku, Tokyo 135, Japan. 03–81–3521–8315

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852–26629298