# 8228 SYSTEM CONTROLLER AND BUS DRIVER FOR 8080A CPU

- Single Chip System Control for MCS®-80 Systems

- Built-In Bidirectional Bus Driver for Data Bus Isolation

- Allows the Use of Multiple Byte Instructions (e.g. CALL) for Interrupt Acknowledge

- Reduces System Package Count

- User Selected Single Level Interrupt Vector (RST 7)

- Available in EXPRESSStandard Temperature Range

- Available in 28-Lead Cerdip and Plastic Packages

(See Packaging Spec, Order #231369)

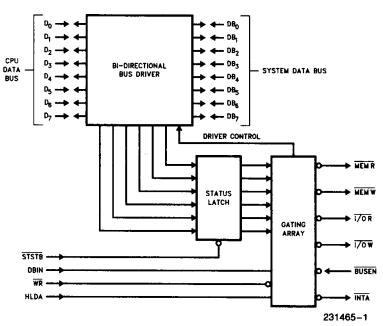

The Intel 8228 is a single chip system controller and bus driver for MCS®-80. It generates all signals required to directly interface MCS-80 family RAM, ROM, and I/O components.

A bidirectional bus driver is included to provide high system TTL fan-out. It also provides isolation of the 8080 data bus from memory and I/O. This allows for the optimization of control signals, enabling the systems designer to use slower memory and I/O. The isolation of the bus driver also provides for enhanced system noise immunity.

A user selected single level interrupt vector (RST 7) is provided to simplify real time, interrupt driven, small system requirements. The 8228 also generates the correct control signals to allow the use of multiple byte instructions (e.g., CALL) in response to an interrupt acknowledge by the 8080A. This feature permits large, interrupt driven systems to have an unlimited number of interrupt levels.

The 8228 is designed to support a wide variety of system bus structures and also reduce system package count for cost effective, reliable design of MCS-80 systems.

### NOTE:

The specifications for the 3228 are identical with those for the 8228.

| D7-DO        | Data Bus (8080 Side)   |

|--------------|------------------------|

| D87-D80      | Date Bus (System Side) |

| I/OR         | I/O Read               |

| 1/ <b>OW</b> | I/O Write              |

| MEMA         | Memory Read            |

| MEMW         | Memory Write           |

| DBIN         | DBIN (from 8080)       |

| INTA  | Interrupt Acknowledge     |

|-------|---------------------------|

| HLDA  | HLDA (from 8080)          |

| WR    | WIR (from 8080)           |

| BUSEN | Bus Enable Input          |

| डाडाछ | Status Strobe (from 8224) |

| Vcc   | + 5V                      |

| GND   | 0 Volts                   |

Figure 2. Pin Configuration

November 1992 Order Number: 231465-002

1-55

### **ABSOLUTE MAXIMUM RATINGS\***

| Temperature Under Bias          | 0°C to +70°C    |

|---------------------------------|-----------------|

| Storage Temperature             | -65°C to +150°C |

| Supply Voltage, V <sub>CC</sub> | 0.5V to +7V     |

| Input Voltage                   | 1.5 to + 7V     |

| Output Current                  | 100 mA          |

NOTICE: This is a production data sheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

## **D.C. CHARACTERISTICS** $T_A = 0^{\circ}C$ to $+70^{\circ}C$ , $V_{CC} = 5V \pm 5\%$

| Symbol          | Parameter                              |                                                                                       | Limits |        |      |      |                                         |  |

|-----------------|----------------------------------------|---------------------------------------------------------------------------------------|--------|--------|------|------|-----------------------------------------|--|

| Symbol          |                                        |                                                                                       | Min    | Typ(1) | Max  | Unit | Test Conditions                         |  |

| Vc              | Input Clamp Voltage,<br>All Input      |                                                                                       |        | 0.75   | -1.0 | ٧    | $V_{CC} = 4.75V; I_{C} = -5 \text{ mA}$ |  |

| lF              | Input Load Current                     | STSTB                                                                                 |        |        | 500  | μΑ   | V <sub>CC</sub> = 5.25V                 |  |

|                 |                                        | D <sub>2</sub> & D <sub>6</sub>                                                       |        |        | 750  | μΑ   | V <sub>F</sub> = 0.45V                  |  |

|                 |                                        | D <sub>0</sub> , D <sub>1</sub> , D <sub>4</sub> ,<br>D <sub>5</sub> & D <sub>7</sub> |        |        | 250  | μΑ   |                                         |  |

|                 |                                        | All Other Inputs                                                                      |        |        | 250  | μΑ   |                                         |  |

| I <sub>R</sub>  | Input Leakage Current                  | STSTB                                                                                 |        |        | 100  | μΑ   | $V_{CC} = 5.25V$                        |  |

|                 |                                        | DB <sub>0</sub> -DB <sub>7</sub>                                                      |        |        | 20   | μΑ   | $V_R = 5.25V$                           |  |

|                 |                                        | All Other Inputs                                                                      |        |        | 100  | μΑ   |                                         |  |

| V <sub>TH</sub> | Input Threshold<br>Voltage, All Inputs |                                                                                       | 0.8    |        | 2.0  | ٧    | V <sub>CC</sub> = 5V                    |  |

| Icc             | Power Supply Current                   |                                                                                       |        | 140    | 190  | mA   | V <sub>CC</sub> = 5.25V                 |  |

| V <sub>OL</sub> | Output Low Voltage                     | D <sub>0</sub> -D <sub>7</sub>                                                        |        |        | 0.45 | ٧    | $V_{CC} = 4.75V; I_{OL} = 2 \text{ mA}$ |  |

|                 |                                        | All Other Outputs                                                                     |        |        | 0.45 | ٧    | I <sub>OL</sub> = 10 mA                 |  |

| V <sub>OH</sub> | Output High Voltage                    | D <sub>0</sub> -D <sub>7</sub>                                                        | 3.6    | 3.8    |      | ٧    | $V_{CC} = 4.75V; I_{OH} = -10\mu A$     |  |

|                 |                                        | All Other Outputs                                                                     | 2.4    |        |      | ٧    | I <sub>OH</sub> = -1 mA                 |  |

| los             | Short Circuit Current, All Outputs     |                                                                                       | 15     |        | 90   | mA   | V <sub>CC</sub> = 5V                    |  |

| IO (off)        |                                        |                                                                                       |        |        | 100  | μΑ   | $V_{CC} = 5.25V; V_{O} = 5.25V$         |  |

|                 | All Control Outputs                    |                                                                                       |        |        | -100 | μΑ   | $V_{O} = 0.45V$                         |  |

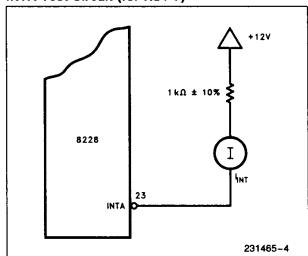

| INT             | INTA Current                           |                                                                                       |        |        | 5    | mA   | (See INTA Test Circuit)                 |  |

### **NOTE:**

<sup>1.</sup> Typical values are for  $T_A = 25^{\circ}C$  and nominal supply voltages.

# **CAPACITANCE** $V_{BIAS}=2.5V, V_{CC}=5.0V, T_A=25^{\circ}C, f=1$ MHz 1. This parameter is periodically sampled and not 100% tested.

| Cumbal           | Parameter                             |     | 11-14  |     |      |

|------------------|---------------------------------------|-----|--------|-----|------|

| Symbol           |                                       | Min | Typ(1) | Max | Unit |

| C <sub>IN</sub>  | Input Capacitance                     |     | 8      | 12  | pF   |

| C <sub>OUT</sub> | Output Capacitance<br>Control Signals |     | 7      | 15  | pF   |

| 1/0              | I/O Capacitance<br>(D or DB)          |     | 8      | 15  | pF   |

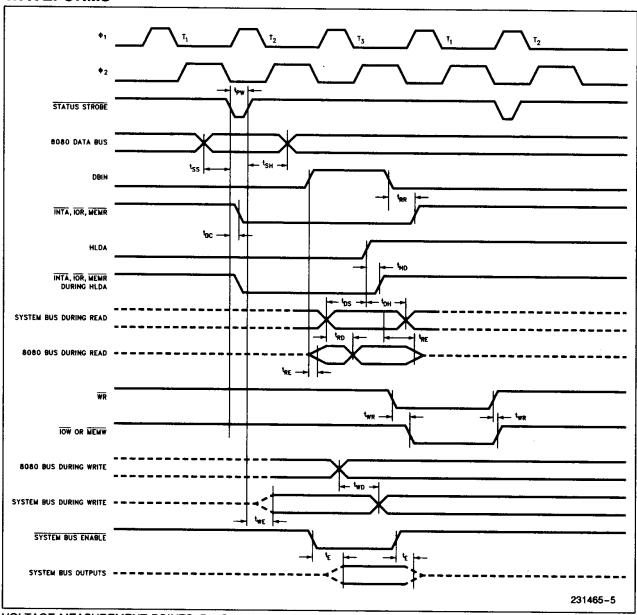

### **A.C. CHARACTERISTICS** $T_A = 0^{\circ}C$ to $+70^{\circ}C$ , $V_{CC} = 5V \pm 5\%$

| Symbol          | Davarratar                                                                                                     | Limits |     | 33   | 0                       |

|-----------------|----------------------------------------------------------------------------------------------------------------|--------|-----|------|-------------------------|

|                 | Parameter                                                                                                      |        | Max | Unit | Conditions              |

| tpw             | Width of Status Strobe                                                                                         | 22     |     | ns   |                         |

| tss             | Setup Time, Status Inputs D <sub>0</sub> -D <sub>7</sub>                                                       | 8      |     | ns   |                         |

| tsH             | Hold Time, Status Inputs D <sub>0</sub> -D <sub>7</sub>                                                        | 5      |     | ns   |                         |

| t <sub>DC</sub> | Delay from STSTB to any Control Signal                                                                         | 20     | 60  | ns   | C <sub>L</sub> = 100 pF |

| t <sub>RR</sub> | Delay from DBIN to Control Outputs                                                                             |        | 30  | ns   | $C_{L} = 100  pF$       |

| t <sub>RE</sub> | Delay from DBIN to Enable/Disable 8080 Bus                                                                     |        | 45  | ns   | $C_L = 25 pF$           |

| t <sub>RD</sub> | Delay from System Bus to 8080 Bus during Read                                                                  |        | 30  | ns   | $C_{L} = 25  pF$        |

| t <sub>WR</sub> | Delay from WR to Control Outputs                                                                               | 5      | 45  | ns   | $C_{L} = 100  pF$       |

| twe             | Delay to Enable System Bus DB <sub>0</sub> -DB <sub>7</sub> after STSTB                                        |        | 30  | ns   | $C_{L} = 100  pF$       |

| t <sub>WD</sub> | Delay from 8080 Bus D <sub>0</sub> -D <sub>7</sub> to System Bus DB <sub>0</sub> -DB <sub>7</sub> during Write | 5      | 40  | ns   | C <sub>L</sub> = 100 pF |

| tE              | Delay from System Bus Enable to System Bus DB <sub>0</sub> -DB <sub>7</sub>                                    |        | 30  | ns   | $C_{L} = 100  pF$       |

| t <sub>HD</sub> | HLDA to Read Status Outputs                                                                                    |        | 25  | ns   |                         |

| tDS             | Setup Time, System Bus Inputs to HLDA                                                                          | 10     |     | ns   |                         |

| t <sub>DH</sub> | Hold Time, System Bus Inputs to HLDA                                                                           | 20     |     | ns   | $C_{L} = 100  pF$       |

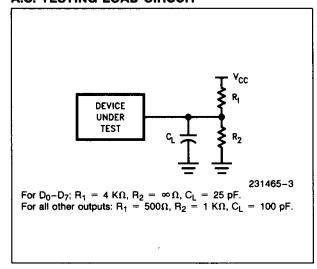

### A.C. TESTING LOAD CIRCUIT

### **INTA Test Circuit (for RST 7)**

### **WAVEFORMS**

VOLTAGE MEASUREMENT POINTS: D<sub>0</sub>-D<sub>7</sub> (when outputs) Logic "0" = 0.8V, Logic "1" = 3.0V. All other signals measured at 1.5V.