Data Book

16bit Micro controller TLCS-900/L1 series

**TMP91C820AF**

Rev. 2.5 07/December/2001

**TOSHIBA** contents

# ----- Contents -----

# TLCS-900/L1 LSI DEVICES TMP91C820AF

| 1. | Outl           | ine and Device Characteristics | 91C820A-1   |

|----|----------------|--------------------------------|-------------|

| 2. | Pin A          | Assignment and Pin Functions   | 91C820A-4   |

|    | 2.1 Pin A      | ssignment Diagram              | 91C820A-4   |

|    | 2.2 Pin N      | ame and Functions              | 91C820A-6   |

| 3. | Oper           | ration                         | 91C820A-10  |

|    | <b>3.1 CPU</b> |                                | 91C820A-10  |

|    | 3.1.1          | Reset                          | 91C820A-10  |

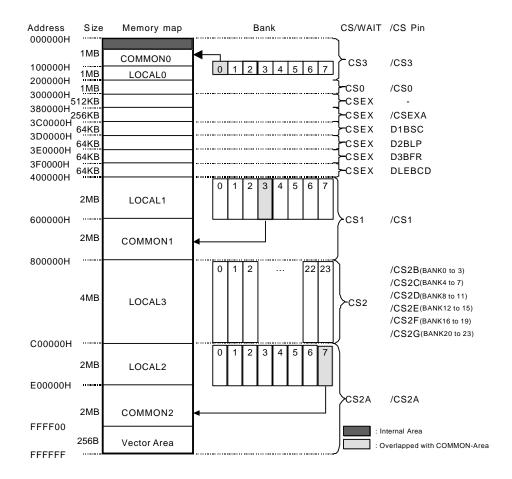

|    | 3.2 Memo       | ory Map                        | 91C820A-12  |

|    | 3.3 Triple     | e Clock, Stand-by Function     | 91C820A-13  |

|    | 3.4 Interr     | rupts                          | 91C820A-37  |

|    | 3.5 Funct      | ions of Ports                  | 91C820A-52  |

|    | 3.5.1          | Port 0                         | 91C820A-57  |

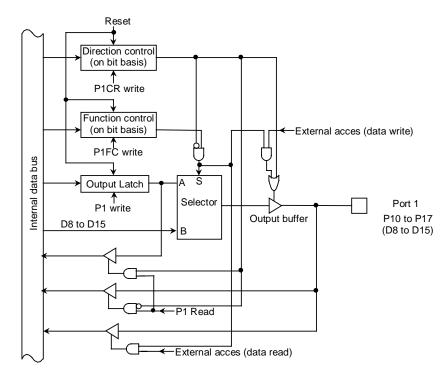

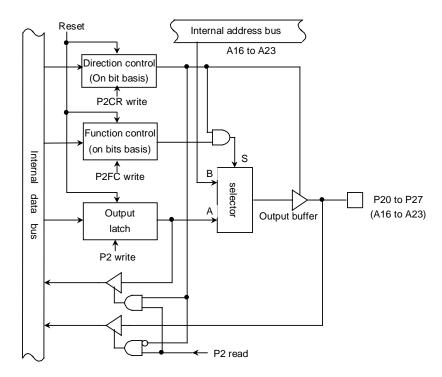

|    | 3.5.2          | Port 1                         | 91C820A-58  |

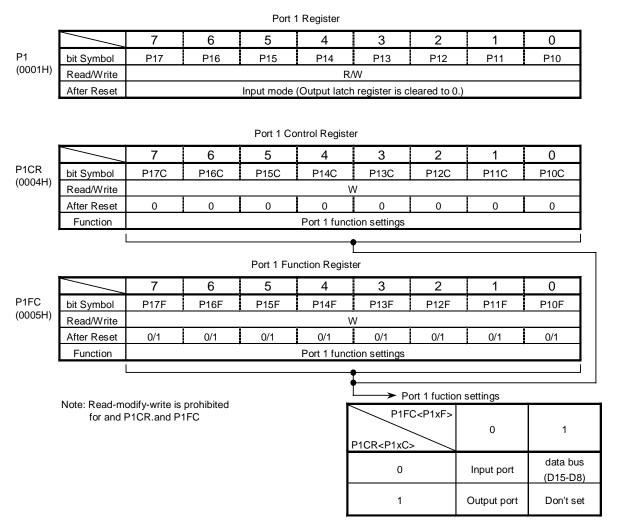

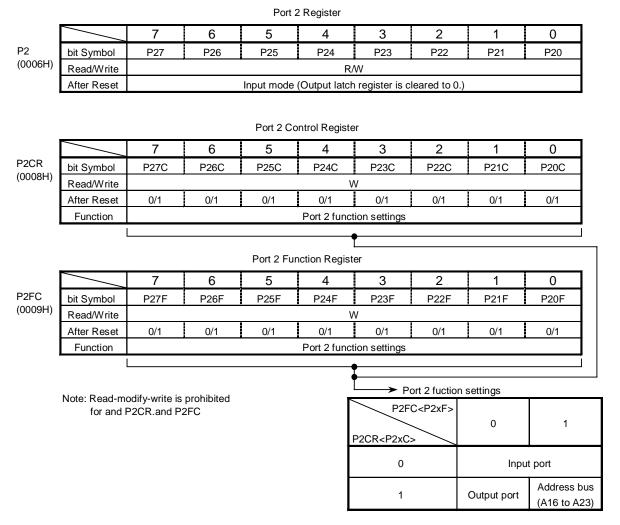

|    | 3.5.3          | Port 2                         | 91C820A-60  |

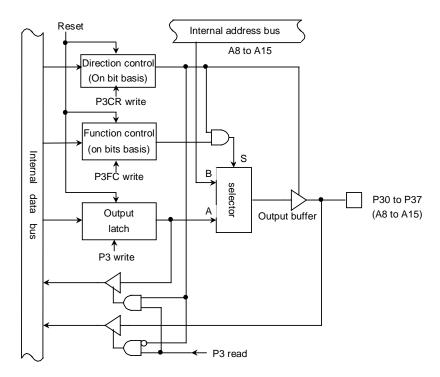

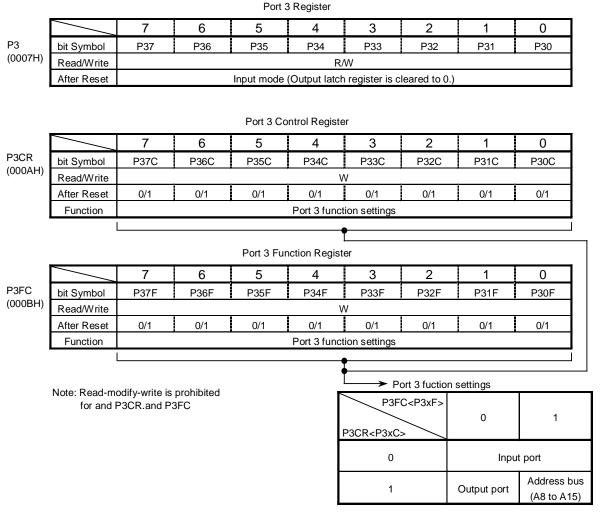

|    | 3.5.4          | Port 3                         | 91C820A-62  |

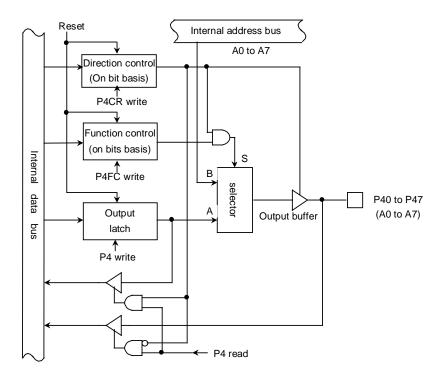

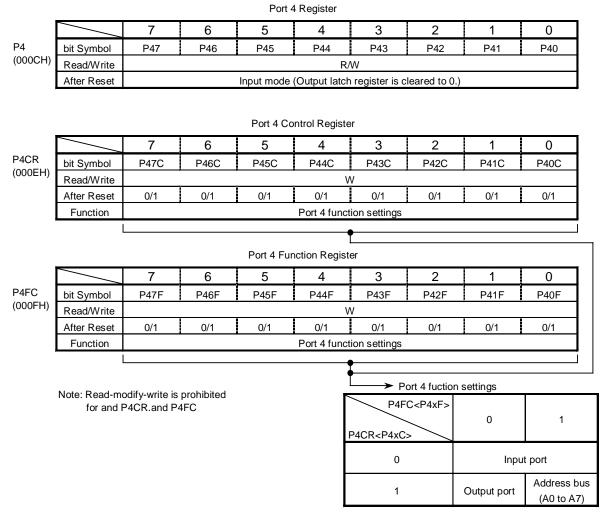

|    | 3.5.5          | Port 4                         | 91C820A-64  |

|    | 3.5.6          | Port Z                         | 91C820A-66  |

|    | 3.5.7          | Port 5                         | 91C820A-70  |

|    | 3.5.8          | Port 6                         | 91C820A-72  |

|    | 3.5.9          | Port 7                         | 91C820A-73  |

|    | 3.5.10         | Port 8                         | 91C820A-79  |

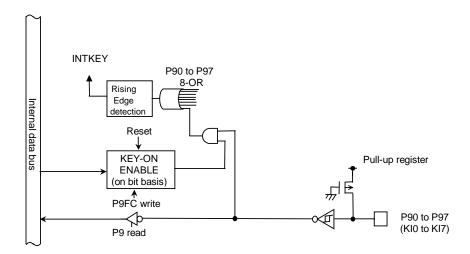

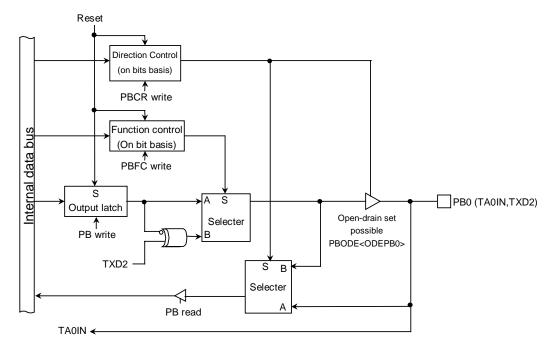

|    | 3.5.11         | Port 9                         | 91C820A-80  |

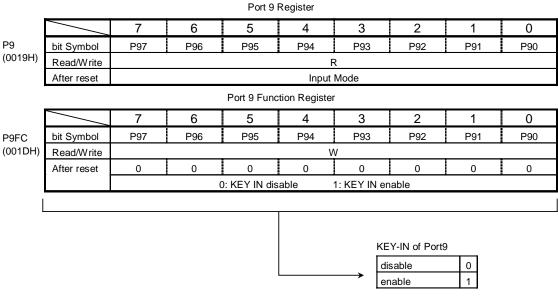

|    | 3.5.12         | Port A                         | 91C820A-81  |

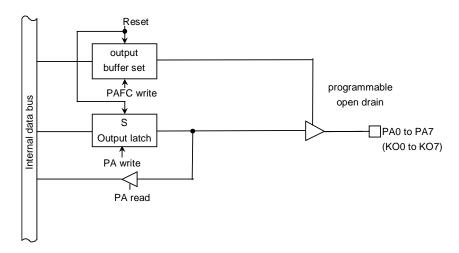

|    | 3.5.13         | Port B                         | 91C820A-82  |

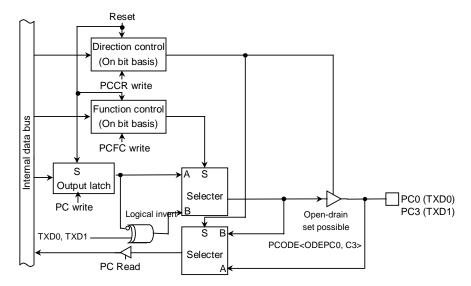

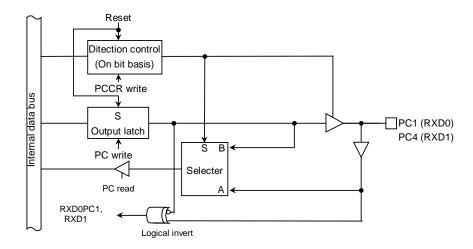

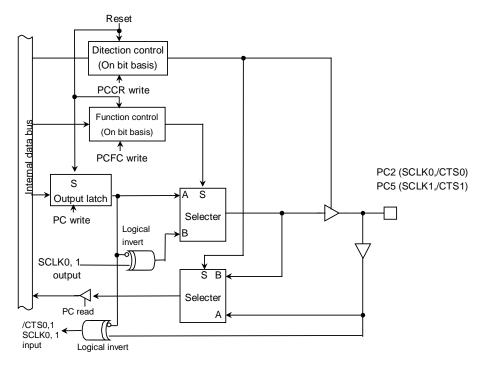

|    | 3.5.14         | Port C                         | 91C820A-86  |

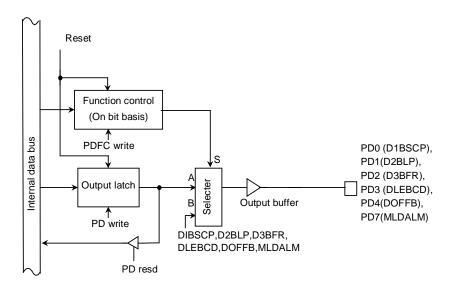

|    | 3.5.15         | Port D                         | 91C820A-89  |

|    | 3.5.16         | Port E                         | 91C820A-91  |

|    | 3.5.17         | Port F                         | 91C820A-92  |

|    | 3.6 Chip       | Select/Wait Controller         | 91C820A-93  |

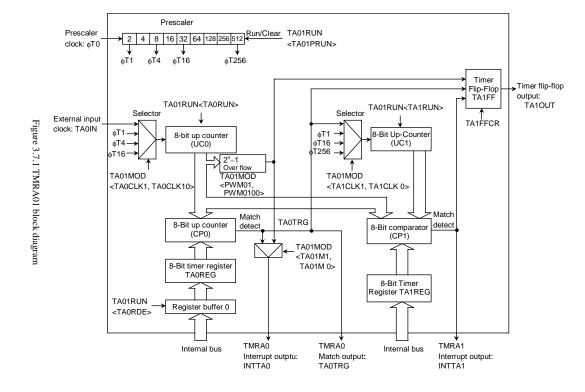

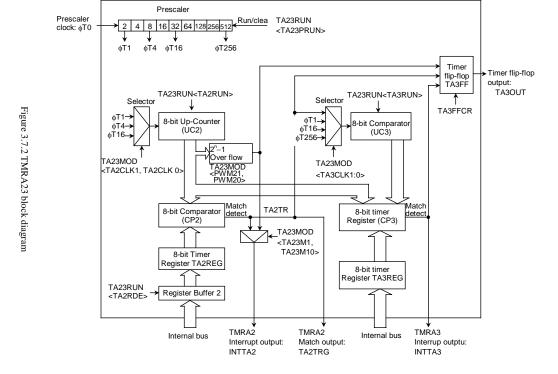

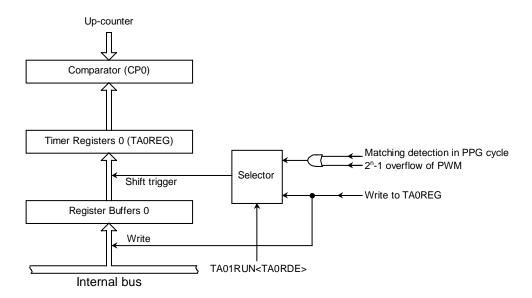

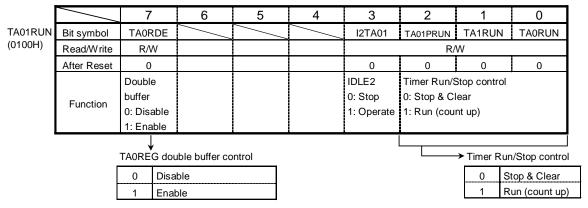

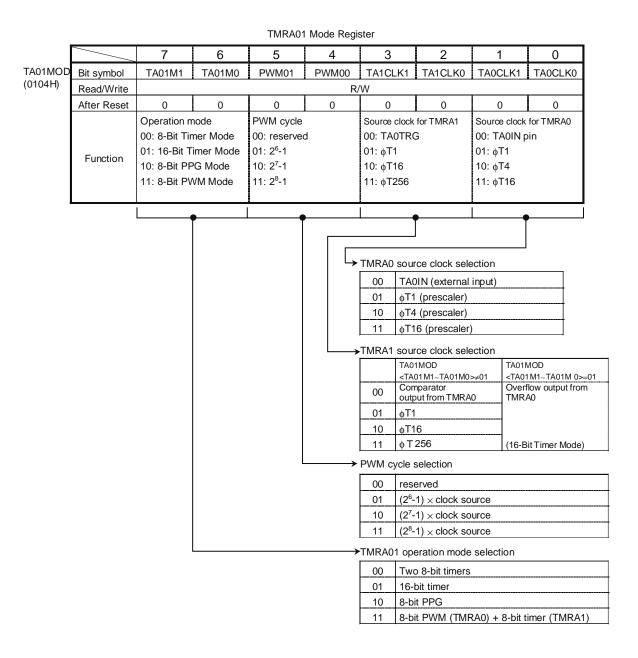

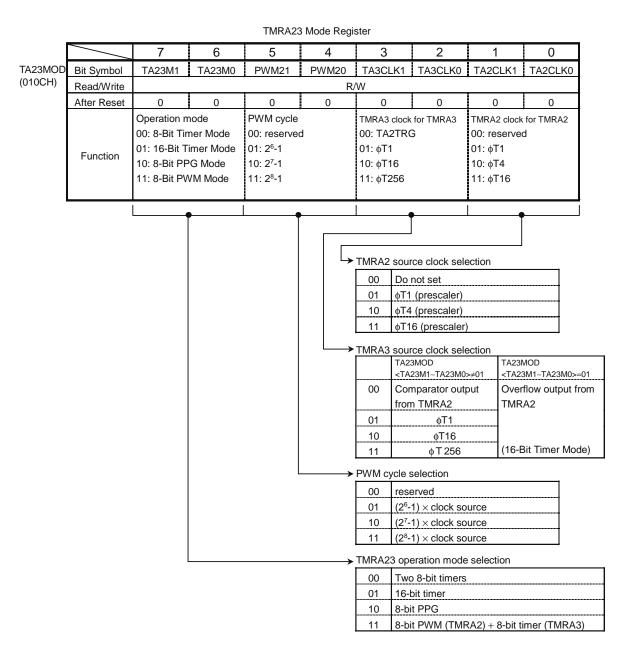

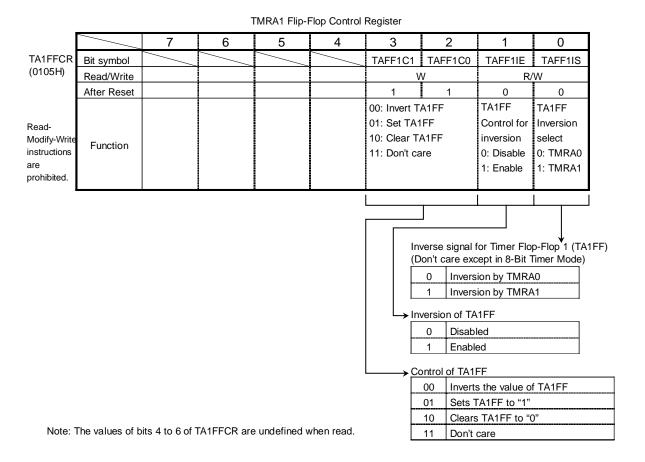

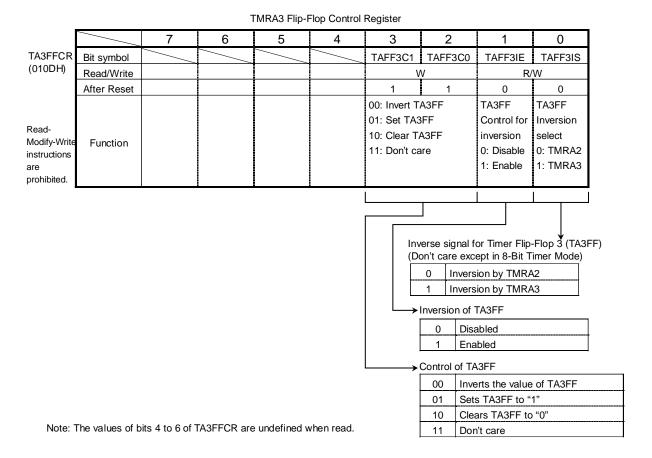

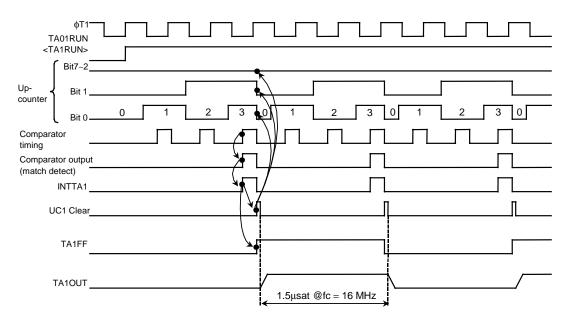

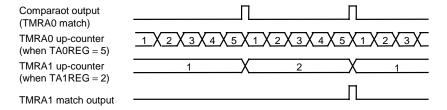

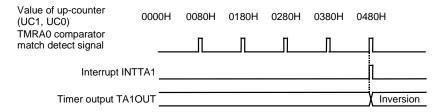

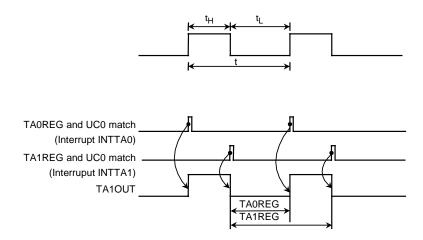

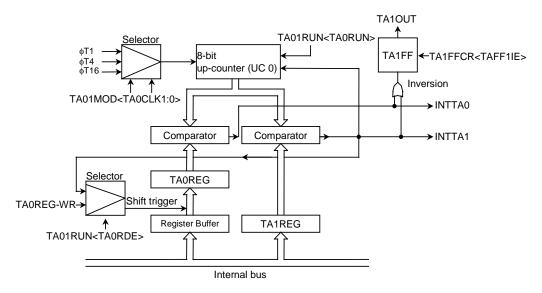

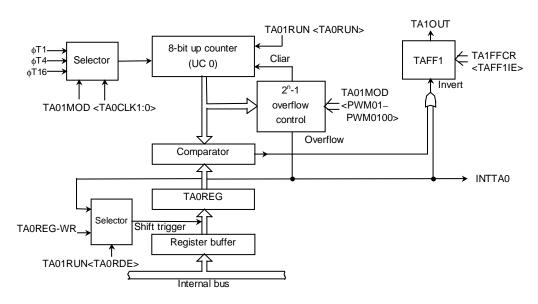

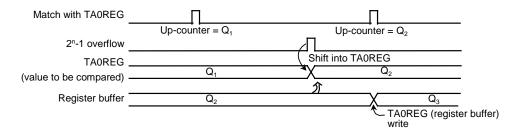

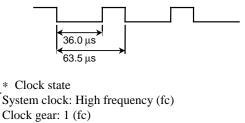

|    | 3.7 8-bit      | Timers (TMRA)                  | 91C820A-103 |

|    | 3.8 MMU        | J                              | 91C820A-124 |

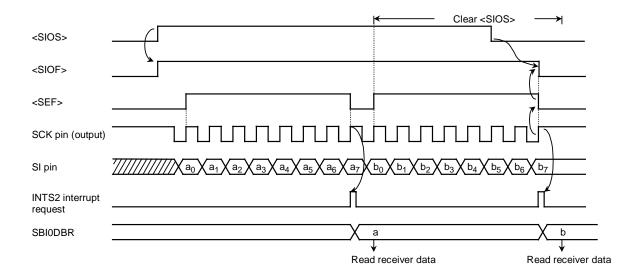

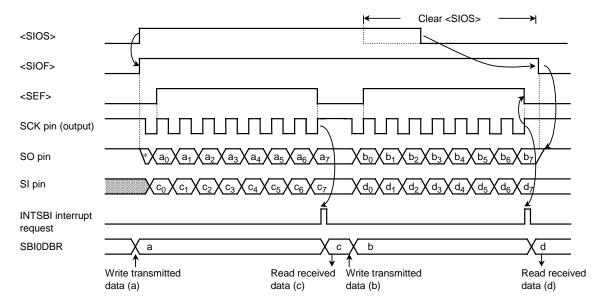

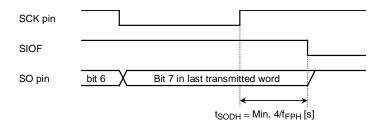

|    | 3.9 Serial     | Channel                        | 91C820A-135 |

|    | 3.10Serial     | Bus Interface                  | 91C820A-171 |

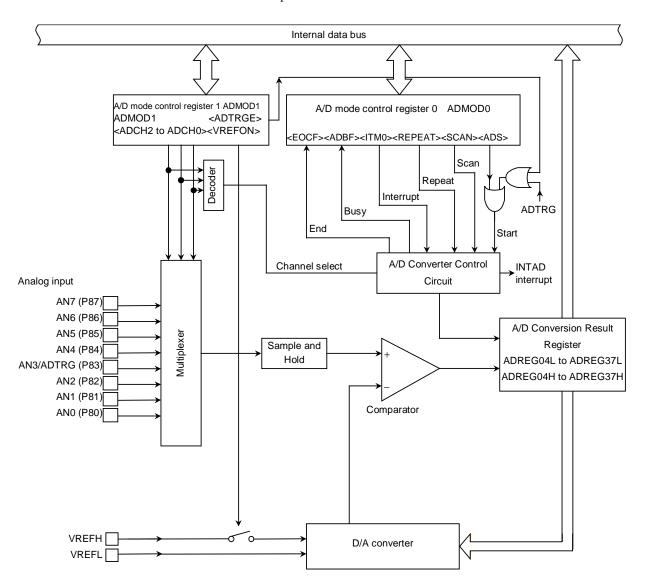

|    | 3.11Analo      | g/Digital Converter            | 91C820A-199 |

|    | 3.12Watcl      | n Dog Timer                    | 91C820A-209 |

|    | 3.13RTC        |                                | 91C820A-214 |

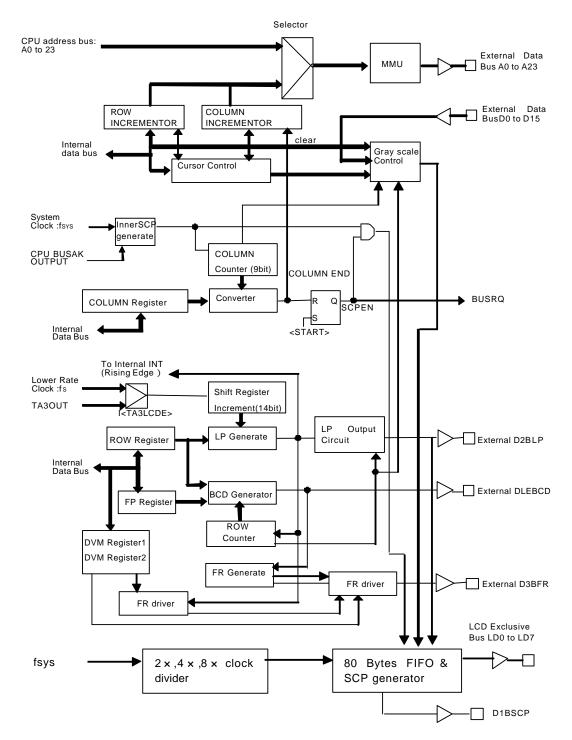

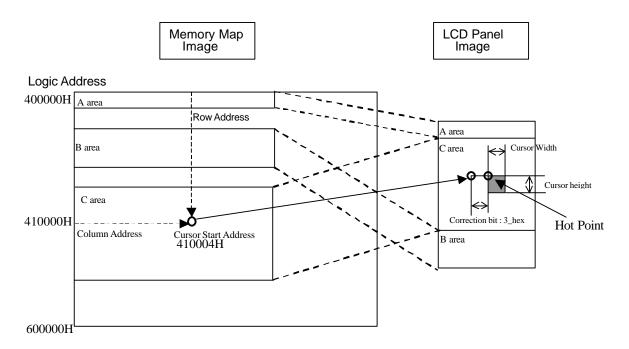

|    | 3.14LCD        | Controller                     | 91C820A-228 |

|    | 3.15Melod      | ly/Alarm Generator             | 91C820A-266 |

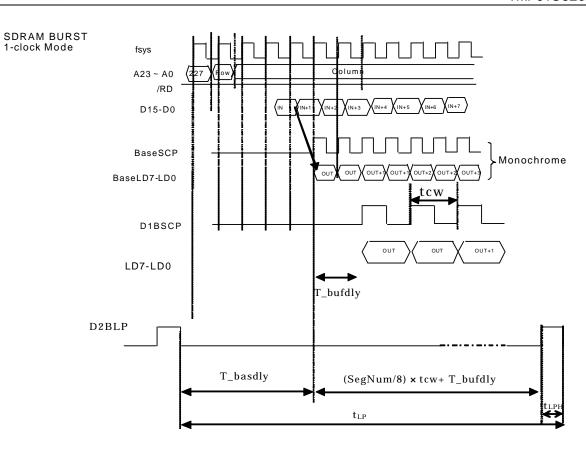

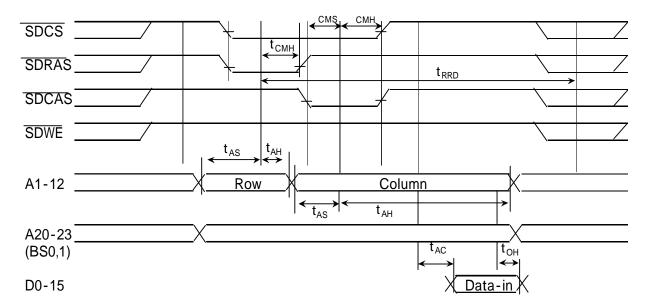

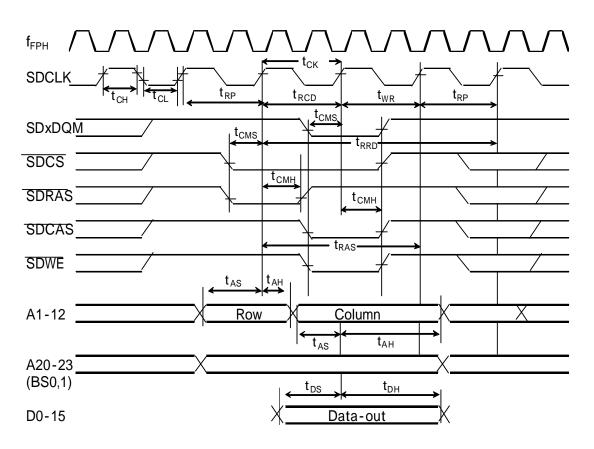

|    | 3.16SDRA       | AM Controller                  | 91C820A-272 |

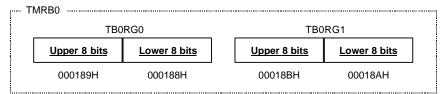

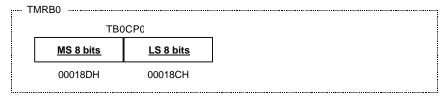

|    | 3.1716-bit     | Timers (TMRB)                  | 91C820A-282 |

|    |                | ware Stand-by Function         | 91C820A-291 |

| 4. |                | rical Characteristics          | 91C820A-292 |

| 5. | Tabl           | e of SFR                       | 91C820A-310 |

| 6. | Poin           | ts to Note and Restrictions    | 91C820A-346 |

| 7. | Pack           | age PKG-1                      | 91C820A-348 |

|    |                |                                |             |

Data Book modification history

| Data Book modification hist Rev./Date |             | Modification item                                                       | Rageon        |

|---------------------------------------|-------------|-------------------------------------------------------------------------|---------------|

| Nev./Date                             | page        |                                                                         | Reason        |

| Rev110/15-Mar-2001                    | 16          | Sample of DFM setting                                                   |               |

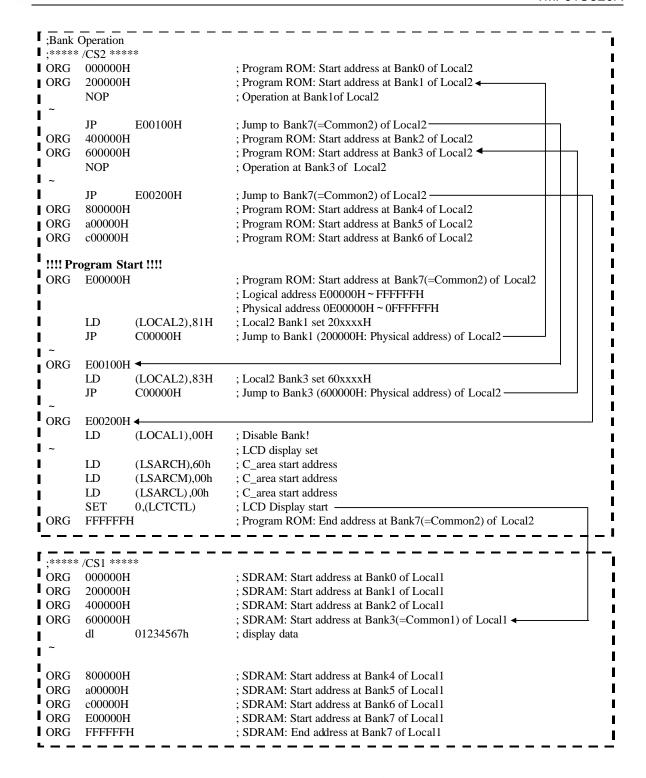

| Rev110/13-Mai-2001                    | 508<br>717  | Bank Operation S/W Example in MMU                                       |               |

|                                       | 717         | Stop condition generation in SBI Timing diagram for TMP91C820 Restar in |               |

|                                       | /10         | SBI                                                                     |               |

| Rev1.3/03-July-2001                   | 704         | SBI: Flocked>Clocked                                                    | Spell Mistake |

| Rev1.5/05-5u1y-2001                   | 705         | SBI: Receiver>Transmitter, Busy>Receiver                                | Word Mistake  |

|                                       | 721         | SBI: Always Write "0" Add                                               | Mistake       |

|                                       | 420         | SFR: generater>generator                                                | Spell mistake |

|                                       | 725         | SBI : (p6)=>(p7)                                                        | Spen mistake  |

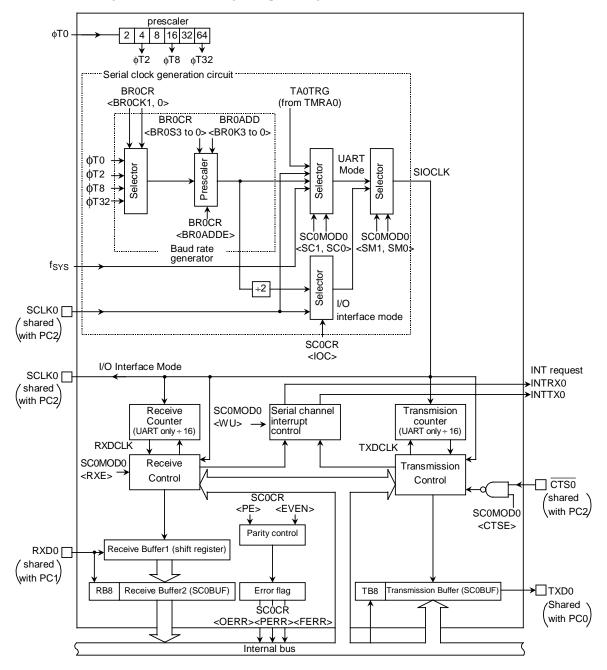

|                                       | 132         | SIO: fixed in the Figure                                                |               |

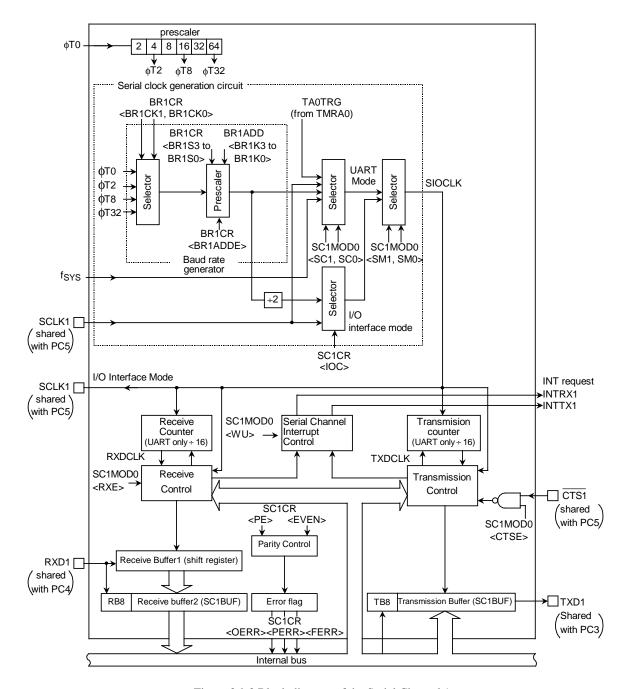

|                                       | 135         | SIO:SC0MOD0=>SC1MOD0 in the figure                                      |               |

|                                       | 136         |                                                                         |               |

|                                       | 130         | SIO: $1 \Rightarrow 2$ and remove partially in the                      |               |

|                                       | 150         | figure                                                                  |               |

|                                       | 156         | SIO: SC1BUF>SC2BUF                                                      |               |

|                                       | 17          | CLK: <drvoscl>fc&gt;fs&amp; bit 3 &amp; add</drvoscl>                   | mistake       |

|                                       | 050 000     | comment                                                                 |               |

|                                       | 259,260     | MLD : Special mode &selector added                                      | 3.61 . 3      |

|                                       | 145         | SIO: fixed except bit 9 in the table                                    | Mistake       |

|                                       | tytle       | "Chapter4" remove & "···" remove                                        |               |

|                                       | 500         | NOTE:TEST >TSET in the program                                          |               |

|                                       |             | 3.14 LCDC: change all                                                   |               |

| Rev2.0/07-August-2001                 | 14,17       | DFM: modify and add                                                     |               |

|                                       | 24,25       |                                                                         |               |

|                                       | 262         | MLD: "special mode" modify                                              |               |

|                                       | 13,16,      | DFM: modify and add                                                     |               |

|                                       | 23,24       |                                                                         |               |

|                                       | 17          | CLK:EMCCR3 BIT0:2 modify the                                            |               |

|                                       |             | explanation                                                             |               |

|                                       | 320         | SFR : EMCCR3 BIT0:2 modify the                                          |               |

|                                       |             | explanation                                                             |               |

|                                       | 127         | MMU:add the figure                                                      |               |

|                                       | 25,26       | CLK: P24:XT2->X2 P25:X1 $\rightarrow$ XT1 in the                        |               |

|                                       |             | figure                                                                  |               |

|                                       | 172         | SBI: bit6 modify                                                        |               |

|                                       | 184         | SBI:modify the figure                                                   |               |

|                                       | 178         | SBI: add the explanation                                                |               |

| Rev2.1/15-August-2001                 | LCDC        | Add the explanation                                                     |               |

| Rev2.2/21-August-2001                 | 5           | Add PAD layout                                                          |               |

| Rev2.3/21-August-2001                 | 14          | CPU : modify                                                            |               |

| Rev2.4/07-September-2001              | 248         | LCDC: modify the equation in the middle                                 |               |

|                                       |             | TA3OUT , "t_LP"→"tLP"                                                   |               |

|                                       | 242         | LCDC: add the explanation                                               |               |

|                                       | 306         | SIO Electrical characteristic misstake                                  |               |

|                                       | 259         | LCDC: add the NOTE                                                      |               |

|                                       | 307         | Oscilation circuit add (inset 2 pages)                                  |               |

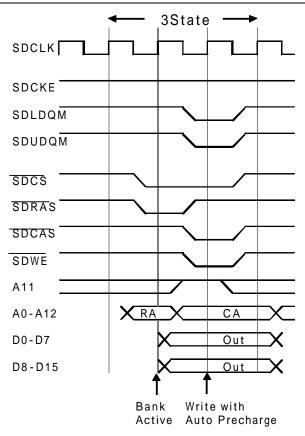

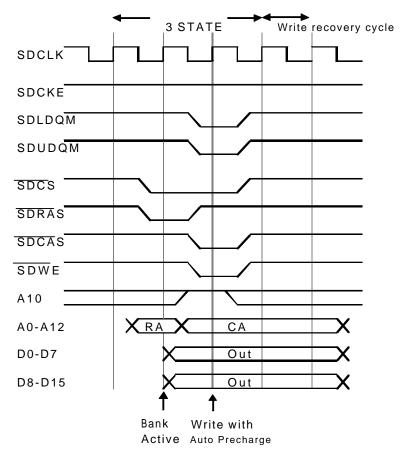

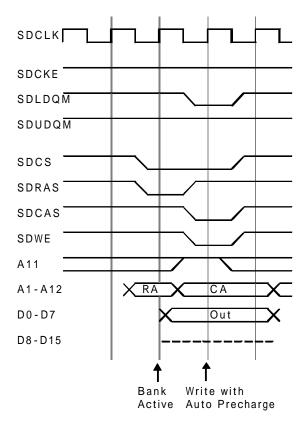

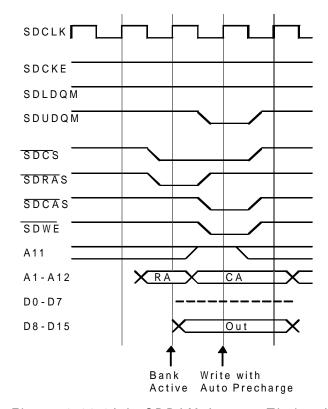

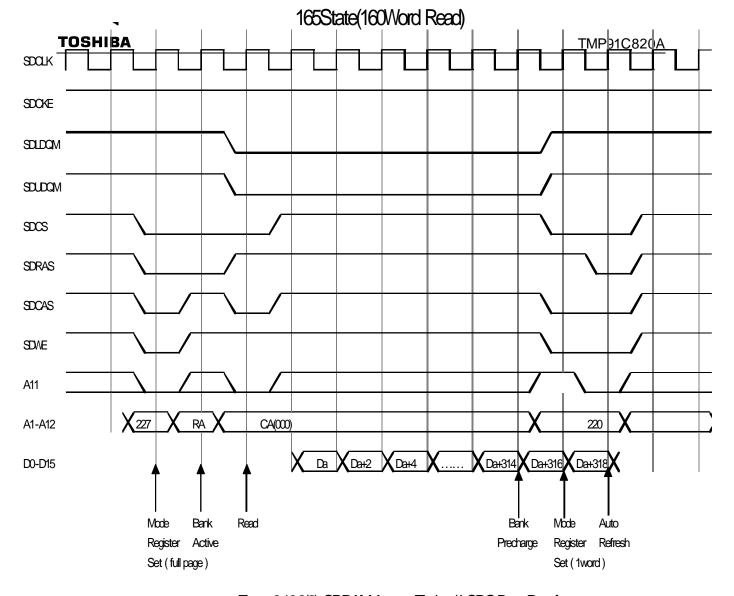

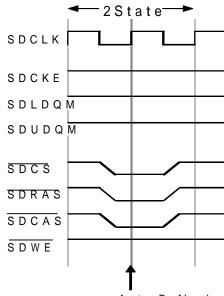

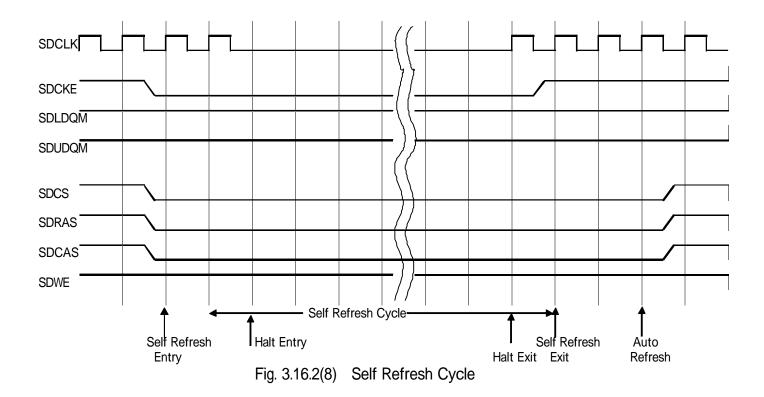

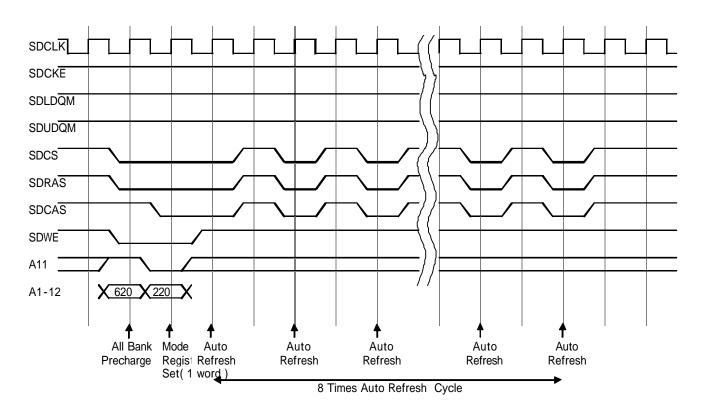

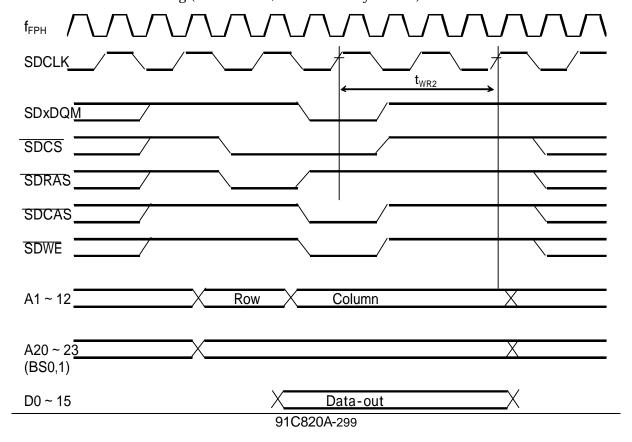

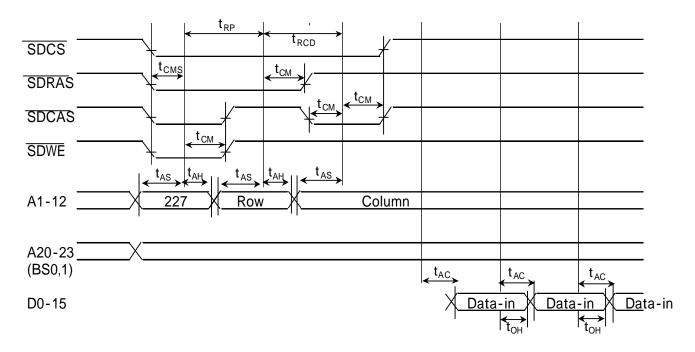

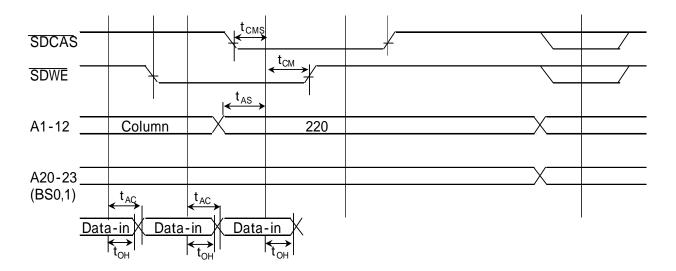

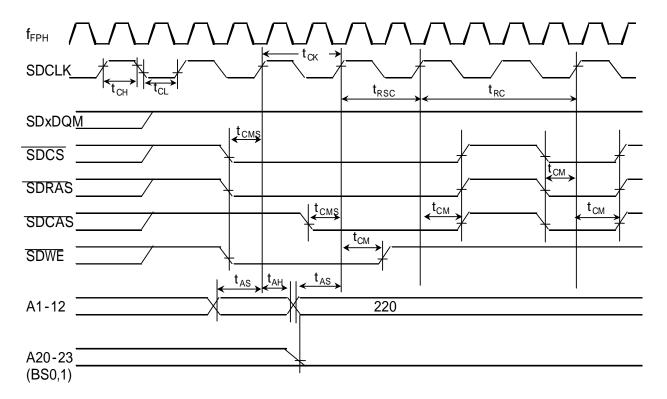

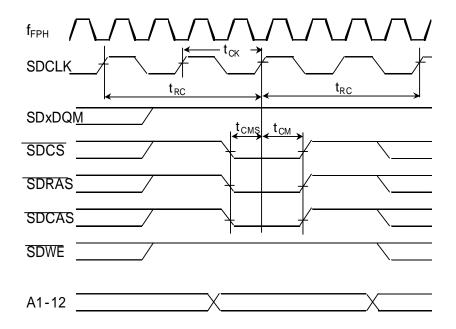

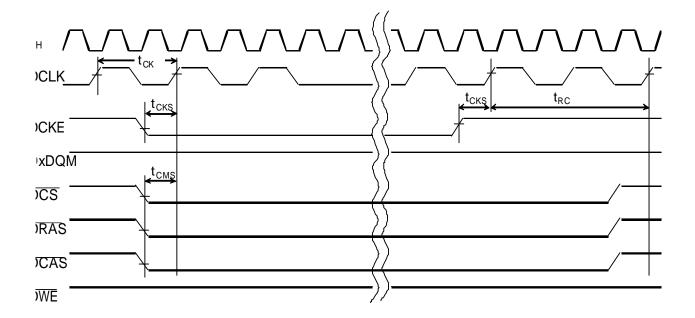

| Rev2.5/31-October-2001                | 276,280     | SDRAMC : modify and add the figure                                      |               |

|                                       |             | (insert 1 page)                                                         |               |

|                                       | 297,299,303 | SPEC: SDRAMC SPEC modify and add                                        |               |

|                                       | 309         | SPWC : Tc modify                                                        |               |

|                                       | 16          | CLK: (SYSCR2) modify                                                    |               |

|                                       | 229,234,244 | LCDC: add and modify the explanation                                    |               |

|                                       | 247,251     | LCDC : modify the explanation                                           |               |

|                                       |             |                                                                         |               |

**TOSHIBA** contents

| 248     | LCDC: TA3OUT equation modify                  |  |

|---------|-----------------------------------------------|--|

| 294,296 | SPEC: t <sub>DW</sub> ,t <sub>WW</sub> modify |  |

|         | •                                             |  |

|         |                                               |  |

|         |                                               |  |

|         |                                               |  |

|         |                                               |  |

Note: Each page number corresponds to each revision when modified.

# CMOS 16-Bit Microcontrollers TMP91C820AF

# OUTLINE AND FEATURES

TMP91C820AF is a high-speed 16-bit microcontroller designed for the control of various mid- to large-scale equipment.

TMP91C820AF comes in a 144-pin flat package.

Listed below are the features.

- (1) High-speed 16-bit CPU (900/L1 CPU)

- Instruction mnemonics are upward-compatible with TLCS-90/900

- 16 Mbytes of linear address space

- General-purpose registers and register banks

- 16-bit multiplication and division instructions; bit transfer and arithmetic instructions

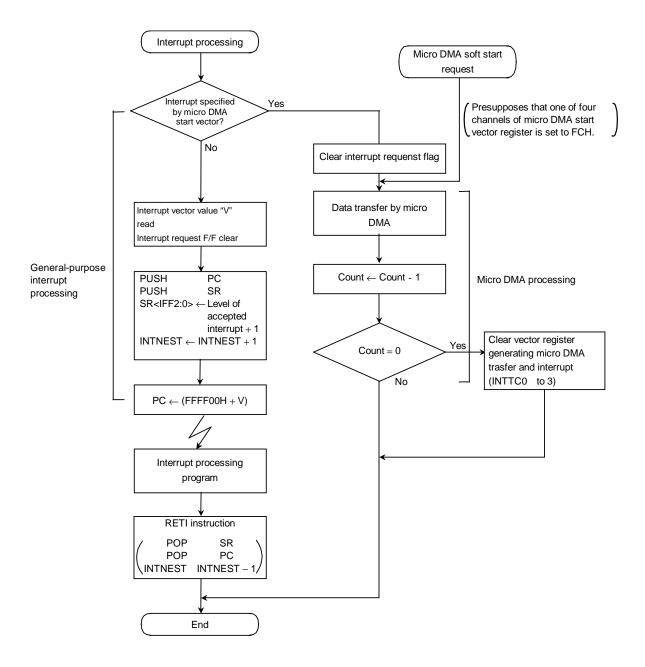

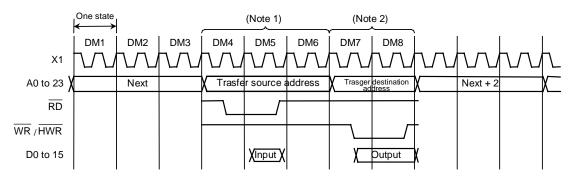

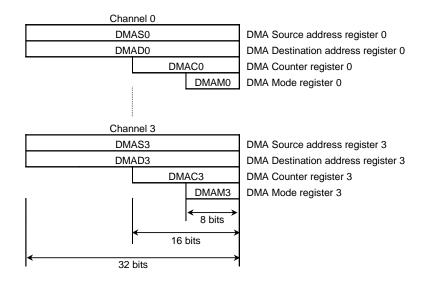

- Micro DMA: Four-channels (1.0 μs/2 bytes at 16 MHz)

- (2) Minimum instruction execution time: 111ns (at 36 MHz)

- (3) Built-in RAM: 8 Kbytes Built-in ROM: 8 Kbytes

- (4) External memory expansion

- Expandable up to 136M bytes (shared program/data area)

- Can simultaneously support 8-/16-bit width external data bus

- ... Dynamic data bus syzing

- Separate bus system

- (5) 8-bit timers: 4 channels

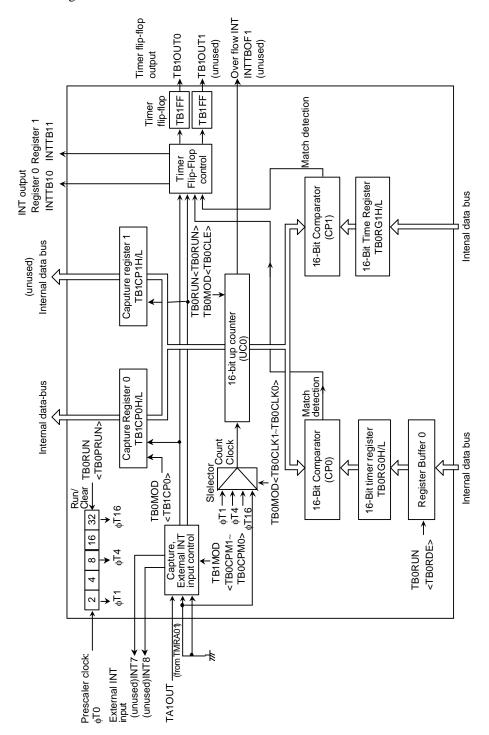

- (6) 16-bit timer/event counter: 1 channel

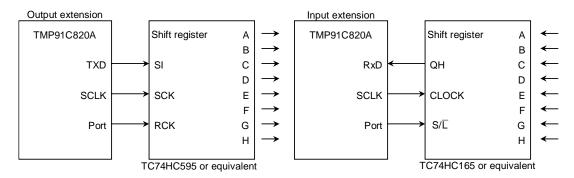

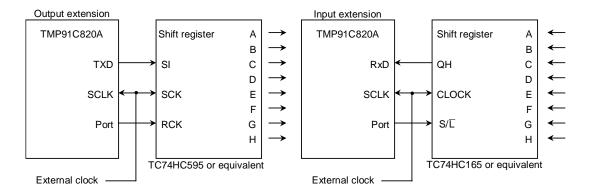

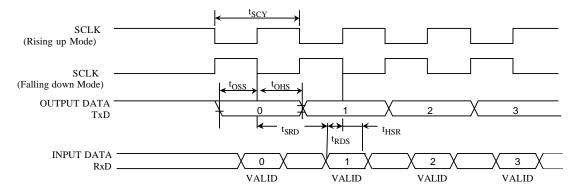

- (7) General-purpose serial interface: 3 channels

- UART/Synchronous mode

- IrDA

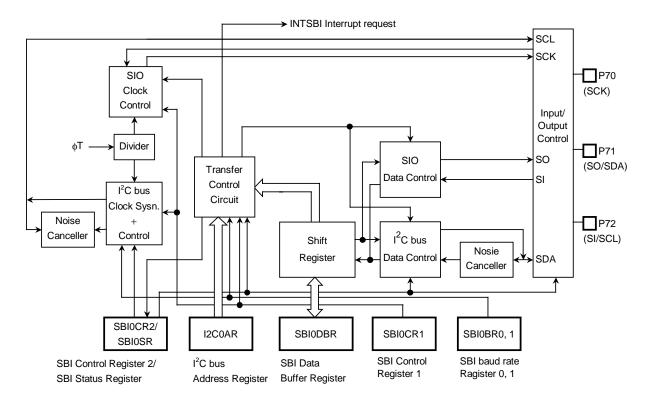

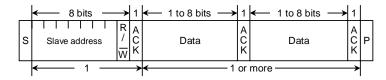

- (8) Serial bus interface: 1 channel

- I<sup>2</sup>C bus mode/clock synchronous select mode

980508TBA1

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance / Handling Precautions.

- TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

- The products described in this document are subject to foreign exchange and foreign trade laws.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA

CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is

granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

- · The information contained herein is subject to change without notice.

Purchase of TOSHIBA  $I^2C$  components conveys a license under the Philips  $I^2C$  Patent Rights to use these components in an  $I^2C$  system, provided that the system conforms to the  $I^2C$  Standard Specification as defined by Philips.

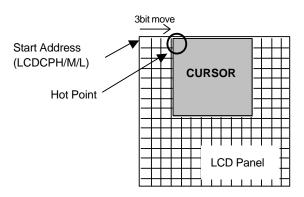

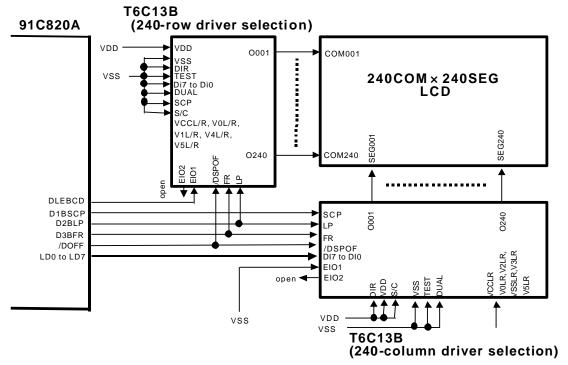

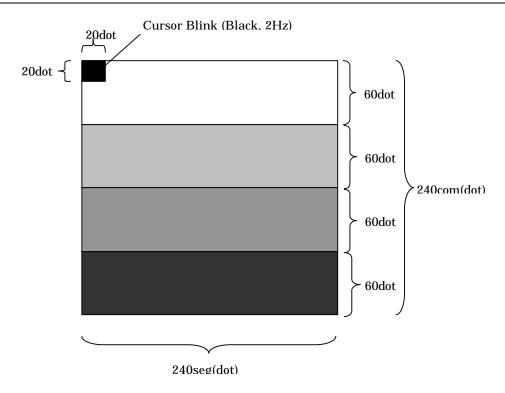

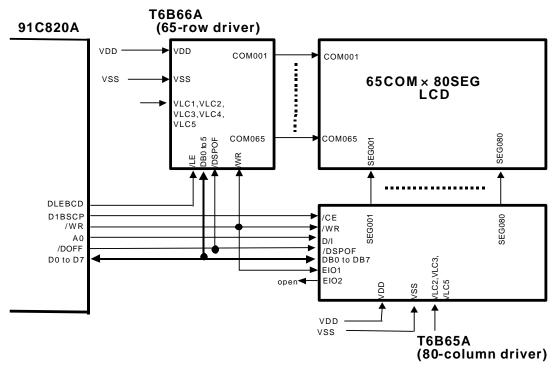

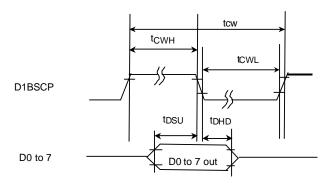

- (9) LCD controller

- Shift register/built-in RAM LCD driver

- Supported 16,8 and 4 Gray-levels and Black and White

- Hardware Blinking Cursor

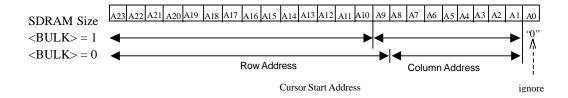

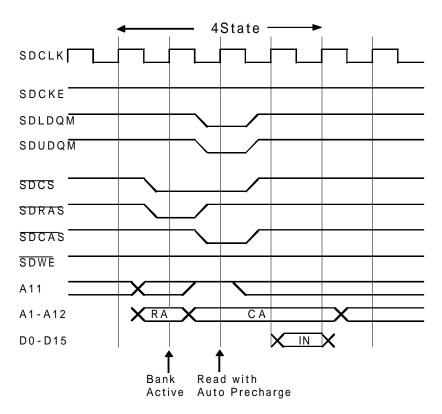

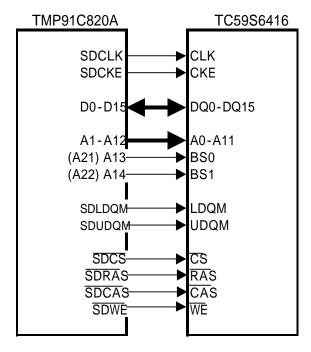

- (10) SDRAM Controller

- Supported 16M,64M and 128Mbit-SDRAM with 16bit Data-bus

- (11) Timer for real-time clock (RTC)

- Based on TC8521A

- (12) Key-on wake up (Interrupt key input)

- (13) 10-bit A/D converter: 8 channels

- (14) Watch dog timer

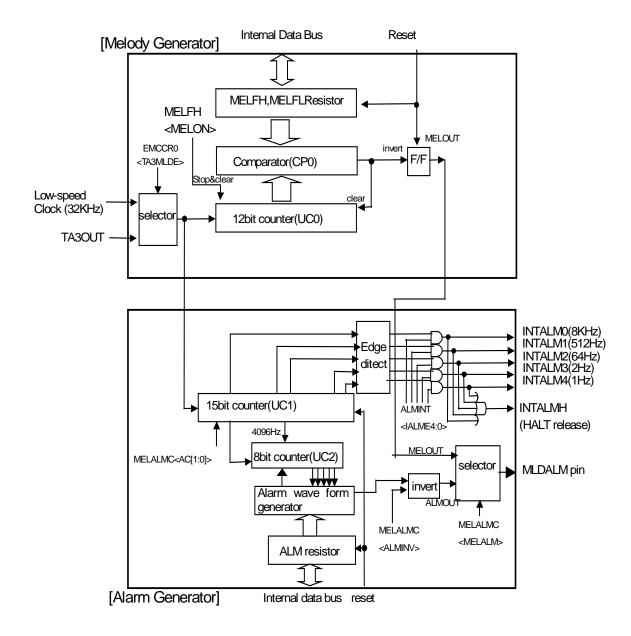

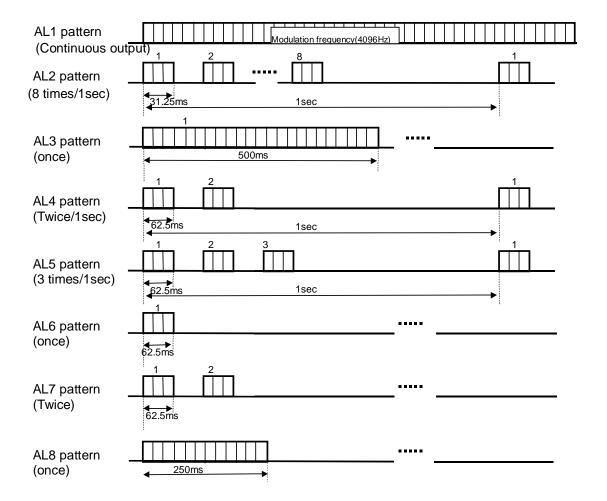

- (15) Melody/alarm generator

- Melody: Output of clock 4 to 5461Hz

- Alarm: Output of the 8 kinds of alarm pattern

- Output of the 5 kinds of interval interrupt

- (16) Chip select/Wait controller: 4 channels

- (17) MMU

- Expandable up to 136M bytes (4 local area/8bank method)

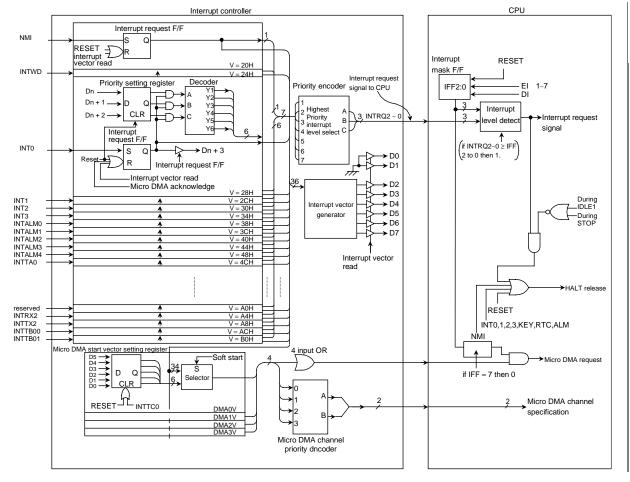

- (18) Interrupts: 43 interrupts

- 9 CPU interrupts: Software interrupt instruction and illegal instruction

- 28 internal interrupts: Seven selectable priority levels

- 6 external interrupts: Seven selectable priority levels(4-edge selectable)

- (19) Input/output ports: 77 pins (at External 16-bit data bus memory)

- (20) Stand-by function

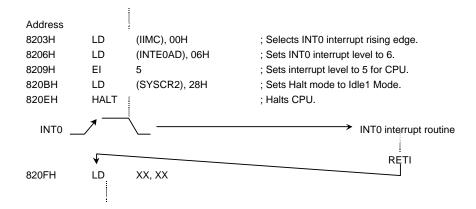

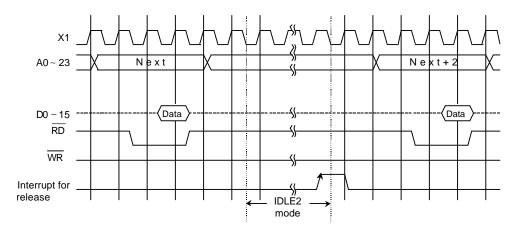

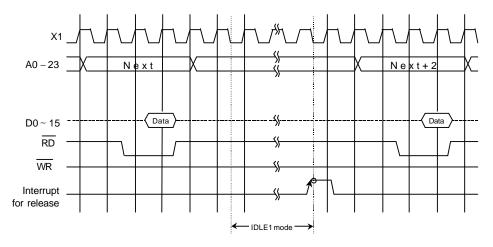

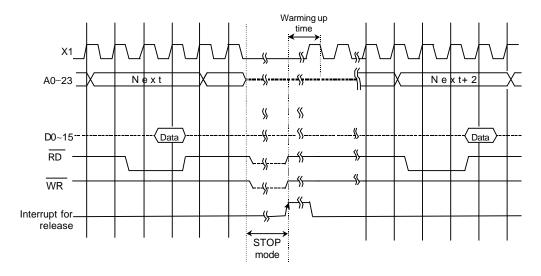

Three Halt modes: Idle2 (programmable), Idle1, Stop

- (21) Triple-clock controller

- Clock doubler (DFM)

- Clock gear function: Select a High-frequency clock fc to fc/16

- RTC (fs=32.768kHz)

- (22) Operating voltage

- VCC = 2.7 V to 3.6 V (fc max = 27 MHz)

- VCC = 3.0 V to 3.6 V (fc max = 36 MHz)

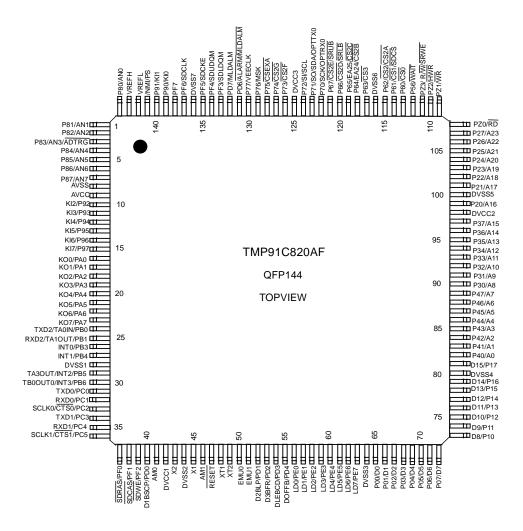

- (23) Package

- 144-pin QFP: LQFP144 P -1616 0.40

- 144-pad Dice form

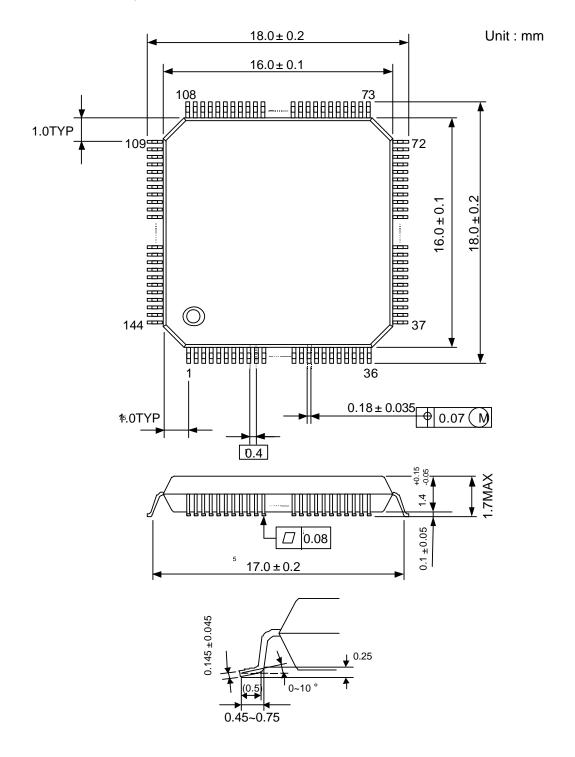

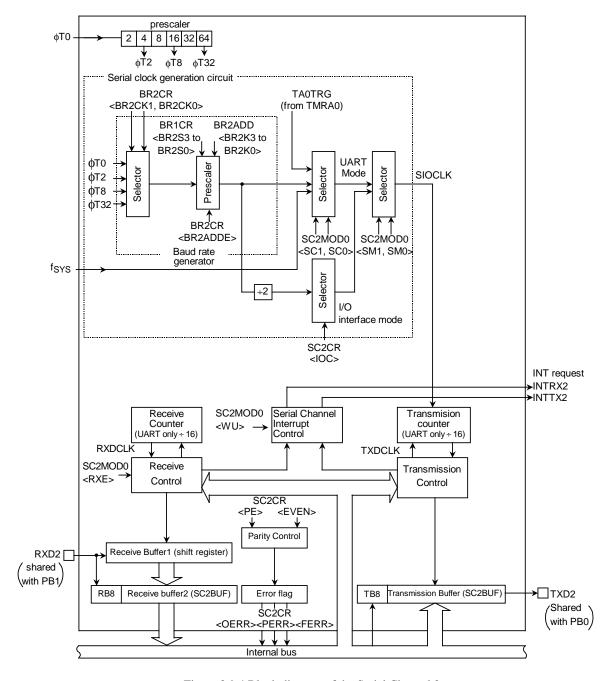

Figure 1.1 TMP91C820A Block Diagram

# 2. PIN ASSIGNMENT AND PIN FUNCTIONS

The assignment of input/output pins for the TMP91C820AF, their names and functions are as follows:

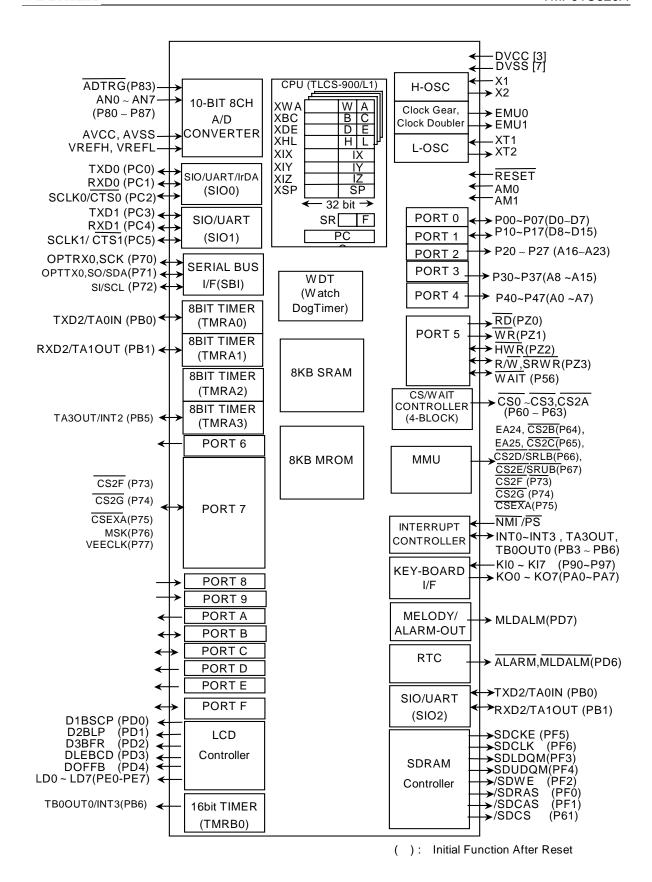

## 2.1 Pin Assignment Diagram

Figure 2.1 shows the pin assignment of the TMP91C820AF.

Figure 2.1 Pin assignment diagram (144-pin QFP)

PAD layout

| (Chi <sub>l</sub> | p size 5.75mi | m × 5.63r | nm)   |     |      |       |       |     | Unit: | J m   |       |

|-------------------|---------------|-----------|-------|-----|------|-------|-------|-----|-------|-------|-------|

| PIN               | Name          | X         | Y     | PIN | Name | X     | Y     | PIN | Name  | X     | Y     |

| No                |               | point     | point | No  |      | point | point | No  |       | point | point |

| 1                 | P81           | -2742     | 2128  | 49  | PC7  | -485  | -2682 | 97  | P37   | 2736  | 758   |

| 2                 | P82           | -2742     | 2004  | 50  | EMU0 | -370  | -2682 | 98  | VDD   | 2736  | 872   |

| 3                 | P83           | -2742     | 1888  | 51  | EMU1 | -256  | -2682 | 99  | P20   | 2736  | 986   |

| 4                 | P84           | -2742     | 1774  | 52  | PD1  | -142  | -2682 | 100 | VSS   | 2736  | 1202  |

| 5                 | P85           | -2742     | 1660  | 53  | PD2  | -28   | -2682 | 101 | P21   | 2736  | 1318  |

| 6                 | P86           | -2742     | 1546  | 54  | PD3  | 86    | -2682 | 102 | P22   | 2736  | 1432  |

| 7                 | P87           | -2742     | 1432  | 55  | PD4  | 200   | -2682 | 103 | P23   | 2736  | 1546  |

| 8                 | AVSS          | -2742     | 1318  | 56  | PE0  | 314   | -2682 | 104 | P24   | 2736  | 1660  |

| 9                 | AVDD          | -2742     | 1204  | 57  | PE1  | 428   | -2682 | 105 | P25   | 2736  | 1774  |

| 10                | P92           | -2742     | 892   | 58  | PE2  | 542   | -2682 | 106 | P26   | 2736  | 1888  |

| 11                | P93           | -2742     | 778   | 59  | PE3  | 656   | -2682 | 107 | P27   | 2736  | 2004  |

| 12                | P94           | -2742     | 664   | 60  | PE4  | 770   | -2682 | 108 | P50   | 2736  | 2128  |

| 13                | P95           | -2742     | 550   | 61  | PE5  | 884   | -2682 | 109 | P51   | 2188  | 2676  |

| 14                | P96           | -2742     | 436   | 62  | PE6  | 998   | -2682 | 110 | P52   | 2062  | 2676  |

| 15                | P97           | -2742     | 322   | 63  | PE7  | 1112  | -2682 | 111 | P53   | 1948  | 2676  |

| 16                | PA0           | -2742     | 208   | 64  | VSS  | 1246  | -2682 | 112 | P56   | 1834  | 2676  |

| 17                | PA1           | -2742     | 94    | 65  | P00  | 1378  | -2682 | 113 | P60   | 1720  | 2676  |

| 18                | PA2           | -2742     | -20   | 66  | P01  | 1492  | -2682 | 114 | P61   | 1606  | 2676  |

| 19                | PA3           | -2742     | -134  | 67  | P02  | 1606  | -2682 | 115 | P62   | 1492  | 2676  |

| 20                | PA4           | -2742     | -248  | 68  | P03  | 1720  | -2682 | 116 | VSS   | 1378  | 2676  |

| 21                | PA5           | -2742     | -362  | 69  | P04  | 1834  | -2682 | 117 | P63   | 1264  | 2676  |

| 22                | PA6           | -2742     | -476  | 70  | P05  | 1948  | -2682 | 118 | P64   | 1150  | 2676  |

| 23                | PA7           | -2742     | -590  | 71  | P06  | 2062  | -2682 | 119 | P65   | 1036  | 2676  |

| 24                | PB0           | -2742     | -704  | 72  | P07  | 2188  | -2682 | 120 | P66   | 922   | 2676  |

| 25                | PB1           | -2742     | -818  | 73  | P10  | 2736  | -2134 | 121 | P67   | 808   | 2676  |

| 26                | PB3           | -2742     | -932  | 74  | P11  | 2736  | -2010 | 122 | P70   | 694   | 2676  |

| 27                | PB4           | -2742     | -1046 | 75  | P12  | 2736  | -1894 | 123 | P71   | 580   | 2676  |

| 28                | VSS           | -2742     | -1210 | 76  | P13  | 2736  | -1780 | 124 | P72   | 382   | 2676  |

| 29                | PB5           | -2742     | -1324 | 77  | P14  | 2736  | -1666 | 125 | VDD   | 268   | 2676  |

| 30                | PB6           | -2742     | -1438 | 78  | P15  | 2736  | -1552 | 126 | P73   | 68    | 2676  |

| 31                | PC0           | -2742     | -1552 | 79  | P16  | 2736  | -1438 | 127 | P74   | -46   | 2676  |

| 32                | PC1           | -2742     | -1666 | 80  | VSS  | 2736  | -1318 | 128 | P75   | -160  | 2676  |

| 33                | PC2           | -2742     | -1780 | 81  | P17  | 2736  | -1066 | 129 | P76   | -274  | 2676  |

| 34                | PC3           | -2742     | -1894 | 82  | P40  | 2736  | -952  | 130 | P77   | -388  | 2676  |

| 35                | PC4           | -2742     | -2010 | 83  | P41  | 2736  | -838  | 131 | PD6   | -520  | 2676  |

| 36                | PC5           | -2742     | -2134 | 84  | P42  | 2736  | -724  | 132 | PD7   | -634  | 2676  |

| 37                | PF0           | -2194     | -2682 | 85  | P43  | 2736  | -610  | 133 | PF3   | -748  | 2676  |

| 38                | PF1           | -2068     | -2682 | 86  | P44  | 2736  | -496  | 134 | PF4   | -862  | 2676  |

| 39                | PF2           | -1954     | -2682 | 87  | P45  | 2736  | -382  | 135 | PF5   | -976  | 2676  |

| 40                | PD0           | -1840     | -2682 | 88  | P46  | 2736  | -268  | 136 | VSS   | -1090 | 2676  |

| 41                | AM0           | -1726     | -2682 | 89  | P47  | 2736  | -154  | 137 | PF6   | -1204 | 2676  |

| 42                | VDD           | -1612     | -2682 | 90  | P30  | 2736  | -40   | 138 | PF7   | -1318 | 2676  |

| 43                | X2            | -1410     | -2682 | 91  | P31  | 2736  | 74    | 139 | P90   | -1432 | 2676  |

| 44                | VSS           | -1244     | -2682 | 92  | P32  | 2736  | 188   | 140 | P91   | -1546 | 2676  |

| 45                | X1            | -1079     | -2682 | 93  | P33  | 2736  | 302   | 141 | NMIV  | -1660 | 2676  |

| 46                | AM1           | -963      | -2682 | 94  | P34  | 2736  | 416   | 142 | VREFL | -1954 | 2676  |

| 47                | RESETV        | -849      | -2682 | 95  | P35  | 2736  | 530   | 143 | VREFH | -2068 | 2676  |

| 48                | PC6           | -734      | -2682 | 96  | P36  | 2736  | 644   | 144 | P80   | -2194 | 2676  |

| 70                | 100           | -134      | -2002 | 70  | 1 30 | 2130  | 0-1-1 | 144 | ΓOU   | -2194 | 2070  |

# 2.2 Pin Names and Functions

The names of the input/output pins and their functions are described below.

Table 2.2 Pin names and functions.

| Pin Name         | Number<br>of Pins | I/O    | Functions                                                                         |

|------------------|-------------------|--------|-----------------------------------------------------------------------------------|

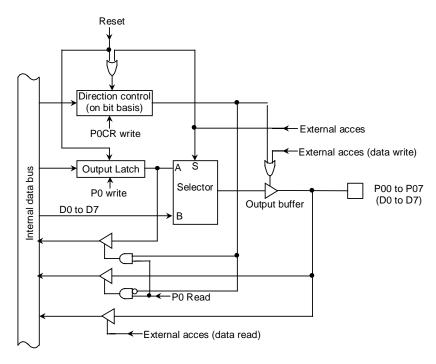

| P00 to P07       | 8                 | I/O    | Port 0: I/O port that allows I/O to be selected at the bit level                  |

| D0 to D7         |                   | I/O    | Data (lower): bits 0 to 7 of data bus                                             |

| P10 to P17       | 8                 | I/O    | Port 1: I/O port that allows I/O to be selected at the bit level                  |

|                  |                   |        | (When used to the external 8bit bus)                                              |

| D8 to D15        |                   | I/O    | Data (upper): bits 8 to15 of data bus                                             |

| P20 to P27       | 8                 | Output | Port 2: I/O port                                                                  |

| A16 to A23       |                   | Output | Address: bits 16 to 23 of address bus                                             |

| P30 to P37       | 8                 | Output | Port 3: I/O port                                                                  |

| A8 to A15        |                   | Output | Address: bits 8 to 15 of address bus                                              |

| P40 o P47        | 8                 | Output | Port 4: I/O port                                                                  |

| A0 to A7         |                   | Output | Address: bits 0 to 7 of address bus                                               |

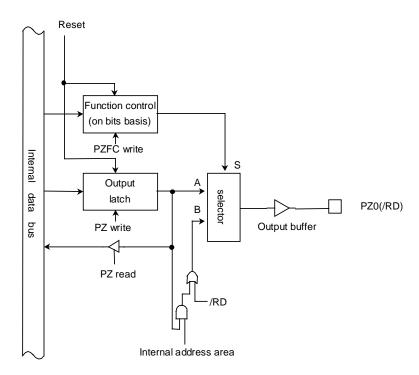

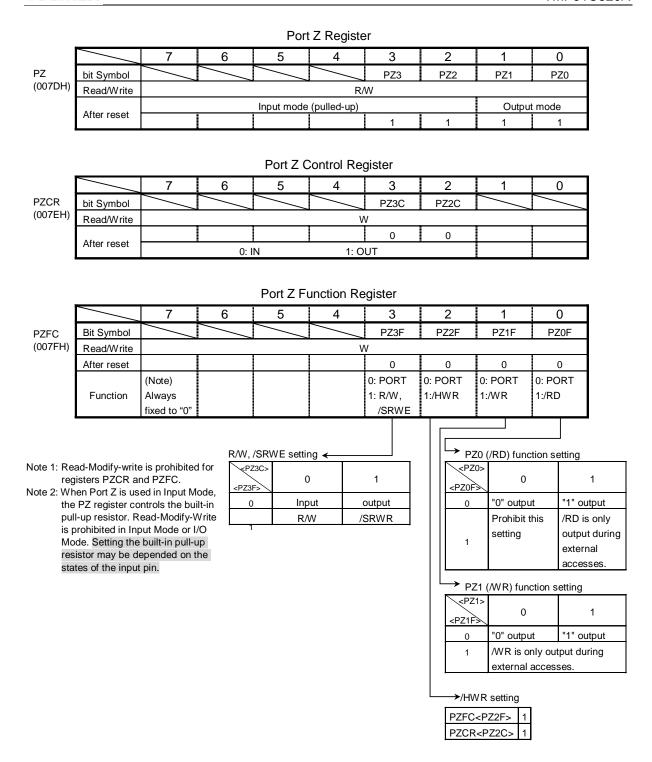

| PZ0              | 1                 | Output | Port Z0:Output port                                                               |

| /RD              |                   | Output | Read: strobe signal for reading external memory                                   |

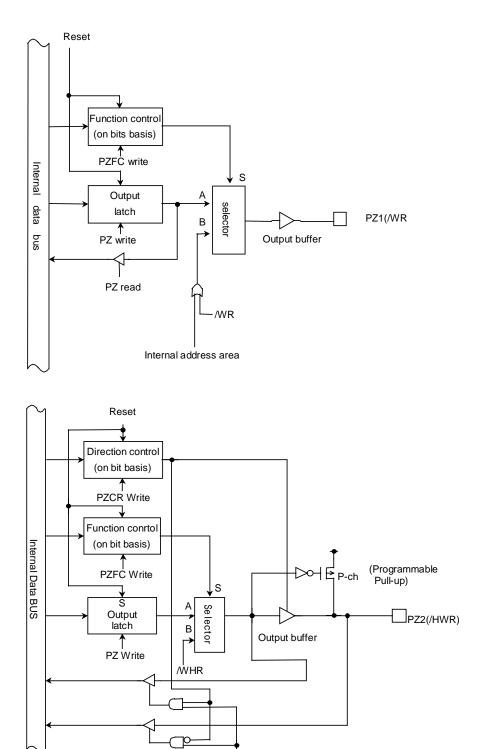

| PZ1              | 1                 | Output | Port Z1:Output port                                                               |

| /WR              |                   | Output | Write: strobe signal for writing data to pins D0 to D7                            |

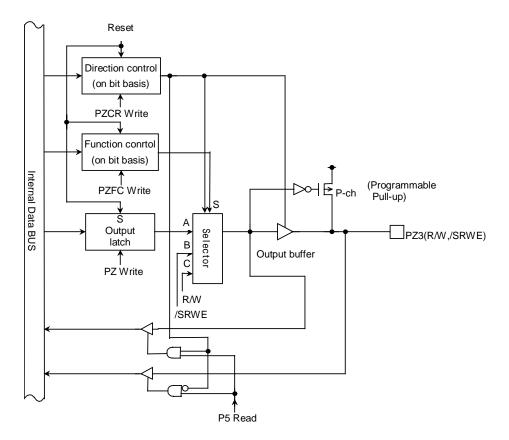

| PZ2              | 1                 | I/O    | Port Z2: I/O port (with pull-up resistor)                                         |

| /HWR             |                   | Output | High Write: strobe signal for writing data to pins D8 to D15                      |

| PZ3              | 1                 | I/O    | Port Z3: I/O port (with pull-up resistor)                                         |

| $R/\overline{W}$ |                   | Output | Read/Write: 1 represents Read or Dummy cycle; 0 represents write cycle.           |

| /SRWR            |                   | Output | Write for SRAM: strobe signal for writing data.                                   |

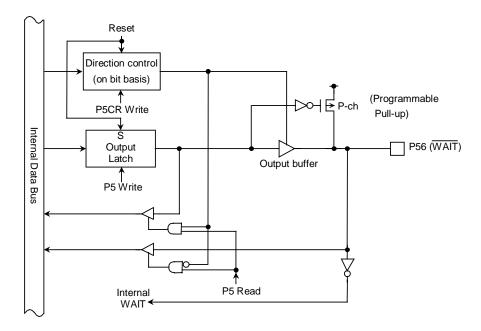

| P56              | 1                 | I/O    | Port 56: I/O port (with pull-up resistor)                                         |

| /WAIT            |                   | Input  | Wait: pin used to request CPU bus wait                                            |

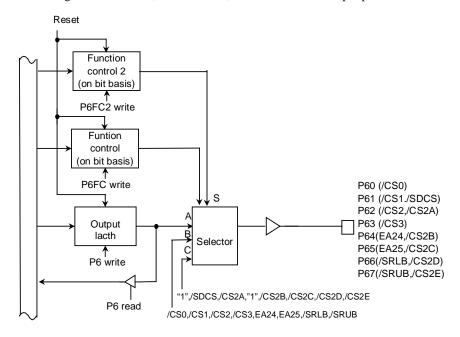

| P60              | 1                 | Output | Port 60:Output port                                                               |

| /CS0             |                   | Output | Chip select 0: Outputs "0" when address is within specified address area.         |

| P61              | 1                 | Output | Port 61:Output port                                                               |

| /CS1             |                   | Output | Chip Select 1: outputs "0" when address is within specified address area          |

| /SDCS            |                   | Output | Chip Select for SDRAM: outputs "0" when address is within SDRAM address area      |

| P62              | 1                 | Output | Port 62: Output port                                                              |

| /CS2             | 1                 | Output | Chip Select 2: outputs "0" when address is within specified address area          |

| /CS2A            |                   | Output | Expand Chip Select: 2A: outputs 0 when address is within specified address area   |

| P63              | 1                 | Output | Port 63:Output port                                                               |

| /CS3             | 1                 | Output | Chip Select 3: outputs "0" when address is within specified address area          |

| P64              |                   | Output | Port 64: Output port                                                              |

| EA24             | 1                 | Output | Chip Select 24: outputs "0" when address is within specified address area         |

| /CS2B            |                   | Output | Expand Chip Select: 2B: outputs "0" when address is within specified address area |

| P65              |                   | Output | Port 65: Output port                                                              |

| EA25             | 1                 | Output | Chip Select 25: outputs "0" when address is within specified address area         |

| /CS2C            |                   | Output | Expand Chip Select: 2C: outputs "0" when address is within specified address area |

| P66              |                   | Output | Port 66: Output port                                                              |

| /CS2D            | 1                 | Output | Expand Chip Select: 2D: outputs "0" when address is within specified address area |

| /SRLB            |                   | Output | Lower Byte enable for SRAM: outputs "0" when lower-data is enable.                |

| P67              |                   | Output | Port 67: Output port                                                              |

| /CS2E            | 1                 | Output | Expand Chip Select: 2E: outputs "0" when address is within specified address area |

| /SRUB            |                   | Output | Upper Byte enable for SRAM: outputs "0" when upper-data is enable.                |

| Pin Name   | Number of Pins | I/O    | Functions                                                                                |

|------------|----------------|--------|------------------------------------------------------------------------------------------|

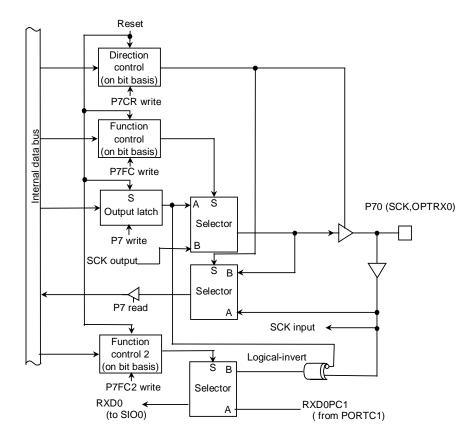

| P70        |                | I/O    | Port 70: I/O port                                                                        |

| SCK        | 1              | I/O    | Serial bus interface clock I/O data at SIO mode                                          |

| OPTRX0     |                | Input  | Serial-0 recive data                                                                     |

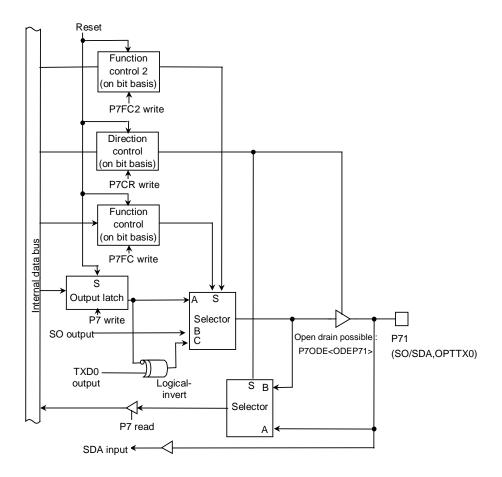

| P71        | 1              | I/O    | Port 71: I/O port                                                                        |

| S0         |                | Output | Serial bus interface send data at SIO mode                                               |

| SDA        |                | I/O    | Serial bus interface send/recive data at I2C mode                                        |

|            |                |        | Open drain output mode by programmable                                                   |

| OPTRX0     |                | Output | Serial-0 send data                                                                       |

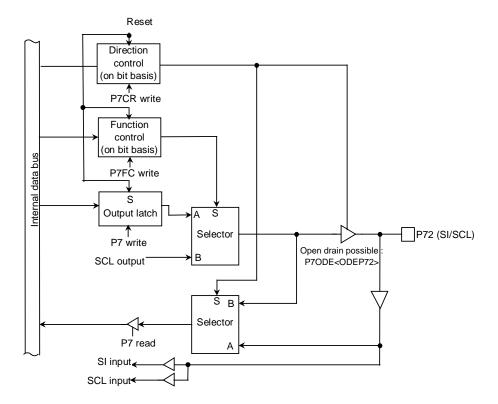

| P72        | 1              | I/O    | Port 72: I/O port                                                                        |

| SI         |                | Output | Serial bus interface recive data at SIO mode                                             |

| SCL        |                | Output | Serial bus interface clock I/O data at I2C mode                                          |

|            |                |        | Open drain output mode by programmable                                                   |

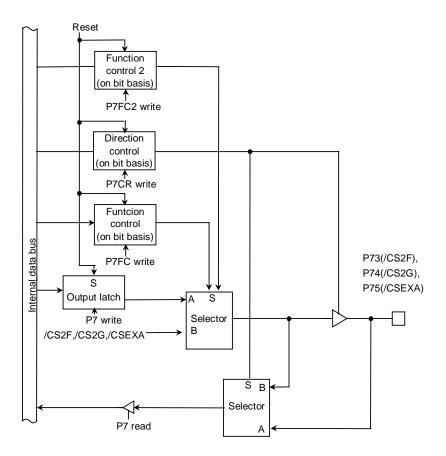

| P73        | 1              | I/O    | Port 73: I/O port                                                                        |

| /CS2F      |                | Output | Expond Chip Select 2F: outputs outputs "0" when address is within specified address area |

| P74        | 1              | I/O    | Port 74: I/O port                                                                        |

| /CS2G      |                | Output | Expond Chip Select 2G: outputs outputs "0" when address is within specified address area |

| P75        | 1              | I/O    | Port 75: I/O port                                                                        |

| /CSEXA     | 1              | Output | Expand Chip Select EXA: outputs outputs "0" when address is within specified address     |

| CSEAA      |                | Output | area                                                                                     |

|            |                |        |                                                                                          |

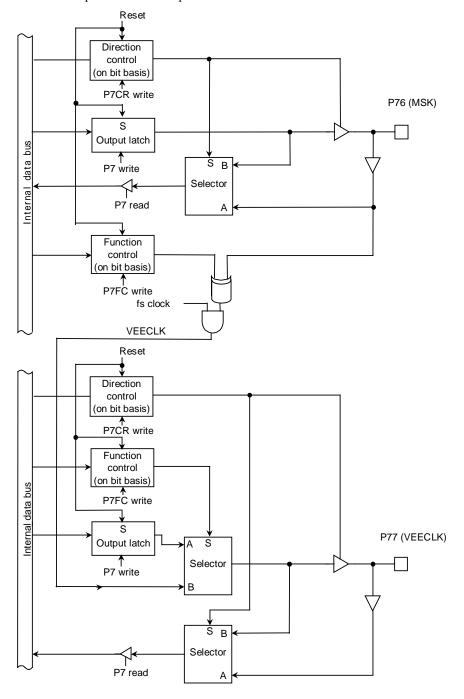

| P76        | 1              | I/O    | Port 76: I/O port                                                                        |

| MSK        |                | Input  | Mask: Use for disable to output VEECLK for LCD-driver                                    |

| P77        | 1              | I/O    | Port 77: I/O port                                                                        |

| VEECLK     |                | Output | Output 32.768KHz clock to LCD-driver. (can be disabled by MSK-pin)                       |

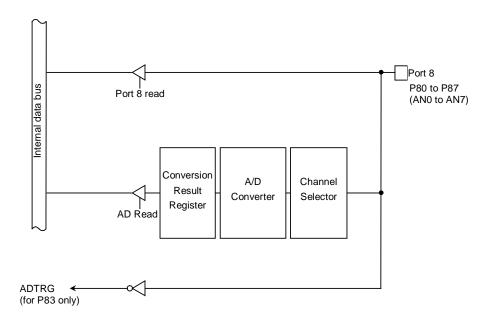

| P80 to P87 | 8              | Input  | Port 80 to 87 port: Pin used to input ports                                              |

| AN0 to AN7 |                | Input  | Analog input 0 to 7: Pin used to Input to A/D conveter                                   |

| ADTRG      |                | Input  | A/D trigger: Signal used to request A/D start (with used to P83)                         |

| P90 to P97 | 8              | Input  | Port: 90 to 97 port: Pin used to input ports                                             |

| KI0 to KI7 |                | Input  | Key input 0 to 7: Pin used of Key on wake-up 0 to 7                                      |

|            |                |        | (schmitt input, with pull-up register)                                                   |

| PA0 to PA7 | 8              | Output | Port: A0 to A7 port: Pin used to output ports                                            |

| KO0 to KO7 |                | Output | Key output 0 to 7: Pin used of Key-scan strobe 0 to 7                                    |

| PB0        | 1              | I/O    | Port B0: I/O port                                                                        |

| TA0IN      |                | Input  | 8bit timer 0 input: Timer 0 input                                                        |

| TXD2       |                | Output | Serial 2 send data: Open drain output pin by programmable                                |

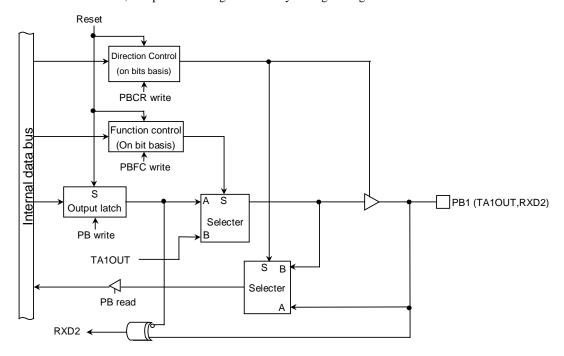

| PB1        | 1              | I/O    | Port B1: I/O port                                                                        |

| TA1OUT     |                | Output | 8bit timer 1 output: Timer 1 output                                                      |

| RXD2       |                | Input  | Serial 2 receive data                                                                    |

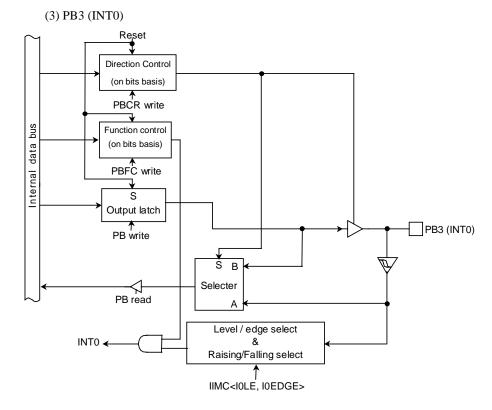

| PB3        | 1              | I/O    | Port B3: I/O port                                                                        |

| INT0       |                | input  | Interrupt request pin0: Interrupt request pin with programmable level / rising /         |

|            |                |        | Falling edge                                                                             |

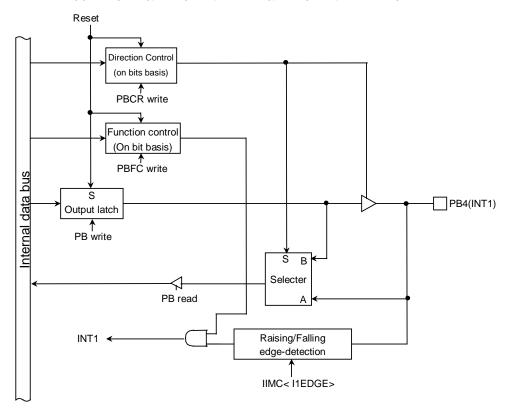

| PB4        | 1              | I/O    | Port B4: I/O port                                                                        |

| INT1       |                | input  | Interrupt request pin1: Interrupt request pin with programmable rising /                 |

|            |                |        | Falling edge                                                                             |

| Pin Name      | Number of Pins | I/O              | Functions                                                                                            |

|---------------|----------------|------------------|------------------------------------------------------------------------------------------------------|

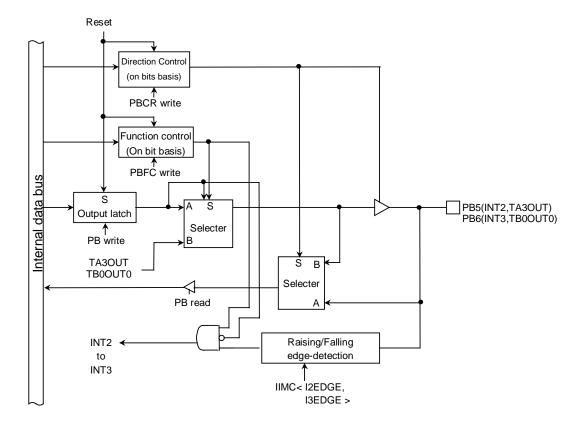

| PB5           | 1              | I/O              | Port B5: I/O port                                                                                    |

| INT2          |                | Input            | Interrupt request pin2 : Interrupt request pin with programmable rising /falling edge                |

|               |                |                  | 8bit timer 3 output: Timer 3 output                                                                  |

| TA3OUT        |                | Output           | 8bit timer 3 output: Timer 2 output or Timer 3 output                                                |

| PB6           | 1              | I/O              | Port B6 : I/O port                                                                                   |

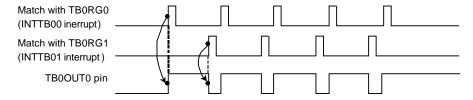

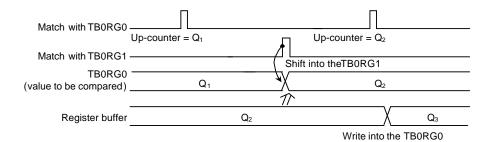

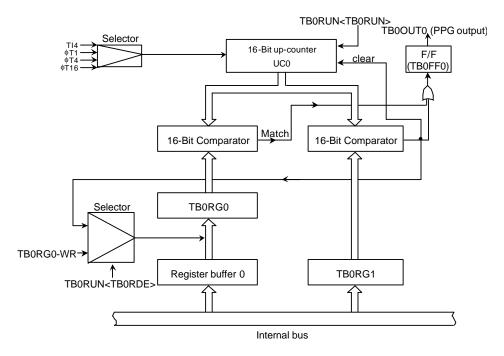

| INT3          |                | Input            | Interrupt request pin3: Interrupt request pin with programmable rising /falling edge Timer B0 output |

| TB0OUT0       |                | Outout           | 8bit timer 0 output: Timer 0 output or Timer 1 output                                                |

| PC0           | 1              | I/O              | Port C0: I/O port                                                                                    |

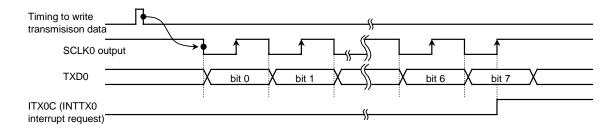

| TXD0          |                | Output           | Serial 0 send data: Open drain output pin by programmable                                            |

| PC1           | 1              | I/O              | Port C1: I/O port                                                                                    |

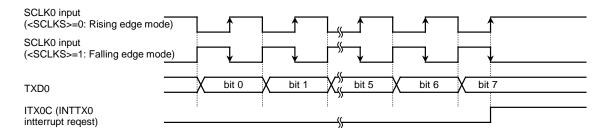

| RXD0          |                | Input            | Serial 0 receive data                                                                                |

| PC2           | 1              | I/O              | Port C2: I/O port                                                                                    |

| SCLK0         |                | I/O              | Serial 0 clock I/O                                                                                   |

| CTS0          |                | Input            | Serial 0 data send enable (Clear to Send)                                                            |

| PC3           | 1              | I/O              | Port C3: I/O port                                                                                    |

| TXD1          |                | Output           | Serial 1 send data: Open drain output pin by programmable                                            |

| PC4           | 1              | I/O              | Port C4: I/O port                                                                                    |

| RXD1          |                | Input            | Serial 1 receive data                                                                                |

| PC5           | 1              | I/O              | Port C5: I/O port                                                                                    |

| SCLK1         |                | I/O              | Serial 1 clock I/O                                                                                   |

| CTS1          |                | Input            | Serial 1 data send enable (Clear to Send)                                                            |

| PD0           | 1              | Output           | Port D0: Output port                                                                                 |

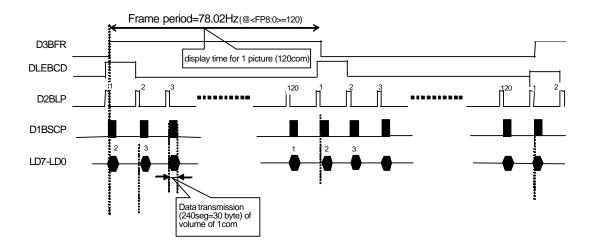

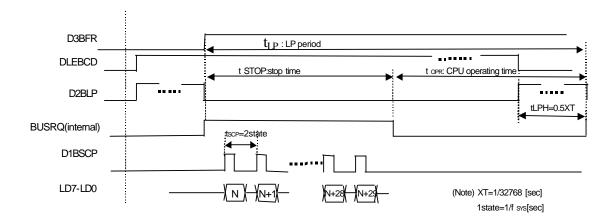

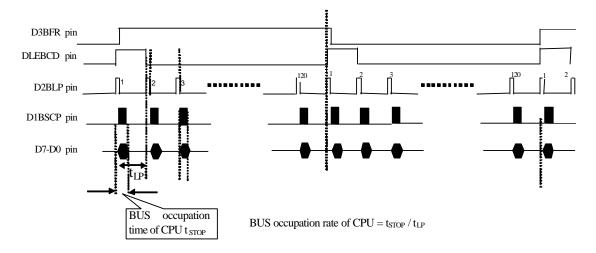

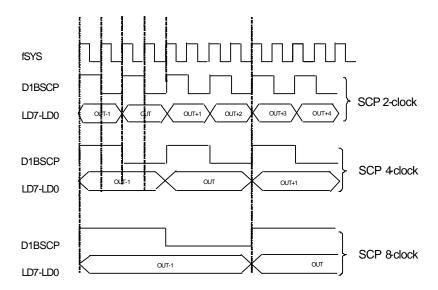

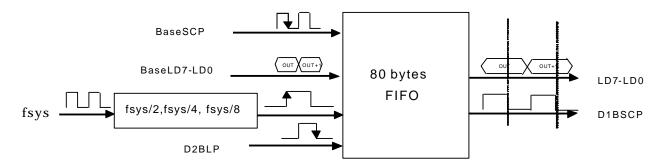

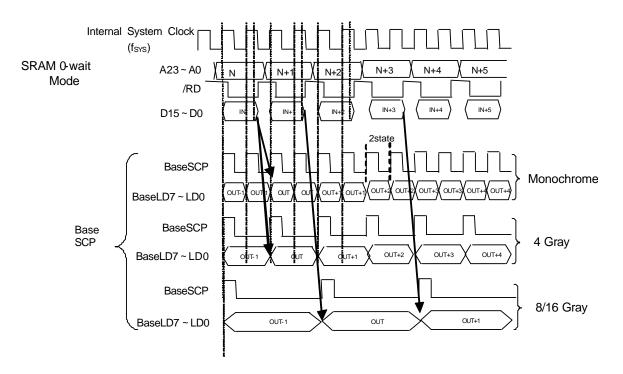

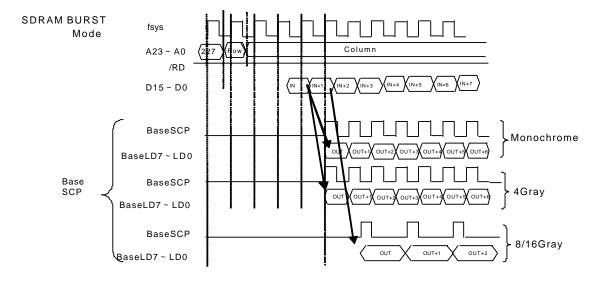

| D1BSCP        |                | Output           | LCD driver output pin                                                                                |

| PD1           | 1              | Output           | Port D1: Output port                                                                                 |

| D2BLP         |                | Output           | LCD driver output pin                                                                                |

| PD2           | 1              | Output           | Port D2: Output port                                                                                 |

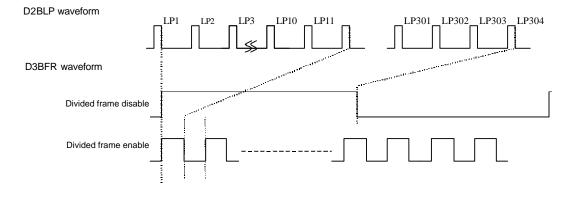

| D3BFR         |                | Output           | LCD driver output pin                                                                                |

| PD3           | 1              | Output           | Port D3: Output port                                                                                 |

| DLEBCD        | 1              | Output           | LCD driver output pin                                                                                |

| PD4           | 1              | Output           | Port D4: Output port                                                                                 |

| DOFFB         | 1              | Output           | LCD driver output pin                                                                                |

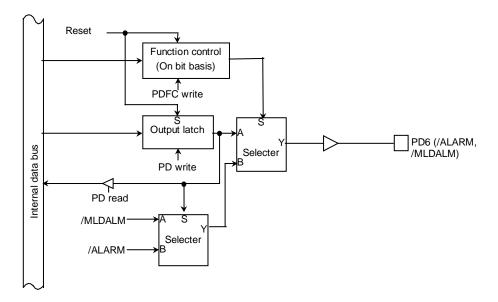

| PD6<br>/ALARM | 1              | Output           | Port D6: Output port RTC alarm output pin                                                            |

| /MLDALM       |                | Output<br>Output | Melody / Alarm output pin (inverted)                                                                 |

|               |                |                  |                                                                                                      |

| PD7           | 1              | Output           | Port D7: Output port                                                                                 |

| MLDALM        |                | Output           | Melody / Alarm output pin                                                                            |

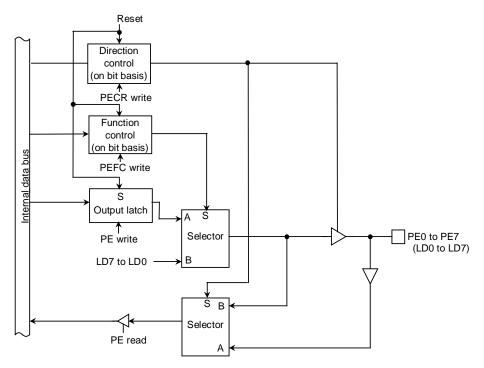

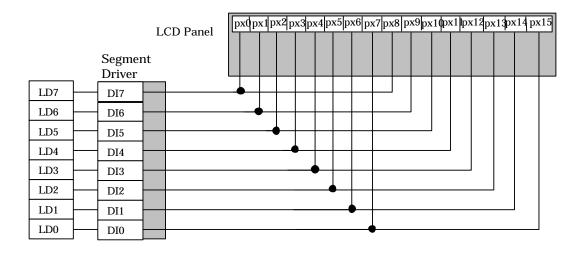

| PE0 to PE7    | 8              | I/O              | Port E0 to E7: I/O port                                                                              |

| LD0 to LD7    |                | Output           | Data Bus for LCD-driver                                                                              |

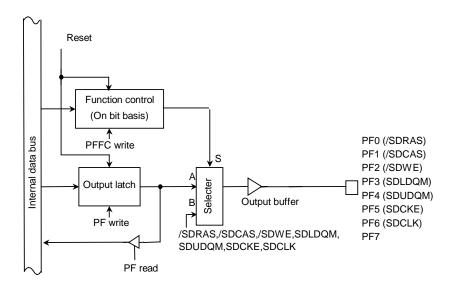

| PF0           | 1              | I/O              | Port F0: Output port                                                                                 |

| /SDRAS        |                | Output           | Row Address Storobe for SDRAM: outputs "0" when address is within SDRAM address area                 |

| PF1           | 1              | I/O              | Port F1: Output port                                                                                 |

| /SDCAS        |                | Output           | Column Address Storobe for SDRAM: outputs "0" when address is within SDRAM                           |

|               |                |                  | address area                                                                                         |

| Pin Name | Number of Pins | I/O    | Functions                                                                        |

|----------|----------------|--------|----------------------------------------------------------------------------------|

| PF2      | 1              | Output | Port F2: Output port                                                             |

| /SDWE    |                | Output | Write Enable for SDRAM                                                           |

| PF3      | 1              | Output | Port F3: Output port                                                             |

| SDLDQM   |                | Output | Lower Data enable for SDRAM                                                      |

| PF4      | 1              | Output | Port F4: Output port                                                             |

| SDUDQM   |                | Output | Upper Data enable for SDRAM                                                      |

| PF5      | 1              | Output | Port F5: Output port                                                             |

| SDCKE    |                | Output | Clock Enable for SDRAM                                                           |

| PF6      | 1              | Output | Port F6: Output port                                                             |

| SDCLK    |                | Output | Clock for SDRAM                                                                  |

| PF7      | 1              | Output | Port F7: Output port                                                             |

| /PS      | 1              | Input  | Power Save mode setting terminal                                                 |

| /NMI     |                | Input  | Non-Maskable Interrupt Request : interrupt request pin with programmable falling |

|          |                |        | edge level or with both edge levels programmable                                 |

| AM0 to 1 | 2              | Input  | Operation mode:                                                                  |

|          |                |        | Fixed to AM1="1",AM0="1" when using internal-ROM.                                |

|          |                |        | Fixed to AM1="0",AM0="1" when using external-ROM                                 |

|          |                |        | by 16-bit external bus.                                                          |

|          |                |        | Fixed to AM1="0",AM0="0" when using external-ROM                                 |

|          |                |        | by 8-bit external bus.                                                           |

| EMU0     | 1              | Output | Open pin                                                                         |

| EMU1     | 1              | Output | Open pin                                                                         |

| RESET    | 1              | Input  | Reset: initializes TMP91C820AF. (With pull-up resistor)                          |

| VREFH    | 1              | Input  | Pin for reference voltage input to AD converter (H)                              |

| VREFL    | 1              | Input  | Pin for reference voltage input to AD converter (L)                              |

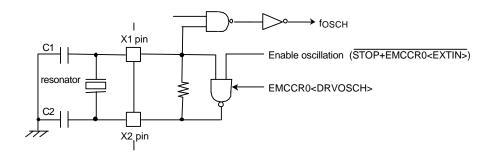

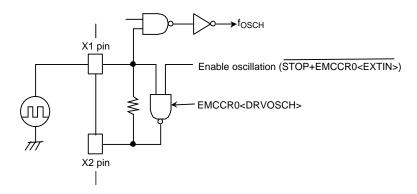

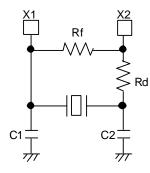

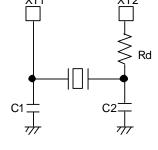

| X1/X2    | 2              | I/O    | High-frequency oscillator connection pins                                        |

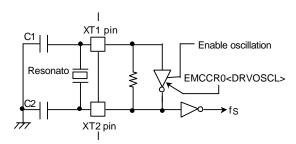

| XT1/XT2  | 2              | I/O    | Low-frequency oscillator connection pins                                         |

| AVCC     | 1              |        | Power supply pin for AD converter                                                |

| AVSS     | 1              |        | GND pin for AD converter (0 V)                                                   |

| DVCC     | 3              |        | Power supply pins (All Vcc pins should be connecyed with the power Supply pin).  |

| DVSS     | 7              |        | GND pins (All pins shoold be connected with GND(0V).                             |

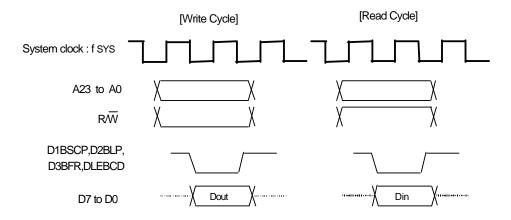

# 3. OPERATION

This following describes block by block the functions and operation of the TMP91C820A.

Notes and restrictions for eatch book are outlined in "6, Precautions and Restrictions " at the end of this manual.

#### 3.1 CPU

The TMP91C820A incorporates a high-performance 16-bit CPU (the 900/L1 CPU). For CPU operation, see the "TLCS-900/L1 CPU".

The following describe the unique function of the CPU used in the TMP91C820A; these functions are not covered in the TLCS-900/L1 CPU section.

#### 3.1.1 Reset

When resetting the TMP91C820A microcontroller, ensure that the power supply voltage is within the operating voltage range, and that the internal high-frequency oscillator has stabilized. Then hold the /RESET input to Low level for at least 10 system clocks (ten states: 80 µs at 4 MHz).

When the reset is accept, the CPU:

Sets as follows the program counter (PC) in accordance with the reset vector stored at address FFFF00H to FFFF02H:

```

PC<7 to 0> ← value at FFFF00H address

PC<15 to 8> ← value at FFFF01H address

PC<23 to 16>←value at FFFF02H address

```

- Sets the stack pointer (XSP) to 100H.

- Sets bits <IFF2:0> of the status register (SR) to 111 (sets the interrupt level mark register to level 7).

- Sets the <MAX> bit of the status register to 1 (MAX mode).

(Note: As this product does not support MIN mode, do not write a 0 to the <MAX>)

- Clears bits  $\langle RFP2:0 \rangle$  of the status register to 000 (sets the register bank to 0).

When reset is released, the CPU starts executing instructions in accordance with the program counter settings. CPU internal registers not mentioned above do not change when the reset is released.

When the reset is accepted, the CPU sets internal I/O, ports, and other pins as follows.

- Initializes the internal I/O registers.

- Sets the port pins, including the pins that also act as internal I/O, to general-purpose input or output port mode.

(Note1) The CPU internal register(except to PC,SR,XSP) and internal RAM data do not change by resetting.

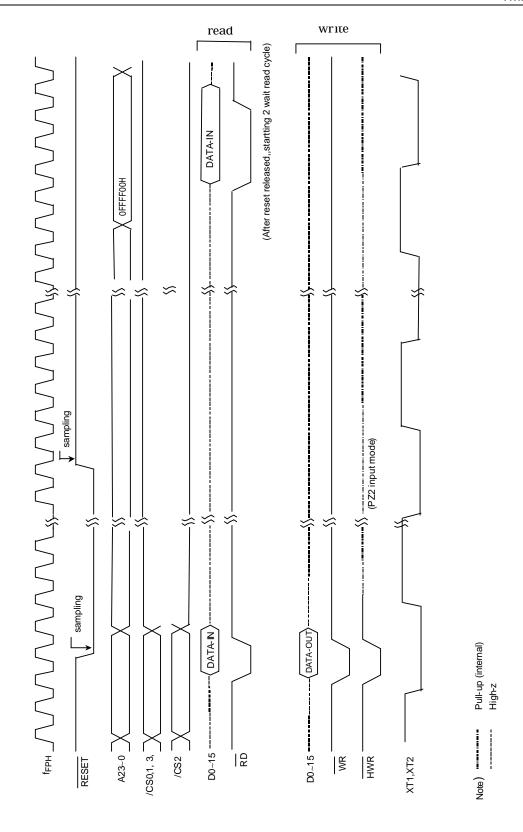

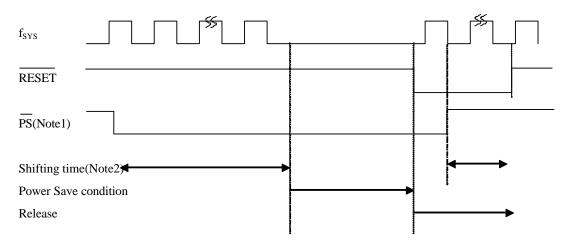

Figure 3.1.1 is a reset timing of the TMP91C820A.

Figure 3.1.1 TMP91C820A Reset Timing Example (the case of using external-ROM)

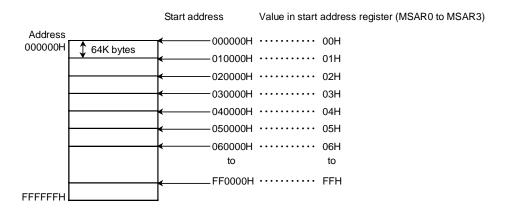

# 3.2 Memory Map

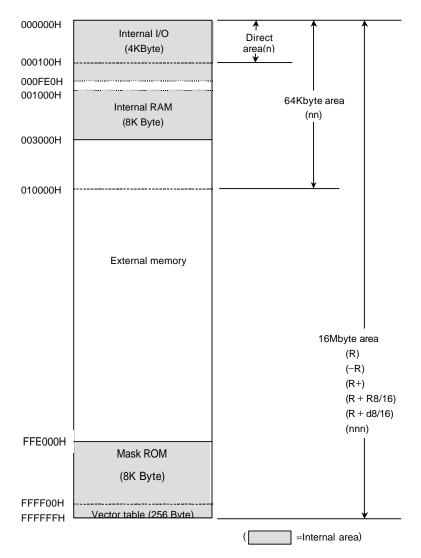

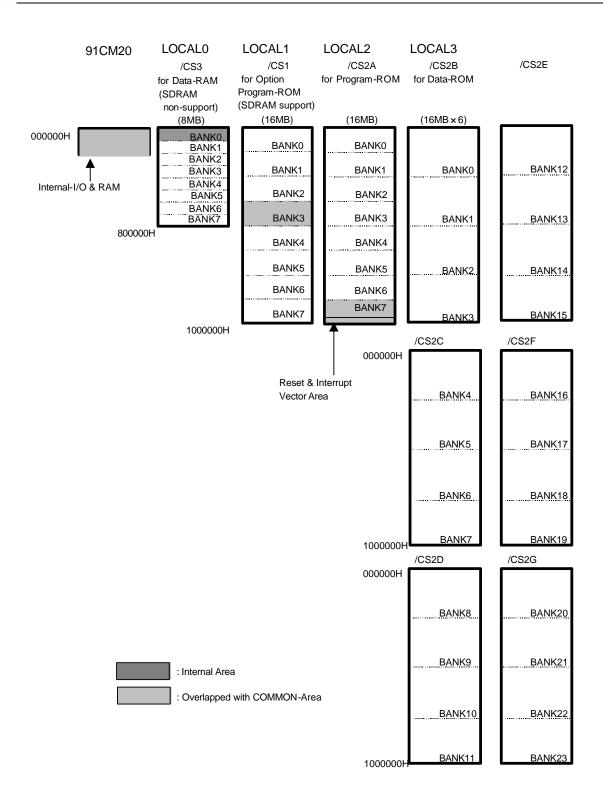

Figure 3.2.1 is a memory map of the TMP91C820A.

Figure 3.2.1 Memory Map

(note): Address 000FE0H – 000FEFH is assigned for the external memory area of Built-in RAM type LCD driver.

# 3.3 Triple Clock Function and Standby Function

TMP91C820A contains (1) a clock gear, (2) clock doubler (DFM), (3) standby controller and (4) noise-reducing circuit. It is used for low-power, low-noise systems.

This chapter is organized as follows:

- 3.3.1 Block diagram of system clock

- 3.3.2 SFRs

- 3.3.3 System clock controller

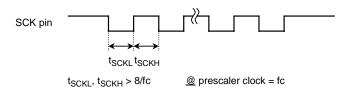

- 3.3.4 Prescaler clock controller

- 3.3.5 Clock doubler (DFM)

- 3.3.6 Noise-reducing circuit

- 3.3.7 Standby controller

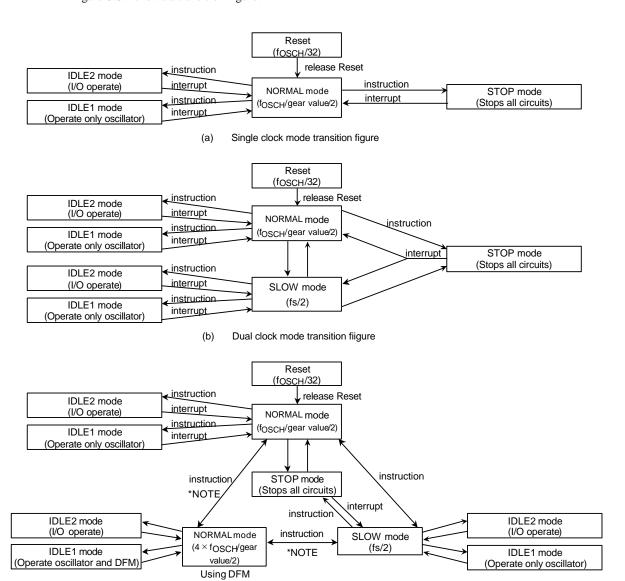

The clock operating modes are as follows: (a) Single Clock Mode (X1, X2 pins only), (b) Dual Clock Mode (X1, X2, XT1 and XT2 pins) and (c) Triple Clock Mode (the X1, X2, XT1 and XT2 pins and DFM).

Figure 3.3.1 shows a transition figure.

(c) Triple clock mode trasision Figure

#### \*NOTE)

- It's prohibited to control DFM in SLOW mode when shifting from SLOW mode to NORMAL mode with use of DFM. ( DFM Start up/Stop/Change Write to DFMCR0<ACT1:0> resister )

- If you shift from NORMAL mode with use of DFM to NORMAL mode, the instruction should be separated into two procedures as below. Change CPU clock->Stop DFM circuit

- It's prohibited to shift from NORMAL mode with use of DFM to STOP mode directly. You should set NORMAL

mode once, and then shift to STOP mode.(You should stop high frequency oscillator after you stop DFM.)

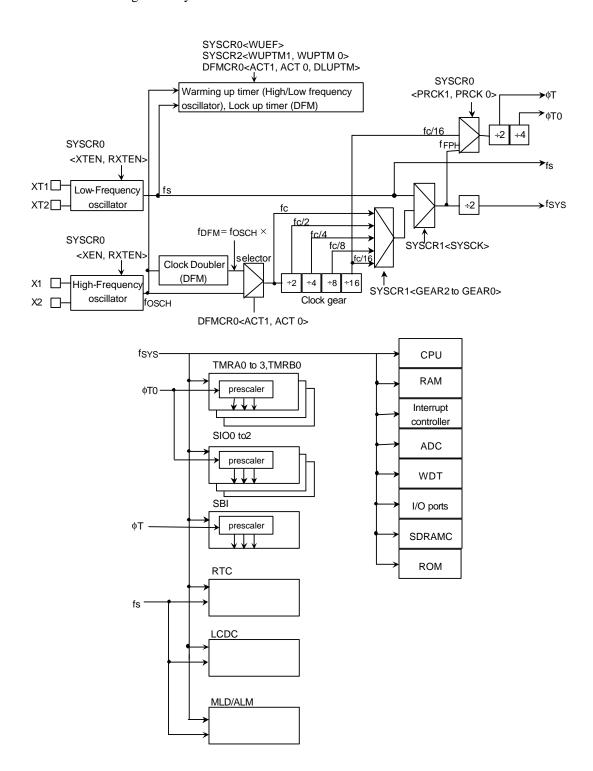

Figure 3.3.1 System clock block diagram

The clock frequency input from the X1 and X2 pins is called fc and the clock frequency input from the XT1 and XT2 pins is called fs. The clock frequency selected by SYSCR1<SYSCK> is called the system clock  $f_{FPH}$ . The system clock  $f_{SYS}$  is defined as the divided clock of  $f_{FPH}$ , and one cycle of  $f_{SYS}$  is defined to as one state.

# 3.3.1 Block diagram of system clock

Figure 3.3.2 Block Diagram of System clock

# 3.3.2 SFR

|                   |             | 7                                                                  | 6                                                                            | 5                                                                                                       | 4                                                                                                  | 3                                                                        | 2                                                                                                     | 1                                                                            | 0                                                                          |  |  |

|-------------------|-------------|--------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|--|

| SYSCR0            | bit Symbol  | XEN                                                                | XTEN                                                                         | RXEN                                                                                                    | RXTEN                                                                                              | RSYSCK                                                                   | WUEF                                                                                                  | PRCK1                                                                        | PRCK0                                                                      |  |  |

| (00E0H)           | Read/Write  | RW                                                                 |                                                                              |                                                                                                         |                                                                                                    |                                                                          |                                                                                                       |                                                                              |                                                                            |  |  |

|                   | After reset | 1                                                                  | 1                                                                            | 1                                                                                                       | 0                                                                                                  | 0                                                                        | 0                                                                                                     | 0                                                                            | 0                                                                          |  |  |

|                   | Function    | High-frequen<br>cy oscillator<br>(fc)<br>0: Stop<br>1: Oscillation | Low-frequen<br>cy oscillator<br>(fs)<br>0: Stop<br>1: Oscillation<br>(Note2) | High-frequen<br>cy oscillator<br>(fc) after<br>release of<br>Stop Mode<br>0: Stop<br>1: Oscillation     | Low-frequen<br>cy oscillator<br>(fs) after<br>release of<br>Stop Mode<br>0: Stop<br>1: Oscillation | Selects clock<br>after release<br>of Stop<br>Mode<br>0: fc<br>1: fs      | Warm-up Timer 0: Write Don't care 1: Write start timer 0: Read end warm-up 1: Read do not end warm-up | Select presca<br>00: fFPH (Note<br>01: reserved<br>10: fc/16<br>11: reserved |                                                                            |  |  |

| CVCCD4            |             | 7                                                                  | 6                                                                            | 5                                                                                                       | 4                                                                                                  | 3                                                                        | 2                                                                                                     | 1                                                                            | 0                                                                          |  |  |

| SYSCR1<br>(00E1H) | bit Symbol  |                                                                    |                                                                              |                                                                                                         |                                                                                                    | SYSCK                                                                    | GEAR2                                                                                                 | GEAR1                                                                        | GEAR0                                                                      |  |  |

| (002)             | Read/Write  |                                                                    |                                                                              |                                                                                                         |                                                                                                    |                                                                          | R/                                                                                                    | W                                                                            |                                                                            |  |  |

|                   | After reset |                                                                    |                                                                              |                                                                                                         |                                                                                                    | 0                                                                        | 1                                                                                                     | 0                                                                            | 0                                                                          |  |  |

|                   | Function    |                                                                    |                                                                              |                                                                                                         |                                                                                                    | Select<br>system clock<br>0: fc<br>1: fs                                 |                                                                                                       | d)                                                                           | quency (fc)                                                                |  |  |

| SYSCR2            |             | 7                                                                  |                                                                              | 5                                                                                                       | 4                                                                                                  | 3                                                                        | 2                                                                                                     | 1                                                                            | 0                                                                          |  |  |

| (00E2H)           | bit Symbol  | PSENV                                                              |                                                                              | WUPTM1                                                                                                  | WUPTM0                                                                                             | HALTM1                                                                   | HALTM0                                                                                                | SELDRV                                                                       | DRVE                                                                       |  |  |

| ( /               | ReadWrite   | RW                                                                 |                                                                              | R/W                                                                                                     | RW                                                                                                 | R/W                                                                      | R/W                                                                                                   | R/W                                                                          | R/W                                                                        |  |  |

|                   | After reset | 0                                                                  |                                                                              | 1                                                                                                       | 0                                                                                                  | 1                                                                        | 1                                                                                                     | 0                                                                            | 0                                                                          |  |  |

|                   | Function    | 1:Disable<br>0:power<br>save<br>mode<br>enable<br>(Note3)          |                                                                              | Warm-Up Tim<br>00: reserved<br>01: 2 <sup>8</sup> /inputted<br>10:2 <sup>14</sup><br>11:2 <sup>16</sup> |                                                                                                    | HALT mode<br>00: reserved<br>01: STOP mo<br>10: IDLE1 mo<br>11: IDLE2 mo | de                                                                                                    | <drve><br/>mode<br/>select<br/>1: STOP<br/>0: IDLE1</drve>                   | Pin state control in STOP mode 0: I/O off 1: Remains the state before HALT |  |  |

(note1): By reset, low-frequency oscilltor is enabled.

(note2): It's prohibit to use to fc/16 prescaler clock when SBI block use.(I2C bus & clock synchronous)

(note3): When you use NMI/PS p in as NMI function, set <PSETV> to "1".

Figure 3.3.3 SFR for system clock

| Symbol | Name       | Address |    | 7                                               | :    | 6                         | 5                 | 4             | 3       | 2 | 1        | 0 |

|--------|------------|---------|----|-------------------------------------------------|------|---------------------------|-------------------|---------------|---------|---|----------|---|

|        |            |         |    | ACT1                                            |      | ACT0                      | DLUPFG            | DLUPTM        |         |   |          |   |

|        |            |         |    | R/W                                             |      | R/W                       | R                 | R/W           |         |   | i<br>!   |   |

|        | DFM        |         |    | 0                                               |      | 0                         | 0                 | 0             |         |   | <u> </u> |   |

| DFMCR0 | Control    | E8H     |    | DFM                                             | LU   | P select f <sub>FPH</sub> | Lock up           | Lock-up Time  |         |   |          |   |

| Dimeno | Register 0 |         | 00 | STOP                                            | STOF | fosch                     |                   | 0: 212 f OSCH |         |   | į        |   |

|        |            |         | 01 | RUN                                             | RUN  | $f_{OSCH}$                | 0: <b>end</b>     | 1: 210 fosch  |         |   | i        |   |

|        |            |         | 10 | RUN                                             | STOF | f <sub>DFM</sub>          | 1: <b>not end</b> | · .           |         | ! | !<br>!   |   |

|        |            |         | 11 | RUN                                             | STOF | fosch                     | !                 |               |         |   | !<br>•   |   |

|        | DFM        |         |    |                                                 |      |                           |                   | DFM re        | evision |   |          |   |

| DFMCR1 | Control    | Е9Н     |    | Input frequency 4~9MHz(@2.7V~3.6V): write "0BH" |      |                           |                   |               |         |   |          |   |

|        | Register 0 |         |    |                                                 |      |                           |                   |               |         |   |          |   |

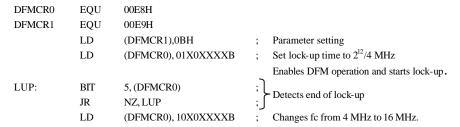

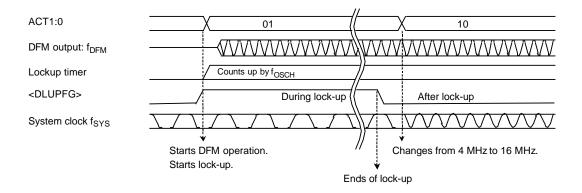

Figure 3.3.4 SFR for DFM

#### Limitation point on the use of DFM

- 1. It's prohibited to execute DFM enable/disable control in the SLOW mode(fs) (write to DFMCR0<ACT1:0>="10"). You should control DFM in the NORMAL mode.

- 2. If you stop DFM operation during using DFM(DFMCR0<ACT1:0>="10") , you shouldn't execute that change the clock  $f_{DFM}$  to  $f_{OSCH}$  and stop the DFM at the same time. Therefore the above executions should be separated into two procedures as showing below.

LD (DFMCR0),C0H ; change the clock  $f_{\text{DFM}}$  to  $f_{\text{OSCH}}$

LD (DFMCR0),00H ; DFM stop

3. If you stop high frequency oscillator during using DFM (DFMCR0<ACT1:0>="10"), you should stop DFM before you stop high frequency oscillator.

Please refer to 3.3.5 Clock Doubler (DFM) for the details.

|                   |                                            | 7                                                                                                                                                             | 6                                                      | 5                                                            | 4                                                      | 3                   | 2                                                                                                  | 1                                                       | 0                                                       |  |  |  |  |

|-------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|--|--|--|--|

| EMCCR0            | bit Symbol                                 | PROTECT                                                                                                                                                       | TA3LCDE                                                | AHOLD                                                        | TA3MLDE                                                |                     | EXTIN                                                                                              | DRVOSCH                                                 | DRVOSCL                                                 |  |  |  |  |

| (00E3H)           | Read/Write                                 | R                                                                                                                                                             | R/W                                                    | R/W                                                          | R/W                                                    | R/W                 | R/W                                                                                                | R/W                                                     | R/W                                                     |  |  |  |  |

|                   | After reset                                | 0                                                                                                                                                             | 0                                                      | 0                                                            | 0                                                      | 0                   | 0                                                                                                  | 1                                                       | 1                                                       |  |  |  |  |

|                   | Function                                   | Protect flag 0: OFF 1: ON                                                                                                                                     | LCDC<br>Source clock<br>0:32KHz<br>1:TA3OUT            | Address hold (*Note) 0;normal 1:enable                       | Melody/Alarm<br>Source clock<br>0:32KHz<br>1:TA3OUT    | Always fixed to "0" | 1: External clock                                                                                  | fc oscillator<br>driver ability<br>1: NORMAL<br>0: WEAK | fs oscillator<br>driver ability<br>1: NORMAL<br>0: WEAK |  |  |  |  |

| EMCCR1<br>(00E4H) | bit Symbol Read/Write After reset Function | Switching the protect ON/OFF by write to following 1 <sup>st</sup> -KEY,2 <sup>rd</sup> -KEY  1 <sup>st</sup> -KEY: EMCCR1=5AH,EMCCR2=A5H in succession write |                                                        |                                                              |                                                        |                     |                                                                                                    |                                                         |                                                         |  |  |  |  |

| EMCCR2<br>(00E5H) | bit Symbol Read/Write After reset Function | 2 <sup>rd</sup> -KEY: EMCCR1=A5H,EMCCR2=5AH in succession write                                                                                               |                                                        |                                                              |                                                        |                     |                                                                                                    |                                                         |                                                         |  |  |  |  |

|                   | bit Symbol                                 |                                                                                                                                                               | ENFROM                                                 | ENDROM                                                       | ENPROM                                                 |                     | FFLAG                                                                                              | DFLAG                                                   | PFLAG                                                   |  |  |  |  |

| EMCCR3            | Read/Write                                 |                                                                                                                                                               | R/W                                                    | R/W                                                          | R/W                                                    |                     | R/W                                                                                                | R/W                                                     | R/W                                                     |  |  |  |  |

| (00E6H)           | After reset                                |                                                                                                                                                               | 0                                                      | 0                                                            | 0                                                      |                     | 0                                                                                                  | 0                                                       | 0                                                       |  |  |  |  |

|                   | Function                                   |                                                                                                                                                               | CS1A area<br>detect control<br>0: disable<br>1: enable | CS2B-2G<br>area detect<br>control<br>0: disable<br>1: enable | CS2A area<br>detect control<br>0: disable<br>1: enable |                     | CS1A write Operation flag  When reading "0": not written "1": written When writing "0": clear flag | CS2B-2G<br>write peration<br>Flag                       | CS2A write<br>Operation<br>Flag                         |  |  |  |  |

Figure 3.3.5 SFR for noise-reducing

Note: When getting access to the logic address 000000H to 003000H and FFE000H to FFFFFFH, A0 to A23 holds the previous address.

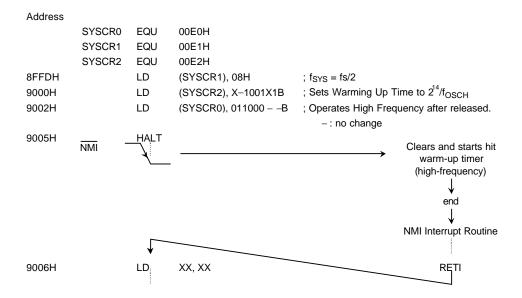

# 3.3.3 System clock controller

The system clock controller generates the system clock signal ( $f_{SYS}$ ) for the CPU core and internal I/O. It contains two oscillation circuits and a clock gear circuit for high-frequency (fc) operation. The register SYSCR1<SYSCK> changes the system clock to either fc or fs, SYSCR0<XEN> and SYSCR0<XTEN> control enabling and disabling of each oscillator, and SYSCR1<GEAR0 to GEAR2> sets the high-frequency clock gear to either 1, 2, 4, 8 or 16 (fc, fc/2, fc/4, fc/8 or fc/16). These functions can reduce the power consumption of the equipment in which the device is installed.

The combination of settings  $\langle XEN \rangle = 1$ ,  $\langle XTEN \rangle = 0$ ,  $\langle SYSCK \rangle = 0$  and  $\langle GEAR0 \rangle = 100$  will cause the system clock ( $f_{SYS}$ ) to be set to  $f_{C}/32$  ( $f_{C}/16 \times 1/2$ ) after a Reset.

For example,  $f_{SYS}$  is set to 0.5 MHz when the 16-MHz oscillator is connected to the X1 and X2 pins.

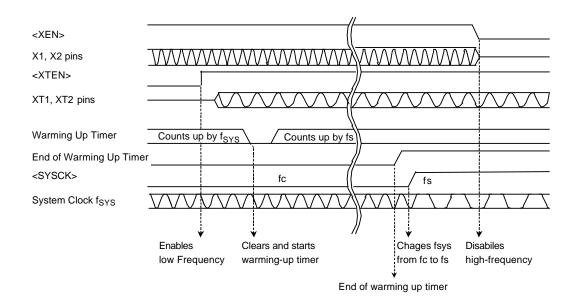

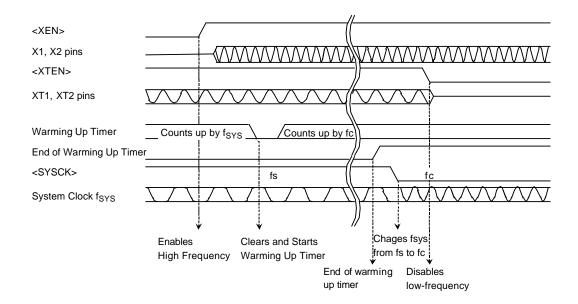

#### (1) Switching from Normal Mode to Slow Mode

When the resonator is connected to the X1 and X2 pins, or to the XT1 and XT2 pins, the warm-up timer can be used to change the operation frequency after stable oscillation has been attained.

The warm-up time can be selected using SYSCR2<WUPTM0,WUPTM1>.

This warm-up timer can be programmed to start and stop as shown in the following examples 1 and 2.

Table 3.3.1 shows the warm-up time.

Note 1: When using an oscillator (other than a resonator) with stable oscillation, a warm-up timer is not needed.

Note 2: The warm-up timer is operated by an oscillation clock. Hence, there may be some variation in warm-up time.

| Warming-up Time<br>SYSCR2<br><wuptm1,wuptm0></wuptm1,wuptm0> | Change to<br>Normal Mode | Change to<br>Slow Mode |

|--------------------------------------------------------------|--------------------------|------------------------|

| 01 (2 <sup>8</sup> / frequency)                              | 16 (μs)                  | 7.8 (ms)               |

| 10 (2 <sup>14</sup> / frequency)                             | 1.024 (ms)               | 500 (ms)               |

| 11 (2 <sup>16</sup> / frequency)                             | 4.096 (ms)               | 2000 (ms)              |

Table 3.3.1 Warming-up times

at  $f_{OSCH} = 16 \text{ MHz}$ , fs = 32.768 kHz

# Example 1-Setting the clock

Changing from high frequency (fc) to low frequency (fs).

| SYSCR0 | EQU | 00E0H             |                                             |

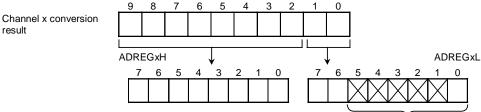

|--------|-----|-------------------|---------------------------------------------|