RTL8208B-LF RTL8208BF-LF

# SINGLE-CHIP OCTAL 10/100BASE-TX/FX PHY TRANSCEIVER

# DATASHEET

Rev. 1.3 22 September 2006 Track ID: JATR-1076-21

**Realtek Semiconductor Corp.**

No. 2, Innovation Road II, Hsinchu Science Park, Hsinchu 300, Taiwan Tel.: +886-3-578-0211. Fax: +886-3-577-6047 www.realtek.com.tw

#### COPYRIGHT

©2006 Realtek Semiconductor Corp. All rights reserved. No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form or by any means without the written permission of Realtek Semiconductor Corp.

#### DISCLAIMER

Realtek provides this document "as is", without warranty of any kind, neither expressed nor implied, including, but not limited to, the particular purpose. Realtek may make improvements and/or changes in this document or in the product described in this document at any time. This document could include technical inaccuracies or typographical errors.

#### TRADEMARKS

Realtek is a trademark of Realtek Semiconductor Corporation. Other names mentioned in this document are trademarks/registered trademarks of their respective owners.

#### USING THIS DOCUMENT

This document is intended for the engineer's reference and provides detailed programming information.

Though every effort has been made to ensure that this document is current and accurate, more information may have become available subsequent to the production of this guide. In that event, please contact your Realtek representative for additional information that may help in the development process.

#### **REVISION HISTORY**

| Revision | Release Date | Summary                                                                                                                         |

|----------|--------------|---------------------------------------------------------------------------------------------------------------------------------|

| 1.0      | 2003/12/16   | Draft release.                                                                                                                  |

| 1.1      | 2004/08/30   | First approved release.                                                                                                         |

| 1.2      | 2004/08/31   | Change bias resistor value to 2K ohm in Figure 22 on page 49.                                                                   |

| 1.3      | 2006/09/22   | <ol> <li>Add Fiber Application information for RTL8208BF-LF.</li> <li>Modify Figure 1, page 3, and Figure 2, page 4.</li> </ol> |

|          |              | 3. Modify Table 1. Pin Assignments, on page 5.                                                                                  |

|          |              | 4. Modify Table 5. RMII/SMII/SS-SMII Pins, page 7.                                                                              |

|          |              | 5. Corrected SMI Clock frequency from 25MHz to 2.5MHz (Table 6,                                                                 |

|          |              | page 9, section 7.1.1, page 26, and Table 40, page 52).                                                                         |

|          |              | 6. Recommend LEDMODE Pin be pulled high or pulled low (see Table 8,                                                             |

|          |              | page 10).<br>7. Add LED rise and fall timing (Figure 16, page 42).                                                              |

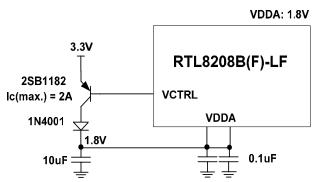

|          |              | 8. Change 2SB1188 to 2SB1182 (Figure 20 and Table 35, page 47).                                                                 |

|          |              | 9. Modify Table 36. Absolute Maximum Ratings, and Table 37. Operating                                                           |

|          |              | Range, on page 50.                                                                                                              |

|          |              | 10. Add power startup internal sequence (section 9.6 Power Start Up &                                                           |

|          |              | Internal Reset Sequence, page 56).                                                                                              |

|          |              | 11. Modify section 10 Mechanical Dimensions, page 58.                                                                           |

|          |              | 12. Modify section 11 Ordering Information, page 59.                                                                            |

## **Table of Contents**

| 1.  | GENI       | ERAL DESCRIPTION                                                        | 1        |

|-----|------------|-------------------------------------------------------------------------|----------|

| 2.  | FEAT       | URES                                                                    | 2        |

| 3.  | APPL       | JCATIONS                                                                | 2        |

| 4.  | PIN A      | SSIGNMENTS                                                              |          |

|     | .1.        | PIN ASSIGNMENTS (RTL8208B-LF)                                           |          |

| -   | .1.        | LEAD (PB)-FREE PACKAGE IDENTIFICATION                                   |          |

| -   | .2.        | PIN ASSIGNMENTS (RTL8208BF-LF)                                          |          |

|     | .3.        | LEAD (PB)-FREE PACKAGE IDENTIFICATION                                   |          |

| -   |            | DESCRIPTIONS                                                            |          |

|     | .1.        | MEDIA CONNECTION PINS.                                                  |          |

|     | .1.        | POWER AND GROUND PINS                                                   |          |

| -   | .2.<br>.3. |                                                                         |          |

| -   | .3.<br>.4. | MISCELLANEOUS PINS<br>RMII/SMII/SS-SMII PINS                            |          |

| -   | .4.<br>.5. | SMI (Serial Management Interface)                                       | /        |

| -   | .5.<br>.6. | LED PINS                                                                |          |

| -   | .0.        | MODE CONTROL PINS                                                       |          |

| -   | .7.<br>.8. | TEST PINS                                                               |          |

|     |            |                                                                         |          |

| 6.  | REGI       | STER DESCRIPTIONS                                                       |          |

| 6   | .1.        | REGISTER0: CONTROL                                                      |          |

| 6   | .2.        | REGISTER1: STATUS                                                       |          |

| 6   | .3.        | REGISTER2: PHY IDENTIFIER 1 REGISTER                                    |          |

| 6   | .4.        | REGISTER3: PHY IDENTIFIER 2 REGISTER                                    |          |

| 6   | .5.        | REGISTER4: AUTO-NEGOTIATION ADVERTISEMENT                               |          |

| 6   | .6.        | REGISTER5: AUTO-NEGOTIATION LINK PARTNER ABILITY                        |          |

| 6   | .7.        | REGISTER6: AUTO-NEGOTIATION EXPANSION                                   | 23       |

| 6   | .8.        | PORT 1 REGISTER24: CABLE TESTER CONTROL REGISTER0                       |          |

| 6   | .9.        | PORT1 REGISTER29: CABLE TESTER CONTROL REGISTER1                        |          |

| 6   | .10.       | PORT1 REGISTER30: CABLE STATUS REGISTER                                 | 25       |

| 7.  | FUNC       | CTION DESCRIPTION                                                       |          |

| 7   | .1.        | GENERAL                                                                 |          |

| ,   | 7.1.1.     |                                                                         |          |

|     | 7.1.2.     |                                                                         |          |

|     | 7.1.3.     | PHY Address                                                             |          |

|     | 7.1.4.     |                                                                         |          |

|     | 7.1.5.     |                                                                         |          |

| 7   | .2.        | INITIALIZATION AND SETUP                                                |          |

|     | 7.2.1.     |                                                                         |          |

|     | 7.2.2.     | Setup and Configuration                                                 |          |

| 7   | .3.        | 10Base-T                                                                |          |

|     | 7.3.1.     | Transmit Function                                                       |          |

|     | 7.3.2.     | Receive Function                                                        |          |

|     | 7.3.3.     | Link Monitor                                                            |          |

|     | 7.3.4.     | Jabber                                                                  |          |

|     | 7.3.5.     | Loopback                                                                |          |

| 7   | .4.        | 100BASE-TX                                                              | 29       |

|     | 7.4.1.     | Transmit Function                                                       | 29       |

|     | 7.4.2.     | Receive Function                                                        |          |

|     | 7.4.3.     | Link Monitor                                                            | 31       |

| Sin | gle-Ch     | <i>ip Octal 10/100-TX/FX PHY Transceiver</i> iii Track ID: JATR-1076-21 | Rev. 1.3 |

#### RTL8208B-LF/RTL8208BF-LF Datasheet

| 7.5.             | BASELINE WANDER COMPENSATION                   |  |

|------------------|------------------------------------------------|--|

| 7.6.             | 100BASE-FX (RTL8208BF-LF ONLY)                 |  |

| 7.6.1.           | Transmit Function                              |  |

| 7.6.2.           | Receive Function                               |  |

| 7.6.3.           | Link Monitor                                   |  |

| 7.6.4.           | Far-End-Fault-Indication                       |  |

| 7.6.5.           | Reduced Fiber Interface                        |  |

| 7.7.             | RMII/SMII/SS-SMII                              |  |

| 7.7.1.           | RMII (Reduced MII)                             |  |

| 7.7.2.           | SMII (Serial MII)                              |  |

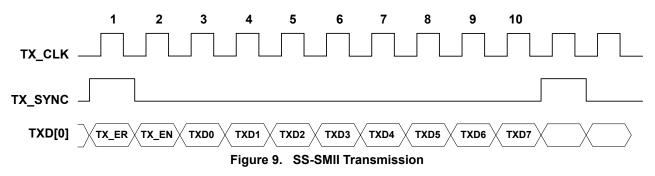

| <i>7.7.3</i> .   | SS-SMII (Source Synchronous -Serial MII)       |  |

| 7.8.             | POWER SAVING AND POWER DOWN MODE               |  |

| 7.8.1.           | Power Saving Mode                              |  |

| 7.8.2.           | 0                                              |  |

| 7.9.             | LED CONFIGURATION                              |  |

| 7.9.1.           | Serial LEDs                                    |  |

| 7.9.2.           | ~ = = =                                        |  |

| 7.10.            | CROSSOVER DETECTION AND AUTO CORRECTION        |  |

| 7.11.            | POLARITY DETECTION AND AUTO CORRECTION         |  |

| 7.12.            | 1.8V POWER GENERATION                          |  |

| 7.13.            | CABLE TESTER                                   |  |

| 8. APPL          | ICATION INFORMATION                            |  |

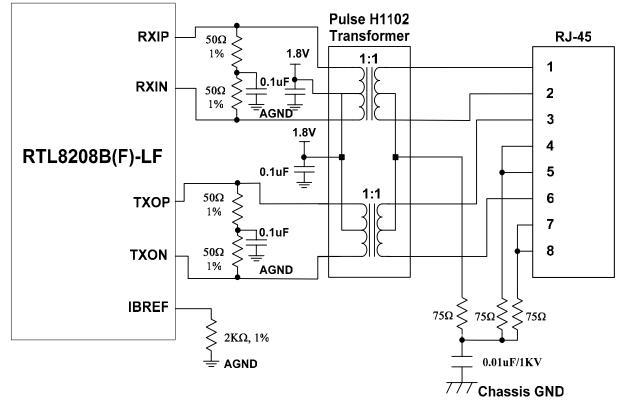

| 8.1.             | 10BASE-T/100BASE-TX APPLICATION                |  |

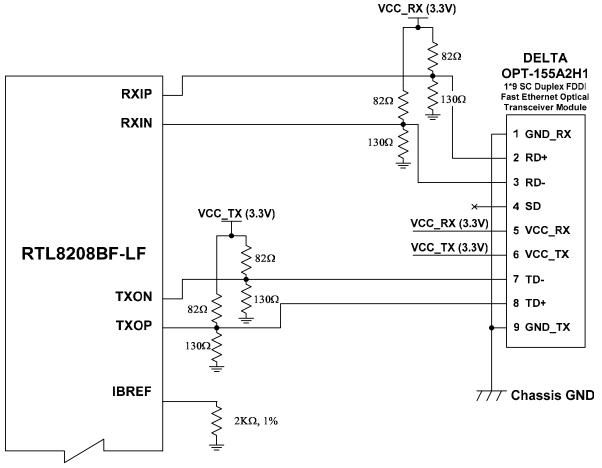

| 8.2.             | 100BASE-FX APPLICATION (RTL8208BF-LF ONLY)     |  |

| 9. CHAI          | RACTERISTICS                                   |  |

| 9.1.             | ABSOLUTE MAXIMUM RATINGS                       |  |

| 9.2.             | OPERATING RANGE                                |  |

| 9.3.             | DC CHARACTERISTICS                             |  |

| 9.4.             | AC CHARACTERISTICS                             |  |

| 9.5.             | DIGITAL TIMING CHARACTERISTICS                 |  |

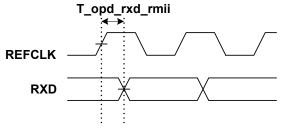

| 9.5.1.           | RMII Receive Timing                            |  |

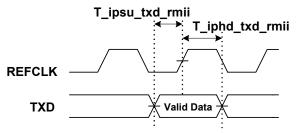

| 9.5.2.           | RMII Transmit Timing                           |  |

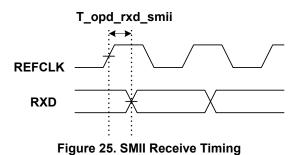

| 9.5.3.           | SMII Receive Timing                            |  |

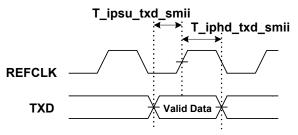

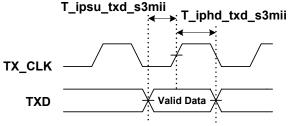

| 9.5.4.           | SMII Transmit Timing                           |  |

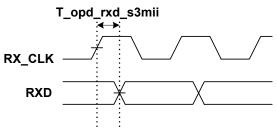

| 9.5.5.           | SS-SMII Receive Timing                         |  |

| 9.5.6.           | SS-SMII Transmit Timing                        |  |

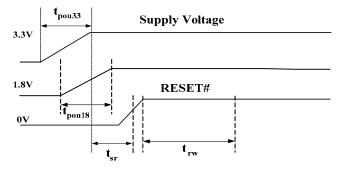

| 9.6.<br>0.7      | POWER START UP & INTERNAL RESET SEQUENCE       |  |

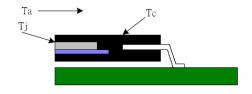

| 9.7.             | THERMAL CHARACTERISTICS.                       |  |

| 9.7.1.<br>9.7.2. | Thermal Operating Range<br>Thermal Resistances |  |

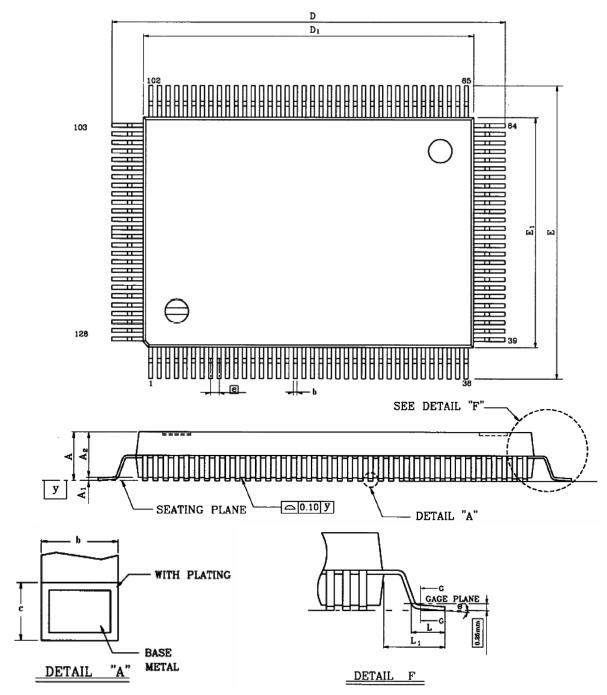

|                  | CHANICAL DIMENSIONS                            |  |

| 10. ME<br>10.1.  | NOTES FOR MECHANICAL DIMENSIONS                |  |

| 10.1.            | INUTES FOR INTEGRATICAL DIMENSIONS             |  |

| 11. OR           | DERING INFORMATION                             |  |

## List of Tables

|           | PIN ASSIGNMENTS                                   |     |

|-----------|---------------------------------------------------|-----|

|           | MEDIA CONNECTION PINS                             |     |

|           | Power and Ground Pins                             |     |

|           | MISCELLANEOUS PINS                                |     |

|           | RMII/SMII/SS-SMII PINS                            |     |

|           | SMI (SERIAL MANAGEMENT INTERFACE)                 |     |

|           | LED PINS                                          |     |

|           | MODE CONTROL PINS                                 |     |

|           | TEST PINS                                         |     |

|           | REGISTER DESCRIPTIONS                             |     |

|           | REGISTERO: CONTROL                                |     |

|           | REGISTER1: STATUS                                 |     |

|           | REGISTER2: PHY IDENTIFIER 1 REGISTER              |     |

|           | REGISTER3: PHY IDENTIFIER 2 REGISTER              |     |

|           | REGISTER4: AUTO-NEGOTIATION ADVERTISEMENT         |     |

|           | REGISTER5: AUTO-NEGOTIATION LINK PARTNER ABILITY  |     |

|           | REGISTER6: AUTO-NEGOTIATION EXPANSION             |     |

|           | PORT 1 REGISTER24: CABLE TESTER CONTROL REGISTER0 |     |

|           | PORT1 REGISTER29: CABLE TESTER CONTROL REGISTER1  |     |

|           | PORT1 REGISTER30: CABLE STATUS REGISTER           |     |

|           | SMI READ/WRITE CYCLES                             |     |

|           | PORT PAIR-LOOP BACK MODE (PP-LPBK)                |     |

|           | 4B/5B CODING                                      |     |

|           | 100BASE-FX                                        |     |

|           | PECL DC CHARACTERISTICS                           |     |

|           | RMII/SMII/SS-SMII MODES                           |     |

|           | RMII/SMII/SS-SMII SIGNALS                         |     |

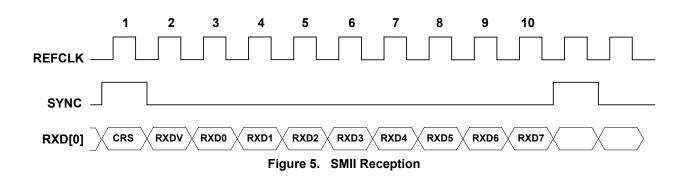

|           | SMII RECEPTION ENCODING                           |     |

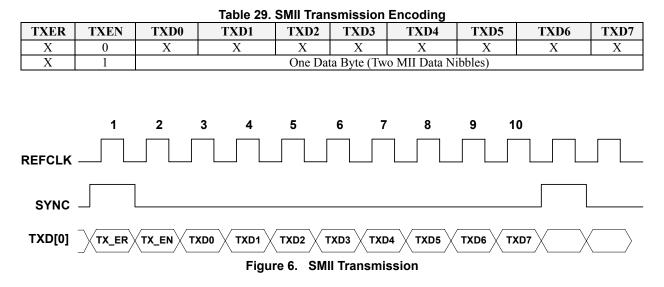

|           | SMII TRANSMISSION ENCODING                        |     |

|           | SERIAL LED MODE                                   |     |

|           | SERIAL LED STATUS                                 |     |

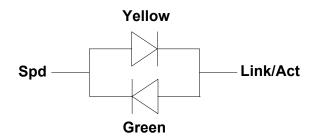

|           | BI-COLOR LED                                      |     |

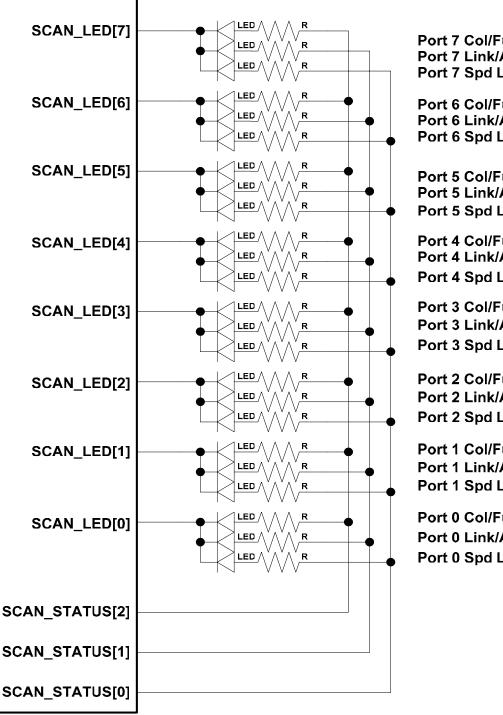

|           | SCAN LED                                          |     |

|           | SCAN LED STATUS                                   |     |

|           | AN EXAMPLE USING POWER TRANSISTOR 2SB1182         |     |

|           | ABSOLUTE MAXIMUM RATINGS                          |     |

|           | OPERATING RANGE                                   |     |

|           | DC CHARACTERISTICS                                |     |

|           | AC CHARACTERISTICS                                |     |

| TABLE 40. | DIGITAL TIMING CHARACTERISTICS                    | .52 |

|           | RMII RECEIVE TIMING                               |     |

|           | RMII TRANSMIT TIMING                              |     |

|           | SMII RECEIVE TIMING                               |     |

|           | SMII TRANSMIT TIMING                              |     |

|           | SS-SMII RECEIVE TIMING                            |     |

|           | SS-SMII TRANSMIT TIMING                           |     |

|           | THERMAL OPERATING RANGE                           |     |

|           | THERMAL RESISTANCES                               |     |

| TABLE 49  | ORDERING INFORMATION                              | .59 |

|           |                                                   |     |

v

# **List of Figures**

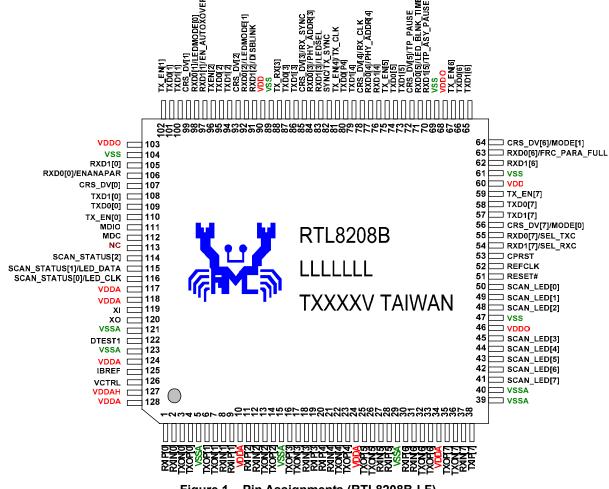

| FIGURE 1. PIN ASSIGNMENTS (RTL8208B-LF)                                    | 3  |

|----------------------------------------------------------------------------|----|

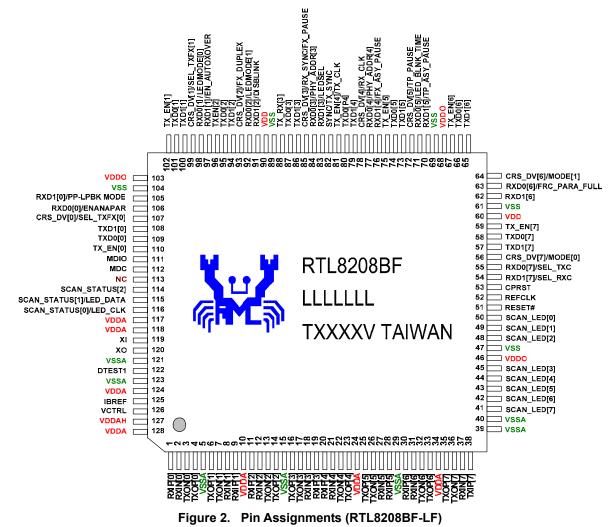

| FIGURE 2. PIN ASSIGNMENTS (RTL8208BF-LF)                                   |    |

| FIGURE 3. RMII SIGNAL DIAGRAM                                              |    |

| FIGURE 4. SMII SIGNAL DIAGRAM                                              |    |

| FIGURE 5. SMII RECEPTION                                                   |    |

| FIGURE 6. SMII TRANSMISSION                                                |    |

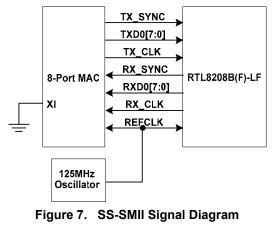

| FIGURE 7. SS-SMII SIGNAL DIAGRAM                                           |    |

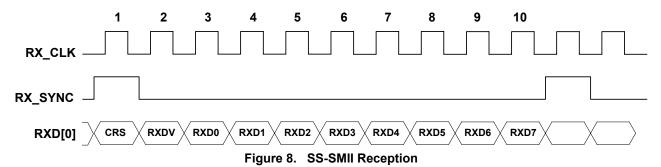

| FIGURE 8. SS-SMII RECEPTION                                                |    |

| FIGURE 9. SS-SMII TRANSMISSION                                             |    |

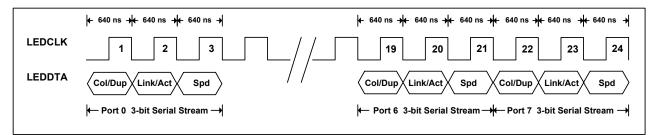

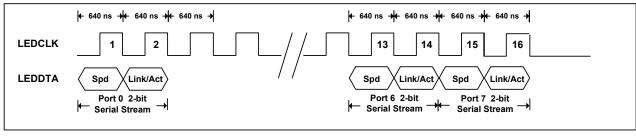

| FIGURE 10. 3-BIT SERIAL STREAM MODE                                        |    |

| FIGURE 11. 2-BIT SERIAL STREAM MODE                                        |    |

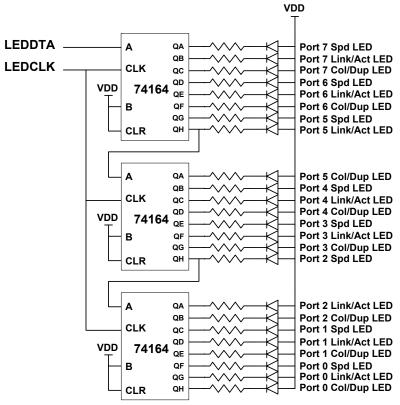

| FIGURE 12. EXTERNAL CIRCUIT FOR 3-BIT SERIAL LED MODE                      |    |

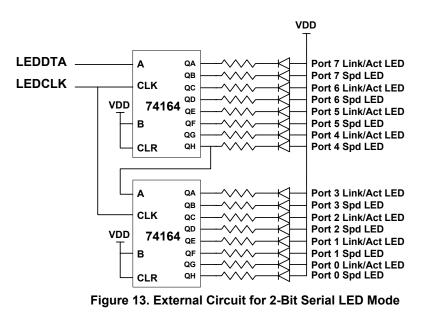

| FIGURE 13. EXTERNAL CIRCUIT FOR 2-BIT SERIAL LED MODE                      | 40 |

| FIGURE 14. 3-BIT BI-COLOR LED.                                             |    |

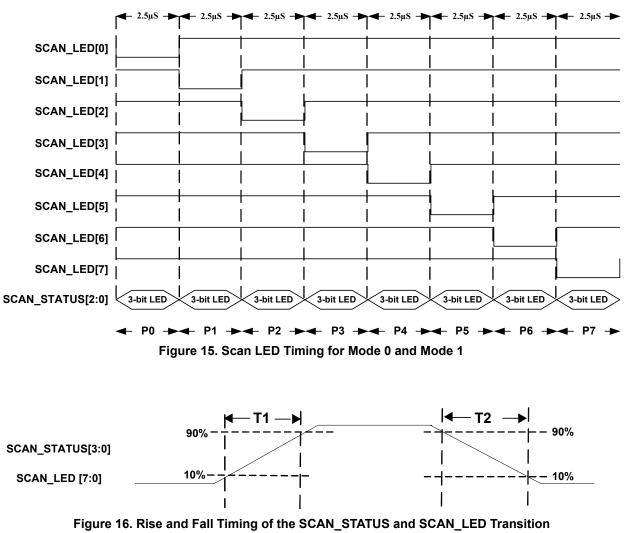

| FIGURE 15. SCAN LED TIMING FOR MODE 0 AND MODE 1                           |    |

| FIGURE 16. RISE AND FALL TIMING OF THE SCAN_STATUS AND SCAN_LED TRANSITION |    |

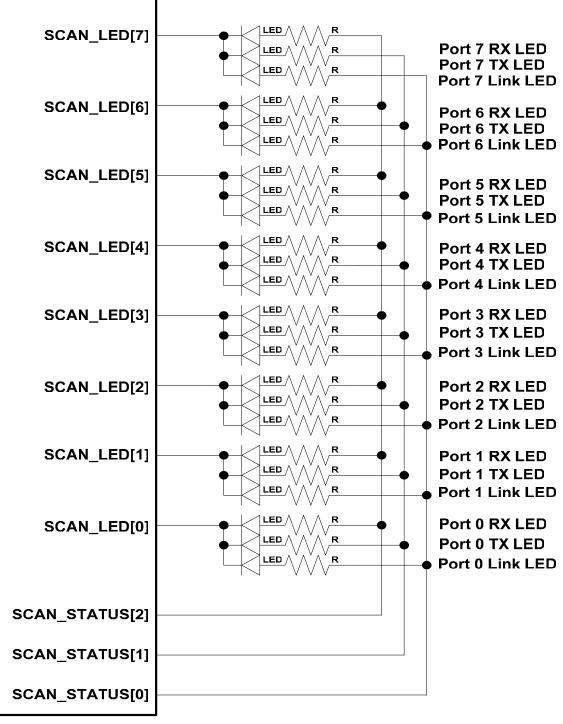

| FIGURE 17. EXTERNAL CIRCUIT FOR SCAN LED MODE 0                            |    |

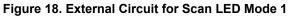

| FIGURE 18. EXTERNAL CIRCUIT FOR SCAN LED MODE 1                            |    |

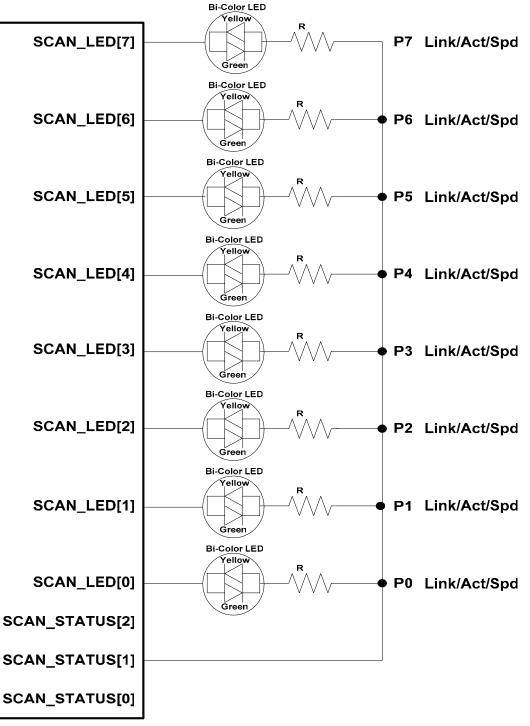

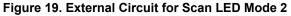

| FIGURE 19. EXTERNAL CIRCUIT FOR SCAN LED MODE 2                            |    |

| FIGURE 20. USING A PNP TRANSISTOR TO TRANSFORM 3.3V INTO 1.8V              |    |

| FIGURE 21. 10BASE-T/100BASE-TX APPLICATION                                 |    |

| FIGURE 22. 100BASE-FX APPLICATION (RTL8208BF-LF ONLY)                      |    |

| FIGURE 23. RMII RECEIVE TIMING                                             |    |

| FIGURE 24. RMII TRANSMIT TIMING                                            |    |

| FIGURE 25. SMII RECEIVE TIMING                                             |    |

| FIGURE 26. SMII TRANSMIT TIMING                                            |    |

| FIGURE 27. SS-SMII RECEIVE TIMING                                          |    |

| FIGURE 28. SS-SMII TRANSMIT TIMING                                         |    |

| FIGURE 29. POWER START UP & INTERNAL RESET SEQUENCE                        |    |

| FIGURE 30. CROSS-SECTION OF 128-PIN QFP                                    | 57 |

|                                                                            |    |

# **1. General Description**

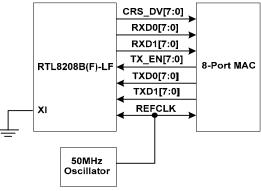

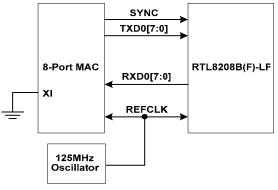

The RTL8208B-LF and RTL8208BF-LF (jointly referred to as the RTL8208B(F)-LF) are single-chip highly integrated 8-port, 10Base-T/100Base-TX (FX) Ethernet transceivers implemented in 0.18µm CMOS technology. They are currently the world's smallest Octal-PHY chip package. Realtek patented removal of traditional SD pins in 100Base-FX (RTL8208BF-LF only) allow us to obtain a lower pincount. Flexible hardware settings are provided to configure the various operating modes of the chip.

The RTL8208B(F)-LF provides 8 separate and independent channels. Each channel consists of an RMII/SMII/SS-SMII interface-to-MAC controller, and hardware pins are used to configure the interface for RMII, SMII, or SS-SMII mode. In RMII mode, another hardware pin is used to set Port-Pair Loopback mode (PP-LPBK MODE, RTL8208BF-LF only), which can extend physical transmission length and perform physical media transport operations without a switch controller.

A PECL (Pseudo Emitter Coupled Logic) receiver accepts input from a fiber transceiver and directly passed to a clock recovery circuit for data/clock recovery. The chip utilizes an advanced CMOS process to meet low voltage and low power requirements. With on-chip DSP (Digital Signal Processing) technology, the chip provides excellent performance under all operating conditions.

A built-in UTP cable tester diagnoses an open/short fault in an attached cable. The RTL8208B(F)-LF also features very low power consumption (maximum of 1.6W). Additionally, pin-outs are designed to provide optimized direct routing, which simplifies the layout work and reduces EMI noise issues.

## 2. Features

- Supports 8-port integrated physical layer and transceiver for 10Base-T and 100Base-TX

- Up to 8 ports support 100Base-FX (RTL8208BF-LF only)

- Reduced 100Base-FX (RTL8208BF-LF only) interface (patented)

- Robust baseline wander correction for improved 100Base-TX performance

- Complies with IEEE 802.3/802.3u

- IEEE 802.3u compliant auto negotiation for 10/100Mbps control

- Hardware controlled Flow control advertisement ability

- Supports RMII/SMII/SS-SMII interfaces

- Very low power consumption

- Supports Port-Pair Loopback mode (PP-LPBK mode, RTL8208BF-LF only)

- Supports two power reduction methods:

- Power saving mode (cable detection)

- Power down mode

- Power-on auto reset function eliminates the need for external reset circuits

- Crossover detection and auto correction

- Polarity detection and Auto Correction

- Flexible serial/scan LED display modes

- Cable tester for diagnosing open/short faults in attached cables

- 128-pin QFP package

- $\blacksquare 1.8V/3.3V \text{ power supply}$

- 0.18µm, CMOS technology

# 3. Applications

#### RTL8208B-LF

• Octal PHY for Fast Ethernet switch with twisted pair interface

#### RTL8208BF-LF

■ Octal PHY for Fast Ethernet switch with twisted pair interface and fiber capability

# 4. Pin Assignments

### 4.1. Pin Assignments (RTL8208B-LF)

Octal PHY for Fast Ethernet Switch with Twisted Pair Interface

Figure 1. Pin Assignments (RTL8208B-LF)

3

*Note: Signal type codes are listed in section 5 Pin Descriptions, page 6.*

## 4.2. Lead (Pb)-Free Package Identification

Lead (Pb)-free package is indicated by an 'L' in the location marked 'T' in Figure 1.

## 4.3. Pin Assignments (RTL8208BF-LF)

Octal PHY for Fast Ethernet Switch with Twisted Pair Interface and Fiber Capability

*Note: Signal type codes are listed in section 5 Pin Descriptions, page 6.*

## 4.4. Lead (Pb)-Free Package Identification

Lead (Pb)-free package is indicated by an 'L' in the location marked 'T' in Figure 2.

#### RTL8208B-LF/RTL8208BF-LF Datasheet

|                                   | Table 1. Pin Assignments |                  |            |                                                 |            |                  |            |  |

|-----------------------------------|--------------------------|------------------|------------|-------------------------------------------------|------------|------------------|------------|--|

| Pin Name                          | Pin#                     | Function         | Driver     | Pin Name                                        | Pin#       | Туре             | Driver     |  |

|                                   |                          |                  | Capacity   |                                                 |            |                  | Capacity   |  |

| RXIP[0]                           | 1                        | AI               | -          | TXD1[6]                                         | 65         | I,ND             | -          |  |

| RXIN[0]                           | 2                        | AI               | -          | TXD0[6]                                         | 66         | I,ND             | -          |  |

| TXON[0]                           | 3                        | AO               | -          | TX_EN[6]                                        | 67         | I,ND             | -          |  |

| TXOP[0]                           | 4                        | AO               | -          | VDDO                                            | 68         | DP               | -          |  |

| VSSA                              | 5                        | AG               | -          | VSS                                             | 69<br>70   | DG<br>I/O,Pd     | 8mA        |  |

| TXOP[1]<br>TXON[1]                | 6<br>7                   | AO<br>AO         | -          | RXD1[5]/ TP_ASY_PAUSE<br>RXD0[5]/ LED BLNK TIME | 70<br>71   | I/O,Pd<br>I/O,Pu | 8mA        |  |

| RXIN[1]                           | 8                        | AU               | -          | CRS DV[5]/ TP PAUSE                             | 71         | I/O,Pu<br>I/O,Pu | 8mA        |  |

| RXIP[1]                           | 9                        | AI               | -          | TXD1[5]                                         | 73         | I,ND             | -          |  |

| VDDA                              | 10                       | AP               | -          | TXD0[5]                                         | 74         | I,ND             |            |  |

| RXIP[2]                           | 11                       | AI               | -          | TX EN[5]                                        | 75         | I,ND             | -          |  |

| RXIN[2]                           | 12                       | AI               | -          | RXD1[4]/FX ASY PAUSE                            | 76         | I/O,Pd           | 8mA        |  |

| TXON[2]                           | 13                       | AO               | -          | RXD0[4]/ PHY ADDR[4]                            | 77         | I/O,Pd           | 8mA        |  |

| TXOP[2]                           | 14                       | AO               | -          | CRS $DV[4]/R\overline{X}$ CLK                   | 78         | I/O,ND           | 16mA       |  |

| VSSA                              | 15                       | AG               | -          | TXD1[4]                                         | 79         | I,ND             | -          |  |

| TXOP[3]                           | 16                       | AO               | -          | TXD0[4]                                         | 80         | I,ND             | -          |  |

| TXON[3]                           | 17                       | AO               | -          | TX_EN[4]/ TX_CLK                                | 81         | I,ND             | -          |  |

| RXIN[3]                           | 18                       | AI               | -          | SYNC/TX_SYNC                                    | 82         | I,Pd             | -          |  |

| RXIP[3]                           | 19                       | AI               | -          | RXD1[3]/ LEDSEL                                 | 83         | I/O,Pd           | 8mA        |  |

| RXIP[4]                           | 20                       | AI               | -          | RXD0[3]/ PHY_ADDR[3]                            | 84         | I/O,Pu           | 8mA        |  |

| RXIN[4]                           | 21                       | AI               | -          | CRS_DV[3]/RX_SYNC/ FX_PAUSE                     | 85         | I/O,Pu           | 8mA        |  |

| TXON[4]                           | 22                       | AO               | -          | TXD1[3]                                         | 86         | I,ND             | -          |  |

| TXOP[4]                           | 23                       | AO               | -          | TXD0[3]                                         | 87         | I,ND             | -          |  |

| VDDA<br>TVODISI                   | 24                       | AP               | -          | TX_EN[3]                                        | 88         | I,ND             | -          |  |

| TXOP[5]                           | 25<br>26                 | AO<br>AO         | -          | VSS<br>VDD                                      | 89<br>90   | DG<br>DP         | -          |  |

| TXON[5]<br>RXIN[5]                | 20                       | AU               | -          | RXD1[2]/ DISBLINK                               | 90<br>91   | I/O,Pd           | 8mA        |  |

| RXIP[5]                           | 28                       | AI               | -          | RXD0[2]/ LEDMODE[1]                             | 92         | I/O,Pd           | 8mA        |  |

| VSSA                              | 20                       | AG               | -          | CRS DV[2]/ FX DUPLEX                            | 93         | I/O,Pu           | 8mA        |  |

| RXIP[6]                           | 30                       | AI               | -          | TXD1[2]                                         | 94         | I,ND             | -          |  |

| RXIN[6]                           | 31                       | AI               | -          | TXD0[2]                                         | 95         | I,ND             | -          |  |

| TXON[6]                           | 32                       | AO               | -          | TX EN[2]                                        | 96         | I,ND             | -          |  |

| TXOP[6]                           | 33                       | AO               | -          | RXD1[1]/EN AUTOXOVER                            | 97         | I/O,Pu           | 8mA        |  |

| VDDA                              | 34                       | AP               | -          | RXD0[1]/ LEDMODE[0]                             | 98         | I/O,Pd           | 8mA        |  |

| TXOP[7]                           | 35                       | AO               | -          | CRS_DV[1]/ SEL_TXFX[1]                          | 99         | I/O,Pd           | 8mA        |  |

| TXON[7]                           | 36                       | AO               | -          | TXD1[1]                                         | 100        | I,ND             | -          |  |

| RXIN[7]                           | 37                       | AI               | -          | TXD0[1]                                         | 101        | I,ND             | -          |  |

| RXIP[7]                           | 38                       | AI               | -          | TX_EN[1]                                        | 102        | I,ND             | -          |  |

| VSSA                              | 39                       | AG               | -          | VDDO                                            | 103        | DP               | -          |  |

| VSSA                              | 40                       | AG               | -          | VSS                                             | 104        | DG               | -          |  |

| SCAN_LED[7]                       | 41                       | O,Pu             | 8mA        | RXD1[0]/ PP-LPBK MODE                           | 105        | I/O,Pd           | 8mA<br>8mA |  |

| SCAN_LED[6]                       | 42                       | O,Pu             | 8mA<br>8mA | RXD0[0]/ENANAPAR                                | 106        | I/O,Pd           | 8mA        |  |

| SCAN_LED[5]                       | 43<br>44                 | O,Pu<br>O,Pu     | 8mA        | CRS_DV[0]/ SEL_TXFX[0]<br>TXD1[0]               | 107<br>108 | I/O,Pd<br>I,ND   | omA        |  |

| SCAN_LED[4]<br>SCAN_LED[3]        | 44                       | O,Pu<br>O,Pu     | 8mA        | TXD0[0]                                         | 108        | I,ND<br>I,ND     | _          |  |

| VDDO                              | 43                       | DP               | -          | TX EN[0]                                        | 1109       | I,ND<br>I,ND     | _          |  |

| VSS                               | 47                       | DG               | -          | MDIO                                            | 110        | I/O,Pu           | 8mA        |  |

| SCAN_LED[2]                       | 48                       | O,Pu             | 8mA        | MDC                                             | 112        | I,Pd             | -          |  |

| SCAN LED[1]                       | 49                       | O,Pu             | 8mA        | NC                                              | 112        | -                | -          |  |

| SCAN LED[0]                       | 50                       | O,Pu             | 8mA        | SCAN_STATUS[2]                                  | 114        | O,Pu             | 8mA        |  |

| RESET#                            | 51                       | I,Pu             | -          | SCAN_STATUS[1] /LED_DATA                        | 115        | O,Pu             | 8mA        |  |

| REFCLK                            | 52                       | I/O,Pd           | 8mA        | SCAN_STATUS[0] /LED_CLK                         | 116        | O,Pu             | 8mA        |  |

| CPRST                             | 53                       | I,Pd             | -          | VDDA                                            | 117        | AP               | -          |  |

| RXD1[7]/ SEL_RXC                  | 54                       | I/O,Pd           | 8mA        | VDDA                                            | 118        | AP               | -          |  |

| RXD0[7]/ SEL_TXC                  | 55                       | I/O,Pd           | 8mA        | XI                                              | 119        | I,ND             | -          |  |

| CRS_DV[7]/ MODE[0]                | 56                       | I/O,Pu           | 8mA        | XO                                              | 120        | O,ND             | -          |  |

| TXD1[7]                           | 57                       | I,ND             | -          | VSSA                                            | 121        | AG               | -          |  |

| TXD0[7]                           | 58                       | I,ND             | -          | DTEST1                                          | 122        | I/O,ND           | -          |  |

| TX_EN[7]                          | 59                       | I,ND             | -          | VSSA                                            | 123        | AG               | -          |  |

| VDD                               | 60<br>61                 | DP               | -          | VDDA                                            | 124        | AP               | -          |  |

| VSS<br>PVD161                     | 61<br>62                 | DG<br>I/O Pd     | -<br>8mA   | IBREF<br>VCTRL                                  | 125        | AO               | -          |  |

| RXD1[6]<br>RXD0[6]/ FRC PARA FULL | 62<br>63                 | I/O,Pd<br>I/O,Pd | 8mA<br>8mA | VDDAH                                           | 126<br>127 | AO<br>AP         | -          |  |

| CRS DV[6]/ MODE[1]                | 63<br>64                 | I/O,Pu           | 8mA        | VDDA                                            | 127        | AP               | -          |  |

|                                   | 04                       | 1/0,1 u          | 01111      | TUUA                                            | 120        | AI               | -          |  |

Single-Chip Octal 10/100-TX/FX PHY Transceiver

Track ID: JATR-1076-21 Rev. 1.3

# 5. Pin Descriptions

In order to reduce pin count, and therefore size and cost, some pins have multiple functions. In such cases the functions are separated with a " / " symbol. For the RTL8208B-LF refer to Figure 1, page 3; for the RTL8208BF-LF refer to Figure 2, page 4, for a graphical representation.

Signal type codes shown below are used in the previous and following tables:

- I: Input

- O: Output

- A: Analog signal

- D: Digital signal

- ND: Not defined

- P: Power

- G: Ground

- Pu: Internal pull up (30K ohm)

- Pd: Internal pull down (30K ohm)

|           | Table 2. Media Connection Pins     |      |                                                                                                     |  |  |

|-----------|------------------------------------|------|-----------------------------------------------------------------------------------------------------|--|--|

| Pin Name  | Pin                                | Туре | Description                                                                                         |  |  |

| RXIP[7:0] | 38, 30,<br>28, 20, 19,<br>11, 9, 1 | AI   | Receiver Input.<br>Differential positive signal shared by 100Base-TX, 100Base-FX, and 10Base-T.     |  |  |

| RXIN[7:0] | 37, 31, 27,<br>21, 18, 12, 8,<br>2 | AI   | Receiver Input.<br>Differential negative signal shared by 100Base-TX, 100Base-FX, and 10Base-T.     |  |  |

| TXOP[7:0] | 35, 33, 25,<br>23, 16, 14, 6,<br>4 | AO   | Transmitter Output.<br>Differential positive signal shared by 100Base-TX, 100Base-FX, and 10Base-T. |  |  |

| TXON[7:0] | 36, 32, 26,<br>22, 17, 13, 7,<br>3 | AO   | Transmitter Output.<br>Differential negative signal shared by 100Base-TX, 100Base-FX, and 10Base-T. |  |  |

### 5.1. Media Connection Pins

## 5.2. Power and Ground Pins

#### Table 3. Power and Ground Pins

| Pin Name | Pin              | Туре | Description                 |

|----------|------------------|------|-----------------------------|

| VDDA     | 10, 24, 34, 117, | AP   | 1.8V Power to analog.       |

|          | 118, 124, 128    |      |                             |

| VDDAH    | 127              | AP   | 3.3V Power to regulator.    |

| VSSA     | 5, 15, 29, 39,   | AG   | Analog ground.              |

|          | 40, 121, 123     |      |                             |

| VDD      | 60, 90           | DP   | 1.8V Power to digital core. |

| VDDO     | 46, 68, 103      | DP   | 3.3V Power to digital I/O.  |

| VSS      | 47, 61, 69, 89,  | DG   | Digital ground.             |

|          | 104              |      |                             |

# 5.3. Miscellaneous Pins

| Table 4. Miscellaneous Pins |     |      |                                                                                                               |  |

|-----------------------------|-----|------|---------------------------------------------------------------------------------------------------------------|--|

| Pin Name                    | Pin | Туре | Description                                                                                                   |  |

| RESET#                      | 51  | I,   | Reset.                                                                                                        |  |

|                             |     | (Pu) | This is an active low input. To complete the reset function, this pin must be asserted low for at least 10ms. |  |

| XI                          | 119 | Ι    | 25MHz Crystal input or 25MHz Oscillator clock input.                                                          |  |

|                             |     |      | The clock tolerance is $\pm 50$ ppm.                                                                          |  |

|                             |     |      | When XI is pulled low, XO must be floating. REFCLK will then be                                               |  |

|                             |     |      | the chip clock input.                                                                                         |  |

| XO                          | 120 | 0    | 25MHz Crystal output.                                                                                         |  |

| REFCLK                      | 52  | I/O  | Reference clock.                                                                                              |  |

|                             |     | (Pd) | If XI is 25MHz active, REFCLK is a 50MHz output.                                                              |  |

|                             |     |      | If XI is pulled-low (disabled), REFCLK is a clock input as described                                          |  |

|                             |     |      | below:                                                                                                        |  |

|                             |     |      | RMII mode = $50$ MHz $\pm 50$ ppm clock input                                                                 |  |

|                             |     |      | SMII/SS-SMII mode = $125$ MHz $\pm 50$ ppm clock input.                                                       |  |

|                             |     |      | Pin driver capacity = $8$ mA.                                                                                 |  |

| IBREF                       | 125 | AO   | Reference Bias Resistor.                                                                                      |  |

|                             |     |      | When using a 1:1 transformer on Tx/Rx, this pin must be tied to analog                                        |  |

|                             |     |      | ground through an external $2K\Omega$ resistor.                                                               |  |

| VCTRL                       | 126 | AO   | Voltage control.                                                                                              |  |

|                             |     |      | This pin controls a PNP transistor to generate the 1.8V power supply                                          |  |

|                             |     |      | for VDD and VDDA pins.                                                                                        |  |

| NC                          | 113 |      | Not Connected.                                                                                                |  |

## 5.4. RMII/SMII/SS-SMII Pins

|           |             | Table 5. | RMII/SMII/SS-SMII Pins                                                                                                                                                                                                    |

|-----------|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name  | Pin         | Туре     | Description                                                                                                                                                                                                               |

| TXD0[7:0] | 58, 66, 74, | Ι        | Transmit Data Input (bit 0).                                                                                                                                                                                              |

|           | 80, 87, 95, |          | RMII: TXD0 and TXD1 are the di-bits input, transmitted and driven                                                                                                                                                         |

|           | 101, 109    |          | synchronously to REFCLK from the MAC.                                                                                                                                                                                     |

|           |             |          | SMII: TXD0 inputs the data that is transmitted and is driven<br>synchronously to REFCLK. In 100Mbps, TXD0 inputs a new 10-bit<br>segment starting with SYNC. In 10Mbps, TXD0 must repeat each<br>10-bit segment 10 times. |

|           |             |          | SS-SMII: TXD0 behaves as SMII except synchronous to TX_CLK instead of REFCLK and inputs a new 10-bit segment starting with TX_SYNC instead of SYNC.                                                                       |

| TXD1[7:0] | 57, 65, 73, | Ι        | Transmit Data Input (bit 1).                                                                                                                                                                                              |

|           | 79, 86, 94, |          | RMII: TXD1 and TXD0 are the input di-bits synchronously to                                                                                                                                                                |

|           | 100, 108    |          | REFCLK.                                                                                                                                                                                                                   |

|           |             |          | SMII/SS-SMII: The I/O pin of TX_EN should not be used.                                                                                                                                                                    |

| Pin Name          | Pin         | Туре           | Description                                                                                 |

|-------------------|-------------|----------------|---------------------------------------------------------------------------------------------|

| TX_EN[7:0]        | 59, 67, 75, | Ι              | Transmit Enable.                                                                            |

| TX_CLK/TX_EN[4]   | 81, 88, 96, |                | RMII: TX_EN indicates the di-bits on TXD is valid and is                                    |

|                   | 102, 110    |                | synchronous to REFCLK.                                                                      |

|                   |             |                |                                                                                             |

|                   |             |                | SMII: The I/O pin of TX_EN should not be used.                                              |

|                   |             |                | SS-SMII: TX EN[4] of RMII is used as TX CLK, which is a                                     |

|                   |             |                | 125MHz clock input from MAC.                                                                |

|                   |             |                | The I/O pin of TX EN should not be used.                                                    |

| RXD0[7:0]         |             | 0              | Receive Data Input (bit 0).                                                                 |

|                   | 55          | (Pd)           | RMII: RXD0 and RXD1 output di-bits synchronously to REFCLK.                                 |

|                   | 63          | (Pd)           |                                                                                             |

|                   | 71          | (Pu)           | SMII: RXD0 outputs data or in-band management information                                   |

|                   | 77          | (Pd)           | synchronously to REFCLK. In 100Mbps, RXD0 outputs a new 10-                                 |

|                   | 84          | (Pu)           | bit segment starting with SYNC. In 10Mbps, RXD0 must repeat                                 |

|                   | 92          | (Pd)           | each 10-bit segment 10 times.                                                               |

|                   | 98          | (Pd)           |                                                                                             |

|                   | 106         | (Pd)           | SS-SMII: RXD0 behaves as SMII except synchronous to RX_CLK                                  |

|                   |             |                | instead of REFCLK and inputs a new 10-bit segment starting with                             |

|                   |             |                | RX_SYNC instead of SYNC.                                                                    |

| D.V.D.117.01      |             | -              | All pins driver capacity = 8mA                                                              |

| RXD1[7:0]         | <b>5</b> 4  | $(\mathbf{D})$ | Receive Data Input (bit 1).                                                                 |

|                   | 54          | (Pd)           | RMII: RXD1 and RXD0 output di-bits synchronously to REFCLK.                                 |

|                   | 62<br>70    | (Pd)<br>(Pd)   | SMII/SS-SMII: The I/O pin of RXD1 should not be used.                                       |

|                   | 70<br>76    | (Pd)<br>(Pd)   | All pins driver capacity = $8\text{mA}$                                                     |

|                   | 83          | (Pd)           | An phils driver capacity – oniA                                                             |

|                   | 91          | (Pd)           |                                                                                             |

|                   | 97          | (Pu)           |                                                                                             |

|                   | 105         | (Pd)           |                                                                                             |

| CRS DV[7:0]       |             | 0              | Carrier Sense and Data Valid.                                                               |

| RX SYNC/CRS DV[3] | 56          | (Pu)           | RMII: CRS DV is asynchronous to REFCLK and asserts when the                                 |

| RX_CLK/CRS_DV[4]  | 64          | (Pu)           | medium is non-idle.                                                                         |

|                   | 72          | (Pu)           | SMII: CRS_DV[7:0] are not used and driven low.                                              |

|                   | 78 (16mA)   | (ND)           | SS-SMII: CRS_DV[3] of RMII is used as RX_SYNC which is a                                    |

|                   | 85          | (Pu)           | sync signal used to delimit the 10-bit segment of RXD0 for all ports.                       |

|                   | 93          | (Pu)           | CRS_DV[4] of RMII is used as RX_CLK, which is a 125MHz clock                                |

|                   | 99<br>97    | (Pd)           | output. CRS_DV[7:5] and CRS_DV[2:0] are not used.                                           |

|                   | 07          | (Pd)           | All pins driver capacity = $8mA$ , except pin 78 (16mA).                                    |

| SYNC/             | 82          | l<br>(Fu)      | Sync/Transmit Synchronous.                                                                  |

| TX_SYNC           |             | (Pd)           | SMII: SYNC is a sync signal used to delimit a 10-bit segment of                             |

|                   |             |                | RXD0 and TXD0 for all ports.                                                                |

|                   |             |                | SS-SMII: TX_SYNC is a sync signal used to delimit the 10-bit segment of TXD0 for all ports. |

|                   |             |                | segment of TADO for all ports.                                                              |

# 5.5. SMI (Serial Management Interface)

|          | Table 6. SMI (Serial Management Interface) |              |                                                                                                                                                                                                                                                                                                                         |  |  |  |

|----------|--------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name | Pin                                        | Туре         | Description                                                                                                                                                                                                                                                                                                             |  |  |  |

| MDIO     | 111                                        | I/O,<br>(Pu) | Management Data I/O. Bi-directional data interface. A $1.5K\Omega$ pull-<br>up resistor is required (as specified in IEEE802.3u).<br>The MAC controller access of the MII registers should be delayed at<br>least 700µs after completion of the reset because of the internal reset<br>operation of the RTL8208B(F)-LF. |  |  |  |

| MDC      | 112                                        | I, (Pd)      | Pin driver capacity = 8mA.Management Data Clock. 0 to 2.5MHz clock sourced by MAC to<br>sample MDIO.The MAC controller access of the MII registers should be delayed at<br>least 700μs after completion of the reset because of the internal reset<br>operation of the RTL8208B(F)-LF.                                  |  |  |  |

#### Table 6. SMI (Serial Management Interface)

### 5.6. LED Pins

|                  |             | Table 7. LED Pins |                                                                            |  |  |  |  |

|------------------|-------------|-------------------|----------------------------------------------------------------------------|--|--|--|--|

| Pin Name         | Pin         | Туре              | Description                                                                |  |  |  |  |

| SCAN_LED[7:0]    | 41, 42, 43, | 0                 | In scan LED mode, SCAN_LED[7:0] is the Scan LED port enable.               |  |  |  |  |

|                  | 44, 45, 48, | (Pu)              | See section 7.9 LED Configuration, page 38.                                |  |  |  |  |

|                  | 49, 50      |                   | All pins driver capacity = $8mA$ .                                         |  |  |  |  |

| SCAN_STATUS[2:0] | 114, 115,   | 0                 | In scan LED mode, SCAN_STATUS[2:0] outputs (Col/Fulldup,                   |  |  |  |  |

|                  | 116         | (Pu)              | Link/Act, Spd) for each port.                                              |  |  |  |  |

| LED_CLK/SCAN_    |             |                   |                                                                            |  |  |  |  |

| STATUS[0]        |             |                   | In serial LED mode, SCAN_STATUS[0] is used as LED_CLK,                     |  |  |  |  |

|                  |             |                   | which outputs the reference clock for the serial LED signals.              |  |  |  |  |

| LED_DATA/SCAN_   |             |                   |                                                                            |  |  |  |  |

| STATUS[1]        |             |                   | In serial LED mode, SCAN_STATUS[1] is used as LED_DATA,                    |  |  |  |  |

|                  |             |                   | which outputs serial status bits that can be shifted into a shift register |  |  |  |  |

|                  |             |                   | to be displayed via LEDs. LED_DATA is output synchronously to              |  |  |  |  |

|                  |             |                   | LED_CLK.                                                                   |  |  |  |  |

|                  |             |                   | All pins driver capacity = $8mA$ .                                         |  |  |  |  |

Table 7. LED Pins

# 5.7. Mode Control Pins

|                | Table 8. Mode Control Pins |              |                                                                           |  |  |  |

|----------------|----------------------------|--------------|---------------------------------------------------------------------------|--|--|--|

| Pin Name       | Pin                        | Туре         | Description                                                               |  |  |  |

| SEL TXFX[1:0]/ | 99, 107                    | I/O,         | Select 10/100BaseTX or 100BaseFX (default = 2'b00).                       |  |  |  |

| CRS_DV[1:0]    |                            | (Pd, Pd)     | If PP-LPBK MODE = $0$ :                                                   |  |  |  |

|                |                            |              | 2'b00: All 8 ports (port0~port7) are 10Base-T/100Base-TX.                 |  |  |  |

|                |                            |              | 2'b01: Port 7 is 100FX, other ports are 10Base-T/100Base-TX.              |  |  |  |

|                |                            |              | 2'b10: Ports 6 & 7 are 100FX, other ports are 10Base-T/                   |  |  |  |

|                |                            |              | 100Base-TX.                                                               |  |  |  |

|                |                            |              | 2'b11: All 8 ports are 100Base-FX.                                        |  |  |  |

|                |                            |              | If PP-LPBK MODE =1:                                                       |  |  |  |

|                |                            |              | 2'b00: All 8 ports (port0~port7) are 10Base-T/100Base-TX.                 |  |  |  |

|                |                            |              | 2'b01: Port 7 and 5 are 100FX, others are 10Base-T/100Base-TX.            |  |  |  |

|                |                            |              | 2'b10: Ports 1, 3, 5 & 7 are 100FX, others are                            |  |  |  |

|                |                            |              | 10Base-T/100Base-TX.                                                      |  |  |  |

|                |                            |              | 2'b11: All 8 ports are 100Base-FX.<br>Note: RTL8208BF-LF only.            |  |  |  |

| PP-LPBK MODE/  | 105                        | I/O,         | Port-Pair Loopback mode (default =0).                                     |  |  |  |

| RXD1[0]        | 105                        | (Pd)         | Upon power-on reset, this pin is input to assert PP-LPBK MODE.            |  |  |  |

| KAD1[0]        |                            | (1 u)        | When set, all eight ports are port-pair looped back, acting like a signal |  |  |  |

|                |                            |              | regeneration/transformation repeater.                                     |  |  |  |

|                |                            |              | See section 7.1.2 Port Pair-Loop Back Mode (PP-LPBK), page 26,            |  |  |  |

|                |                            |              | covering PP-LPBK MODE.                                                    |  |  |  |

|                |                            |              | Note: RTL8208BF-LF only.                                                  |  |  |  |

| PHY ADDR[4:3]/ | 77, 84                     | I/O,         | PHY Address (default = $2$ 'b01).                                         |  |  |  |

| RXD0[4:3]      |                            | (Pd, Pu)     | These 2 bits determine the highest 2 bits of the 5-bit PHY address        |  |  |  |

|                |                            |              | upon reset.                                                               |  |  |  |

|                |                            |              | We recommend using a resistor to pull up or pull down.                    |  |  |  |

| MODE[1:0]/     | 64, 56                     | I/O, (Pu,Pu) | Select RMII/SMII/SS-SMII mode (default = 2'b11).                          |  |  |  |

| CRS_DV[6:7]    |                            |              | 2'b1x: RMII                                                               |  |  |  |

|                |                            |              | 2'b00: SMII                                                               |  |  |  |

|                |                            |              | 2'b01: SS-SMII                                                            |  |  |  |

|                |                            | T(0, (7, )   | We recommend using a resistor to pull up or pull down.                    |  |  |  |

| TP_PAUSE/      | 72                         | I/O, (Pu)    | Twisted Pair Pause capability (default =1).                               |  |  |  |

| CRS_DV[5]      |                            |              | Sets the Flow control ability of Reg.4.10 for UTP ports upon power-       |  |  |  |

|                |                            |              | on reset.                                                                 |  |  |  |

|                |                            |              | 1: With flow control ability<br>0: Without flow control ability           |  |  |  |

| FX PAUSE/      | 85                         | I/O, (Pu)    | 100Base-FX Flow control capability (default =1).                          |  |  |  |

| CRS DV[3]      | 85                         | 1/O, (Fu)    | Forces the flow control capability of Reg.4.10 and Reg.5.10 upon          |  |  |  |

|                |                            |              | power-on reset.                                                           |  |  |  |

|                |                            |              | 1: With flow control ability in 100Base-FX                                |  |  |  |

|                |                            |              | 0: Without flow control ability in 100Base-FX                             |  |  |  |

|                |                            |              | Note: RTL8208BF-LF only.                                                  |  |  |  |

| TP ASY PAUSE/  | 70                         | I/O, (Pd)    | Twisted Pair Asymmetric Pause capability (default =0).                    |  |  |  |

| RXD1[5]        |                            |              | Sets the Asymmetric Flow control ability of Reg.4.11 for UTP ports        |  |  |  |

|                |                            |              | upon power-on reset.                                                      |  |  |  |

|                |                            |              | 1: With asymmetric flow control ability                                   |  |  |  |

|                |                            |              | 0: Without asymmetric flow control ability.                               |  |  |  |

Single-Chip Octal 10/100-TX/FX PHY Transceiver

#### RTL8208B-LF/RTL8208BF-LF Datasheet

| Pin Name       | Pin    | Туре       | Description                                                               |

|----------------|--------|------------|---------------------------------------------------------------------------|

| FX ASY PAUSE/  | 76     | I/O, (Pd)  | 100Base-FX Asymmetric Flow control capability (default =0).               |

| RXD1[4]        |        |            | Forces the asymmetric flow control capability of Reg.4.11 and             |

|                |        |            | Reg.5.11 upon power-on reset.                                             |

|                |        |            | 1: Asymmetric flow control ability in 100Base-FX                          |

|                |        |            | 0: No asymmetric flow control ability in 100Base-FX                       |

|                |        |            | Note: RTL8208BF-LF only.                                                  |

| FX DUPLEX/     | 93     | I/O, (Pu)  | FX_DUPLEX: Force 100Base-FX Full Duplex Mode (default =1).                |

| CRS_DV[2]      |        | , ( )      | This pin sets 100Base-FX duplex and affects those ports in                |

|                |        |            | 100Base-FX mode.                                                          |

|                |        |            | 1: Full duplex                                                            |

|                |        |            | 0: Half duplex                                                            |

|                |        |            | Upon reset, this pin sets the default values of Reg.0.8 of those ports in |

|                |        |            | 100Base-FX.                                                               |

|                |        |            | Note: RTL8208BF-LF only.                                                  |

| EN AUTOXOVER/  | 97     | I/O, (Pu)  | Enable Auto Crossover Detection (default =1).                             |

| RXD1[1]        |        |            | 1: Enable auto crossover detection                                        |

|                |        |            | 0: Disable auto crossover detection                                       |

| DISBLINK/      | 91     | I/O, (Pd)  | Disable power-on/reset LED blinking: (default = $0$ )                     |

| RXD1[2]        | 71     | 1,0,(1,0)  | 1: Disable power-on LED blinking                                          |

|                |        |            | 0: Blink                                                                  |

| LED BLNK TIME/ | 71     | I/O, (Pu)  | LED Blink Time (default =1).                                              |

| RXD0[5]        | /1     | 1/0, (1 u) | Controls the blinking speed of activity and collision LEDs.               |

| KAD0[5]        |        |            | 1: 43ms (recommended to use external 10K pull up resistor)                |

|                |        |            | 0: 120ms                                                                  |

| LEDSEL/RXD1[3] | 83     | I/O, (Pd)  | LED Selection (default=1'b0).                                             |

| LEDSEL/KADI[5] | 85     | 1/O, (I U) | LED Selection (default=1 00).<br>LEDSEL                                   |

|                |        |            | 1'b1: Scan LED                                                            |

|                |        |            | 1'b0: Serial LED                                                          |

| LEDMODE[1:0]/  | 92, 98 | I/O,       | LEDMODE[1:0] (default = 00).                                              |

| RXD0[2:1]      | 92, 98 | (Pd, Pd)   | When using the RTL8208B(F)-LF LED solution, we recommend using            |

| KAD0[2.1]      |        | (1 u, 1 u) | an external resister to pull high or pull low.                            |

|                |        |            | In Serial LED, LEDMODE[1:0] controls the forms of serial LED status.      |

|                |        |            | LEDMODE Mode Output                                                       |

|                |        |            | 2'b00 3-bit serial stream Col/Fulldup, Link/Act, Spd                      |

|                |        |            | 2'b01 2-bit serial stream Spd, Link/Act                                   |

|                |        |            | 2'bl0 3-bit for Bi-color LED Col/Fulldup, Link/Act, Spd                   |

|                |        |            | 2'b11 1-bit serial stream Link/Act/Spd                                    |

|                |        |            | 2 011 1-0it serial stream Ellik/Act/Spd                                   |

|                |        |            | In Scan LED, LEDMODE[1:0] controls the output of                          |

|                |        |            | SCAN_STATUS[2:0].                                                         |

|                | 1      |            | LEDMODE Mode Output                                                       |

|                |        |            | 2'b00 Mode 0 Col/Fulldup, Link/Act, Spd                                   |

|                |        |            | 2'b01 Mode 1 RX, TX, Link                                                 |

|                |        |            | 2'b10 Mode 2 NC, Bi-color Link/Act/Spd, NC                                |

|                |        |            | 2'b11 Reserved                                                            |

| FRC PARA FULL/ | 63     | I/O        | Force full duplex when link is established by parallel detection          |

| RXD0[6]        | 05     | (Pd)       | (default=0).                                                              |

|                | 1      | (ru)       | 1: Force full duplex when link is established by parallel detection       |

|                |        |            | 0: Normal operation                                                       |

|                | 1      | l          |                                                                           |

#### RTL8208B-LF/RTL8208BF-LF Datasheet

| Pin Name        | Pin                   | Туре        | Description                                                                                                      |

|-----------------|-----------------------|-------------|------------------------------------------------------------------------------------------------------------------|

| SEL_RXC/RXD1[7] | 54                    | I/O<br>(Pd) | In SMII, SEL_RXC control the clock to output delay of RXD.<br>0: Clock out data on falling edge of receive clock |

|                 |                       | (1 4)       | 1: Clock out data on rising edge of receive clock                                                                |

|                 |                       |             | Recommended to set SEL_RXC=1.                                                                                    |

|                 |                       |             | In SS-SMII, SEL_RXC, must be set to 1.                                                                           |

| SEL_TXC/RXD0[7] | SEL_TXC/RXD0[7] 55 I/ |             | In SMII, SEL_TXC control the clock to output delay of TXD.                                                       |

|                 |                       | (Pd)        | 0: Clock out data on falling edge of transmit clock                                                              |

|                 |                       |             | 1: Clock out data on rising edge of transmit clock                                                               |

|                 |                       |             | Recommended to set SEL_TXC=1.                                                                                    |

|                 |                       |             | In SS-SMII, SEL_TXC, must be set to 1.                                                                           |

### 5.8. Test Pins

| Table 9. Test Pins |     |      |                                             |  |

|--------------------|-----|------|---------------------------------------------|--|

| Pin Name           | Pin | Туре | Description                                 |  |

| ENANAPAR/          | 106 | I/O, | Enable analog parameter write (default =0). |  |

| RXD0[0]            |     | (Pd) | 1: Enable analog parameter write operation  |  |

|                    |     |      | 0: Disable analog parameter write operation |  |

| CPRST              | 53  | I,   | Reserved for internal use.                  |  |

|                    |     | (Pd) | Must be left floating.                      |  |

| DTEST1             | 122 | I/O  | Reserved for internal use.                  |  |

|                    |     |      | Must be left floating.                      |  |

#### **Register Descriptions 6**.

The first six registers of the MII are defined by the MII specification. Other registers are defined by Realtek for internal use.

Signal type codes below are used in the following tables:

- RO: Read Only LL:

- Read/Write RW:

- SC: Self Clearing

Latch Low until cleared

LH: Latch High until cleared

**Table 10. Register Descriptions**

| Register | Description                                     |

|----------|-------------------------------------------------|

| 0        | Control Register.                               |

| 1        | Status Register.                                |

| 2        | PHY Identifier 1 Register.                      |

| 3        | PHY Identifier 2 Register.                      |

| 4        | Auto-Negotiation Advertisement Register.        |

| 5        | Auto-Negotiation Link Partner Ability Register. |

| 6        | Auto-Negotiation Expansion Register.            |

# 6.1. Register0: Control

#### Table 11. Register0: Control

| Reg. bit | Name                        | Description                                                                                                                                                                   | Туре  | Default               |

|----------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------|

| 0.15     | Reset                       | 1: PHY reset. This bit is self-clearing.                                                                                                                                      | RW/SC | 0                     |

| 0.14     | Loopback                    | This will loopback TXD to RXD and ignore all activity on<br>the cable media.<br>1: Enable loopback<br>0: Normal operation                                                     | RW    | 0                     |

| 0.13     | Spd_Sel                     | When NWay is enabled, this bit reflects the auto negotiation result (Read Only).                                                                                              | RW    | 0                     |

|          |                             | When NWay is disabled, this bit can be set by SMI*. (Read/Write).                                                                                                             |       |                       |

|          |                             | When 100FX is enabled, this bit =1 (Read Only).<br>1: 100Mbps<br>0: 10Mbps                                                                                                    |       |                       |

| 0.12     | Auto Negotiation<br>Enable  | This bit can be set through SMI (Read/Write).<br>When 100FX is enabled, this bit =0 (Read only).<br>1: Enable auto negotiation process<br>0: Disable auto negotiation process | RW    | 1<br>(0 for<br>100FX) |

| 0.11     | Power Down                  | 1: Power down. All functions will be disabled except SMI<br>read/write function<br>0: Normal operation                                                                        | RW    | 0                     |

| 0.10     | Isolate                     | 1: Electrically isolate the PHY from RMII/SMII/SS-SMII.<br>PHY is still able to respond to MDC/MDIO<br>0: Normal operation                                                    | RW    | 0                     |