# CMOS ST-BUS™ FAMILY MT9079

**Features**

- Meets applicable requirements of CCITT G.704, G.706, G.732, G.775, G.796, I.431 and ETSI ETS 300 011

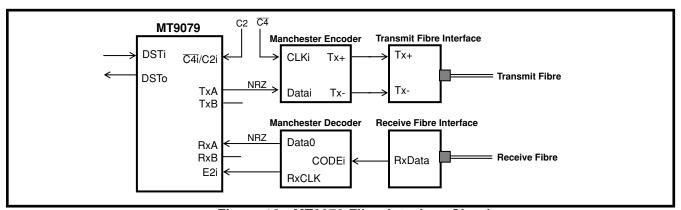

- HDB3, RZ, NRZ (fibre interface) and bipolar NRZ line codes

- Data link access and national bit buffers (five bytes each)

- Enhanced alarms, performance monitoring and error insertion

- Maskable interrupts for alarms, receive CAS bit changes, exception conditions and counter overflows

- Automatic interworking between CRC-4 and non-CRC-4 multiframing

- Dual transmit and receive 16 byte circular channel buffers

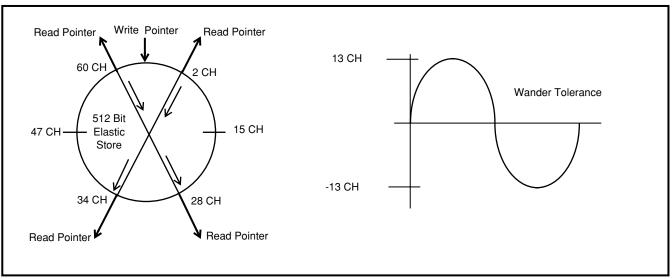

- Two frame receive elastic buffer with controlled slip direction indication and 26 channel hysteresis (208 UI wander tolerance)

- CRC-4 updating algorithm for intermediate path points of a message-based data link application

## **Applications**

- Primary rate ISDN network nodes

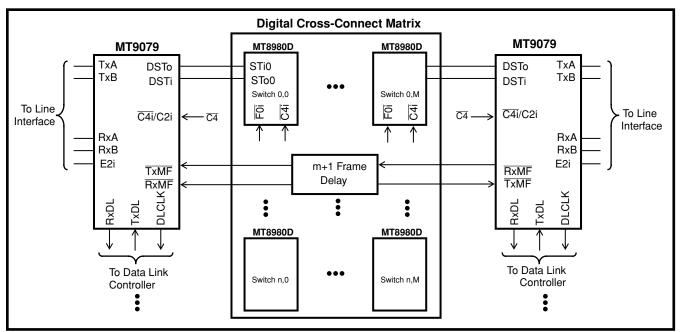

- Digital Access Cross-connect (DACs)

- CO and PABX switching equipment interfaces

- E1 add/drop multiplexers and channel banks

- · Test equipment and satellite interfaces

ISSUE 5 March 1997

### **Ordering Information**

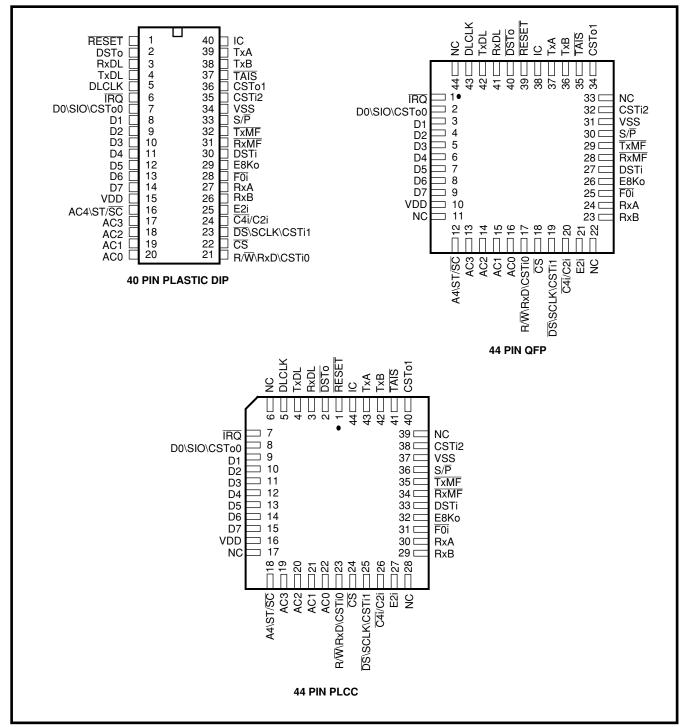

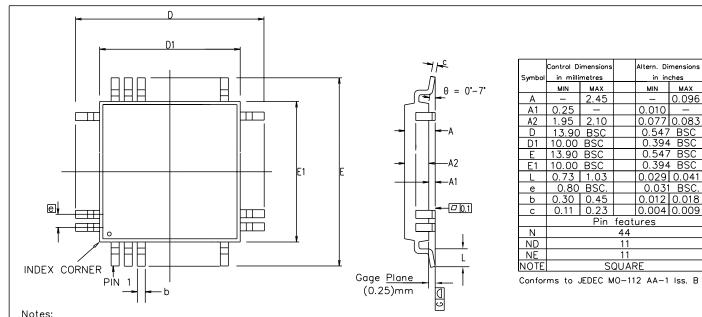

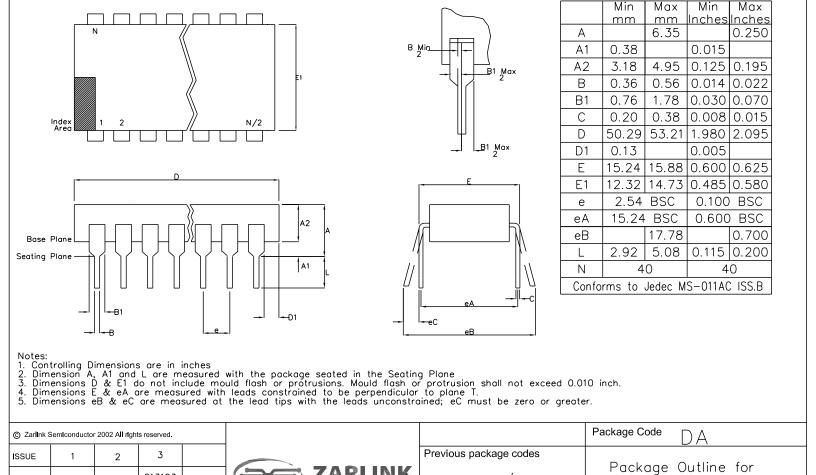

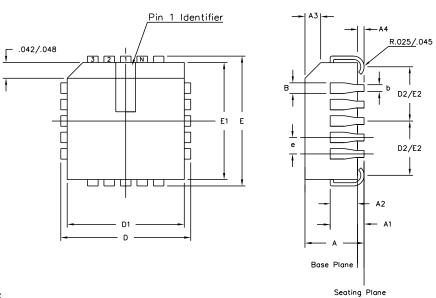

MT9079AE 40 Pin Plastic DIP MT9079AL 44 Pin QFP MT9079AP 44 Pin PLCC -40° to 85°C

### Description

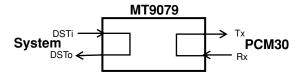

The MT9079 is a feature rich E1 (PCM 30, 2.048 Mbps) link framer and controller that meets the latest CCITT and ETSI requirements.

The MT9079 will interface to a 2.048 Mbps backplane and can be controlled directly by a parallel processor, serial controller or through the ST-BUS.

Extensive alarm transmission and reporting, as well as exhaustive performance monitoring and error diagnostic features make this device ideal for a wide variety of applications.

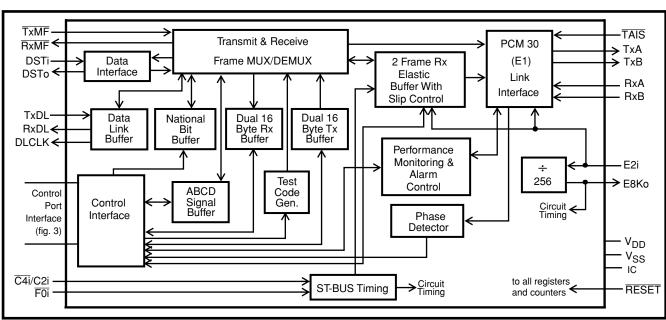

Figure 1 - Functional Block Diagram

Figure 2 - Pin Connection

# **Pin Description**

|           | Pin #     |           |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------|-----------|-----------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIP       | PLCC      | QFP       | Name                        | Description (see notes 1, 2 and 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1         | 1         | 39        | RESET                       | RESET (Input): Low - maintains the device in a reset condition. High - normal operation. The MT9079 should be reset after power-up. The time constant for a power-up reset circuit (see Figure 11) must be a minimum of five times the rise time of the power supply. In normal operation, the RESET pin must be held low for a minimum of 100 nsec. to reset the device.                                                                                                                                                |

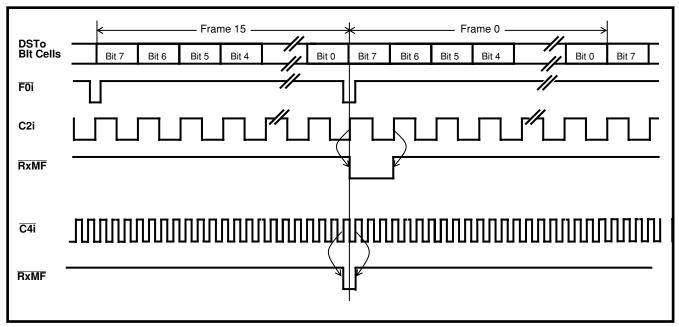

| 2         | 2         | 40        | DSTo                        | Data ST-BUS (Output): A 2.048 Mbit/s serial output stream which contains the 30 PCM or data channels received from the PCM 30 line. See Figure 4b.                                                                                                                                                                                                                                                                                                                                                                       |

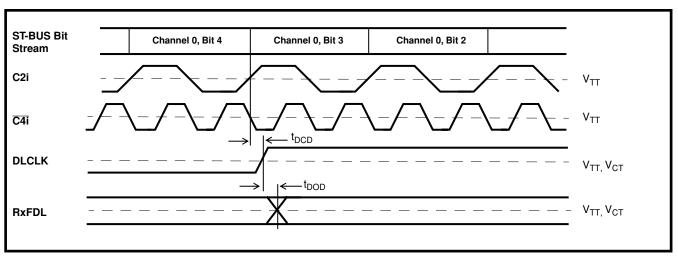

| 3         | 3         | 41        | RxDL                        | Receive Data Link (Output): A 4 kbit/s serial stream which is demultiplexed from a selected national bit (non-frame alignment signal) of the PCM 30 receive signal. Received DL data is clocked out on the rising edge of DLCLK, see Figure 20.                                                                                                                                                                                                                                                                          |

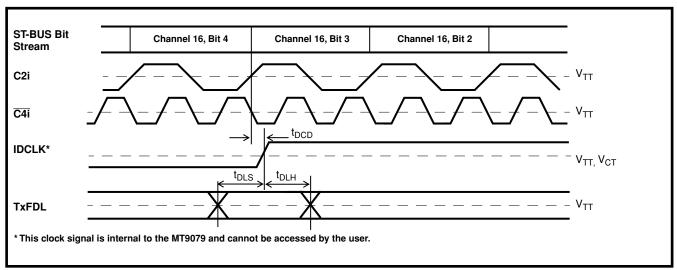

| 4         | 4         | 42        | TxDL                        | <b>Transmit Data Link (Input)</b> : A 4 kbit/s serial stream which is multiplexed into a selected national bit (non-frame alignment signal) of the PCM 30 transmit signal. Transmit DL data is clocked in on the rising edge of internal clock IDCLK, see Figure 21.                                                                                                                                                                                                                                                     |

| 5         | 5         | 43        | DLCLK                       | <b>Data Link Clock (Output)</b> : A 4 kHz clock signal used to clock out DL data (RxDL) on its rising edge. It can also be used to clock DL data in and out of external serial controllers (i.e., MT8952). See TxDL and RxDL pin descriptions.                                                                                                                                                                                                                                                                           |

| -         | 6         | 44        | NC                          | No Connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6         | 7         | 1         | ĪRQ                         | Interrupt Request (Output): Low - interrupt request. High - no interrupt request. $\overline{\text{IRQ}}$ is an open drain output that should be connected to $V_{DD}$ through a pull-up resistor. An active $\overline{\text{CS}}$ signal is not required for this pin to function. This pin should be left open when the ST-BUS control port is selected.                                                                                                                                                              |

| 7         | 8         | 2         | D0<br>[P]                   | Data 0 (Three-state I/O): The least significant bit of the bidirectional data bus of the parallel processor interface.                                                                                                                                                                                                                                                                                                                                                                                                   |

|           |           |           | SIO<br>[S]                  | Serial Input/Output (Three state I/O): This pin function is used in serial controller mode and can be configured as control data input/output for Intel operation (connect to controller pin RxD). Input data is sampled LSB first on the rising edge of SCLK; data is output LSB first on the falling edge of SCLK. It can also be configured as the control data output for Motorola and National Microwire operation (data output MSB first on the falling edge of SCLK). See $\overline{\text{CS}}$ pin description. |

|           |           |           | CSTo0<br>[ST]               | Control ST-BUS Zero (Output): A 2.048 Mbit/s serial status stream which provides device status, performance monitoring, alarm status and phase status data.                                                                                                                                                                                                                                                                                                                                                              |

| 8-14      | 9-15      | 3-9       | D1-D7<br>[P]                | Data 1 to Data 7 (Three-state I/O): These signals, combined with D0, form the bidirectional data bus of the parallel processor interface (D7 is the most significant bit).                                                                                                                                                                                                                                                                                                                                               |

| 15        | 16        | 10        | $V_{DD}$                    | Positive Power Supply (Input): +5V ± 10%.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | 17        | 11        | NC                          | No Connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 16        | 18        | 12        | AC4<br>[P]                  | Address/Control 4 (Input): The most significant address and control input for the non-multiplexed parallel processor interface.                                                                                                                                                                                                                                                                                                                                                                                          |

|           |           |           | ST/ <del>SC</del><br>[ST S] | ST-BUS/Serial Controller (Input): High - selects ST-BUS mode of operation.  Low - selects serial controller mode of operation.                                                                                                                                                                                                                                                                                                                                                                                           |

| 17-<br>20 | 19-<br>22 | 13-<br>16 | AC3-AC<br>0<br>[P]          | Address/Control 3 to 0 (Inputs): Address and control inputs for the non-multiplexed parallel processor interface. AC0 is the least significant input.                                                                                                                                                                                                                                                                                                                                                                    |

# Pin Description (Continued)

|     | Pin # |     | Name          | Description (see notes 1, 2 and 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|-------|-----|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIP | PLCC  | QFP | Ivaille       | Description (see notes 1, 2 and 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 21  | 23    | 17  | R/W<br>[P]    | <b>Read/Write (Input):</b> High - the parallel processor is reading data from the MT9079. Low - the parallel processor is writing data to the MT9079.                                                                                                                                                                                                                                                                                                                                           |

|     |       |     | RxD<br>[S]    | Receive Data (Input): This pin function is used in Motorola and National Microwire serial controller mode. Data is sampled on the rising edge of SCLK, MSB first. See $\overline{\text{CS}}$ pin description.                                                                                                                                                                                                                                                                                   |

|     |       |     | CSTi0<br>[ST] | Control ST-BUS Zero (Input): A 2.048 Mbit/s serial control stream which contains the device control, mode selection, and performance monitoring control.                                                                                                                                                                                                                                                                                                                                        |

| 22  | 24    | 18  | CS<br>[SP]    | Chip Select (Input): Low - selects the MT9079 parallel processor or serial controller interface. High - the parallel processor or serial controller interface is idle and all bus I/O pins will be in a high impedance state. When controller mode is selected, the SCLK input is sampled when $\overline{\text{CS}}$ is brought low. If SCLK is high the device in is Intel mode; if SCLK is low it will be in Motorola/National Microwire mode. This pin has no function (NC) in ST-BUS mode. |

| 23  | 25    | 19  | DS<br>[P]     | Data Strobe (Input): This input is the active low data strobe of the parallel processor interface.                                                                                                                                                                                                                                                                                                                                                                                              |

|     |       |     | SCLK<br>[S]   | Serial Clock (Input): This is used in serial controller mode to clock serial data in and out of the MT9079 on RxD and SIO. If SCLK is high when $\overline{CS}$ goes low, the device will be in Intel mode; if SCLK is low when $\overline{CS}$ goes low, it will be in Motorola/National Microwire mode.                                                                                                                                                                                       |

|     |       |     | CSTi1<br>[ST] | Control ST-BUS One (Input): A 2.048 Mbit/s serial control stream which contains the per timeslot control programming.                                                                                                                                                                                                                                                                                                                                                                           |

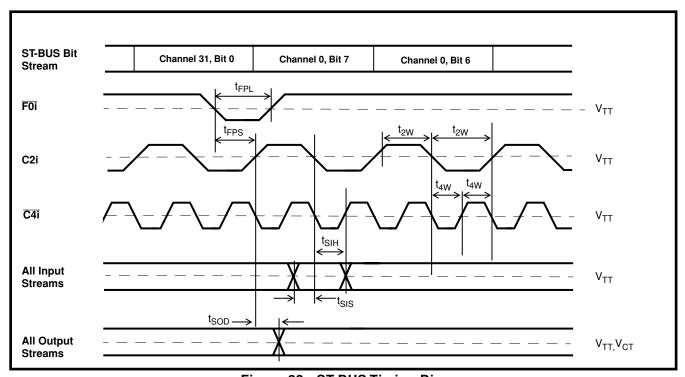

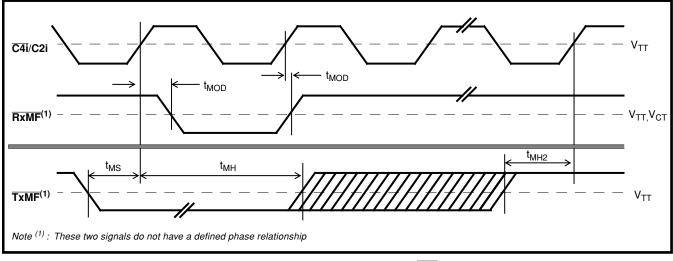

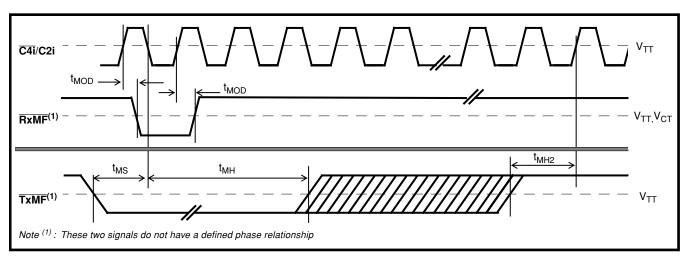

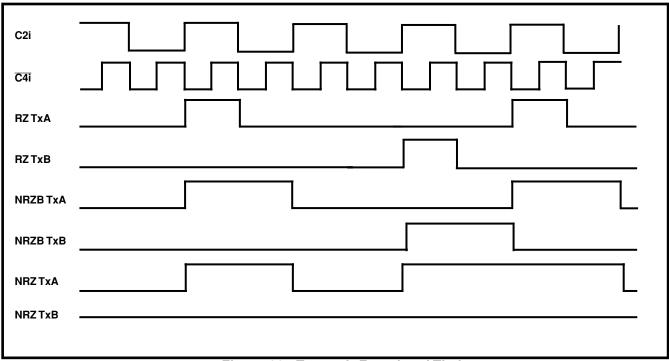

| 24  | 26    | 20  | C4i/C2i       | <b>4.096 MHz and 2.048 MHz System Clock (Input):</b> This is master clock for the serial PCM data and ST-BUS sections of the MT9079. The MT9079 automatically detects whether a 4.096 or 2.048 MHz clock is being used. See Figure 22 for timing information.                                                                                                                                                                                                                                   |

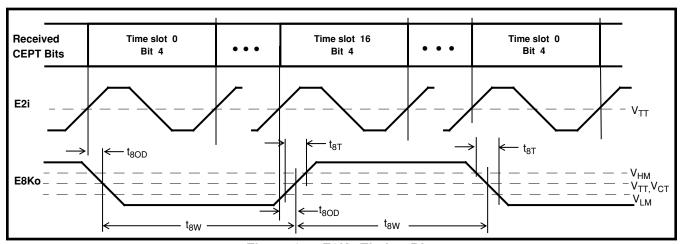

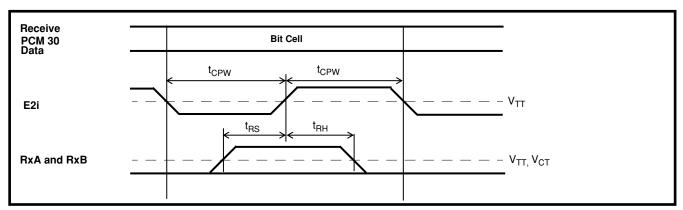

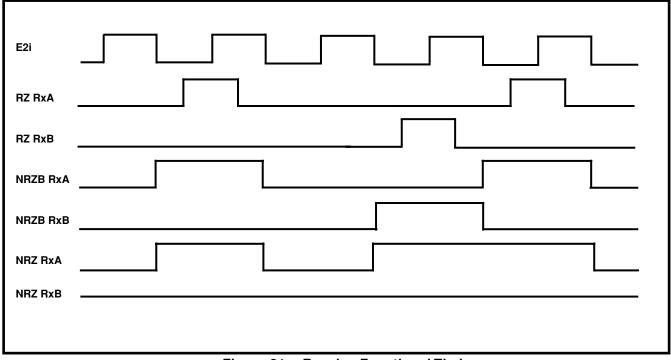

| 25  | 27    | 21  | E2i           | <b>2.048 MHz Extracted Clock (Input):</b> This clock is extracted from the received signal. Its rising edge is used internally to clock in data received on RxA and RxB. See Figure 29.                                                                                                                                                                                                                                                                                                         |

| -   | 28    | 22  | NC            | No Connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 26  | 29    | 23  | RxB           | Receive B (Input): Received split phase unipolar signal decoded from a bipolar line receiver. Receives RZ and NRZ bipolar signals. See Figures 29 and 31.                                                                                                                                                                                                                                                                                                                                       |

| 27  | 30    | 24  | RxA           | Receive A (Input): Received split phase unipolar signal decoded from a bipolar line receiver. Receives RZ and NRZ bipolar signals. See Figurs 29 and 31.                                                                                                                                                                                                                                                                                                                                        |

| 28  | 31    | 25  | F0i           | <b>Frame Pulse (Input):</b> This is the ST-BUS frame synchronization signal which delimits the 32 channel frame of all ST-BUS streams, as well as DSTi and DSTo in all modes.                                                                                                                                                                                                                                                                                                                   |

| 29  | 32    | 26  | E8Ko          | <b>Extracted 8 kHz Clock (Output):</b> An 8 kHz signal generated by dividing the extracted 2.048 MHz clock (E2i) by 256 and aligning it with the received PCM 30 frame. The 8 kHz signal can be used to synchronize the system clock with the extracted 2.048 MHz clock. E8Ko is high when 8KSEL=0. See Figure 27.                                                                                                                                                                              |

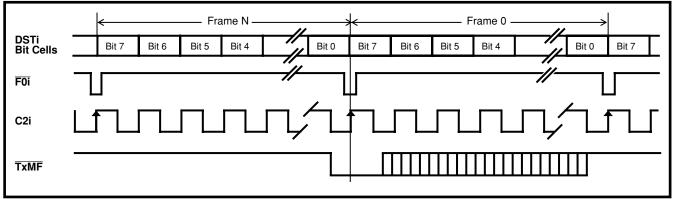

| 30  | 33    | 27  | DSTi          | Data ST-BUS (Input). A 2.048 Mbit/s serial stream which contains the 30 PCM or data channels to be transmitted on the PCM 30 line. See Figure 4a.                                                                                                                                                                                                                                                                                                                                               |

# **Pin Description (Continued)**

|     | Pin # |     | Name            | Description (see notes 1, 2 and 3)                                                                                                                                                                                                                                                                                                                             |

|-----|-------|-----|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIP | PLCC  | QFP |                 | , _ a.i.a. o,                                                                                                                                                                                                                                                                                                                                                  |

| 31  | 34    | 28  | RxMF            | Receive Multiframe Boundary (Output): An output pulse delimiting the received multiframe boundary. The next frame output on the data stream (DSTo) is basic frame zero on the PCM 30 link. This receive multiframe signal can be related to either the receive CRC multiframe (MFSEL=1) or the receive signalling multiframe (MFSEL=0). See Figures 25 and 26. |

| 32  | 35    | 29  | TxMF            | <b>Transmit Multiframe Boundary (Input):</b> This input is used to set the channel associated and CRC transmit multiframe boundary. The device will generate its own multiframe if this pin is held high. This input is pulled high in most applications. See Figures 24 to 26.                                                                                |

| 33  | 36    | 30  | S/P             | Serial/Parallel (Input): High - serial controller port or ST-BUS operation.  Low - parallel processor port operation.                                                                                                                                                                                                                                          |

| 34  | 37    | 31  | V <sub>SS</sub> | Negative Power Supply (Input): Ground.                                                                                                                                                                                                                                                                                                                         |

| 35  | 38    | 32  | CSTi2           | Control ST-BUS Input Two (Input): A 2.048 Mbit/s ST-BUS control stream which contains the 30 (ABCDXXXX) transmit signalling nibbles when RPSIG=0. When RPSIG=1 this pin has no function. Only the most significant nibbles of each ST-BUS timeslot are valid. See Figure 4c.                                                                                   |

| -   | 39    | 33  | NC              | No Connection.                                                                                                                                                                                                                                                                                                                                                 |

| 36  | 40    | 34  | CSTo1           | Control ST-BUS Output One (Output): A 2.048 Mbit/s serial status stream which provides the 30 (ABCDABCD) receive signalling nibbles. See Tables 15 - 17.                                                                                                                                                                                                       |

| 37  | 41    | 35  | TAIS            | <b>Transmit Alarm Indication Signal (Input):</b> High - TxA and TxB will transmit data normally. Low - TxA and TxB transmits an AIS (all ones signal).                                                                                                                                                                                                         |

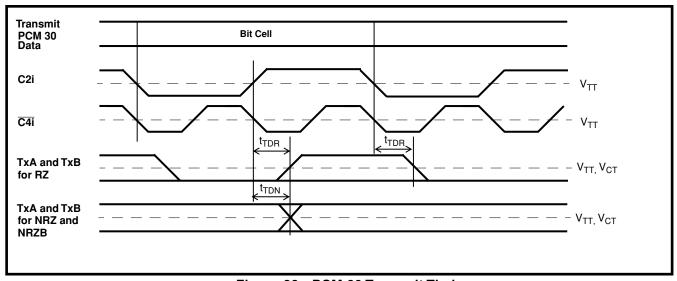

| 38  | 42    | 36  | ТхВ             | <b>Transmit B (Output):</b> A split phase unipolar signal suitable for use with TxA, an external line driver and a transformer to construct a bipolar PCM 30 line signal. This output can also transmit RZ and NRZ bipolar signals. See Figures 28 and 30.                                                                                                     |

| 39  | 43    | 37  | TxA             | <b>Transmit A (Output):</b> A split phase unipolar signal suitable for use with TxB, an external line driver and a transformer to construct a bipolar PCM 30 line signal. This output can also transmit RZ and NRZ bipolar signals. See Figures 28 and 30.                                                                                                     |

| 40  | 44    | 38  | IC              | Internal Connection (Input): Connect to ground for normal operation.                                                                                                                                                                                                                                                                                           |

#### Notes:

- 1. All inputs are CMOS with TTL compatible logic levels.

- 2. All outputs are CMOS and are compatible with both TTL and CMOS logic levels.

- 3. See AC Electrical Characteristics Timing Parameter Measurement Voltage Levels for input and output voltage thresholds.

#### **Functional Description**

The MT9079 is an advanced PCM 30 framer that meets or supports the layer 1 CCITT Recommendations of G.703, G.704, G.706, G.775, G.796 and G.732 for PCM 30; I.431 for ISDN Primary Rate; and T1.102 for DS1A. It also meets or supports the layer 1 requirements of ETSI ETS 300 011 and ETS 300 233. Included are all the features of the MT8979, except for the digital attenuation ROM and Alternate Digit Inversion (ADI). It also provides extensive performance monitoring data collection features.

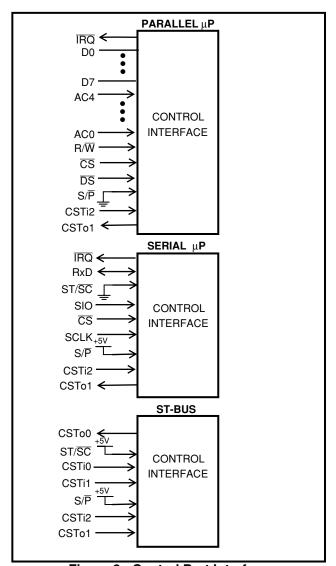

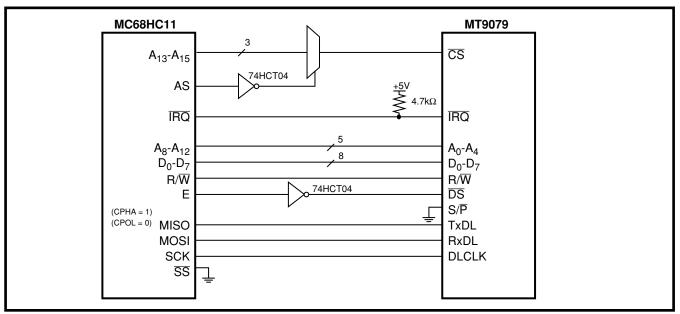

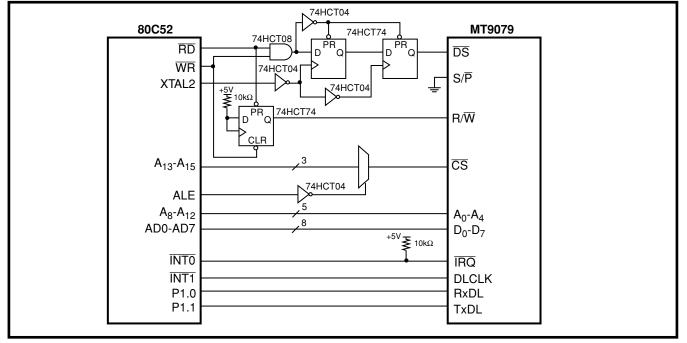

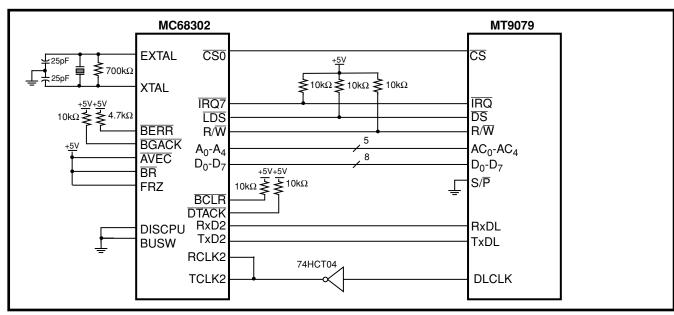

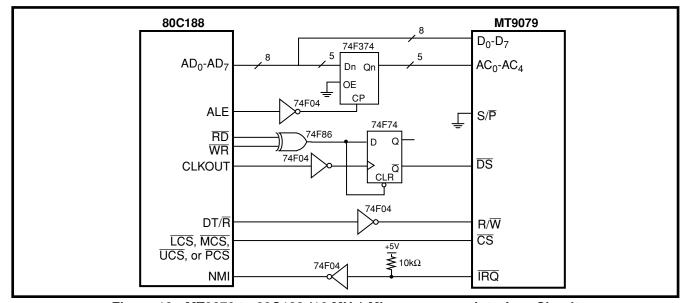

Control of the MT9079 is achieved through the hardware selection of either a parallel non-multiplexed microprocessor port, an Intel or Motorola serial controller port, or an ST-BUS port. The parallel port is based on the signals used by Motorola microprocessors, but it can also be easily mated to Intel microprocessors (see the Applications section of this data sheet).

The serial microcontroller interface of the MT9079 will automatically adapt to either Intel or Motorola signalling. An ST-BUS interface, consisting of two control and one status stream, may also be selected, however, the circular and national bit buffers cannot be accessed in this mode.

The MT9079 supports enhanced features of the MT8979. The receive slip buffer hysteresis has been extended to 26 channels, which is suitable for multiple trunk applications where large amounts of wander tolerance is required. The phase status word has been extended to the one sixteenth bit when the device is clocked with  $\overline{C4}$ . This provides the resolution required for high performance phase locked loops.

The received CAS (Channel Associated Signalling) bits are frozen when signalling multiframe synchronization is lost, and the CAS debounce duration has been extended to be compliant with CCITT Q.422.

The MT9079 framing algorithm has been enhanced to allow automatic interworking between CRC-4 and non-CRC-4 interfaces. Automatic basic frame alarm and multiframe alarms have also been added.

The national bits of the MT9079 can be accessed in three ways. First, through single byte registers; second, through five byte transmit and receive national bit buffers; and third, through the data link pins TxDL, RxDL and DLCLK.

A new feature is the ability to select transparent or termination modes of operation. In termination mode the CRC-4 calculation is performed as part of the framing algorithm. In transparent mode the MT9079 allows the data link maintenance channel to be modified and updates the CRC-4 remainder bits to reflect this new data. All channel, framing and signalling data passes through the device unaltered. This is useful for intermediate point applications of an PCM 30 link where the data link data is modified, but the error information transported by the CRC-4 bits must be passed to the terminating end. See the Application section of this data sheet.

The MT9079 has a comprehensive suite of status, alarm, performance monitoring and reporting features. These include counters for BPVs, CRC errors, E-bit errors, errored frame alignment signals, BERT, and RAI and continuous CRC errors. Also, included are transmission error insertion for BPVs, CRC-4 errors, frame and non-frame alignment signal errors, and loss of signal errors.

Dual transmit and receive 16 byte circular buffers, as well as line code insertion and detection features have been implemented and can be associated with any PCM 30 time slot.

A complete set of loopbacks has been implemented, which include digital, remote, ST-BUS, payload, and local and remote time slot.

The functionality of the MT9079 has been heighten with the addition of a comprehensive set of maskable interrupts and an interrupt vector function. Interrupt sources consist of synchronization status, alarm status, counter indication and overflow, timer status, slip indication, maintenance functions and receive channel associated signalling bit changes.

#### The PCM 30 Interface

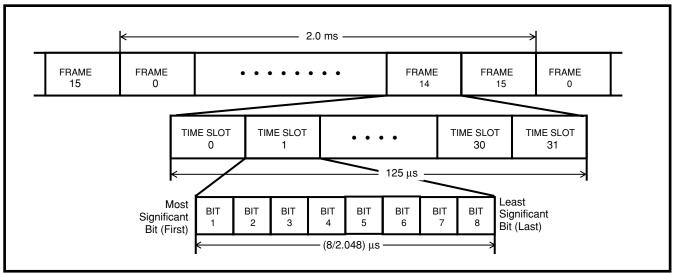

PCM 30 (E1) basic frames are 256 bits long and are transmitted at a frame repetition rate of 8000 Hz, which results in a aggregate bit rate of 256 bits x 8000/sec.= 2.048 Mbits/sec. The actual bit rate is 2.048 Mbits/sec +/- 50 ppm encoded in HDB3 format. Basic frames are divided into 32 time slots numbered 0 to 31, see Figure 32. Each time slot is 8 bits in length and is transmitted most significant bit first (numbered bit 1). This results in a single time slot data rate of 8 bits x 8000/sec. = 64 kbits/sec.

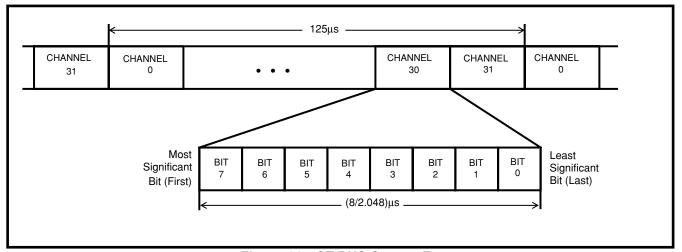

It should be noted that the Zarlink ST-BUS also has 32 channels numbered 0 to 31, but the most significant bit of an eight bit channel is numbered bit 7 (see Zarlink Application Note MSAN-126).

Therefore, ST-BUS bit 7 is synonymous with PCM 30 bit 1; bit 6 with bit 2: and so on. See Figure 33.

PCM 30 time slot zero is reserved for basic frame alignment, CRC-4 multiframe alignment and the communication of maintenance information. In most configurations time slot 16 is reserved for either channel associated signalling (CAS or ABCD bit signalling) or common channel signalling (CCS). The remaining 30 time slots are called channels and carry either PCM encoded voice frequency signals or digital data signals. Channel alignment and bit numbering is consistent with time slot alignment and bit numbering. However, channels are numbered 1 to 30 and relate to time slots as per Table 1.

| PCM 30<br>Timeslots    | 0 | 1 2 315 | 16 | 17 18 1931 |

|------------------------|---|---------|----|------------|

| Voice/Data<br>Channels | Х | 1 2 315 | Х  | 16 17 1830 |

Table 1 - Time slot to Channel Relationship

#### **Basic Frame Alignment**

Time slot zero of every basic frame is reserved for basic frame alignment and contains either a Frame Alignment Signal (FAS) or a Non-frame Alignment Signal (NFAS). FAS and NFAS occur in time slot zero of consecutive basic frames as can be see in Table 4. Bit two is used to distinguish between a FAS (bit two = 0) and a NFAS (bit two = 1).

Basic frame alignment is initiated by a search for the bit sequence 0011011 which appears in the last seven bit positions of the FAS, see Frame Algorithm section. Bit position one of the FAS can be either a CRC-4 remainder bit or an international usage bit.

Bits four to eight of the NFAS (i.e.,  $S_{a4}$  -  $S_{a8}$ ) are national bits, which telephone authorities used to communicate maintenance, control and status information. A single national bit can also be used as a 4 KHz maintenance channel or data link. Bit three, the ALM bit, is used to indicate the near end basic frame synchronization status to the far end of a link. Bit position one of the NFAS can be either a CRC-4 multiframe alignment signal, an E-bit or an international usage bit. Refer to an approvals laboratory and national standards bodies for specific requirements.

#### **CRC-4 Multiframing**

The primary purpose for CRC-4 multiframing is to provide a verification of the current basic frame alignment, although it can be used for other functions

such as bit error rate estimation. The CRC-4 multiframe consists of 16 basic frames numbered 0 to 15, and has a repetition rate of 16 frames X 125 microseconds/frame = 2 msec. CRC-4 multiframe alignment is based on the 001011 bit sequence, which appears in bit position one of the first six NFASs of a CRC-4 multiframe.

The CRC-4 multiframe is divided into two submultiframes, numbered 1 and 2, which are each eight basic frames or 2048 bits in length.

The CRC-4 frame alignment verification functions as follows. Initially, the CRC-4 operation must be activated and CRC-4 multiframe alignment must be achieved at both ends of the link. At the local end of a link all the bits of every transmit submultiframe are passed through a CRC-4 polynomial (multiplied by  $X^4$  then divided by  $X^4 + X + 1$ ), which generates a four bit remainder. This remainder is inserted in bit position one of the four FASs of the following submultiframe before it is transmitted, see Table 4. The submultiframe is then transmitted and at the far end the same process occurs. That is, a CRC-4 remainder is generated for each submultiframe. These bits are compared with the bits received in position one of the four FASs of the next received submultiframe. This process takes place in both directions of transmission.

When more than 914 CRC-4 errors (out of a possible 1000) are counted in a one second interval, the framing algorithm will force a search for a new basic frame alignment. See Frame Algorithm section for more details.

The result of the comparison of the received CRC-4 remainder with the locally generated remainder will be transported to the near end by the E-bits. Therefore, if  $E_1 = 0$ , a CRC-4 error was discovered in a submultiframe one received at the far end; and if  $E_2 = 0$ , a CRC-4 error was discovered in a submultiframe two received at the far end. No submultiframe sequence numbers or re-transmission capabilities are supported with layer 1 PCM 30 protocol. See CCITT G.704 and G.706 for more details on the operation of CRC-4 and E-bits.

#### **CAS Signalling Multiframing**

The purpose of the signalling multiframing algorithm is to provide a scheme that will allow the association of a specific ABCD signalling nibble with the appropriate PCM 30 channel. Time slot 16 is reserved for the communication of Channel Associated Signalling (CAS) information (i.e., ABCD signalling bits for up to 30 channels). Refer to CCITT

G.704 and G.732 for more details on CAS mutliframing requirements.

A CAS signalling multiframe consists of 16 basic frames (numbered 0 to 15), which results in a multiframe repetition rate of 2 msec. It should be noted that the boundaries of the signalling multiframe may be completely distinct from those of the CRC-4 multiframe. CAS multiframe alignment is based on a multiframe alignment signal (a 0000 bit sequence), which occurs in the most significant nibble of time slot 16 of basic frame zero of the CAS multiframe. Bit 6 of this time slot is the multiframe alarm bit (usually designated Y). When CAS multiframing is acquired on the receive side, the transmit Y-bit is zero; when CAS multiframing is not acquired, the transmit Y-bit is one. Bits 5, 7 and 8 (usually designated X) are spare bits and are normally set to one if not used.

Time slot 16 of the remaining 15 basic frames of the CAS multiframe (i.e., basic frames 1 to 15) are reserved for the ABCD signalling bits for the 30 payload channels. The most significant nibbles are the reserved for channels 1 to 15 and the least significant nibbles are reserved for channels 16 to 30. That is, time slot 16 of basic frame 1 has ABCD for channel 1 and 16, time slot 16 of basic frame 2 has ABCD for channel 2 and 17, through to time slot 16 of basic frame 15 has ABCD for channel 15 and 30.

#### MT9079 Access and Control

#### The Control Port Interface

The control and status of the MT9079 is achieved through one of three generic interfaces, which are parallel microprocessor, serial microcontroller, and ST-BUS. This control port selection is done through pins  $S/\overline{P}$  and  $ST/\overline{SC}$ .

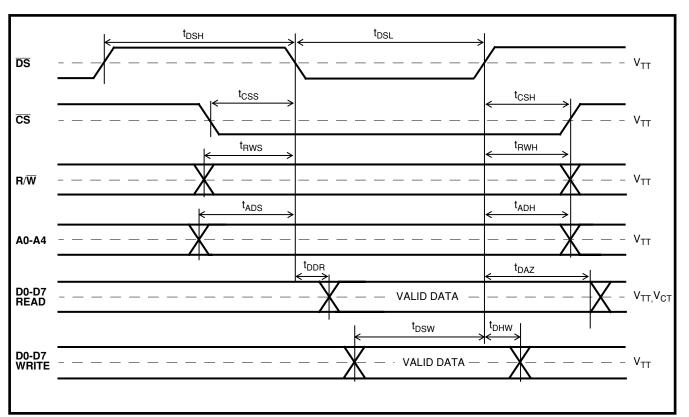

The parallel microprocessor port ( $S/\overline{P}=0$  and  $ST/\overline{SC}=AC4$ ) is non-multiplexed and consists of an eight bit bidirectional data bus (D0-D7), a five bit address/command bus (AC0-AC4), read/write (R/ $\overline{W}$ ), chip select ( $\overline{CS}$ ), data strobe ( $\overline{DS}$ ) and an interrupt request ( $\overline{IRQ}$ ). This port can be easily interfaced to most high speed parallel microprocessors.

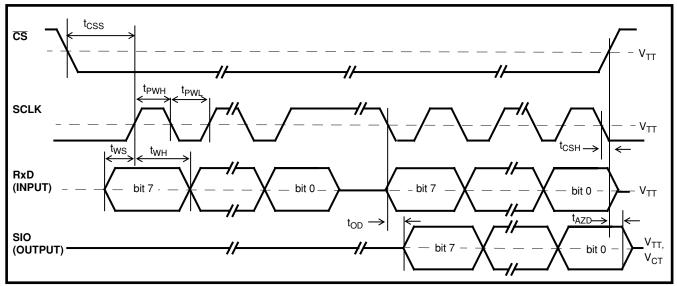

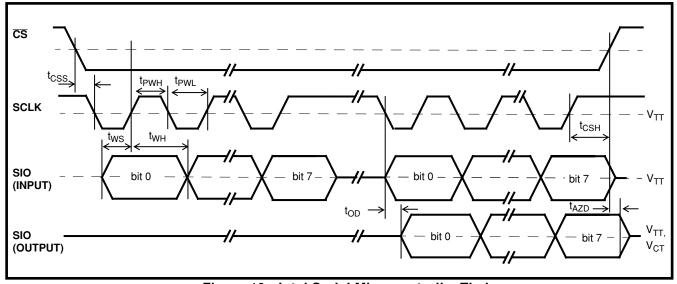

The serial microcontroller port ( $S/\overline{P}=1$  and  $ST/\overline{SC}=0$ ) consists of a receive data input (RxD), serial clock input (SCLK), serial data input/output (SIO), interrupt request ( $\overline{IRQ}$ ), and chip select ( $\overline{CS}$ ). This port will automatically interface to Intel, Motorola or National microcontrollers in either synchronous or asynchronous modes. When controller mode is

selected, the SCLK input is sampled when  $\overline{CS}$  is brought low. If SCLK is high the device is in Intel mode; if SCLK is low it will be in Motorola/National Microwire mode.

The ST-BUS port ( $S/\overline{P}=1$  and  $ST/\overline{SC}=1$ ) consists of control streams CSTi0 and CSTi1 and status stream CSTo0. It should be noted that in this mode access to the circular buffers and notional bit buffers is not provided, and the  $\overline{IRQ}$  function is not supported. This port meets the requirements of the "ST-BUS Generic Device Specification", Zarlink Application Note MSAN-126.

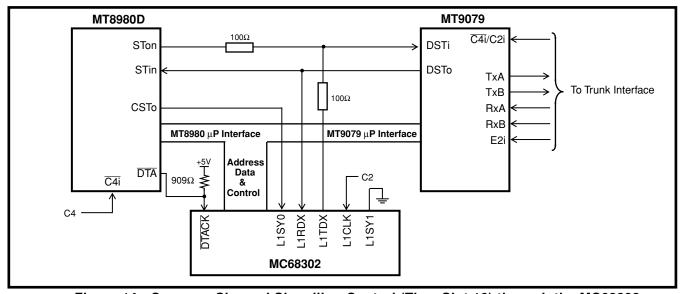

Figure 3 - Control Port Interface

#### **Control and Status Register Access**

The parallel microprocessor and serial microcontroller interfaces gain access to specific registers of the MT9079 through a two step process. First, writing to the Command/Address Register (CAR) selects one of the 14 pages of control and status registers (CAR address: AC4 = 0, AC3-AC0 =

don't care, CAR data D7 - D0 = page number). Second, each page has a maximum of 16 registers that are addressed on a read or write to a non-CAR address (non-CAR: address AC4 = 1, AC3-AC0 = register address, D7-D0 = data). Once a page of memory is selected, it is only necessary to write to the CAR when a different page is to be accessed. See Figure 17 for timing requirements.

Communications between a serial controller and MT9079 is a two byte operations. First, a Command/Address byte selects the address and operation that follows. That is, the  $R/\overline{W}$  bit selects a read or write function and  $A_4$  determines if the next byte is a new memory page address ( $A_4=0$ ) or a data transfer within the current memory page ( $A_4=1$ ). The second byte is either a new memory page address (when  $A_4=0$ ) or a data byte (when  $A_4=1$ ). This is illustrated as follows:

#### a) Command/Address byte -

| R/W | Х | Χ | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |

|-----|---|---|----------------|----------------|----------------|----------------|----------------|

|-----|---|---|----------------|----------------|----------------|----------------|----------------|

#### where:

$R/\overline{W}$  - read or write operation,

X - no function,

$A_4 = 0$  - new memory page address to follow,

$A_4 = 1$  - data byte to follow, and

A<sub>3</sub>-A<sub>0</sub> - determines the byte address.

#### b) Page address or data byte -

| D <sub>7</sub> D <sub>6</sub> D <sub>5</sub> D <sub>4</sub> D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D |

|------------------------------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------------------------------|

See Figures 18 and 19 for timing requirements.

#### Register Access and Locations

Table 2 associates the MT9079 control and status pages with access and page descriptions, as well as an ST-BUS stream. When ST-BUS access mode is used, each page contains 16 registers that are associated consecutively with the first or second 16 channels of each ST-BUS stream. That is, page 1 register locations 10000 to 11111 appear on CSTi0 time slots 0 to 15, and page 2 register locations 10000 to 11111 appear on CSTi0 time slots 16 to 31. It should be noted that access to the transmit and receive circular buffers is not supported in ST-BUS mode.

#### **Common ST-BUS Streams**

There are several control and status ST-BUS streams that are common to all modes. CSTo1 contains the received channel associated signalling bits (e.g., CCITT R1 and R2 signalling), and when control bit RPSIG = 0, CSTi2 is used to control the transmit channel associated signalling. DSTi and DSTo contain the transmit and receive voice and digital data. Figures 4a, b and c illustrate the relative channel positions of the ST-BUS and PCM 30

| Page Address<br>D <sub>7</sub> - D <sub>0</sub> | Register Description            | Processor/<br>Controller<br>Access | ST-BUS<br>Access |

|-------------------------------------------------|---------------------------------|------------------------------------|------------------|

| 0000001                                         | Master                          | R/W                                | CSTi0            |

| 0000010                                         | Control                         | R/W                                |                  |

| 00000011                                        | Master                          | R                                  | CSTo0            |

| 00000100                                        | Status                          | R/W                                |                  |

| 00000101                                        | Per Channel Transmit Signalling | R/W                                | CSTi2            |

| 00000110                                        | Per Channel Receive Signalling  | R                                  | CSTo1            |

| 00000111                                        | Per Time Slot                   | R/W                                | CSTi1            |

| 00001000                                        | Control                         | R/W                                |                  |

| 00001001                                        | Transmit Circular Buffer Zero   | R/W                                |                  |

| 00001010                                        | Transmit Circular Buffer One    | R/W                                |                  |

| 00001011                                        | Receive Circular Buffer Zero    | R                                  |                  |

| 00001100                                        | Receive Circular Buffer One     | R                                  |                  |

| 00001101                                        | Transmit National Bit Buffer    | R/W                                |                  |

| 00001110                                        | Receive National Bit Buffer     | R                                  |                  |

**Table 2 - Register Summary**

interface. See Tables 13, 14, 16 and 17 for CAS bit positions in CSTo1 and CSTi2.

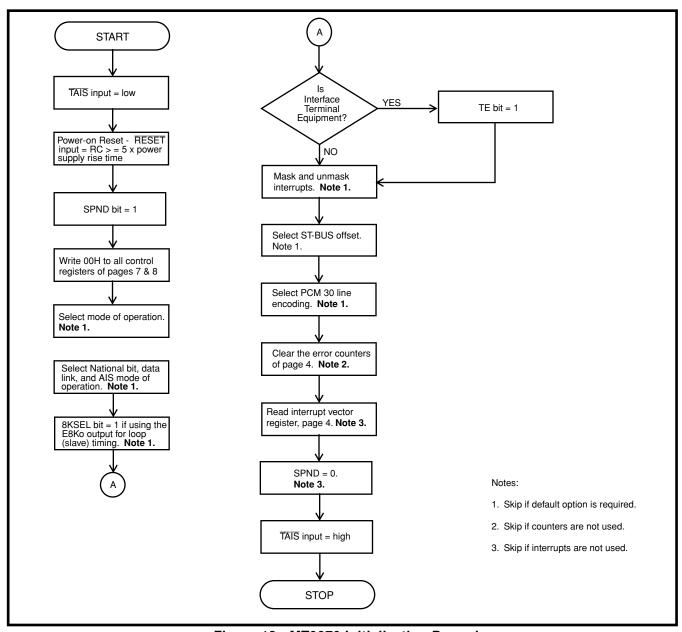

#### **Reset Operation (Initialization)**

The MT9079 can be reset using the hardware RESET pin (see pin description for external reset circuit requirements) or the software reset bit RST (page 1, address 11H). During the reset state, TxA and TxB are low. When the device emerges from its reset state it will begin to function with the default settings described in Table 3.

| Function              | Status                                                                                  |

|-----------------------|-----------------------------------------------------------------------------------------|

| Port Selection        | as per pins S/P & ST/SC                                                                 |

| Mode                  | Termination                                                                             |

| Receive G.704 Framing | Activated                                                                               |

| ST-BUS Offset         | 0000000*                                                                                |

| Loopbacks             | Deactivated                                                                             |

| E8Ko                  | Deactivated                                                                             |

| Transmit FAS          | C <sub>n</sub> 0011011                                                                  |

| Transmit non-FAS      | 1/S <sub>n</sub> 1111111                                                                |

| Transmit MFAS (CAS)   | 00001111                                                                                |

| Data Link             | Deactivated                                                                             |

| CRC Interworking      | Activated                                                                               |

| Code Insert/Detect    | Deactivated                                                                             |

| Signalling            | CAS (CSTi2 & CSTo1)                                                                     |

| ABCD Bit Debounce     | Deactivated                                                                             |

| Interrupts            | Interrupt Mask Word Zero<br>unmasked, all others<br>masked; interrupts not<br>suspended |

| RxMF Output           | Signalling Multiframe                                                                   |

| Error Insertion       | Deactivated                                                                             |

| Coding                | 10*                                                                                     |

| Tx/Rx Buffers         | Deactivated                                                                             |

| Counters              | Random                                                                                  |

Table 3 - Reset Status

See the Applications section for the MT9079 initialization procedure.

|  | 10 00 63 07 07 07 07 07 07 07 07 07 07 07 07 07 | OM 30 | # :F3C | c | - | ç | ç | Ţ | Ц | ú | 7 | ° | Г | 9 | ÷ | 4.5 | 0, | Ş | ñ | ٥ | ,7 | ٥ | 0 | , | Ċ | , 00 | 0 | 70 | 90 | 27 | 00 | 00 | 00 | г |

|--|-------------------------------------------------|-------|--------|---|---|---|---|---|---|---|---|---|---|---|---|-----|----|---|---|---|----|---|---|---|---|------|---|----|----|----|----|----|----|---|

|--|-------------------------------------------------|-------|--------|---|---|---|---|---|---|---|---|---|---|---|---|-----|----|---|---|---|----|---|---|---|---|------|---|----|----|----|----|----|----|---|

| CSTo1/CSTi2 | PCM 30 | Basic Frame | Timeslot 16 for | channel |

|-------------|--------|-------------|-----------------|---------|

| 0           |        | 0           | ×               |         |

| -           |        | _           | _               |         |

| 2           |        | 0           | 0               |         |

| ဗ           |        | က           | က               |         |

| 4           |        | 4           | 4               |         |

| 2           |        | 2           | 2               |         |

| 9           |        | 9           | 9               |         |

|             |        |             | ~               |         |

| 8           |        |             | 8               |         |

| 9           |        | 9 10        |                 |         |

| 10 11       |        | 0 11        | 0 11            |         |

| 1 12        |        | 1 12        | 1 12            |         |

| 2 13        |        | 2 13        |                 |         |

|             |        | 3           | 3               |         |

| 14 15       |        | 14 15       | 14 15           |         |

| 5 16        |        | 2           | ×               |         |

| 6 17        |        | _           | 16              |         |

| 7 18        |        | 0           | 5 17            |         |

| 3 19        |        | ო           | 7 18            |         |

| 9 20        |        | 4           |                 |         |

| ) 21        |        |             |                 |         |

| 22          |        | 9           |                 |         |

| 23          |        | 7           |                 |         |

| 3 24        |        | ∞           |                 |         |

| . 25        |        | 6           |                 |         |

| 56          |        | 9           | 52              |         |

| 27          |        | Ξ           |                 |         |

| , 28        |        | 12          | 27              |         |

| 3 29        |        | 13          |                 |         |

| 30          |        | 4           | 59              |         |

| 31          |        | 15          |                 |         |

8 8

ළ ම

තු <u>ත</u>

28

27

8 8

25 25

24

23

22 22

2 2

2 S

19

8 8

<u>+</u> + +

13 5

전 전

우 우

ω ω

ဖ ဖ

ო ო

a

0

PCM 30 Timeslot # **DSTo Channels**

Output

and

30 Timeslots

- Relationship between Received PCM

5 **4b**

Figure

Ξ

Figure 4c - Relationship between PCM 30 Frames, Channels and CSTo1 Channels CCS = denotes Signalling Channel if Common Channel Signalling Mode Selected

x = Unused Channel

<sup>\*</sup>cleared by the  $\overline{RESET}$  pin, but not by the RST control bit.

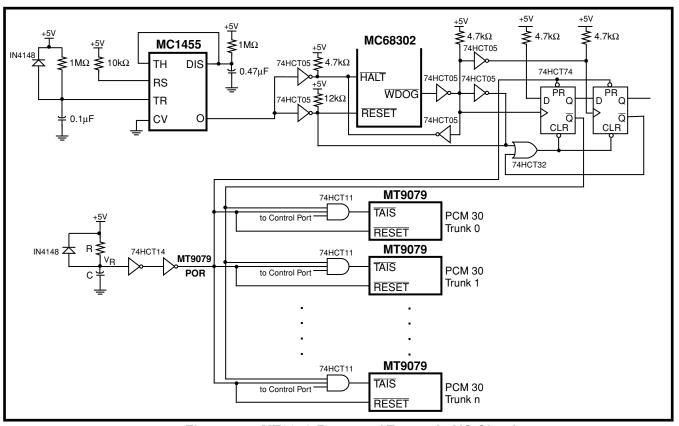

#### **TAIS Operation**

The TAIS (Transmit AIS) pin allows the PRI interface to transmit an all ones signal form the point of power-up without writing to any control registers. After the interface has been initialized normal operation can take place by making TAIS high.

#### **National Bit Buffers**

Table 4 shows the contents of the transmit and receive Frame Alignment Signals (FAS) and Non-frame Alignment Signals (NFAS) of time slot zero of a PCM 30 signal. Even numbered frames (CRC Frame # 0, 2, 4, ...) are FASs and odd numbered frames (CRC Frame # 1, 3, 5, ...) are NFASs. The bits of each channel are numbered 1 to 8, with 1 being the most significant and 8 the least significant.

| CRC             | CRC<br>Frame/ |                | P | CM 3 | 0 Ch            | anne            | l Ze            | ro              |                 |

|-----------------|---------------|----------------|---|------|-----------------|-----------------|-----------------|-----------------|-----------------|

|                 | Type          | 1              | 2 | 3    | 4               | 5               | 6               | 7               | 8               |

|                 | 0/FAS         | C <sub>1</sub> | 0 | 0    | 1               | 1               | 0               | 1               | 1               |

| l _             | 1/NFAS        | 0              | 1 | ALM  | S <sub>a4</sub> | S <sub>a5</sub> | S <sub>a6</sub> | S <sub>a7</sub> | S <sub>a8</sub> |

| me ,            | 2/FAS         | $C_2$          | 0 | 0    | 1               | 1               | 0               | 1               | 1               |

| Fra             | 3/NFAS        | 0              | 1 | ALM  | S <sub>a4</sub> | S <sub>a5</sub> | S <sub>a6</sub> | S <sub>a7</sub> | S <sub>a8</sub> |

| Multi           | 4/FAS         | C <sub>3</sub> | 0 | 0    | 1               | 1               | 0               | 1               | 1               |

| Sub Multi Frame | 5/NFAS        | 1              | 1 | ALM  | S <sub>a4</sub> | S <sub>a5</sub> | S <sub>a6</sub> | S <sub>a7</sub> | S <sub>a8</sub> |

|                 | 6/FAS         | C <sub>4</sub> | 0 | 0    | 1               | 1               | 0               | 1               | 1               |

|                 | 7/NFAS        | 0              | 1 | ALM  | S <sub>a4</sub> | S <sub>a5</sub> | S <sub>a6</sub> | S <sub>a7</sub> | S <sub>a8</sub> |

|                 | 8/FAS         | C <sub>1</sub> | 0 | 0    | 1               | 1               | 0               | 1               | 1               |

| 2               | 9/NFAS        | 1              | 1 | ALM  | S <sub>a4</sub> | S <sub>a5</sub> | S <sub>a6</sub> | S <sub>a7</sub> | S <sub>a8</sub> |

|                 | 10/FAS        | C <sub>2</sub> | 0 | 0    | 1               | 1               | 0               | 1               | 1               |

| Sub Multi Frame | 11/NFAS       | 1              | 1 | ALM  | S <sub>a4</sub> | S <sub>a5</sub> | S <sub>a6</sub> | S <sub>a7</sub> | S <sub>a8</sub> |

| Mult            | 12/FAS        | C <sub>3</sub> | 0 | 0    | 1               | 1               | 0               | 1               | 1               |

| gng             | 13/NFAS       | E <sub>1</sub> | 1 | ALM  | S <sub>a4</sub> | S <sub>a5</sub> | S <sub>a6</sub> | S <sub>a7</sub> | S <sub>a8</sub> |

|                 | 14/FAS        | C <sub>4</sub> | 0 | 0    | 1               | 1               | 0               | 1               | 1               |

|                 | 15/NFAS       | E <sub>2</sub> | 1 | ALM  | S <sub>a4</sub> | S <sub>a5</sub> | S <sub>a6</sub> | S <sub>a7</sub> | S <sub>a8</sub> |

Table 4 - FAS and NFAS Structure

indicates position of CRC-4 multiframe alignment signal.

Table 5 illustrates the organization of the MT9079 transmit and receive national bit buffers. Each row is an addressable byte of the MT9079 national bit buffer, and each column contains the national bits of an odd numbered frame of each CRC-4 Multiframe.

The transmit and receive national bit buffers are selectible in microprocessor or microcontroller

modes, but cannot be accessed in ST-BUS mode. In ST-BUS mode access to the national bits can be achieved through the Transmit and Receive Non-frame Alignment Signal (CSTi0 and CSTo). When selected, the Data Link (DL) pin functions override the transmit national bit buffer function.

The CALN (CRC-4 Alignment) status bit and maskable interrupt CALNI indicate the beginning of every received CRC-4 multiframe.

| Addre ssable | Fran            | nes 1,          | 3, 5,           |                 | 1, 13 a<br>frame | & 15 с          | f a Cl          | RC-4            |

|--------------|-----------------|-----------------|-----------------|-----------------|------------------|-----------------|-----------------|-----------------|

| Bytes        | F1              | F3              | F5              | F7              | F9               | F11             | F13             | F15             |

| NBB0         | S <sub>a4</sub>  | S <sub>a4</sub> | S <sub>a4</sub> | S <sub>a4</sub> |

| NBB1         | S <sub>a5</sub>  | S <sub>a5</sub> | S <sub>a5</sub> | S <sub>a5</sub> |

| NBB2         | S <sub>a6</sub>  | S <sub>a6</sub> | S <sub>a6</sub> | S <sub>a6</sub> |

| NBB3         | S <sub>a7</sub>  | S <sub>a7</sub> | S <sub>a7</sub> | S <sub>a7</sub> |

| NBB4         | S <sub>a8</sub>  | S <sub>a8</sub> | S <sub>a8</sub> | S <sub>a8</sub> |

Table 5 - MT9079 National Bit Buffers

Note: NBB0 - NBB4 are addressable bytes of the MT9079 transmit and receive national bit buffers.

#### **Data Link Operation**

The MT9079 has a user defined 4 kbit/sec. data link for the transport of maintenance and performance monitoring information across the PCM 30 link. This channel functions using one of the national bits ( $S_{a4}$ ,  $S_{a5}$ ,  $S_{a6}$ ,  $S_{a7}$  or  $S_{a8}$ ) of the PCM 30 channel zero non-frame alignment signal. The  $S_a$  bit used for the DL is selected by making one of the bits,  $S_{a4}$  -  $S_{a8}$ , high in the Data Link Select Word. Access to the DL is provided by pins DLCLK, TxDL and RxDL, which allow easy interfacing to an HDLC controller.

The 4 kHz DLCLK output signal is derived from the ST-BUS clocks and is aligned with the receive data link output RxDL. The DLCLK will not change phase with a received frame slip, but the RxDL data has a 50% chance of being lost or repeated when a slip occurs.

The TxDL input signal is clocked into the MT9079 by the rising edge of an internal 4 kHz clock (e.g., internal data link clock IDCLK). The IDCLK is 180 degrees out of phase with the DLCLK. See Figures 20 and 21 for timing requirements.

#### **Elastic Buffer**

When control bit RDLY=0, the MT9079 has a two frame receive elastic buffer, which absorbs wander and low frequency jitter in multi-trunk applications. The received PCM 30 data (RxA and RxB) is clocked into the elastic buffer with the E2i clock and is clocked out of the elastic buffer with the  $\overline{C4i}/C2i$  clock. The E2i extracted clock is generated from, and is therefore phase-locked with, the receive PCM 30 data. In normal operation, the E2i clock will be phase-locked to the  $\overline{C4i}/C2i$  clock by an external phase locked loop (PLL). Therefore, in a single trunk system the receive data is in phase with the E2i clock, the  $\overline{C4i}/C2i$  clock is phase-locked to the E2i clock, and the read and write positions of the elastic buffer will remain fixed with respect to each other.

In a multi-trunk slave or loop-timed system (i.e., PABX application) a single trunk will be chosen as a network synchronizer, which will function as described in the previous paragraph. The remaining trunks will use the system timing derived form the synchronizer to clock data out of their elastic buffers. Even though the PCM 30 signals from the network are synchronize to each other, due to multiplexing, transmission impairments and route diversity, these signals may jitter or wander with respect to the synchronizer trunk signal. Therefore, the E2i clocks of non-synchronizer trunks may wander with respect to the E2i clock of the synchronizer and the system bus. Network standards state that, within limits, trunk interfaces must be able to receive error-free data in the presence of jitter and wander (refer to network requirements for jitter and wander tolerance). The MT9079 will allow a minimum of 26 channels (208 UI, unit intervals) of wander and low frequency jitter before a frame slip will occur.

The minimum delay through the receive elastic buffer is approximately two channels and the maximum delay is approximately 60 channels (RDLY=0), see Figure 5.

When the C4i/C2i and the E2i clocks are not phase-locked, the rate at which data is being written into the elastic buffer from the PCM 30 side may differ from the rate at which it is being read out onto the ST-BUS. If this situation persists, the delay limits stated in the previous paragraph will be violated and the elastic buffer will perform a controlled frame slip. That is, the buffer pointers will be automatically adjusted so that a full PCM 30 frame is either repeated or lost. All frame slips occur on PCM 30 frame boundaries.

The RSLIP and RSLPD status bits give indication of a slip occurrence and direction. A maskable interrupt SLPI is also provided.

Figure 5 illustrates the relationship between the read and write pointers of the receive elastic buffer. Measuring clockwise from the write pointer, if the read pointer comes within two channels of the write pointer a frame slip will occur, which will put the read pointer 34 channels from the write pointer. Conversely, if the read pointer moves more than 60 channels from the write pointer, a slip will occur, which will put the read pointer 28 channels from the write pointer. This provides a worst case hysteresis of 13 channels peak (26 channels peak-to-peak) or a wander tolerance of 208 UI.

When control bit RDLY=1, the receive elastic buffer becomes one frame long and the controlled slip function is disabled. This is to allow the user to control the receive throughput delay of the MT9079 in one of the following ways:

by programming the SOFF7-0 bits to select the desired throughput delay, which is indicated by

Figure 5 - Elastic Buffer Functional Diagram (208 UI Wander Tolerance)

the phase status word bits RxTS4-0 and RxBC2-0.

2) by controlling the position of the F0i pulse with respect to the received time slot zero position. The phase status word bits RxTS4-0 and RxBC2-0 will also indicate the delay in this application.

With RDLY=1, the elastic buffer may underflow or overflow. This is indicated by the RSLIP and RSLPD status bits. If RSLPD=0, the elastic buffer has overflowed and a bit was lost; if RSLPD=1, a underflow condition occurred and a bit was repeated.

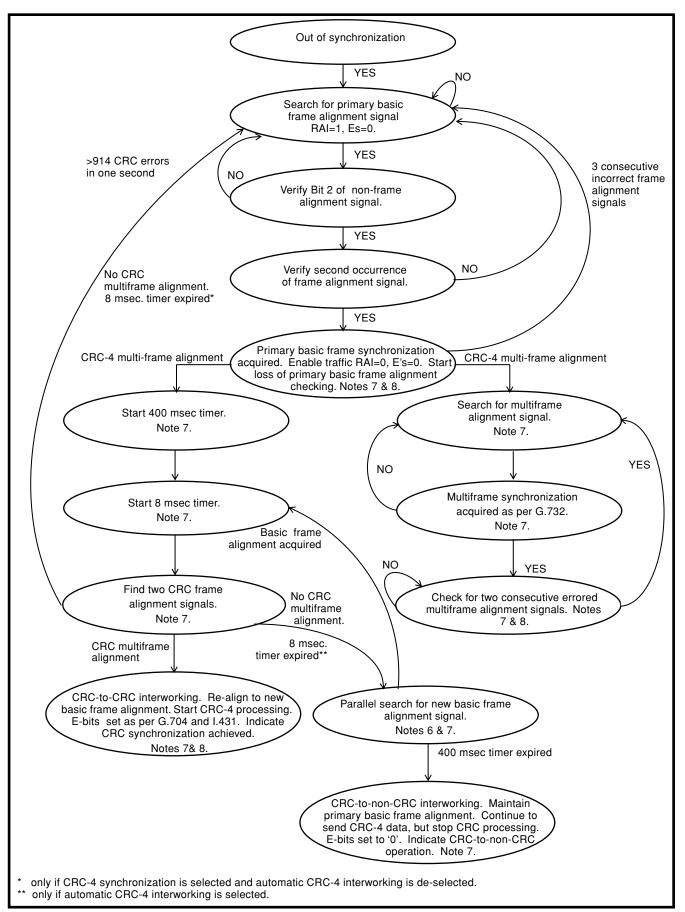

#### Framing Algorithm

The MT9079 contains three distinct, but interdependent, framing algorithms. These algorithms are for basic frame alignment, signalling multiframe alignment and CRC-4 multiframe alignment. Figure 6 is a state diagram that illustrates these functions and how they interact.

After power-up the basic frame alignment framer will search for a frame alignment signal (FAS) in the PCM 30 receive bit stream. Once the FAS is detected, the corresponding bit two of the non-frame alignment signal (NFAS) is checked. If bit two of the NFAS is zero a new search for basic frame alignment is initiated. If bit two of the NFAS is one and the next FAS is correct, the algorithm declares that basic frame synchronization has been found (i.e., SYNC is low).

Once basic frame alignment is acquired the signalling and CRC-4 multiframe searches will be initiated. The signalling multiframe algorithm will align to the first multiframe alignment signal pattern (MFAS = 0000) it receives in the most significant nibble of channel 16 (MFSYNC = 0). Signalling multiframing will be lost when two consecutive multiframes are received in error.

The CRC-4 multiframe alignment signal is a 001011 bit sequence that appears in PCM 30 bit position one of the NFAS in frames 1, 3, 5, 7, 9 and 11 (see Table 4). In order to achieved CRC-4 synchronization two consecutive CRC-4 multiframe alignment signals must be received without error ( $\overline{\text{CRCSYN}} = 0$ ). See Figure 6 for a more detailed description of the framing functions.

The MT9079 framing algorithm supports automatic interworking of interfaces with and without CRC-4 processing capabilities. That is, if an interface with

CRC-4 capability, achieves valid basic frame alignment, but does not achieve CRC-4 multiframe alignment by the end of a predefined period, the distant end is considered to be a non-CRC-4 interface. When the distant end is a non-CRC-4 interface, the near end automatically suspends receive CRC-4 functions, continues to transmit CRC-4 data to the distant end with its E-bits set to zero, and provides a status indication. Naturally, if distant end initially achieves CRC-4 synchronization, CRC-4 processing will be carried out by both ends. This feature is selected when control bit  $\overline{AUTC} = 0$ . See Figure 6 for more details.

#### Notes for Figure 6:

- 1) The basic frame alignment, signalling multiframe alignment, and CRC-4 multiframe alignment functions operate in parallel and are independent.

- 2) The receive channel associated signalling bits and signalling multiframe alignment bit will be frozen when multiframe alignment is lost.

- 3) Manual re-framing of the receive basic frame alignment and signalling multiframe alignment functions can be performed at any time.

- 4) The transmit RAI bit will be one until basic frame alignment is established, then it will be zero.

- 5) E-bits can be optionally set to zero until the equipment interworking relationship is established. When this has been determined one of the following will take place:

- a) CRC-to-non-CRC operation E-bits = 0,

- b) CRC-to-CRC operation E-bits as per G.704 and I.431.

- 6) All manual re-frames and new basic frame alignment searches start after the current frame alignment signal position.

- 7) After basic frame alignment has been achieved, loss of frame alignment will occur any time three consecutive incorrect FAS or NFAS are received. Loss of basic frame alignment will reset the complete framing algorithm.

- 8) When CRC-4 multiframing has been achieved, the primary basic frame alignment and resulting multiframe alignment will be adjusted to the basic frame alignment determined during CRC-4

Figure 6 - Synchronization State Diagram

synchronization. Therefore, the primary basic frame alignment will not be updated during the CRC-4 multiframing search, but will be updated when the CRC-4 multiframing search is complete.

#### **Channel Signalling**

When control bit TxCAS is low the MT9079 is in Channel Associated Signalling mode (CAS); when TxCAS is high it is in Common Channel Signalling (CCS) mode. The CAS mode ABCD signalling nibbles can be passed either via the micro-ports (RPSIG = 1) or through related channels of the CSTo1 and CSTi2 serial links (RPSIG = 0), see Figure 4. Memory page five contains the receive ABCD nibbles and page six the transmit ABCD nibbles for micro-port CAS access.

In CAS operation an ABCD signalling bit debounce of 14 msec. can be selected (DBNCE = 1). This is consistent with the signalling recognition time of CCITT Q.422. It should be noted that there may be as much as 2 msec. added to this duration because signalling equipment state changes are not synchronous with the PCM 30 multiframe.

If basic frame synchronization is lost (page 3, address 10H,  $\overline{\text{SYNC}}$  = 1) all receive CAS signalling nibbles are frozen. Receive CAS nibbles will become unfrozen when basic frame synchronization is acquired.

When the SIGI interrupt is unmasked,  $\overline{IRQ}$  will become active when a signalling nibble state change is detected in any of the 30 receive channels. The SIGI interrupt mask is located on page 1, address 1CH, bit 0; and the SIGI interrupt vector (page 4, address 12H) is 01H.

#### Loopbacks

In order to meet PRI Layer 1 requirements and to assist in circuit fault sectionalization the MT9079 has six loopback functions. These are as follows:

a) Digital loopback (DSTi to DSTo at the PCM 30 side). Bit DLBK = 0 normal; DLBK = 1 activate.

b) Remote loopback (RxA and RxB to TxA and TxB respectively at the PCM 30 side). Bit RLBK = 0 normal; RLBK = 1 activate.

c) ST-BUS loopback (DSTi to DSTo at the system side). Bit SLBK = 0 normal; SLBK = 1 activate.

d) Payload loopback (RxA and RxB to TxA and TxB respectively at the system side with FAS and NFAS operating normally). Bit PLBK = 0 normal; PLBK = 1 activate. The payload loopback is effectively a physical connection of DSTo to DSTi within the MT9079. Channel zero and the DL originate at the point of loopback.

e) Local and remote time slot loopback. Local time slot loopback control bit LTSL = 0 normal; LTSL = 1 activate, will loop around transmit ST-BUS time slots to the DSTo stream. Remote time slot loopback bits RTSL = 0 normal; RTSL = 1 activate, will loop around receive PCM 30 time slots towards the remote PCM 30 end.

The digital, remote, ST-BUS and payload loopbacks are located on page 1, address 15H, control bits 3 to 0. The remote and local time slot loopbacks are controlled through control bits 4 and 5 of the per time slot control words, pages 7 and 8.

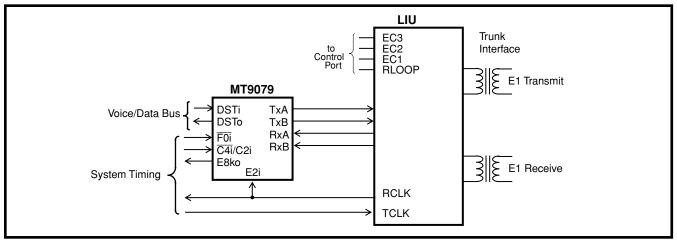

#### PCM 30 Interfacing and Encoding

Bits 7 and 6 of page 1, address 15H (COD1-0) determine the PCM 30 format of the PCM 30 transmit and receive signals. The RZ format (COD1-0 = 00) can be used where the line interface is implemented with discrete components. In this case, the pulse width and state of TxA and TxB directly determine the width and state of the PCM 30 pulses.

NRZ format (COD1-0 = 01) is not bipolar, and therefore, only requires a single output line and a single input line (i.e., TxA and RxA). This signal along with a synchronous 4, 8 or 16 MHz clock can interface to a manchester or similar encoder to produce a self-clocking code for a fibre optic transducer.

The NRZB format (default COD1-0 = 10) is used for interfacing to monolithic Line Interface Units (LIUs). With this format pulses are present for the full bit cell, which allows the set-up and hold times to be meet easily.

The HDB3 control bit (page 1, address 15H, bit 5) selects either HDB3 encoding or alternate mark inversion (AMI) encoding.

#### **Performance Monitoring**

#### MT9079 Error Counters

The MT9079 has six error counters, which can be used for maintenance testing, an ongoing measure of the quality of a PCM 30 link and to assist the designer in meeting specifications such as CCITT I.431 and G.821. In parallel microprocessor and serial microcontroller modes, all counters can be preset or cleared by writing to the appropriate locations. When ST-BUS access is used, this is done by writing the value to be loaded into the counter in the appropriate counter load word (page 2, address 18H to 1FH). The counter is loaded with the new value when the appropriate counter load bit is toggled (page 2, address 15H).

Associated with each counter is a maskable event occurrence interrupt and a maskable counter overflow interrupt. Overflow interrupts are useful when cumulative error counts are being recorded. For example, every time the frame error counter overflow interrupt (FERO) occurs, 256 frame errors have been received since the last FERO interrupt.

An eight bit Error Rate (BERT) counter BR7 - BR0 is located on page 4 address 18H, and is incremented once for every bit detected in error on either the seven frame alignment signal bits or in a selected channel. When a selected channel is used, the data received in this channel will be compared with the data of the bit error rate compare word CMP7-CMP0. See the explanation of the RBUF1 control bit of the per time slot control words (pages 7 and 8) and the bit error rate compare word (page 2, address 11).

There are two maskable interrupts associated with the bit error rate measurement. BERI is initiated when the least significant bit of the BERT counter (BR0) toggles, and BERO in initiated when the BERT counter value changes from FFH to 00H.

# Errored Frame Alignment Signal Counter (EFAS7-EFAS0)

An eight bit Frame Alignment Signal Error counter EFAS7 - EFAS0 is located on page 4 address 1AH, and is incremented once for every receive frame alignment signal that contains one or more errors.

There are two maskable interrupts associated with the frame alignment signal error measurement. FERI is initiated when the least significant bit of the errored frame alignment signal counter toggles, and FERO is initiated when the counter changes from FFH to 00H.

#### **Bipolar Violation Error Counter (BPV15-BPV0)**

The bipolar violation error counter will count bipolar violations or encoding errors that are not part of HDB3 encoding. This counter BPV15-BPV0 is 16 bits long (page 4, addresses 1DH and 1CH) and is incremented once for every BPV error received. It should be noted that when presetting or clearing the BPV error counter, the least significant BPV counter address should be written to before the most significant location.

There are two maskable interrupts associated with the bipolar violation error measurement. BPVI is initiated when the least significant bit of the BPV error counter toggles. BPVO is initiated when the counter changes from FFFFH to 0000H.

#### **Bit Error Rate Counter (BR7-BR0)**

#### **CRC Error and E-bit Counters**

CRC-4 errors and E-bit errors are counted by the MT9079 in order to support compliance with CCITT requirements. These eight bit counters are located on page 4, addresses 1FH and 1EH respectively. They are incremented by single error events, which is a maximum rate of twice per CRC-4 multiframe.

There are two maskable interrupts associated with the CRC error and E-bit error measurement. CRCI and EBI are initiated when the least significant bit of the appropriate counter toggles, and CRCO and EBO are initiated when the appropriate counter changes from FFH to 00H.

#### **G.821 Bit Error Rate Estimation**

A G.821 BERT estimation for an E1 link can be done with either the BERT counter, when it is associated with the FAS, or the Errored Frame Alignment Signal counter. It should be noted that the BERT counter will be incremented once for every bit error found in the FAS, and not just once for every FAS in error. The formula for the link BERT estimation is as follows:

BERT estimation = BERT counter value/(N\*F\*T)

where:

N is the number of bits verified (i.e., when the FAS is used N = 7; when a channel is selected N = 8).

F is the number of FAS or channels in one second (i.e., when the FAS is used F=4000, when a channel is selected F=8000).

T is the elapsed time in seconds.

A similar formula can be used with the FAS error counter.

BERT estimation = FAS Error counter value/(7\*4000\*T).

The CRC-4 error counter can also be used for BERT estimation. The formula for BERT estimation using the CRC-4 error count is as follows:

BERT estimation = CEt counter value/(2048000\*T)

where:

2048000 is the number of bits that are received in one second.

T is the elapsed time in seconds.

A similar formula can be used to provide a BERT estimation of the transmit direction by using the E-bit error counter, EBt.

A more accurate BERT estimation can be done using the Bipolar Violation Error counter. The BPV error counter will count violations that are not due to  $\overline{\text{HDB3}}$  encoding. The formula for this is as follows:

BERT estimation = BPV Error counter value/(256\*8000\*T)

where:

256 is the number of bits per basic frame.

8000 is the number of basic frames in one second.

T is the elapsed time in seconds.

This assumes that one BPV error will be the result of one bit error.

#### **RAI and Continuous CRC-4 Error Counter**

When the receive Remote Alarm Indication is active (RAI = 1 - bit 3 of the NFAS) and a receive E-bit indicates a remote error (En = 0), the RCRC counter will be incremented. This counter will count the number of submultiframes that were received in error at the remote end of a link during a time when layer one capabilities were lost at that end. This eight bit RCRC counter is located on page 4, addresses 19H.

There are two maskable interrupts associated with the RCRC counter. RCRI is initiated when the least significant bit of the RCRC counter toggles, and RCRO and EBO are initiated when the counter changes from FFH to 00H.

#### Maintenance and Alarms

#### **Error Insertion**

Five types of error conditions can be inserted into the transmit PCM 30 data stream through control bits, which are located on page 2, address 10H. These error events include the bipolar violation errors (BPVE), CRC-4 errors (CRCE), FAS errors (FASE), NFAS errors (NFSE), and a loss of signal condition (LOSE). The LOSE function overrides the HDB3 encoding function.

#### **Circular Buffers**

The MT9079 is equipped with two 16 byte circular receive buffers and two 16 byte circular transmit buffers, which can be connected to any PCM 30 time slot. Connection is made through control bits 3 to 0 of the per time slot control words on pages 7 and 8. These buffers will transmit and receive time slot data synchronously with the CRC-4 multiframe.