# CA3262A, CA3262

August 1997

### Features

- Independent Over-Current Limiting On Each Output

- Independent Over-Temperature Limiting On Each Output

- Output Drivers Capable of Switching 700mA Load

- Inputs Compatible With TTL or 5V CMOS Logic

- Suitable For Resistive, Lamp or Inductive Loads

- Power-Frame Package Construction For Good Heat Dissipation

- Operating Temperature Ranges

- CA3262A .....-40°C to 125°C

#### System Applications

Solenoids

Applications

- Automotive

- Relays

- Appliances

- Lamps

- Industrial ControlsRobotics

- SteppersSmall Motors

- Displays

## Ordering Information

| PART NUMBER | TEMP.<br>RANGE ( <sup>o</sup> C) | PACKAGE        | PKG.<br>NO. |

|-------------|----------------------------------|----------------|-------------|

| CA3262E     | -40 to 85                        | 16 Ld PDIP     | E16.3       |

| CA3262AE    | -40 to 125                       | 16 Ld PDIP     | E16.3       |

| CA3262AQ    | -40 to 125                       | 28 Ld PLCC     | N28.45      |

| CA3262AM    | -40 to 125                       | 24 Ld SOIC (W) | M24.3       |

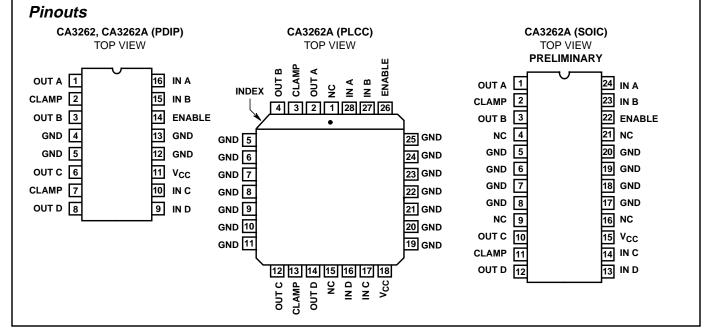

# Description

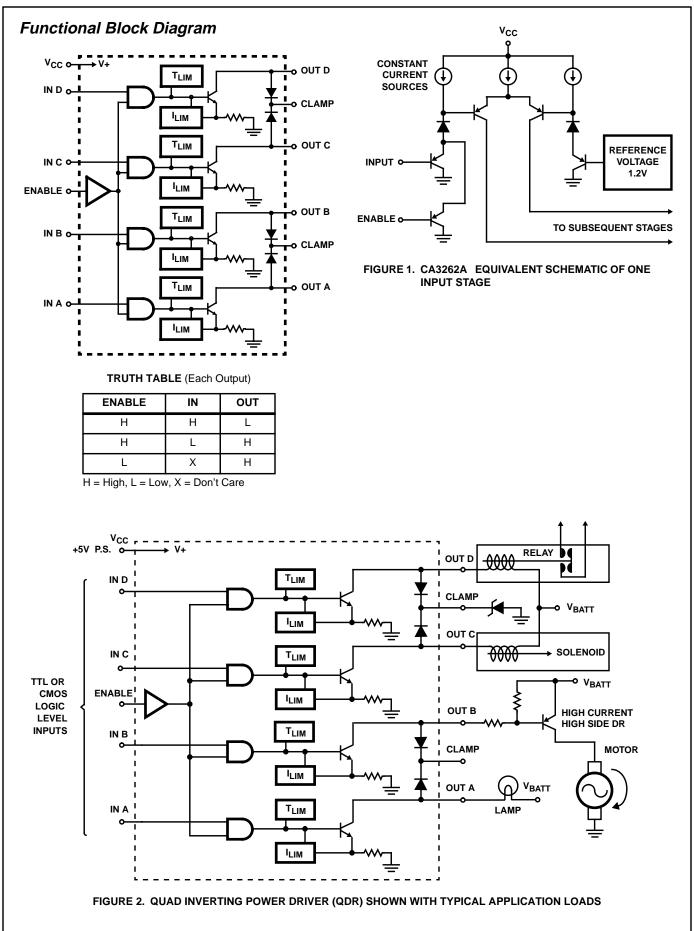

The CA3262 and CA3262A are used to interface low-level logic to high current loads. Each Power Driver has four inverting switches consisting of a non-inverting logic input stage and an inverting low-side driver output stage. All inputs are 5V TTL/CMOS logic compatible and have a common Enable input. Each output device has independent current limiting (I<sub>LIM</sub>) and thermal limiting (T<sub>LIM</sub>) for protection from over-load conditions. Steering diodes connected from each output (in pairs) to the Clamp pins may be used in conjunction with external zener diodes to protect the IC against over-voltage transients that result from inductive load switching.

Quad-Gated, Inverting Power Drivers

To allow for maximum heat transfer from the chip, all ground pins on the DIP, PLCC and SOIC packages are directly connected to the mounting pad of the chip. Integral heat spreading lead frames directly connect the bond pads and ground leads to conduct heat from the chip junction to the PC Board for good heat dissipation.

The CA3262 and CA3262A can drive four incandescent lamp loads without modulating their brilliance when the "cold" lamps are energized. Outputs may be parallel connected to drive high current loads. The maximum output current of each output is determined by the over-current limiting threshold which is typically 1.2A but may be as low as 0.7A.

#### **Absolute Maximum Ratings**

| Logic Supply Voltage, V <sub>CC</sub>              | V  |

|----------------------------------------------------|----|

| Logic Input Voltage, V <sub>IN</sub> 15            | V  |

| Output Voltage, V <sub>CEX</sub> 60 <sup>°</sup>   | V  |

| Output Sustaining Voltage, V <sub>CE(SUS)</sub> 40 | V  |

| Output Transient Current (Note 1                   |    |

| Output Load Current (Note 2                        | 2) |

# **Operating Conditions**

Temperature Range

| i emperatare i tange         |                                          |

|------------------------------|------------------------------------------|

| CA3262AE, CA3262AQ, CA3262AM | -40 <sup>o</sup> C to 125 <sup>o</sup> C |

| CA3262E                      | 40 <sup>0</sup> C to 85 <sup>0</sup> C   |

#### **Thermal Information**

| /  | Thermal Resistance (Typical, Note 3)               | $\theta_{JA}$ (°C/W)                   |

|----|----------------------------------------------------|----------------------------------------|

| /  | For PC Mount Without Added Copper Ground Area      | ••••                                   |

| /  | CA3262E (PDIP)                                     | 60                                     |

| /  | CA3262AE (PDIP)                                    | 60                                     |

| )  | CA3262AQ (PLCC)                                    | 45                                     |

| )  | CA3262AM (SOIC)                                    | 60                                     |

|    | For PC Mount With 2 sq. in. of Added Copper Ground | Area                                   |

|    | CA3262E (PDIP)                                     | 40                                     |

|    | CA3262AE (PDIP)                                    | 40                                     |

|    | CA3262AQ (PLCC)                                    | 36                                     |

| <  | CA3262AM (SOIC)                                    | 36                                     |

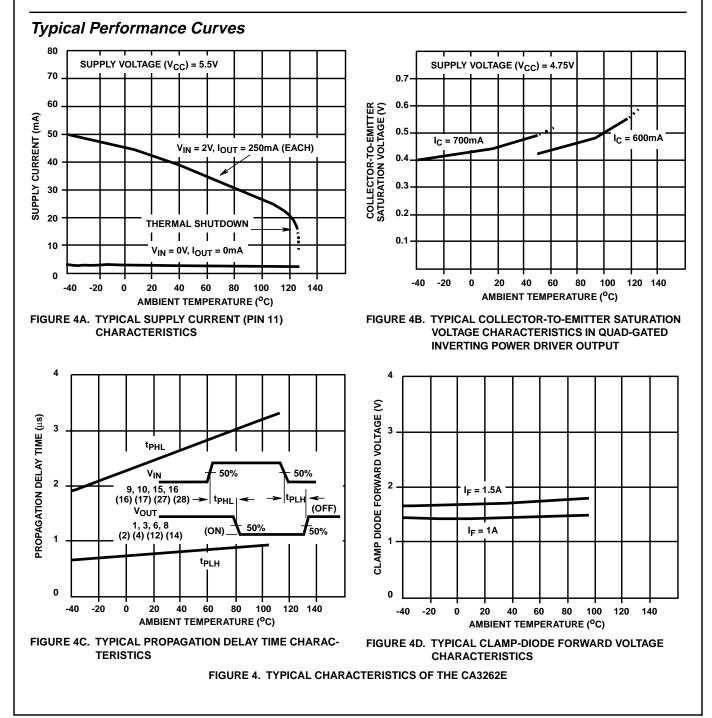

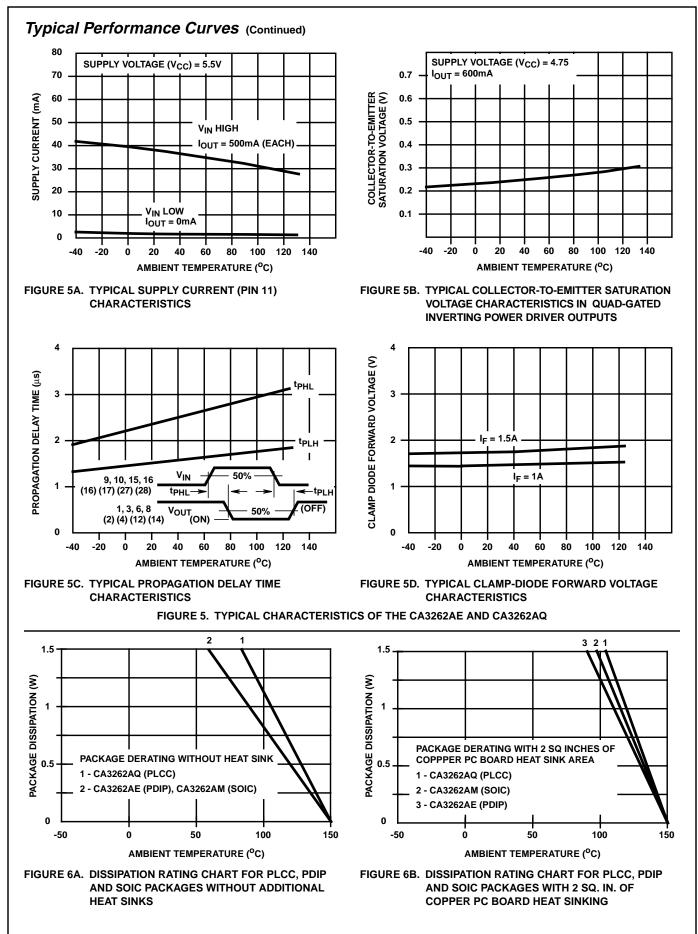

| j, | See Maximum Power Dissipation vs Temperature cu    | rves, Figures                          |

|    | 6A and 6B.                                         |                                        |

|    | Maximum Junction Temperature                       | 150 <sup>0</sup> C                     |

|    | Maximum Storage Temperature Range65                | 5 <sup>0</sup> C to 150 <sup>0</sup> C |

|    | Maximum Lead Temperature (Soldering 10s)           | 265 <sup>0</sup> C                     |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

| Electrical Specifications | $V_{CC} = 5.5V$ , $T_A = -40^{\circ}C$ to $125^{\circ}C$ for CA3262A and $V_{CC} = 5.5V$ , $T_A = -40^{\circ}C$ to $85^{\circ}C$ for CA3262 |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

|                           | Unless Otherwise Specified                                                                                                                  |

|                                                                |                                     |                                                                                                                                                                  |     | CA326 | 62       | CA3262A |          |          |       |

|----------------------------------------------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|----------|---------|----------|----------|-------|

| PARAMETER                                                      | SYMBOL                              | TEST CONDITIONS                                                                                                                                                  | MIN | TYP   | MAX      | MIN     | TYP      | MAX      | UNITS |

| Output Leakage Current                                         | ICEX                                | $V_{CE} = 60V, V_{ENABLE} = 0.8V$                                                                                                                                | -   | -     | 100      | -       | 0.6      | 50       | μA    |

| Output Sustaining<br>Voltage                                   | V <sub>CE(SUS)</sub>                | Note 5                                                                                                                                                           | 40  | -     | -        | 40      | -        | -        | V     |

| Collector Emitter<br>Saturation Voltage                        | V <sub>CE(SAT)</sub>                | $V_{IN} = 2V, V_{CC} = 4.75V$<br>$I_C = 100$ mA                                                                                                                  | -   | -     | 0.25     | -       | 0.05     | 0.15     | v     |

| (See Figures 4B and 5B)                                        |                                     | I <sub>C</sub> = 200mA                                                                                                                                           | -   | -     | -        | -       | -        | 0.2      | V     |

|                                                                |                                     | I <sub>C</sub> = 300mA                                                                                                                                           | -   | -     | -        | -       | -        | 0.25     | V     |

|                                                                |                                     | I <sub>C</sub> = 400mA                                                                                                                                           | -   | -     | 0.4      | -       | 0.2      | 0.3      | V     |

|                                                                |                                     | I <sub>C</sub> = 500mA                                                                                                                                           | -   | -     | -        | -       | -        | 0.4      | V     |

|                                                                |                                     | I <sub>C</sub> = 600mA                                                                                                                                           | -   | -     | 0.6      | -       | -        | 0.5      | V     |

|                                                                |                                     | I <sub>C</sub> = 700mA, T <sub>A</sub> = -40 <sup>o</sup> C                                                                                                      | -   | -     | 0.6      | -       | -        | 0.5      | V     |

| Input Low Voltage                                              | VIL                                 |                                                                                                                                                                  | -   | -     | 0.8      | -       | -        | 0.8      | V     |

| Input High Voltage                                             | VIH                                 |                                                                                                                                                                  | 2   | -     | -        | 2       | -        | -        | V     |

| Input Low Current                                              | Ι <sub>L</sub>                      | V <sub>IN</sub> = 0.8V                                                                                                                                           | -   | -     | 10       | -       | 0.75     | 10       | μA    |

| Input High Current                                             | Iн                                  | $V_{IN} = V_{ENABLE} = 5.5V,$<br>I <sub>C</sub> = 600mA                                                                                                          | -   | -     | 10       | -       | -        | 10       | μΑ    |

| Supply Current,<br>All Outputs ON,<br>(See Figures 4A and 5A)  | I <sub>CC(ON)</sub>                 | $\label{eq:VIN} \begin{array}{l} V_{IN} = 2V, \ V_{ENABLE} = 5.5V, \\ I_{OUTA} = 250mA, \ I_{OUTB} = 250mA, \\ I_{OUTC} = 250mA, \ I_{OUTD} = 250mA \end{array}$ | -   | -     | 70       | -       | (Note 4) | 55       | mA    |

| Supply Current, All<br>Outputs OFF,<br>(See Figures 4A and 5A) | ICC(OFF)                            | V <sub>IN</sub> = 0V                                                                                                                                             | -   | -     | 5        | -       | (Note 4) | 5        | mA    |

| Clamp Diode Leakage<br>Current                                 | I <sub>R</sub>                      | V <sub>R</sub> = 60V                                                                                                                                             | -   | -     | 100      | -       | -        | 50       | μΑ    |

| Clamp Diode Forward                                            | V <sub>F</sub>                      | I <sub>F</sub> = 1A, V <sub>IN</sub> = 0V                                                                                                                        | -   | -     | 1.7      | -       | -        | 1.7      | V     |

| Voltage,<br>(See Figures 4D and 5D)                            |                                     | I <sub>F</sub> = 1.5A, V <sub>IN</sub> = 0V                                                                                                                      | -   | -     | 2.1      | -       | -        | 2.1      | V     |

| Turn-On Delay,<br>(See Figures 4C and 5C)                      | t <sub>PHL</sub> , t <sub>PLH</sub> | I <sub>OUT</sub> = 500mA                                                                                                                                         | -   | -     | 8        | -       | -        | 8        | μs    |

| Over Current Limiting                                          | ILIM                                | V <sub>OUT</sub> = 2V, V <sub>IN</sub> = 5.5V,<br>V <sub>ENABLE</sub> = 5.5V                                                                                     | 0.7 | -     | (Note 1) | 0.7     | -        | (Note 1) | A     |

| DESIGN PARAMETERS                                              | •                                   |                                                                                                                                                                  |     | -     |          |         | •        | •        | -     |

| Over Temperature Limiting (Junction Temperature)               | T <sub>LIM</sub>                    |                                                                                                                                                                  | -   | 155   | -        | -       | 155      | -        | °C    |

**Electrical Specifications**  $V_{CC} = 5.5V$ ,  $T_A = -4$

$V_{CC} = 5.5V$ ,  $T_A = -40^{\circ}C$  to  $125^{\circ}C$  for CA3262A and  $V_{CC} = 5.5V$ ,  $T_A = -40^{\circ}C$  to  $85^{\circ}C$  for CA3262 Unless Otherwise Specified **(Continued)**

|                          |                 |                 | CA3262 |     | CA3262A |     |     |     |       |

|--------------------------|-----------------|-----------------|--------|-----|---------|-----|-----|-----|-------|

| PARAMETER                | SYMBOL          | TEST CONDITIONS | MIN    | TYP | MAX     | MIN | TYP | MAX | UNITS |

| Input Capacitance, Input | C <sub>IN</sub> |                 | -      | -   | -       | -   | 3   | -   | pF    |

| Enable Capacitance       | C <sub>EN</sub> |                 | -      | -   | -       | -   | 4.4 | -   | pF    |

NOTES:

- The CA3262 and CA3262A have on-chip limiting for transient peak currents. Under short-circuit conditions with voltage applied to the collector of the output transistor and with the output transistor turned ON, the current will increase to 1.2A, typical. Over-Current Limiting protects a short circuit condition for a normal operating range of output supply voltage. During a short circuit condition, the output driver will shortly thereafter (approx. 5ms) go into Over-Temperature Limiting. While Over-Current Limiting may range to peak currents greater than 2A, each output will typically withstand a direct short circuit up to supply voltage levels of 16V. Excessive dissipation before thermal limiting occurs may cause damage to the chip for supply voltages greater than 18V. The CA3262 and CA3262A are rated to withstand peak current, cold turn-on conditions of #168 or #194 lamp loads.

- 2. The total DC current for the CA3262 and CA3262A with all 4 outputs ON should not exceed the total of (4 x 0.7A + Max. I<sub>CC</sub>) ~ 2.85A. This level of current will significantly increase the chip temperature due to increased dissipation and may cause thermal shutdown in high ambient temperature conditions (See Absolute Maximum Ratings for Dissipation). Any one output may be allowed to exceed 0.7A but may be subject to Over-Current Limiting above the I<sub>LIM</sub> min. limit of 0.7A. As a practical limit, no single output should be loaded to more than 1A (Max).

- 3. Normal applications require a surface mount of the 28 lead PLCC and 24 lead SOIC packages on a PC Board. The PLCC, SOIC and PDIP packages have power lead frame construction through the ground pins to conduct heat from the frame to the PC Board ground area. Thermal resistance, θ<sub>JA</sub>, is given for a surface mount of the 28 lead PLCC and the 24 lead SOIC packages on a 1 oz. copper PC board with minimal ground area and with 2 square inches of ground area.

- 4. I<sub>CC</sub> varies with temperature. Typically, I<sub>CC(ON)</sub> is 18mA at 125<sup>o</sup>C and 41mA at -40<sup>o</sup>C. Typically, I<sub>CC(OFF)</sub> is 2.2mA at 125<sup>o</sup>C and 1.2mA at -40<sup>o</sup>C.

- 5. Tested with a switched-off 500mA Load of 120mH (with 24 $\Omega$  series resistance), V<sub>BATT</sub> = 12V and the outputs (V<sub>CE</sub>) clamped to +40V maximum with an external zener diode.

# Applications

Typical circuit configurations for applying the CA3262 and CA3262A are shown in the application circuit of Figure 2. To their rated capabilities, both circuits can be used to drive inductive, resistive and lamp loads. The CA3262A has a lower V<sub>SAT</sub> than the CA3262 and is rated for 125°C ambient temperature applications. The CA3262 data sheet rating is 85°C. Otherwise, the protection features described apply to both the CA3262 and CA3262A.

The maximum voltage for full load current switching is the output sustaining voltage,  $V_{CE(SUS)}$  which should not exceed 40V. To provide a means of over-voltage protection, on-chip steering diodes are connected from each output to one of two CLAMP pins. Over-voltage pulses may be generated from inductive load switching and must be clamped or limited to a peak voltage less than  $V_{CE(SUS)}$ . To limit an inductive voltage pulse, a zener diode should be connected to the appropriate CLAMP pin. When the voltage pulse exceeds the zener threshold, the excess energy is dumped to ground via the on-chip steering diode and the external zener diode.

The on-chip diodes may be used in a free-wheeling mode by connecting the CLAMP pins to an external clamp supply voltage. Zener diode clamp protection is preferred over the power supply clamp option, primarily because the power supplies may be subject to large transient changes; including turn-ON and turn-OFF conditions where non-tracking conditions between supplies could allow forward conduction through the steering diodes. For all transient conditions of either method, the clamp voltage should greater than the maximum supply voltage of the switching outputs and less than V<sub>CE(SUS)</sub>.

Note that the rate of change of the output current during load switching is fast. Therefore, even small values of inductance, including the inductance of a few meters of hook-up wire to the load circuit, can generate voltage spikes of considerable amplitude at the output terminals and may require clamping to protect the device ratings.

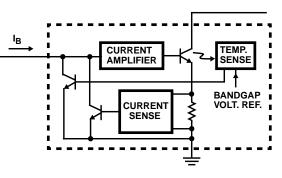

Current-limiting is provided as protection for shorted or overloaded output conditions. Voltage is sampled across a small metal resistor in the emitter of each output stage. When the voltage exceeds a preset comparator level, drive is reduced to the output. Current limiting is sustained unless thermal conditions exceed the preset thermal shutdown temperature of 155°C.

If an output is shorted, the remaining three outputs will continue to function normally unless the continued heat spreading is sufficient to raise the junction temperature at any other output to a level greater than 155°C. High ambient temperature conditions may allow this to happen. The degree of interaction is minimized at chip layout design by separating the output devices, each to a separate corner of the chip.

As noted, the thermal resistance values of the PDIP, PLCC and SOIC packages are improved by direct connection of the leads to the chip mounting pad. For a normal PC Board application, the thermal resistance coefficient for each package can be significantly lowered by increasing ground copper area on the PC board next to the ground pins of the IC.

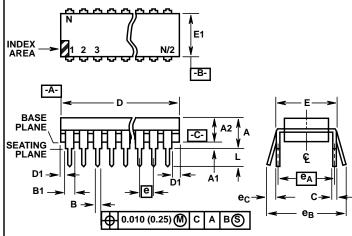

# Dual-In-Line Plastic Packages (PDIP)

#### NOTES:

- 1. Controlling Dimensions: INCH. In case of conflict between English and Metric dimensions, the inch dimensions control.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- 3. Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication No. 95.

- 4. Dimensions A, A1 and L are measured with the package seated in JEDEC seating plane gauge GS-3.

- D, D1, and E1 dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

- E and e<sub>A</sub> are measured with the leads constrained to be perpendicular to datum -C-.

- 7.  $e_B$  and  $e_C$  are measured at the lead tips with the leads unconstrained.  $e_C$  must be zero or greater.

- 8. B1 maximum dimensions do not include dambar protrusions. Dambar protrusions shall not exceed 0.010 inch (0.25mm).

- 9. N is the maximum number of terminal positions.

- Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3, E42.6 will have a B1 dimension of 0.030 - 0.045 inch (0.76 - 1.14mm).

#### E16.3 (JEDEC MS-001-BB ISSUE D) 16 LEAD DUAL-IN-LINE PLASTIC PACKAGE

|                | INC   | HES   | MILLIM   | MILLIMETERS |       |  |  |

|----------------|-------|-------|----------|-------------|-------|--|--|

| SYMBOL         | MIN   | MAX   | MIN      | MAX         | NOTES |  |  |

| A              | -     | 0.210 | -        | 5.33        | 4     |  |  |

| A1             | 0.015 | -     | 0.39     | -           | 4     |  |  |

| A2             | 0.115 | 0.195 | 2.93     | 4.95        | -     |  |  |

| В              | 0.014 | 0.022 | 0.356    | 0.558       | -     |  |  |

| B1             | 0.045 | 0.070 | 1.15     | 1.77        | 8, 10 |  |  |

| С              | 0.008 | 0.014 | 0.204    | 0.355       | -     |  |  |

| D              | 0.735 | 0.775 | 18.66    | 19.68       | 5     |  |  |

| D1             | 0.005 | -     | 0.13     | -           | 5     |  |  |

| E              | 0.300 | 0.325 | 7.62     | 8.25        | 6     |  |  |

| E1             | 0.240 | 0.280 | 6.10     | 7.11        | 5     |  |  |

| е              | 0.100 | BSC   | 2.54     | 2.54 BSC    |       |  |  |

| e <sub>A</sub> | 0.300 | BSC   | 7.62 BSC |             | 6     |  |  |

| e <sub>B</sub> | -     | 0.430 | -        | 10.92       | 7     |  |  |

| L              | 0.115 | 0.150 | 2.93     | 3.81        | 4     |  |  |

| N              | 1     | 6     | 1        | 6           | 9     |  |  |

Rev. 0 12/93

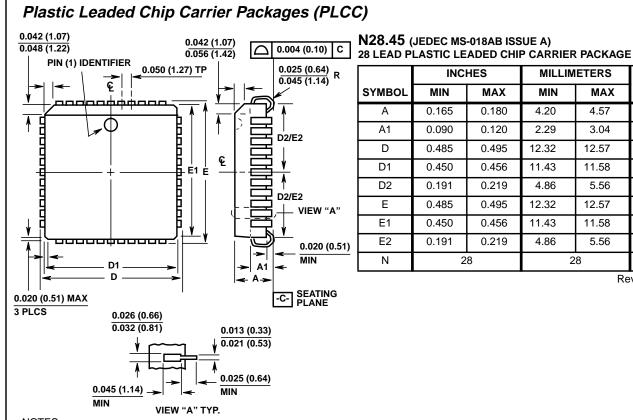

MILLIMETERS

MAX

4.57

3.04

12.57

11.58

5.56

12.57

11.58

5.56

28

NOTES

-

-

-

3

4, 5

-

3

4, 5

6

Rev. 1 3/95

#### NOTES:

- 1. Controlling dimension: INCH. Converted millimeter dimensions are not necessarily exact.

- 2. Dimensions and tolerancing per ANSI Y14.5M-1982.

- 3. Dimensions D1 and E1 do not include mold protrusions. Allowable mold protrusion is 0.010 inch (0.25mm) per side.

- 4. To be measured at seating plane -C- contact point.

- 5. Centerline to be determined where center leads exit plastic body.

- 6. "N" is the number of terminal positions.

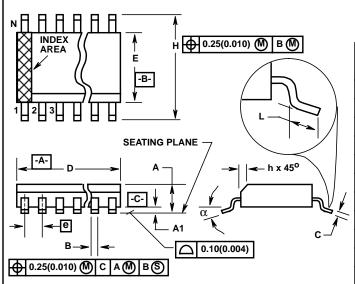

# Small Outline Plastic Packages (SOIC)

#### M24.3 (JEDEC MS-013-AD ISSUE C) 24 LEAD WIDE BODY SMALL OUTLINE PLASTIC PACKAGE

|        | INC            | HES            | MILLIN         |                |       |  |

|--------|----------------|----------------|----------------|----------------|-------|--|

| SYMBOL | MIN            | MAX            | MIN MAX        |                | NOTES |  |

| А      | 0.0926         | 0.1043         | 2.35           | 2.65           | -     |  |

| A1     | 0.0040         | 0.0118         | 0.10           | 0.30           | -     |  |

| В      | 0.013          | 0.020          | 0.33           | 0.51           | 9     |  |

| С      | 0.0091         | 0.0125         | 0.23           | 0.32           | -     |  |

| D      | 0.5985         | 0.6141         | 15.20          | 15.60          | 3     |  |

| E      | 0.2914         | 0.2992         | 7.40           | 7.60           | 4     |  |

| е      | 0.05           | BSC            | 1.27           | BSC            | -     |  |

| Н      | 0.394          | 0.419          | 10.00          | 10.65          | -     |  |

| h      | 0.010          | 0.029          | 0.25           | 0.75           | 5     |  |

| L      | 0.016          | 0.050          | 0.40           | 1.27           | 6     |  |

| Ν      | 2              | 4              | 24             |                | 7     |  |

| α      | 0 <sup>0</sup> | 8 <sup>0</sup> | 0 <sup>0</sup> | 8 <sup>0</sup> | -     |  |

#### NOTES:

- 1. Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

- 5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- The lead width "B", as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch)

- 10. Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

Rev. 0 12/93

#### All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com