# MOTOROLA SEMICONDUCTORI TECHNICAL DATA

## Gate Controlled Two Channel Input Wideband Amplifier

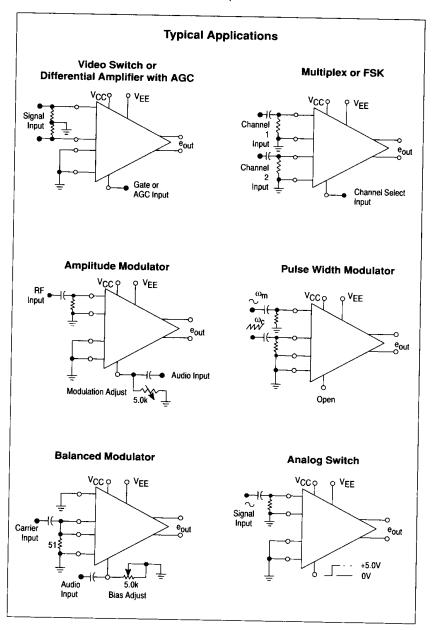

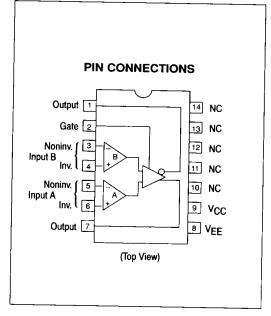

The MC1445/1545 was designed for use as a general purpose gated wideband amplifier, video switch, sense amplifier, multiplexer, modulator, FSK circuit, limiter, AGC circuit, or pulse amplifier.

- Large Bandwidth; 50 MHz Typical

- Channel Select Time of 20 ns Typical

- Differential Inputs and Differential Output

## MC1445 MC1545

#### GATE CONTROLLED TWO CHANNEL INPUT WIDEBAND AMPLIFIER

SILICON MONOLITHIC INTEGRATED CIRCUIT

#### ORDERING INFORMATION

| Device  | Temperature Range | Package     |  |  |

|---------|-------------------|-------------|--|--|

| LM1445L | 0° to +75°C       | Ceramic DIP |  |  |

| LM1545L | −55° to +125°C    | Ceramic DIP |  |  |

MOTOROLA LINEAR/INTERFACE ICs DEVICE DATA

#### **MAXIMUM RATINGS** ( $T_A = +25$ °C, unless otherwise noted.)

| Rating                                                                                                  | Symbol                 | Value      | Unit                    |             |

|---------------------------------------------------------------------------------------------------------|------------------------|------------|-------------------------|-------------|

| Power Supply Voltage                                                                                    | V <sub>CC</sub><br>VEE | +12<br>-12 | Vdc                     |             |

| Input Differential Voltage Range                                                                        | V <sub>IDR</sub>       | ±5.0       | V                       |             |

| Load Current                                                                                            |                        | ΙL         | 25                      | mA          |

| Power Dissipation (Package Limitation) Ceramic Dual In-Line Package Derate above T <sub>A</sub> = +25°C |                        | PD         | 625<br>5.0              | mW<br>mW/°C |

| Operating Ambient Temperature Range                                                                     | MC1445<br>MC1545       | TA         | 0 to +75<br>-55 to +125 | °C          |

| Storage Temperature Range                                                                               |                        | ⊤stg       | -65 to +150             | °C          |

#### $\textbf{ELECTRICAL CHARACTERISTICS} \hspace{0.3cm} (V_{CC} = +5.0 \text{ Vdc}, V_{EE} = -5.0 \text{ Vdc}, @ T_{A} = +25^{\circ}\text{C}, \text{ specifications apply to both input channels,} \\$ unless otherwise noted.)

|                                                                                                                   | Fig. No. | Symbol                       | MC1545      |                          |                      | MC1445      |                          |     |                  |

|-------------------------------------------------------------------------------------------------------------------|----------|------------------------------|-------------|--------------------------|----------------------|-------------|--------------------------|-----|------------------|

| Characteristics                                                                                                   |          |                              | Min Typ     |                          | Max                  | Min         | Тур                      | Max | Unit             |

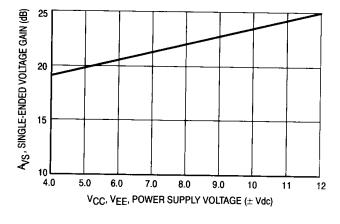

| Single-Ended Voltage Gain                                                                                         | 1, 12    | Avs                          | 16          | 19                       | 21                   | 16          | 19.5                     | 23  | dB               |

| Bandwidth                                                                                                         | 1, 12    | BW                           | 40          | 50                       | _                    | _           | 50                       | _   | MHz              |

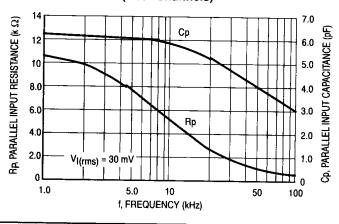

| Input Impedance<br>(f = 50 kHz)                                                                                   | 5, 14    | zį                           | 4.0         | 10                       | _                    | 3.0         | 10                       | _   | kΩ               |

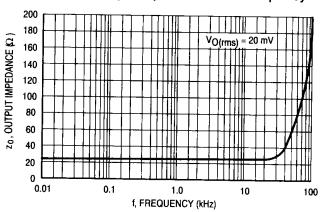

| Output Impedance<br>(f = 50 kHz)                                                                                  | 6, 15    | z <sub>o</sub>               | _           | 25                       | _                    |             | 25                       | _   | Ω                |

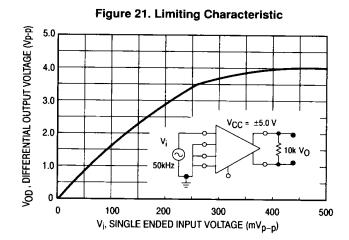

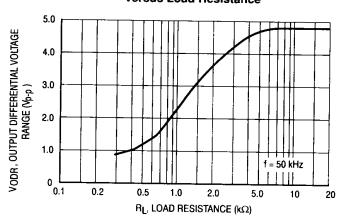

| Output Differential Voltage Range $(R_L = 1.0 \text{ k}\Omega, f = 50 \text{ kHz})$                               | 4, 13    | VODR                         | 1.5         | 2.5                      | _                    | 1.5         | 2.5                      | _   | V <sub>p-p</sub> |

| Input Bias Current                                                                                                | 16       | Iв                           | _           | 15                       | 25                   | -           | 15                       | 30  | μAdc             |

| Input Offset Current                                                                                              | 16       | lio                          | <u> </u>    | 2.0                      | _                    | _           | 2.0                      | _   | μAdc             |

| Input Offset Voltage                                                                                              | 17       | VIO                          | -           | 1.0                      | 5.0                  | _           | _                        | 7.5 | mVdc             |

| Quiescent Output dc Level                                                                                         | 17       | v <sub>o</sub>               | -           | 0.1                      |                      |             | 0.1                      | _   | Vdc              |

| Output dc Level Change<br>(Gate Input Voltage Change: +5.0 V to 0 V)                                              | 17       | ΔVO                          | _           | ±15                      | _                    | _           | ±15                      | _   | mV               |

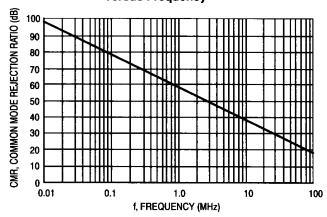

| Common Mode Rejection<br>(f = 50 kHz)                                                                             | 9, 18    | CMR                          | _           | 85                       | _                    | _           | 85                       | _   | dB               |

| Input Common Mode Voltage Range                                                                                   | 18       | VICR                         | -           | ±2.5                     | <b> </b>             | _           | ±2.5                     | _   | V <sub>pk</sub>  |

| Gate Characteristics Gate Input Voltage – Low Logic State (Note 1) Gate Input Voltage – High Logic State (Note 2) | 8        | VIL(G)<br>VIH(G)             | 0.40        | 0.70<br>1.5              | <br>2.2              | 0.2         | 0.4<br>1.3               | 3.0 | Vdc              |

| Gate Input Current – Low Logic State (VIL(G) = 0 V)                                                               | 18       | liL(G)                       | -           | _                        | 2.5                  | _           | _                        | 4.0 | mA               |

| Gate Input Current – High Logic State (VIH(G) = +5.0 V)                                                           | 18       | l <sub>l</sub> H(G)          | -           | _                        | 2.0                  | _           | _                        | 4.0 | μА               |

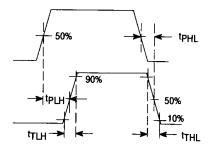

| Step Response<br>(e <sub>in</sub> = 20 mV)                                                                        | 19       | tPLH<br>tPHL<br>tTLH<br>tTHL | _<br>_<br>_ | 6.5<br>6.3<br>6.5<br>7.0 | 10<br>10<br>15<br>15 | _<br>_<br>_ | 6.5<br>6.3<br>6.5<br>7.0 |     | ns               |

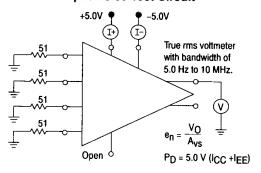

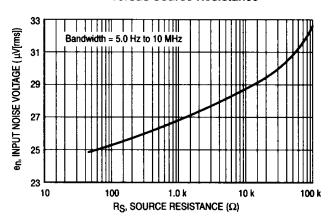

| Wideband Input Noise (5.0 Hz $-$ 10 MHz, R <sub>S</sub> = 50 $\Omega$ )                                           | 10, 20   | en                           |             | 25                       | _                    | _           | 25                       | _   | μV(rms)          |

| DC Power Consumption                                                                                              | 11, 20   | PC                           | _           | 70                       | 110                  | _           | 70                       | 150 | mW               |

NOTES: 1. V<sub>IL(G)</sub> is the gate voltage which results in channel A gain of unity or less and channel B gain of 16 dB or greater.

2. V<sub>IH(G)</sub> is the gate voltage which results in channel B gain of unity or less and channel A gain of 16 dB or greater.

## MC1445, MC1545

Figure 1. Single-Ended Voltage Gain versus Frequency

(9) 25

20 15

10 10 10 100 1000

f, FREQUENCY (kHz)

Figure 2. Single-Ended Voltage Gain versus Temperature

25

20

20

15

10

5.0

5.5

25

0

25

50

75

100

125

T<sub>A</sub>, AMBIENT TEMPERATURE (°C)

Figure 3. Voltage Gain versus Power Supply Voltages

Figure 4. Output Voltage Swing versus Load Resistance

Figure 5. Input Cp and Rp versus Frequency (Both Channels)

Figure 6. Output Impedance versus Frequency

MOTOROLA LINEAR/INTERFACE ICs DEVICE DATA

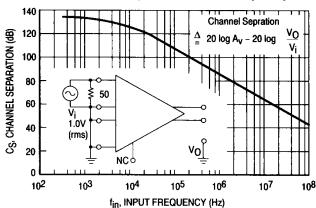

Figure 7. Channel Separation versus Frequency

Figure 8. Gate Characteristics A<sub>VS</sub>, SINGLE-ENDED VOLTAGE GAIN (dB) +20 +10 -10 -20 -30 50≸ 50≸ -40 -50 -60 0.5 1.5 2.0 2.5 VG, GATE VOLTAGE (V)

Figure 9. Common Mode Rejection Ratio versus Frequency

Figure 10. Input Wideband Noise versus Source Resistance

Figure 11. Circuit Schematic

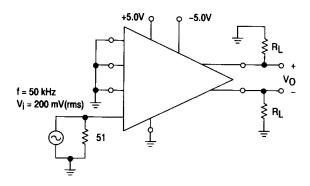

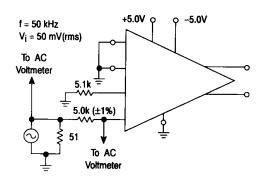

Figure 12. Single-Ended Voltage Gain and Bandwidth Test Circuit

MOTOROLA LINEAR/INTERFACE ICS DEVICE DATA

Figure 13. Output Voltage Swing Test Circuit

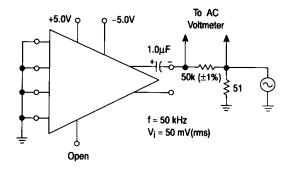

Figure 15. Output Impedance Test Circuit

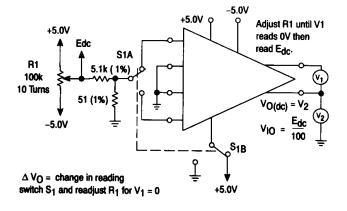

Figure 17. Input Offset Voltage and Quiescent Output Level Test Circuit

Figure 14. Input Impedance Test Circuit

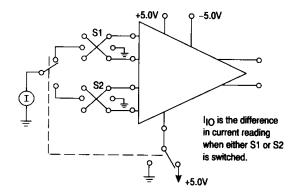

Figure 16. Input Bias Current and Input Offset Current Test Circuit

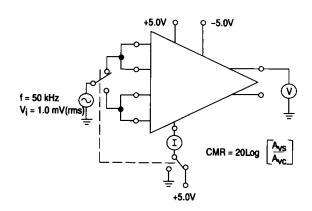

Figure 18. Gate Current (High and Low), Common Mode Rejection and Common Mode Input Range Test Circuit

MOTOROLA LINEAR/INTERFACE ICs DEVICE DATA

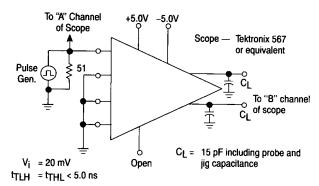

Figure 19. Propagation Delay, Rise and Fall Times Test Circuit

Figure 20. Power Dissipation and Wideband Input Noise Test Circuit