November 1998

## PC87338/PC97338 ACPI 1.0 and PC98/99 Compliant SuperI/O

### **General Description**

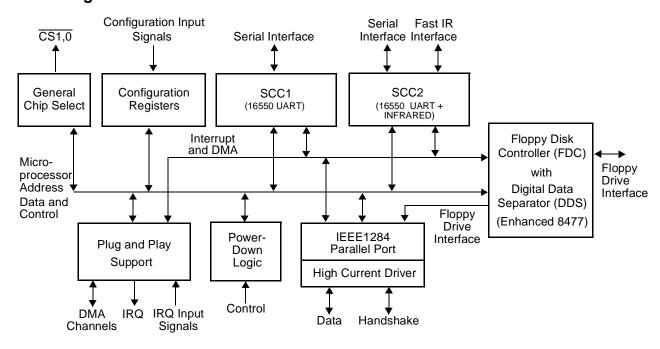

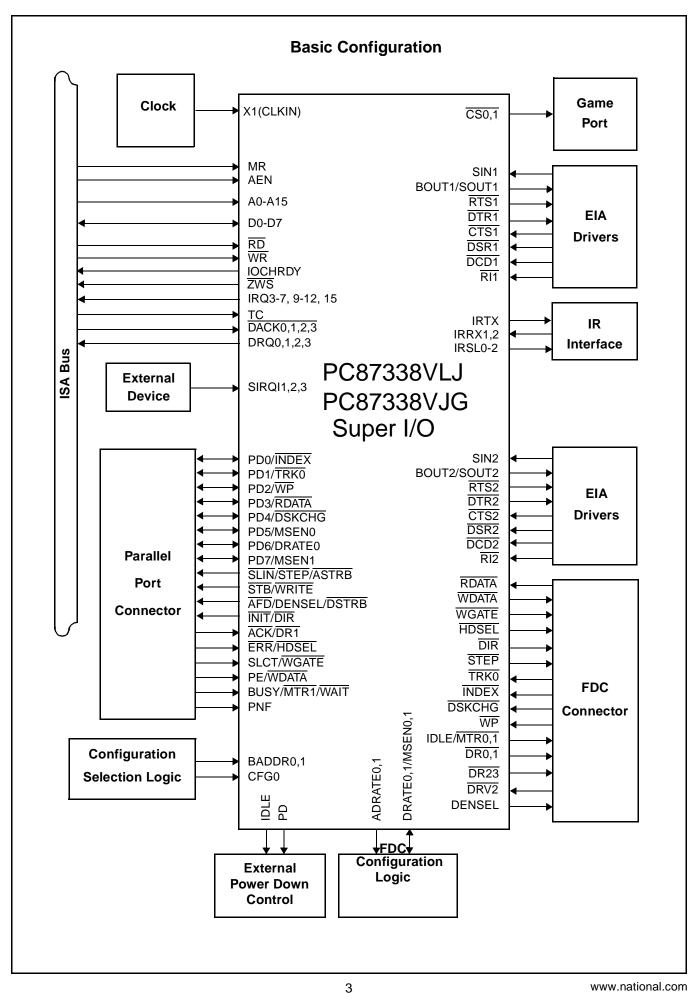

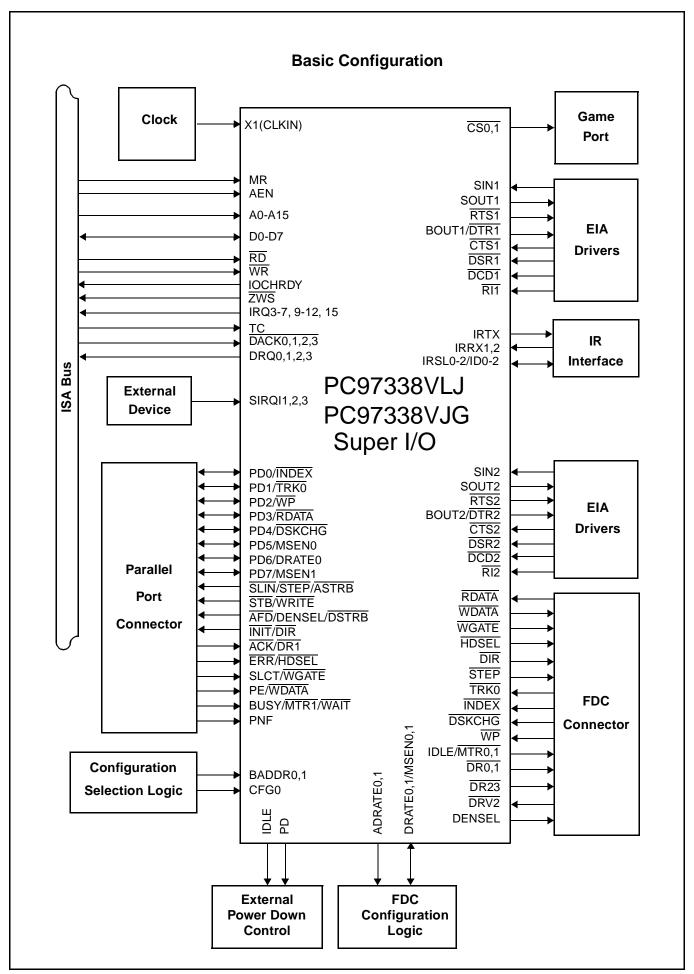

The PC97338 is a fully ACPI 1.0 and PC98/99 compliant, ISA based Super I/O. It is functionally compatible with the PC87338. It includes a Floppy Disk Controller (FDC), two Serial Communication Controllers (SCC) for UART and Infrared support, one IEEE1284 compatible Parallel Port, and two general purpose Chip Select signals for game port support. The device supports power management as well as 3.3V and 5V mixed operation making it particularly suitable for notebook and sub-notebook applications.

The PC87338 and PC97338 are fully compliant to the Plug and Play specifications included in the "Hardware Design Guide for Microsoft Windows 95".

Differences between the PC87338 and PC97338 are indicated in italics. These differences are summarized in Appendix A.

#### **Features**

- Meets ACPI 1.0 and PC98/99 requirements

- Backward compatible with PC87338

- 100% compatibility with Plug and Play requirements specified in the "Hardware Design Guide for Microsoft Windows 95", ISA, EISA, and Micro-Channel architectures

- A special Plug and Play module includes:

- Flexible IRQs, DMAs and base addresses

- General Interrupt Requests (IRQs) that can be multiplexed to the ten supported IRQs

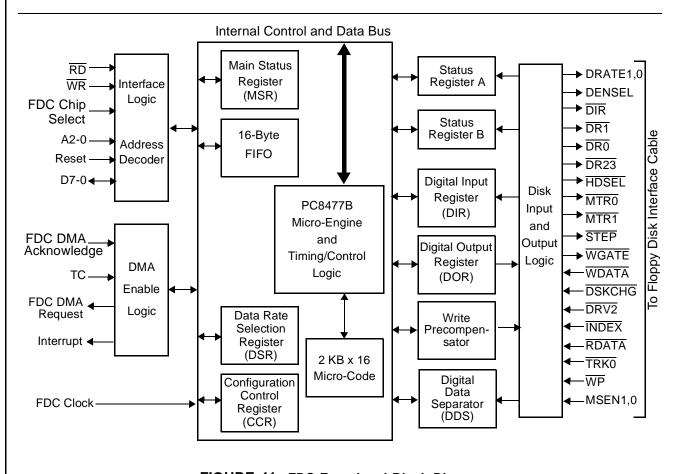

### **Block Diagram**

TRI-STATE<sup>®</sup> is a registered trademark of National Semiconductor Corporation. IBM<sup>®</sup>, MicroChannel<sup>®</sup>, PC-AT<sup>®</sup> and PS/2<sup>®</sup> are registered trademarks of International Business Machines Corporation. Microsoft<sup>®</sup> and Windows<sup>®</sup> are registered trademarks of Microsoft Corporation.

- A new, high performance, on-chip Floppy Disk Controller (FDC) provides:

- Software compatibility with the PC8477, which contains a superset of the floppy disk controller functions in the μDP8473, the NEC μPD765A and the N82077

- A modifiable 13-bit address

- Ten IRQ channel options

- Four 8-bit DMA channel options

- 16-byte FIFO

- Burst and non-burst modes

- Low-power CMOS with enhanced power-down mode

- A new, high-performance, on-chip, digital data separator without external filter components

- Support for 5.25"/3.5" floppy disk drives

- Automatic media sense support

- Perpendicular recording drive support

- Three mode Floppy Disk Drive (FDD) support

- Full support for IBM's Tape Drive Register (TDR) implementation

- Support for new fast tape drives (2 Mbps) and standard tape drives (1 Mbps, 500 Kbps and 250 Kbps)

- Support for both FM and MFM modes.

- Two Serial Communication Controllers provide:

- Software compatibility with the 16550A and the 16450

- A modifiable 13-bit address

- Ten IRQ channel options

- MIDI baud rate support

- Four 8-bit DMA channel options on SCC2

- Shadow register support UART write-only bits

- A fast universal Infrared interface on SCC2 supports the following:

- Data rates of up to 115.2 Kbps (SIR)

- A data rate of 1.152 Mbps (MIR)

- A data rate of 4.0 Mbps (FIR)

- Selectable internal or external modulation/demodulation (Sharp-IR)

- Consumer Electronic IR mode

- A bidirectional parallel port that includes:

- A modifiable 13-bit address

- Ten IRQ channel options

- Four 8-bit DMA channel options

- An Enhanced Parallel Port (EPP) compatible with version EPP 1.9 (IEEE1284 compliant), that also supports version EPP 1.7 of the Xircom specification.

- An Extended Capabilities Port (ECP) that is IEEE1284 compliant, including level 2

- Bidirectional data transfer under either software or hardware control

- Compatibility with ISA, EISA, and MicroChannel parallel ports

- Multiplexing of additional external FDC signals on parallel port pins that enables use of an external Floppy Disk Drive (FDD)

- A protection circuit that prevents damage to the parallel port when an external printer powers up or operates at high voltages

- 14 mA output drivers

- Two general purpose pins for two programmable chip select signals can be programmed for game port control.

- An address decoder that:

- Selects all primary and secondary ISA addresses, including COM1-4 and LPT1-3

- Decodes up to 16 address bits

- Clock source:

- An internal clock multiplier generates all required internal frequencies.

- A clock input source 14.318 MHz, 24 MHz, or 48 MHz may be selected

- Enhanced power management features:

- Special power-down configuration registers

- Enhanced programmable FDC command to trigger power down

- Programmable power-down and wake-up modes

- Two dedicated pins for FDC power management

- Low power-down current consumption (typically for PC97338, 400  $\mu$ A for 3.3V and 600  $\mu$ A for 5V application)

- Reduced pin leakage current

- Low power CMOS technology

- The ability to shut off clocks to either the entire chip or only to specific modules

- Mixed voltage support provides:

- Standard 5 V operation

- Low voltage 3.3 V operation

- Simultaneous internal 3.3 V operation and reception or transmission to devices that have either 3.3 V or 5 V power supply

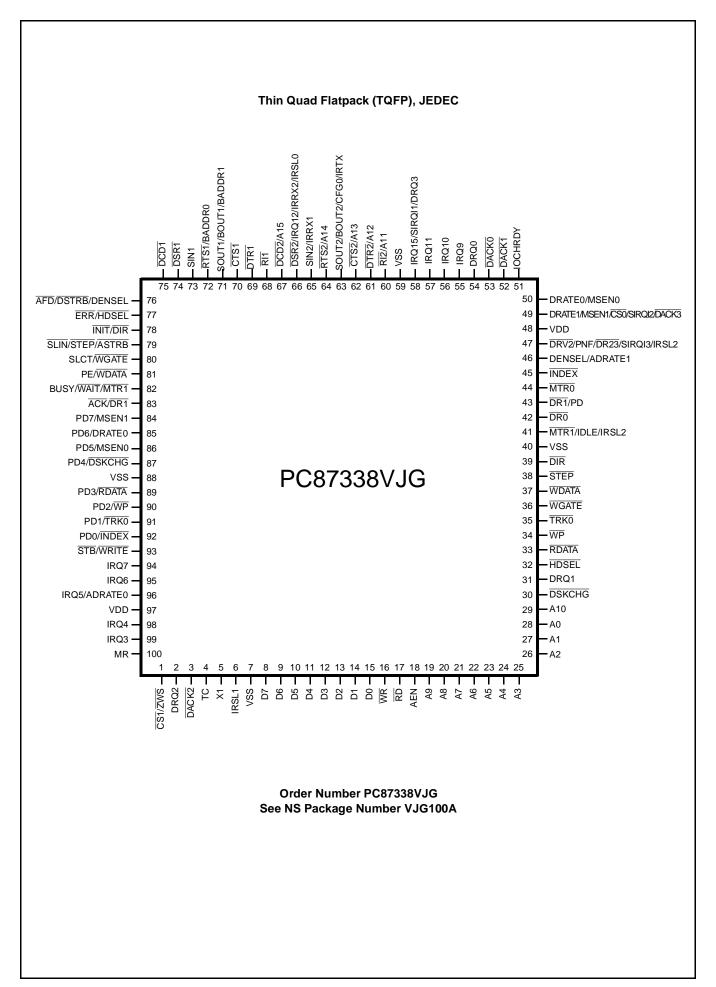

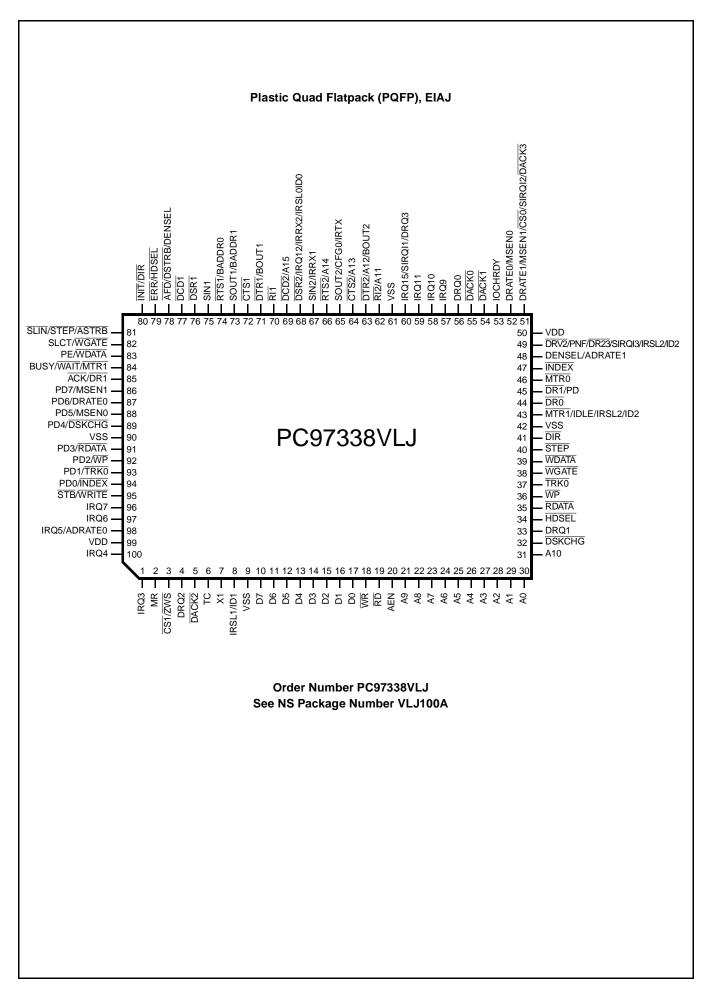

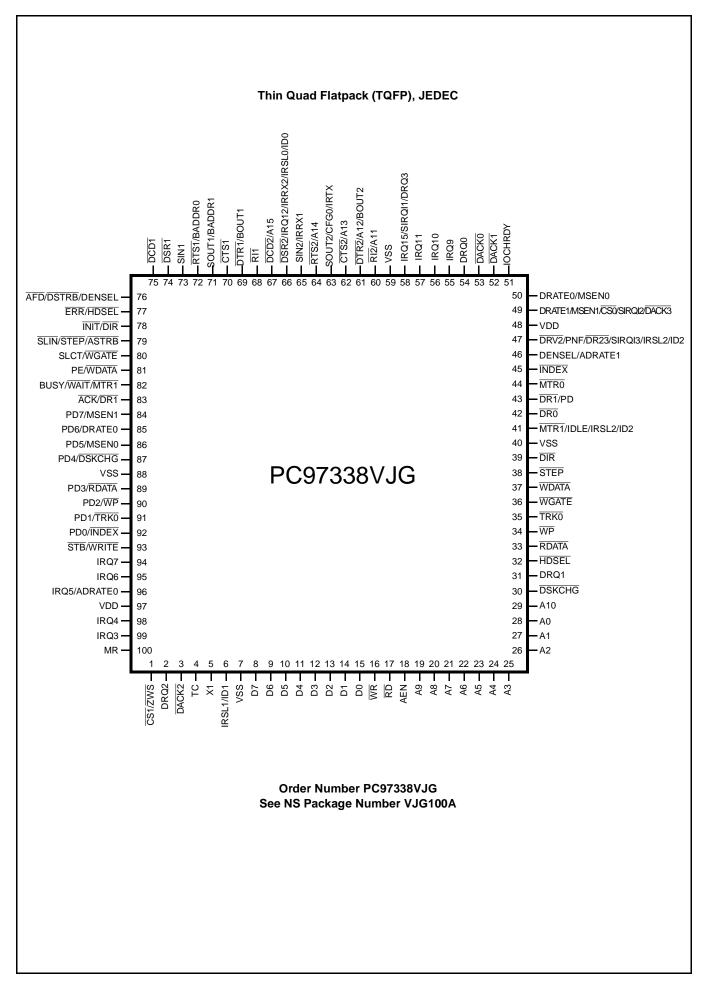

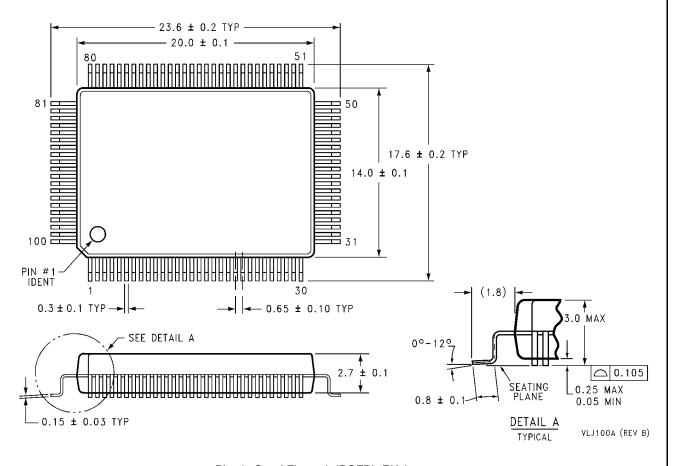

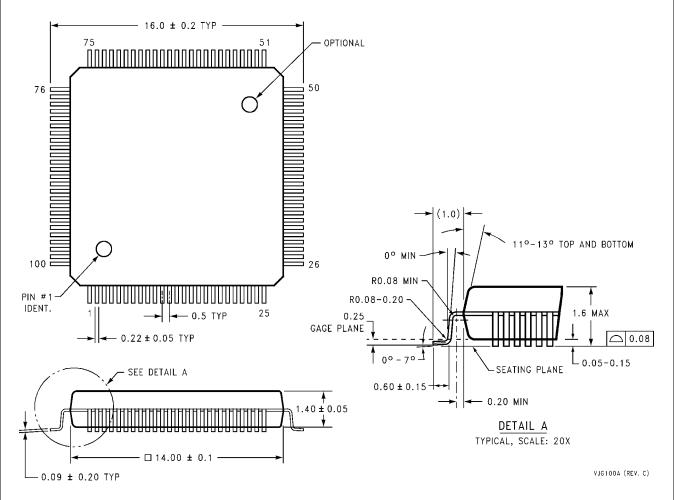

- 100-pin TQFP VJG package PC87338/PC97338

- 100-pin PQFP VLJ package PC87338/PC97338

## **Table of Contents**

| 1.0 Pin Descriptions                                                       |    |

|----------------------------------------------------------------------------|----|

| 1.1 CONNECTION DIAGRAMS                                                    | 18 |

| 1.2 SIGNAL/PIN DESCRIPTIONS                                                | 22 |

| 2.0 Configuration                                                          |    |

| 2.1 OVERVIEW                                                               | 36 |

| 2.2 CONFIGURATION REGISTER SETUP                                           | 36 |

| 2.2.1 Hardware Device Configuration                                        |    |

| 2.2.2 Software Device Configuration                                        |    |

| 2.2.3 Updating Configuration Registers                                     |    |

| 2.2.4 Reserved Bits in Configuration Registers                             |    |

| 2.2.5 INDEX and DATA Register Locations                                    |    |

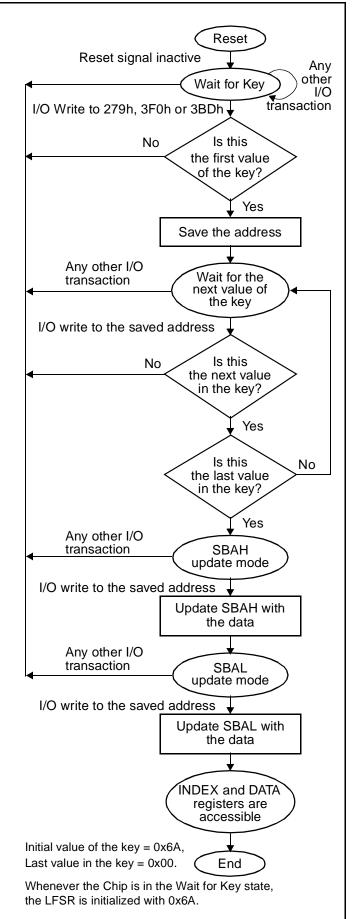

| 2.2.6 Plug and Play Protocol                                               | 39 |

| 2.3 THE CONFIGURATION REGISTERS                                            | 40 |

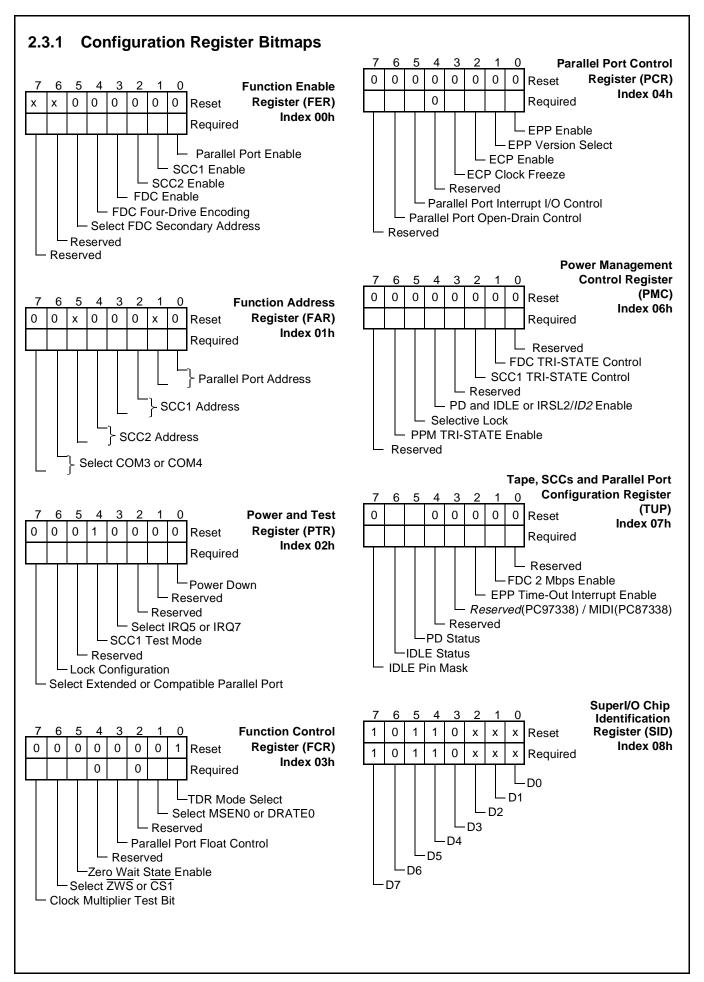

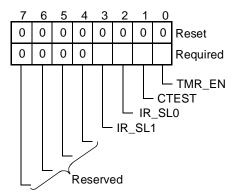

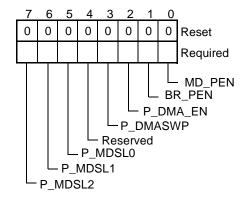

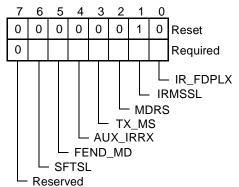

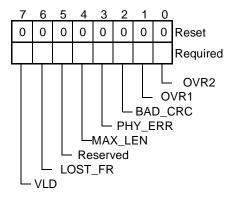

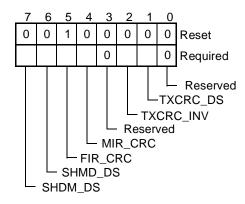

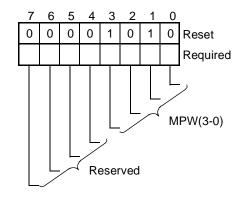

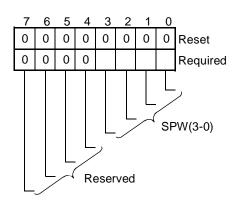

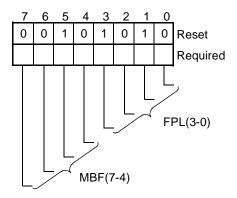

| 2.3.1 Configuration Register Bitmaps                                       | 41 |

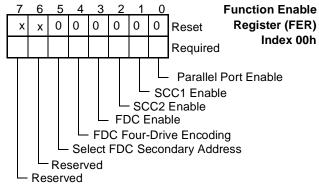

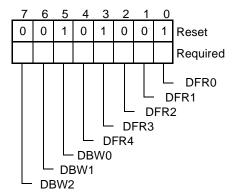

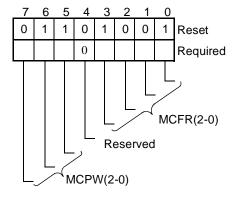

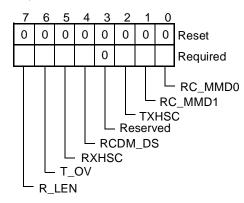

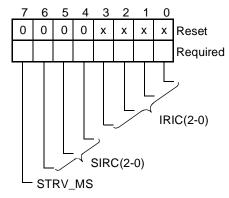

| 2.3.2 Function Enable Register (FER), Index 00h                            | 45 |

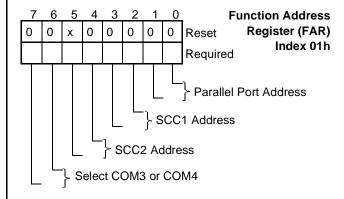

| 2.3.3 Function Address Register (FAR), Index 01h                           | 47 |

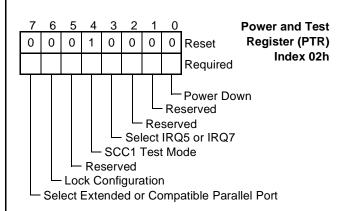

| 2.3.4 Power and Test Register (PTR), Index 02h                             | 47 |

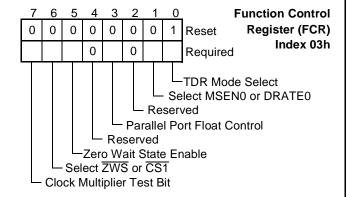

| 2.3.5 Function Control Register (FCR), Index 03h                           | 48 |

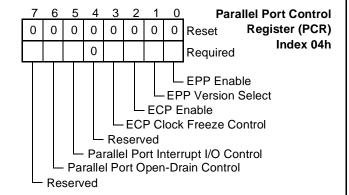

| 2.3.6 Printer Control Register (PCR), Index 04h                            | 49 |

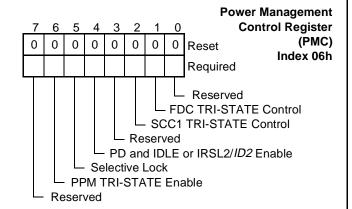

| 2.3.7 Power Management Control Register (PMC), Index 06h                   |    |

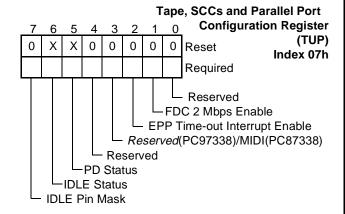

| 2.3.8 Tape, SCCs and Parallel Port Configuration Register (TUP), Index 07h |    |

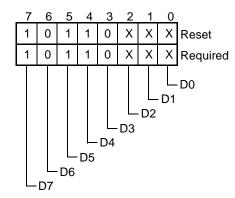

| 2.3.9 SuperI/O Chip Identification Register (SID), Index 08h               |    |

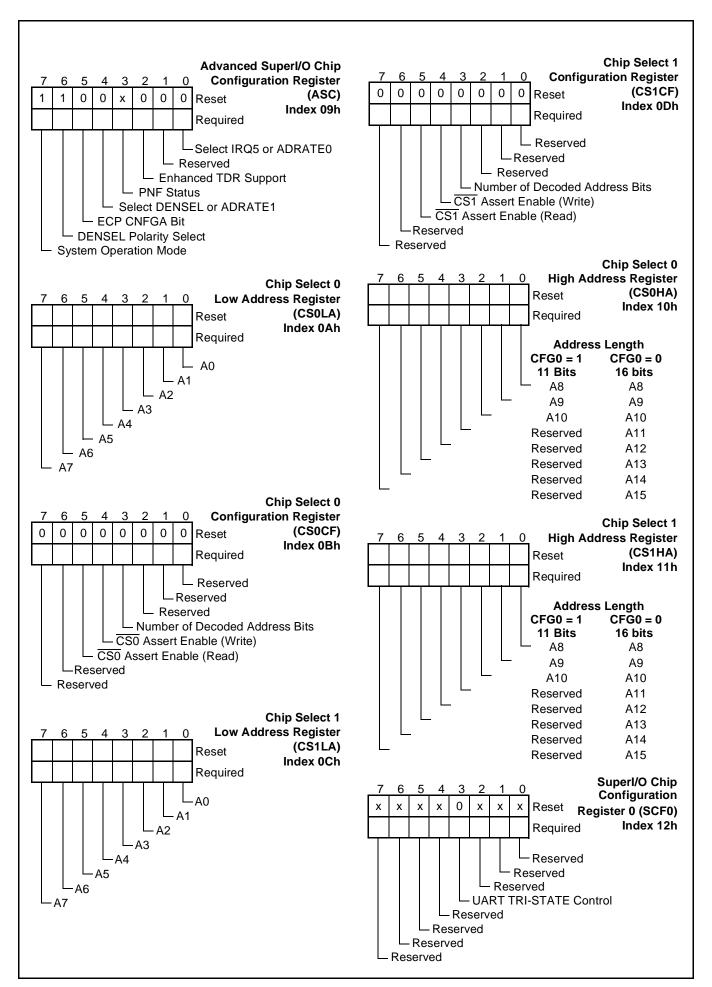

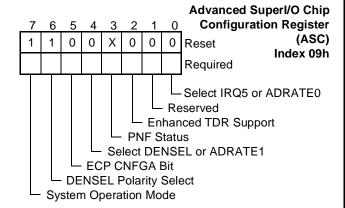

| 2.3.10 Advanced SuperI/O Chip Configuration Register (ASC), Index 09h      |    |

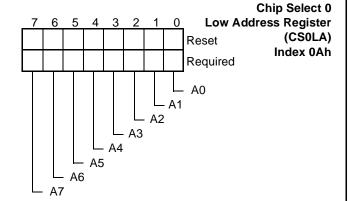

| 2.3.11 Chip Select 0 Low Address Register (CS0LA), Index 0Ah               |    |

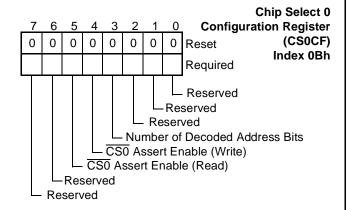

| 2.3.12 Chip Select 0 Configuration Register (CS0CF), Index 0Bh             |    |

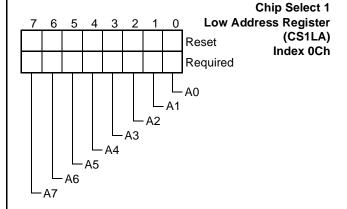

| 2.3.13 Chip Select 1 Low Address Register (CS1LA), Index 0Ch               |    |

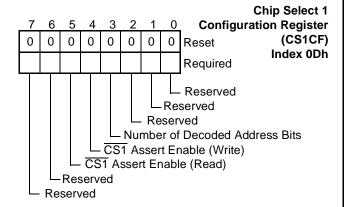

| 2.3.14 Chip Select 1 Configuration Register (CS1CF), Index 0Dh             |    |

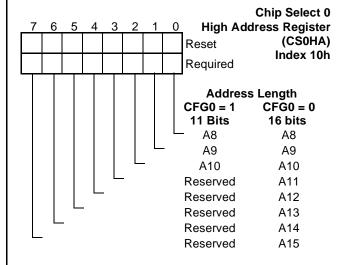

| 2.3.15 Chip Select 0 High Address Register (CS0HA), Index 10h              |    |

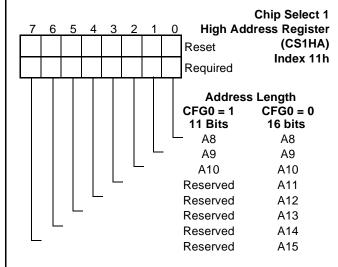

| 2.3.16 Chip Select 1 High Address Register (CS1HA), Index 11h              |    |

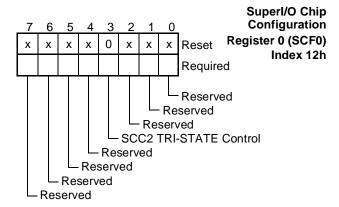

| 2.3.17 SuperI/O Chip Configuration Register 0 (SCF0), Index 12h            |    |

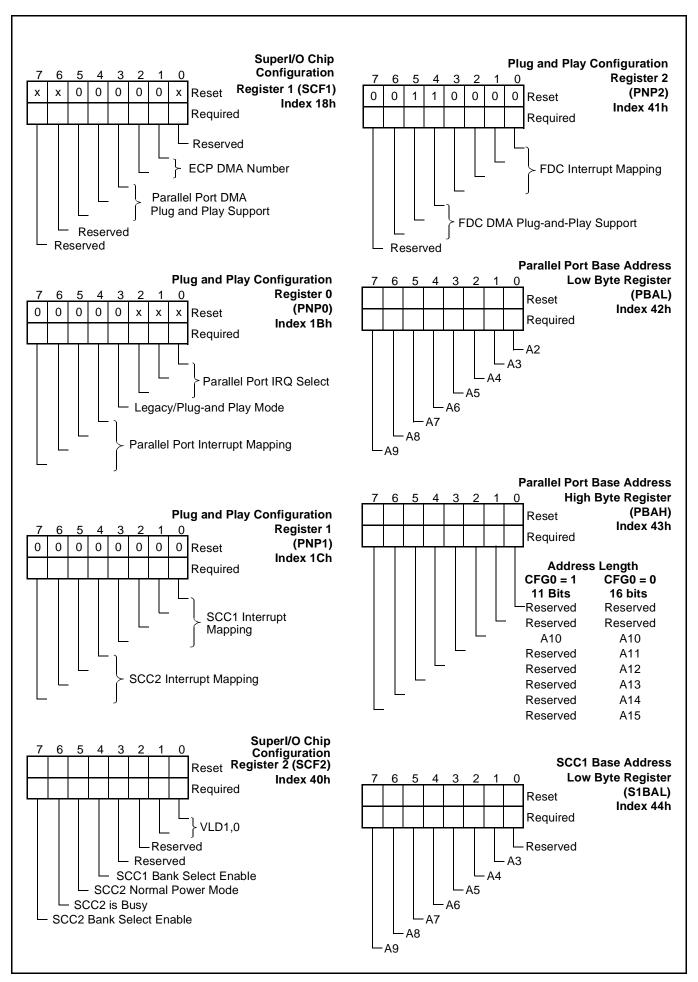

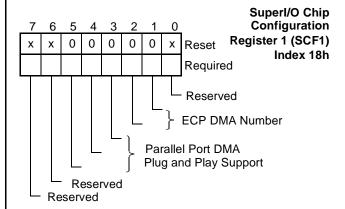

| 2.3.18 SuperI/O Chip Configuration Register 1 (SCF1), Index 18h            |    |

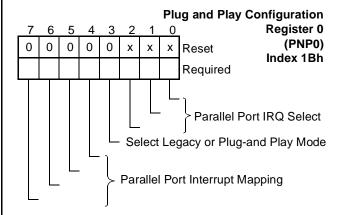

| 2.3.19 Plug and Play Configuration 0 Register (PNP0), Index 1Bh            |    |

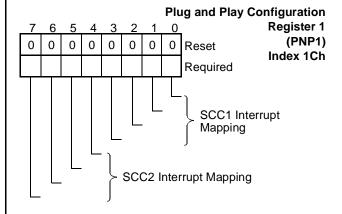

| 2.3.20 Plug and Play Configuration 1 Register (PNP1), Index 1Ch            |    |

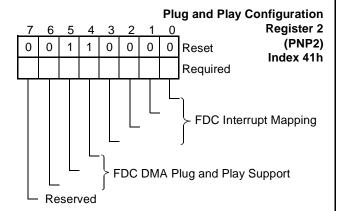

| 2.3.22 Plug and Play Configuration 2 Register (PNP2), Index 41h            |    |

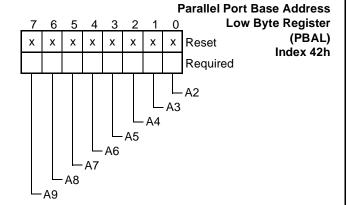

| 2.3.23 Parallel Port Base Address Low Byte Register (PBAL), Index 41h      |    |

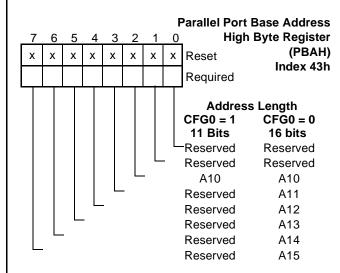

| 2.3.24 Parallel Port Base Address High Byte Register (PBAH), Index 42h     |    |

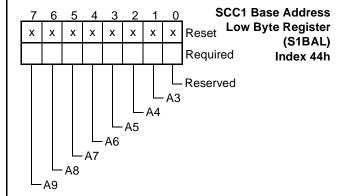

| 2.3.25 SCC1 Base Address Low Byte Register (S1BAL), Index 44h              |    |

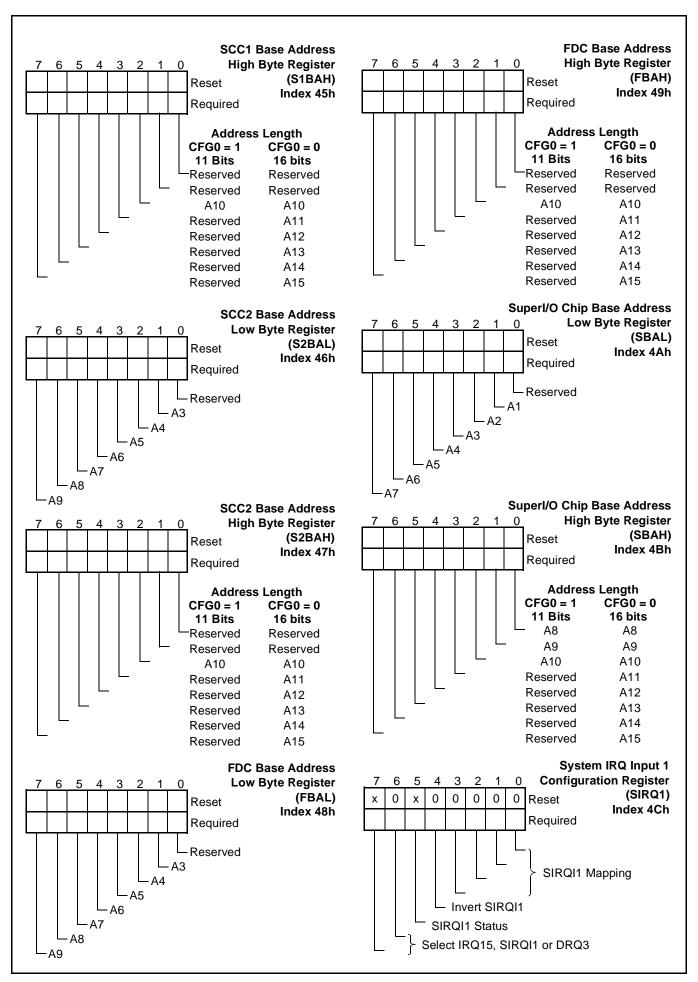

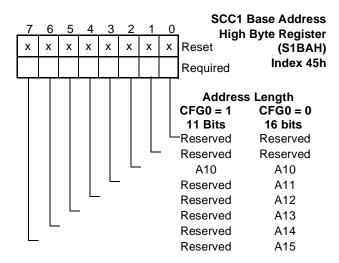

| 2.3.26 SCC1 Base Address High Byte Register (S1BAH), Index 44h             |    |

| 2.3.27 SCC1 Base Address Fight Byte Register (S1BAH), Index 45H            |    |

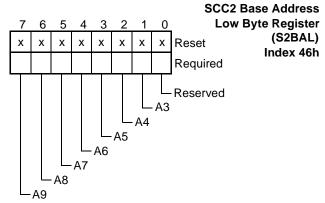

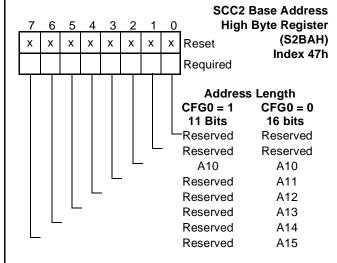

| 2.3.28 SCC2 Base Address High Byte Register (S2BAH), Index 47h             |    |

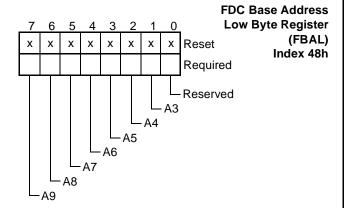

| 2.3.29 FDC Base Address Low Byte Register (FBAL), Index 48h                |    |

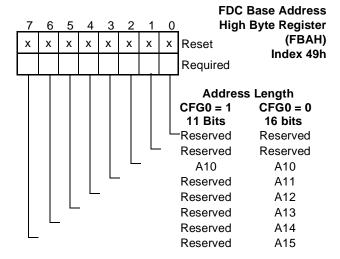

| 2.3.30 FDC Base Address High Byte Register (FBAH.) Index 49h               |    |

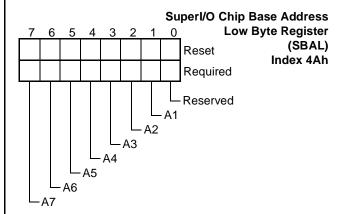

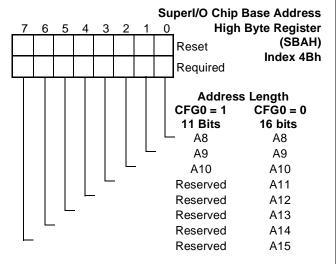

| 2.3.31 SIO Base Address Low Byte Register (SBAL), Index 4Ah         |    |

|---------------------------------------------------------------------|----|

| 0.000.010. December 11' 1. D. (c. D. c.) (c. (ODALI). Le le 14DI    | 63 |

| 2.3.32 SIO Base Address High Byte Register (SBAH), Index 4Bh        |    |

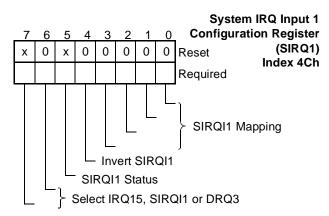

| 2.3.33 System IRQ Input 1 Configuration Register (SIRQ1), Index 4Ch | 63 |

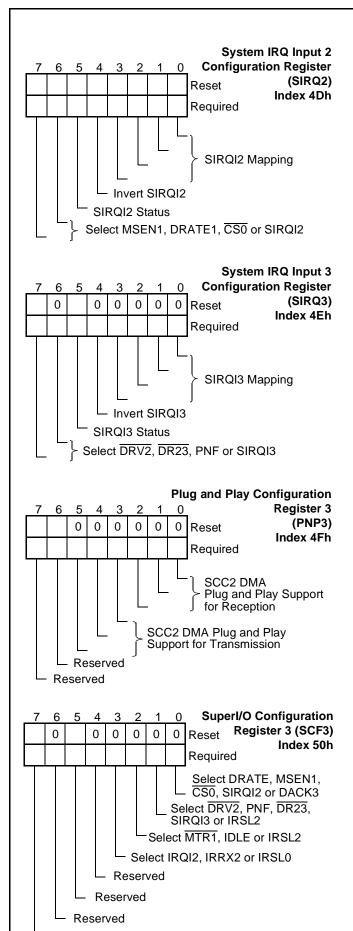

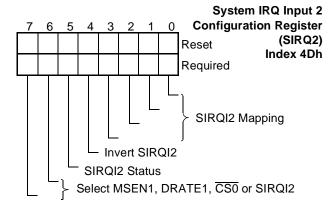

| 2.3.34 System IRQ Input 2 Configuration Register (SIRQ2), Index 4Dh | 64 |

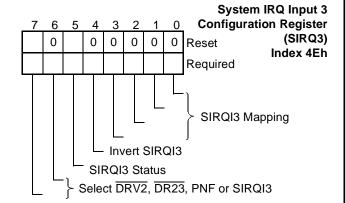

| 2.3.35 System IRQ Input 3 Configuration Register (SIRQ3), Index 4Eh | 65 |

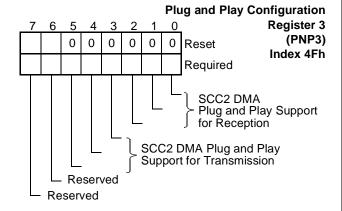

| 2.3.36 Plug-and-Play Configuration 3 Register (PNP3), Index 4Fh     | 66 |

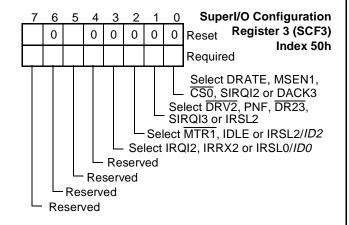

| 2.3.37 SuperI/O Configuration 3 Register (SCF3), Index 50h          | 67 |

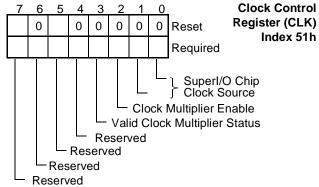

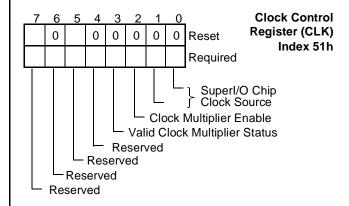

| 2.3.38 Clock Control Register (CLK), Index 51h                      | 68 |

| 2.3.39 Manufacturing Test Register (MTEST), Index 52h               | 68 |

| 3.0 The Digital Floppy Disk Controller (FDC)                        |    |

| 3.1 FDC FUNCTIONS                                                   | 69 |

| 3.1.1 Microprocessor Interface                                      | 69 |

| 3.1.2 System Operation Modes                                        | 70 |

| 3.2 DATA TRANSFER                                                   | 70 |

| 3.2.1 Data Rates                                                    |    |

| 3.2.2 The Data Separator                                            |    |

| 3.2.3 Perpendicular Recording Mode Support                          |    |

| 3.2.4 Data Rate Selection                                           |    |

| 3.2.5 Write Precompensation                                         |    |

| 3.2.6 FDC Low-Power Mode Logic                                      |    |

| 3.2.7 Reset                                                         |    |

| 3.3 THE REGISTERS OF THE FDC                                        |    |

| 3.3.1 FDC Register Bitmaps                                          |    |

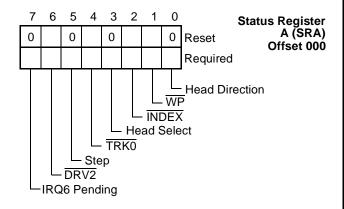

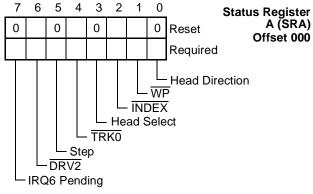

| 3.3.2 Status Register A (SRA), Offset 000                           |    |

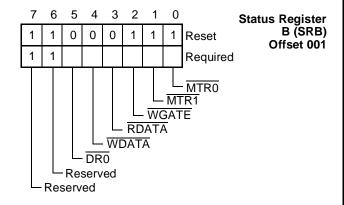

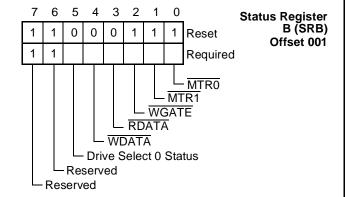

| 3.3.3 Status Register B (SRB), Offset 001                           |    |

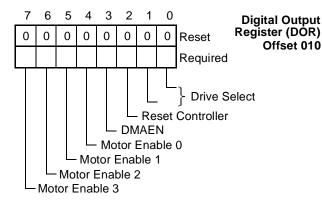

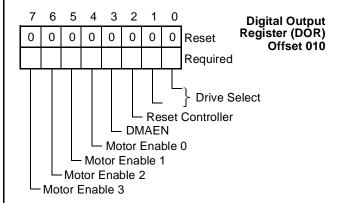

| 3.3.4 Digital Output Register (DOR), Offset 010                     |    |

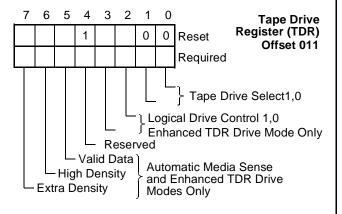

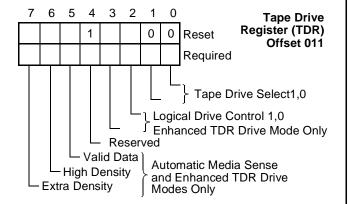

| 3.3.5 Tape Drive Register (TDR), Offset 011                         |    |

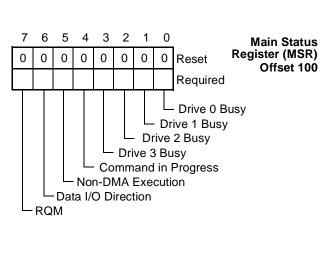

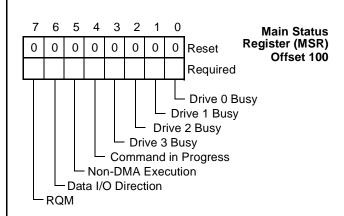

| 3.3.6 Main Status Register (MSR), Offset 100                        |    |

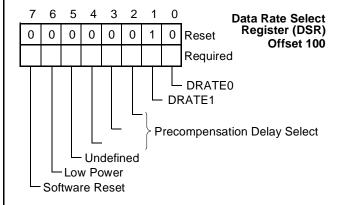

| 3.3.7 Data Rate Select Register (DSR), Offset 100                   |    |

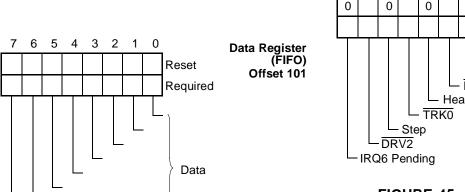

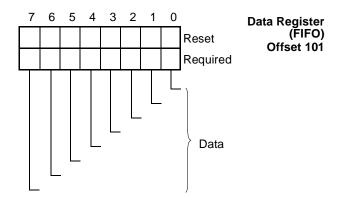

| 3.3.8 Data Register (FIFO), Offset 101                              |    |

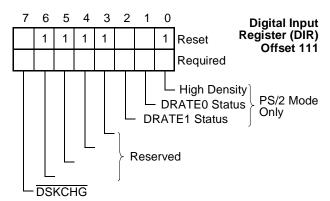

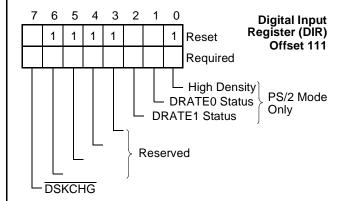

| 3.3.9 Digital Input Register (DIR), Offset 111                      |    |

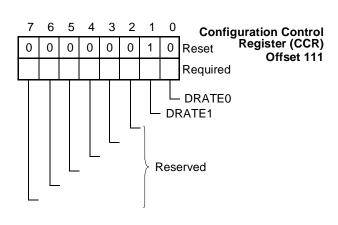

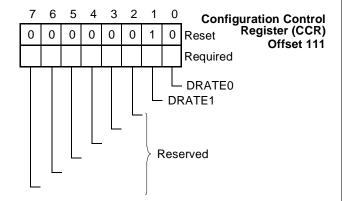

| 3.3.10 Configuration Control Register (CCR), Offset 111             |    |

|                                                                     |    |

| 3.4 THE PHASES OF FDC COMMANDS                                      |    |

| 3.4.1 Command Phase                                                 |    |

| 3.4.2 Execution Phase                                               |    |

| 3.4.4 Idle Phase                                                    |    |

| 3.4.5 Drive Polling Phase                                           |    |

| Ç .                                                                 |    |

| 3.5 THE RESULT PHASE STATUS REGISTERS                               |    |

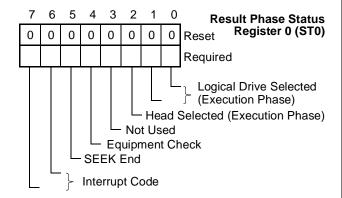

| 3.5.1 Result Phase Status Register 0 (ST0)                          |    |

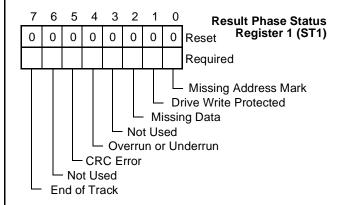

| 3.5.2 Result Phase Status Register 1 (ST1)                          |    |

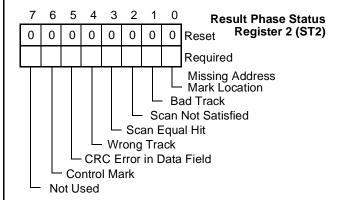

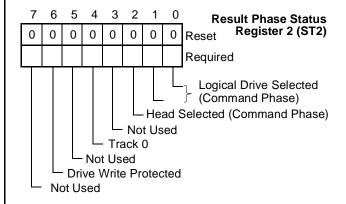

| 3.5.3 Result Phase Status Register 2 (ST2)                          |    |

| 3.5.4 Result Phase Status Register 3 (ST3)                          |    |

| 3.6 THE FDC COMMAND SET                                             |    |

| 3.6.1 Abbreviations Used in FDC Commands                            | 92 |

| 3.6.2 The CONFIGURE Command                                                      | 94  |

|----------------------------------------------------------------------------------|-----|

| 3.6.3 The DUMPREG Command                                                        | 95  |

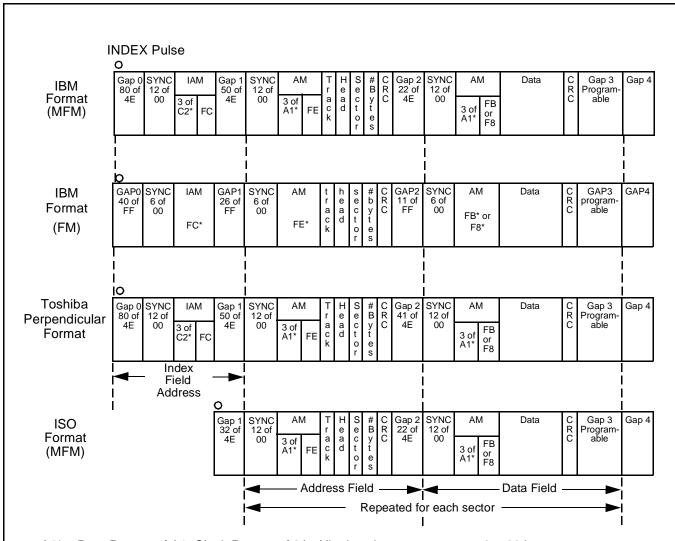

| 3.6.4 The FORMAT TRACK Command                                                   | 96  |

| 3.6.5 The INVALID Command                                                        | 99  |

| 3.6.6 The LOCK Command                                                           | 100 |

| 3.6.7 The MODE Command                                                           | 100 |

| 3.6.8 The NSC Command                                                            | 103 |

| 3.6.9 The PERPENDICULAR MODE Command                                             | 103 |

| 3.6.10 The READ DATA Command                                                     | 105 |

| 3.6.11 The READ DELETED DATA Command                                             | 108 |

| 3.6.12 The READ ID Command                                                       | 109 |

| 3.6.13 The READ A TRACK Command                                                  | 110 |

| 3.6.14 The RECALIBRATE Command                                                   | 110 |

| 3.6.15 The RELATIVE SEEK Command                                                 | 111 |

| 3.6.16 The SCAN EQUAL, the SCAN LOW OR EQUAL and the SCAN HIGH OR EQUAL Commands | 112 |

| 3.6.17 The SEEK Command                                                          | 113 |

| 3.6.18 The SENSE DRIVE STATUS Command                                            | 114 |

| 3.6.19 The SENSE INTERRUPT Command                                               | 114 |

| 3.6.20 The SET TRACK Command                                                     | 115 |

| 3.6.21 The SPECIFY Command                                                       | 116 |

| 3.6.22 The VERIFY Command                                                        | 118 |

| 3.6.23 The VERSION Command                                                       | 119 |

| 3.6.24 The WRITE DATA Command                                                    | 120 |

| 3.6.25 The WRITE DELETED DATA Command                                            | 121 |

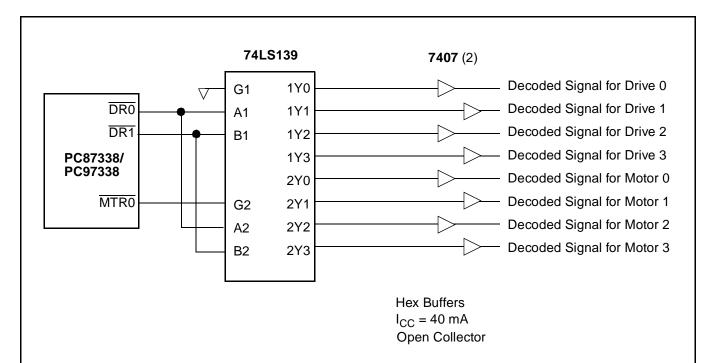

| 3.7 EXAMPLE OF A FOUR-DRIVE CIRCUIT USING THE PC87338/PC97338                    | 121 |

| O. P. EXXIVII. EE OF AT CORE DRIVE CIRCOTT COINCE THE P. COPOCOT COTOCO          |     |

| 4.0 Parallel Port                                                                |     |

| 4.1 INTRODUCTION                                                                 | 123 |

| 4.1.1 The Chip Parallel Port Modes                                               | 123 |

| 4.1.2 Device Configuration                                                       | 123 |

| 4.2 STANDARD PARALLEL PORT MODES                                                 | 123 |

| 4.2.1 Standard Parallel Port (SPP) Modes Register Set                            | 124 |

| 4.2.2 SPP Mode Parallel Port Register Bitmaps                                    |     |

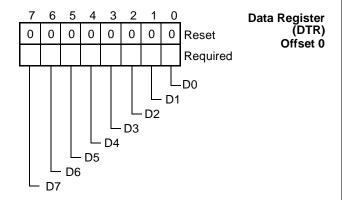

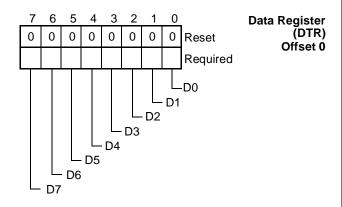

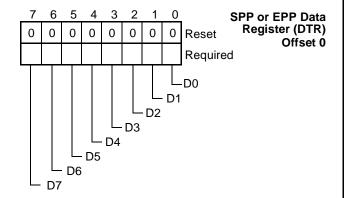

| 4.2.3 Data Register (DTR), Offset 0                                              |     |

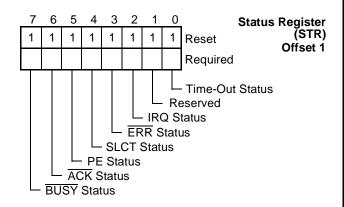

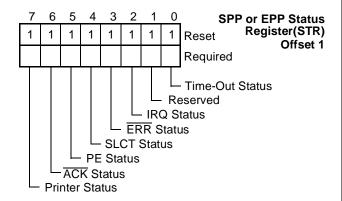

| 4.2.4 Status Register (STR), Offset 1                                            |     |

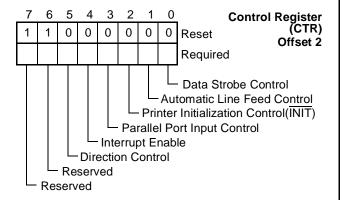

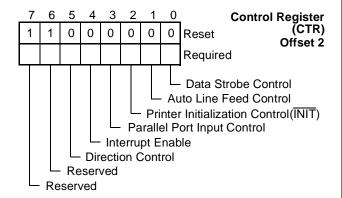

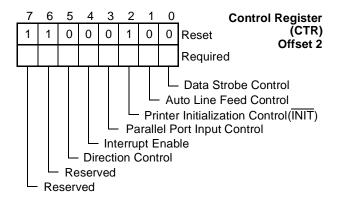

| 4.2.5 Control Register (CTR), Offset 2                                           |     |

| 4.3 ENHANCED PARALLEL PORT (EPP) MODES                                           |     |

| 4.3.1 Enhanced Parallel Port (EPP) Modes Register Set                            |     |

| , ,                                                                              |     |

| 4.3.2 EPP Modes Parallel Port Register Bitmaps                                   |     |

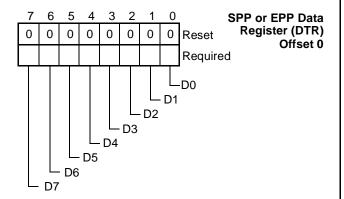

| 4.3.3 SPP or EPP Data Register (DTR), Offset 0                                   |     |

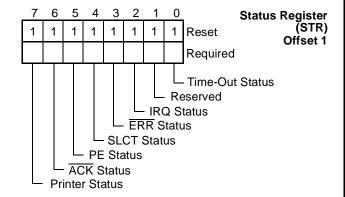

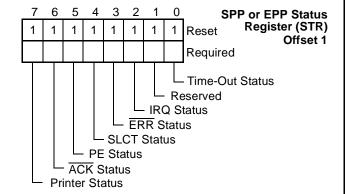

| 4.3.4 SPP or EPP Status Register (STR), Offset 1                                 |     |

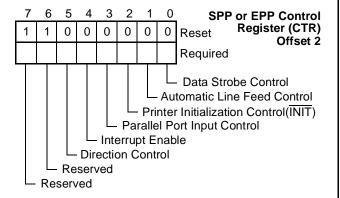

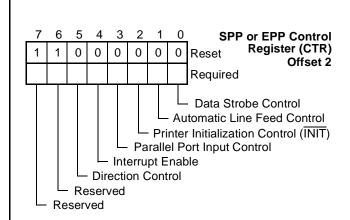

| 4.3.5 SPP or EPP Control Register (CTR), Offset 2                                |     |

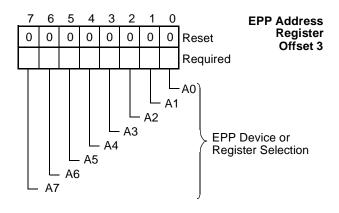

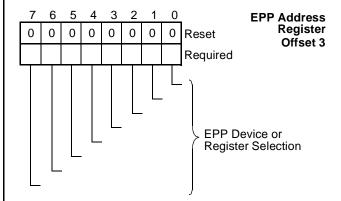

| 4.3.6 EPP Address Register, Offset 3                                             |     |

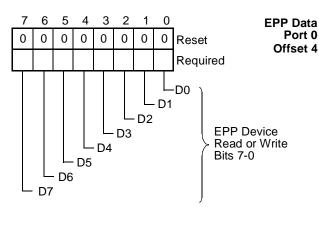

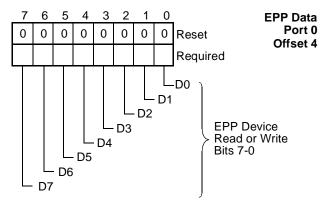

| 4.3.7 EPP Data Port 0, Offset 4                                                  |     |

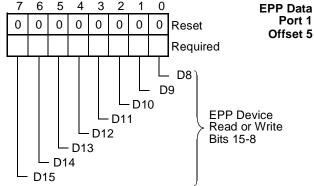

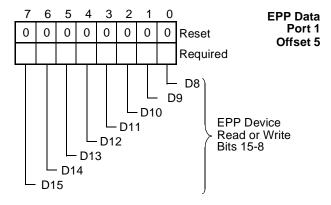

| 4.3.8 EPP Data Port 1, Offset 5                                                  |     |

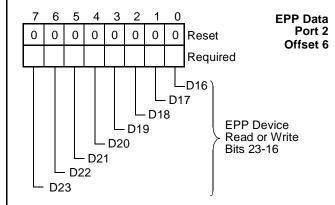

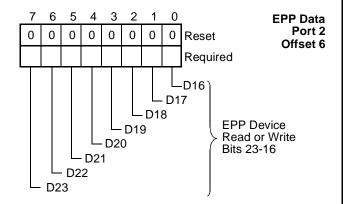

| 4.3.9 EPP Data Port 2, Offset 6                                                  | 130 |

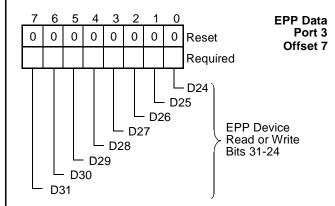

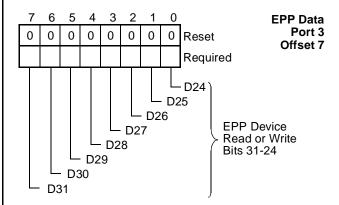

| 4.3.10 EPP Data Port 3, Offset 7                                                   | 131 |

|------------------------------------------------------------------------------------|-----|

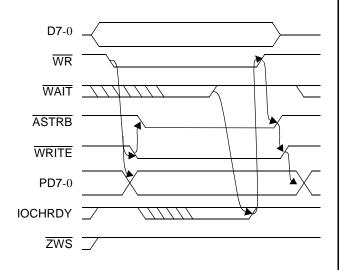

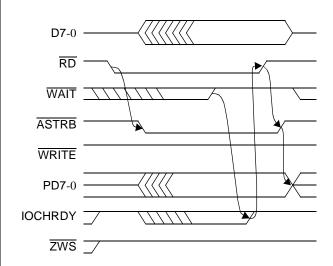

| 4.3.11 EPP Mode Transfer Operations                                                | 131 |

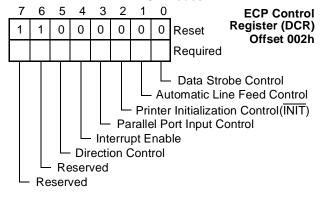

| 4.4 EXTENDED CAPABILITIES PARALLEL PORT (ECP) MODES                                | 133 |

| 4.4.1 Accessing the ECP Registers                                                  |     |

| 4.4.2 Software Operation in ECP Modes                                              |     |

| 4.4.3 Hardware Operation in ECP Modes                                              |     |

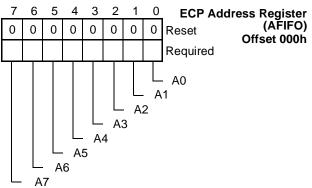

| 4.4.4 ECP Modes Parallel Port Register Bitmaps                                     |     |

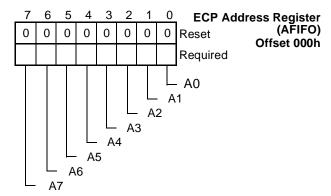

| 4.4.6 ECP Address FIFO (AFIFO) Register, Bits 7-5 of ECR = 011, Offset 000h        |     |

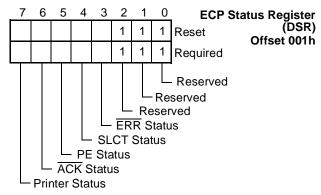

| 4.4.7 ECP Status Register (DSR), Offset 001h                                       |     |

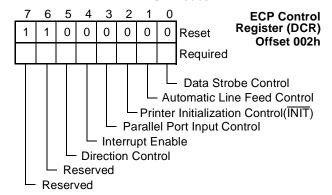

| 4.4.8 ECP Control Register (DCR), Offset 002h                                      | 137 |

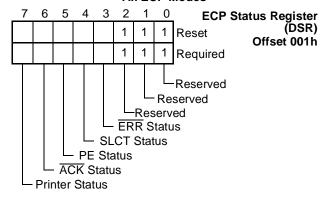

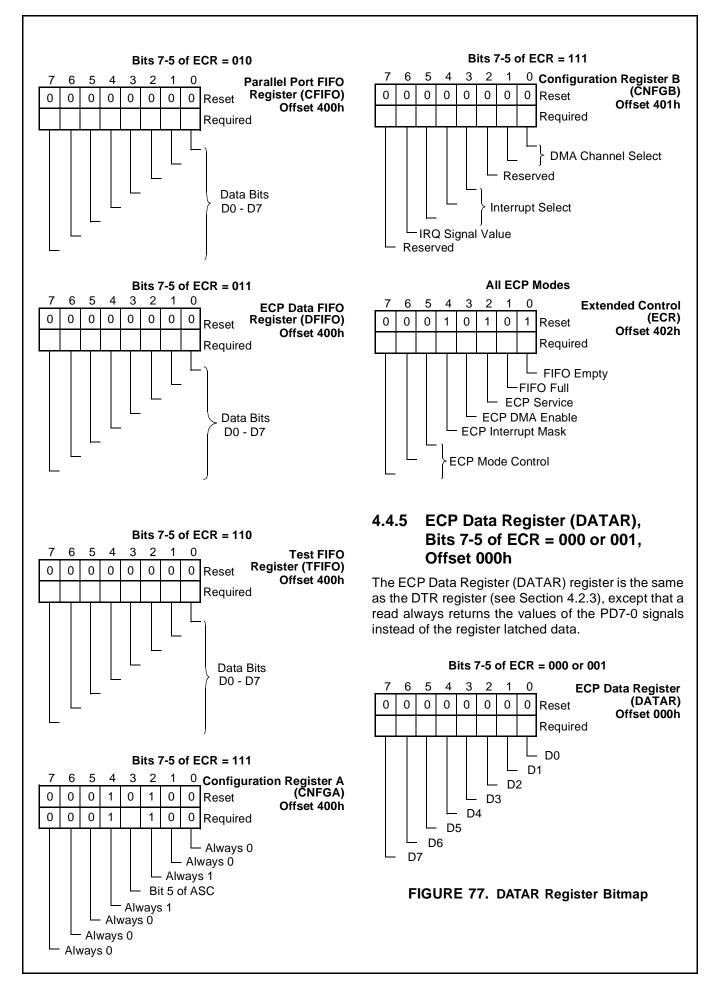

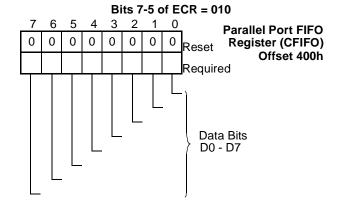

| 4.4.9 Parallel Port Data FIFO (CFIFO) Register, Bits 7-5 of ECR = 010, Offset 400h |     |

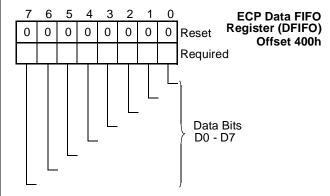

| 4.4.10 ECP Data FIFO (DFIFO) Register, Bits 7-5 of ECR = 011, Offset 400h          |     |

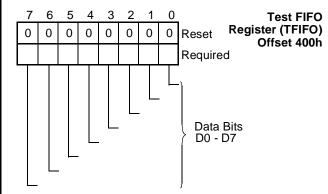

| 4.4.11 Test FIFO (TFIFO) Register, Bits 7-5 of ECR = 110, Offset 400h              |     |

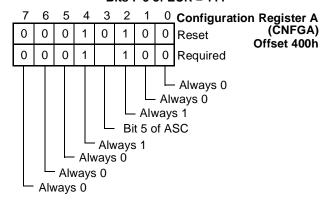

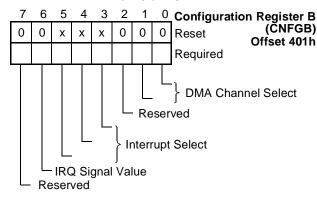

| 4.4.12 Configuration Register A (CNFGA), Bits 7-5 of ECR = 111, Offset 400h        |     |

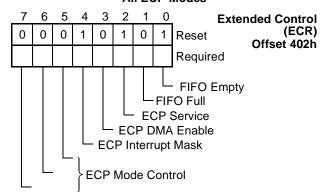

| 4.4.14 Extended Control Register (ECR), Offset 402h                                |     |

| 4.5 ECP MODE DESCRIPTIONS                                                          |     |

| 4.5.1 Software Controlled Data Transfer (Modes 000 and 001)                        |     |

| 4.5.2 Automatic Data Transfer (Modes 010 and 011)                                  |     |

| 4.5.3 FIFO Test Access (Mode 110)                                                  |     |

| 4.5.4 Configuration Registers Access (Mode 111)                                    |     |

| 4.5.5 Interrupt Generation                                                         | 143 |

| 4.6 THE PARALLEL PORT MULTIPLEXER (PPM)                                            | 144 |

| 4.7 PARALLEL PORT PIN/SIGNAL LIST                                                  | 144 |

| 5.0 Serial Communications Controllers (SCC1 and SCC2)                              |     |

| 5.1 FEATURES                                                                       | 146 |

| 5.2 FUNCTIONAL MODES OVERVIEW                                                      | 146 |

| 5.3 UART MODE                                                                      | 146 |

| 5.4 SHARP-IR MODE                                                                  | 147 |

| 5.5 IRDA 1.0 SIR MODE                                                              |     |

| 5.6 IRDA 1.1 MIR AND FIR MODES                                                     |     |

| 5.6.1 High Speed Infrared Transmit Operation                                       |     |

| 5.6.2 High Speed Infrared Receive Operation                                        |     |

| 5.7 CONSUMER ELECTRONIC IR (CEIR) MODE                                             | 149 |

| 5.7.1 CEIR Transmit Operation                                                      |     |

| 5.7.2 CEIR Receive Operation                                                       | 150 |

| 5.8 FIFO TIME-OUTS                                                                 | 150 |

| 5.9 TRANSMIT DEFERRAL                                                              | 151 |

| 5.10 AUTOMATIC FALLBACK TO 16550 COMPATIBILITY MODE                                | 151 |

| 5.11 PIPELINING                                                                    | 152 |

| 5.12 OPTICAL TRANSCEIVER INTERFACE                                                 |     |

|                                                                                    |     |

| 5.14 BANK 0                                                        |  |

|--------------------------------------------------------------------|--|

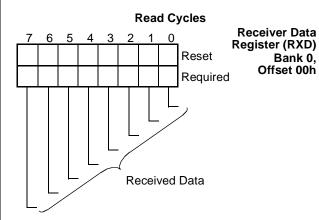

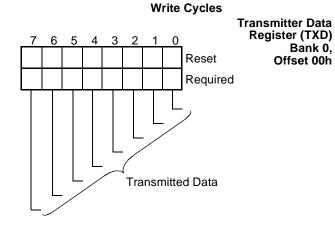

| 5.14.1 TXD/RXD – Transmit/Receive Data Ports                       |  |

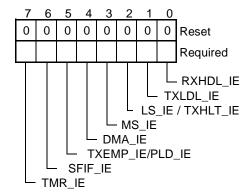

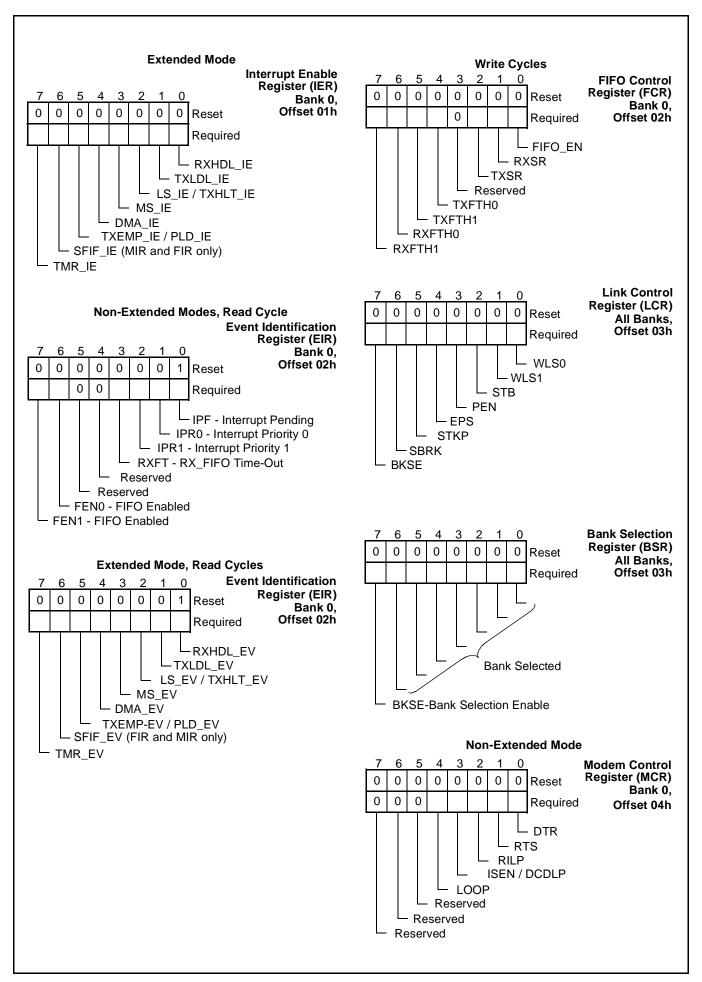

| 5.14.2 IER – Interrupt Enable Register                             |  |

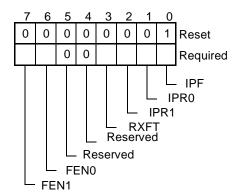

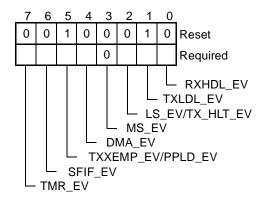

| 5.14.3 EIR/FCR – Event Identification/FIFO Control Registers       |  |

| 5.14.4 LCR/BSR – Link Control/Bank Select Register                 |  |

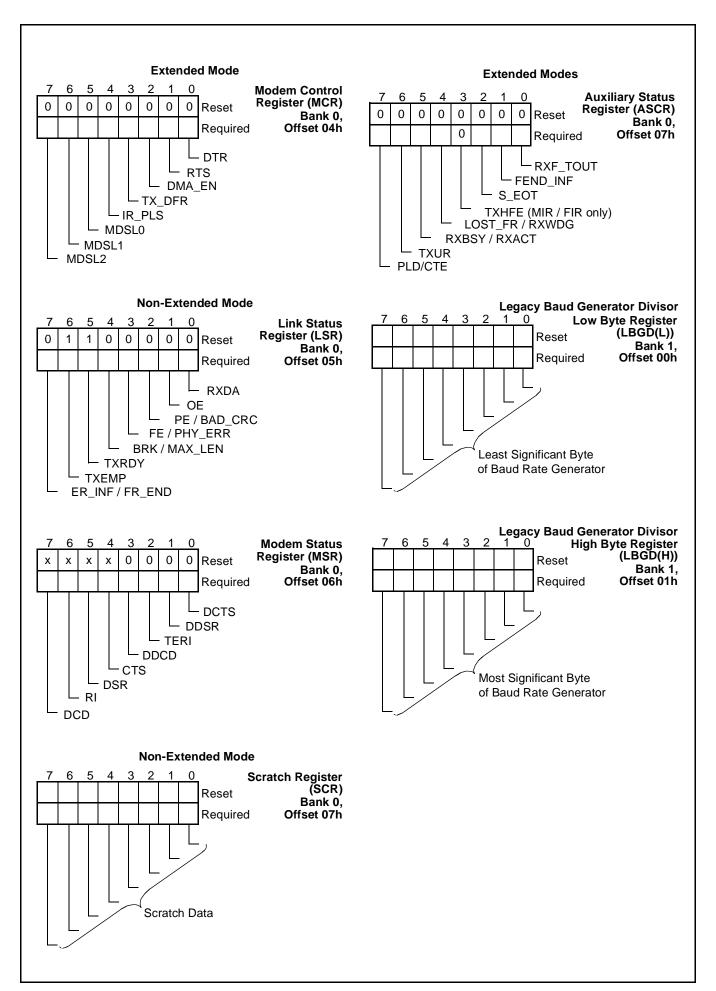

| 5.14.5 MCR – Modem/Mode Control Register                           |  |

| 5.14.6 LSR – Link Status Register                                  |  |

| 5.14.7 MSR – Modem Status Register                                 |  |

| 5.14.8 SPR/ASCR – Scratchpad/Auxiliary Status and Control Register |  |

| 5.15 BANK 1                                                        |  |

| 5.15.1 LBGD – Legacy Baud Generator Divisor Port                   |  |

| 5.15.2 LCR/BSR – Link Control/Bank Select Registers                |  |

| 5.16 BANK 2                                                        |  |

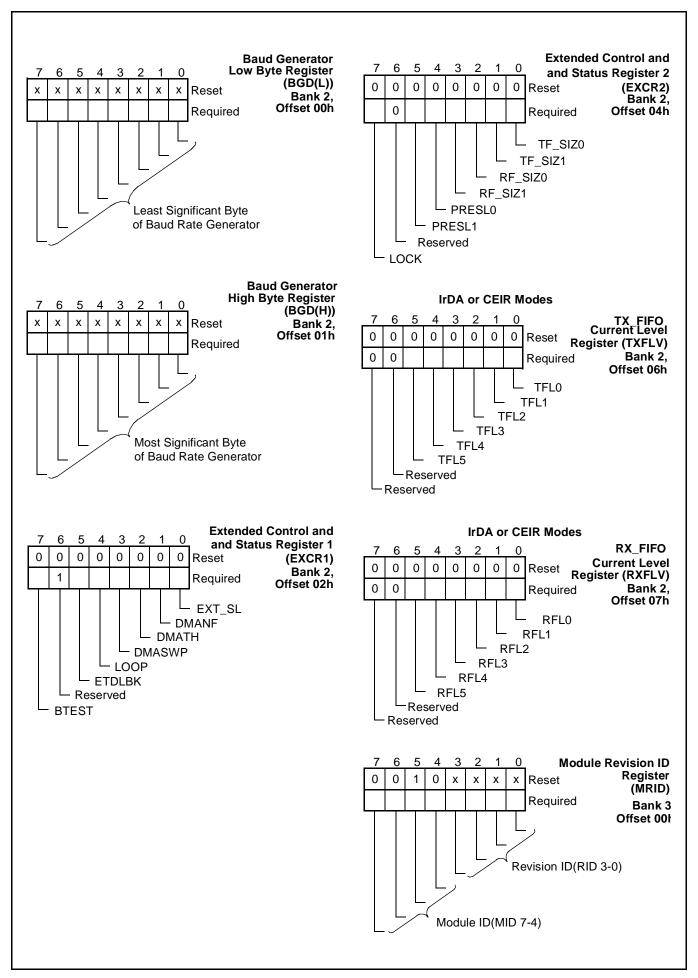

| 5.16.1 BGD – Baud Generator Divisor Port                           |  |

| 5.16.2 EXCR1 – Extended Control Register 1                         |  |

| 5.16.3 LCR/BSR – Link Control/Bank Select Registers                |  |

| 5.16.4 EXCR2 – Extended Control Register 2                         |  |

| 5.16.5 TXFLV - TX_FIFO Level, Read-Only                            |  |

| 5.16.6 RXFLV – RX_FIFO Level, Read-Only                            |  |

| 5.17 BANK 3                                                        |  |

| 5.17.1 MID – Module Identification Register, Read Only             |  |

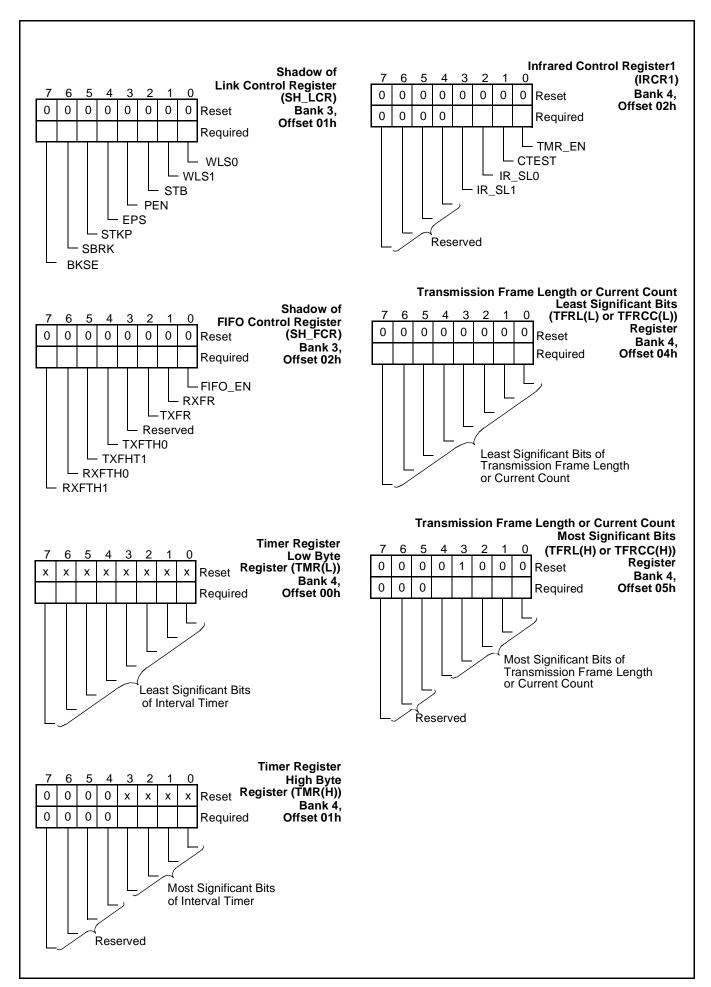

| 5.17.2 SH_LCR – Link Control Register Shadow, Read Only            |  |

| 5.17.3 SH_FCR – FIFO Control Register Shadow, Read-Only            |  |

| 5.17.4 LCR/BSR – Link Control/Bank Select Registers                |  |

| 5.18 BANK 4                                                        |  |

| 5.18.1 TMR – Timer Register                                        |  |

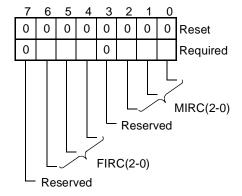

| 5.18.2 IRCR1 – Infrared Control Register 1                         |  |

| 5.18.3 LCR/BSR – Link Control/Bank Select Registers                |  |

| 5.18.4 TFRL/TFRCC – Transmitter Frame-Length/Current-Count         |  |

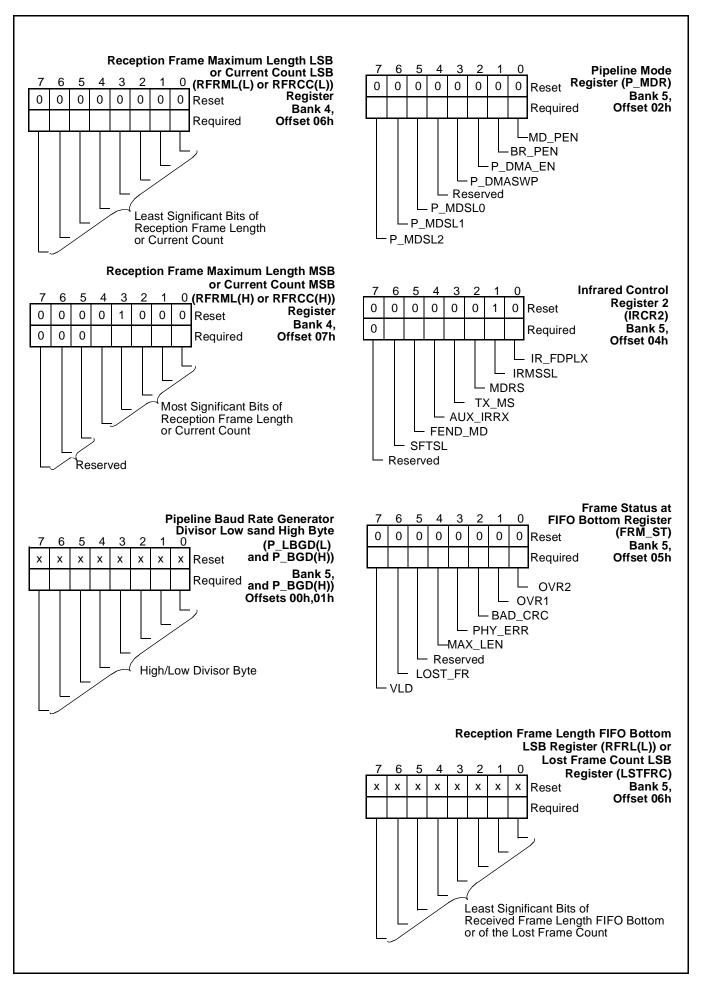

| 5.18.5 RFRML/RFRCC – Receiver Frame Maximum-Length/Current-Count   |  |

| 5.19 BANK 5                                                        |  |

| 5.19.1 P_BGD – Pipelined Baud Generator Divisor Register           |  |

| 5.19.2 P_MDR – Pipelined Mode Register                             |  |

| 5.19.3 LCR/BSR – Link Control/Bank Select Registers                |  |

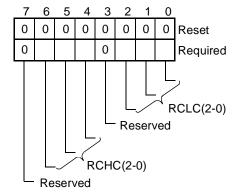

| 5.19.4 IRCR2 – Infrared Control Register 2                         |  |

| 5.19.5 ST_FIFO – Status FIFO                                       |  |

| 5.20 BANK 6                                                        |  |

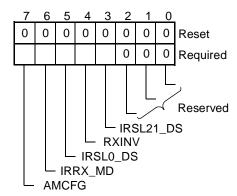

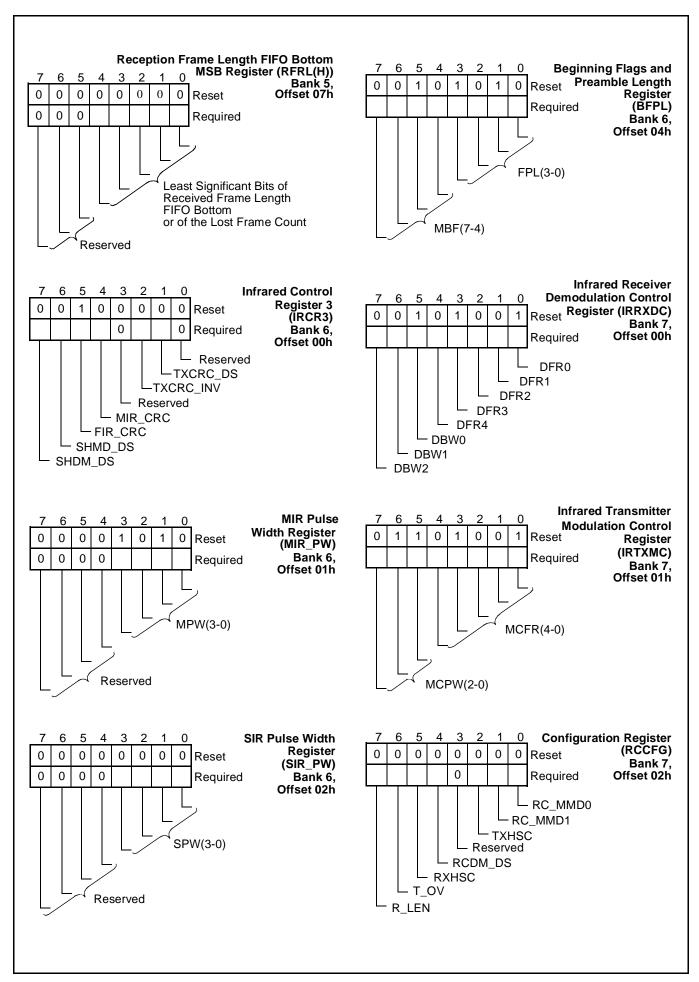

| 5.20.1 IRCR3 – Infrared Control Register 3                         |  |

| 5.20.2 MIRPW – MIR Pulse Width Register                            |  |

| 5.20.3 SIR_PW – SIR Pulse Width Register                           |  |

| 5.20.4 LCR/BSR – Link Control/Bank Select Registers                |  |

| 5.20.5 BFPL – Beginning Flags/Preamble Length Register             |  |

| 0.20.0 bi i e beginning i lagori reamble Length Neglotel           |  |

| 5.21.2 IRTXMC – Infrared Transmitter Modulator Control Register                                                                                                                                                                                      |                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 5.21.3 RCCFG – CEIR Configuration Register                                                                                                                                                                                                           |                          |

| 5.21.4 LCR/BSR – Link Control/Bank Select Registers                                                                                                                                                                                                  |                          |

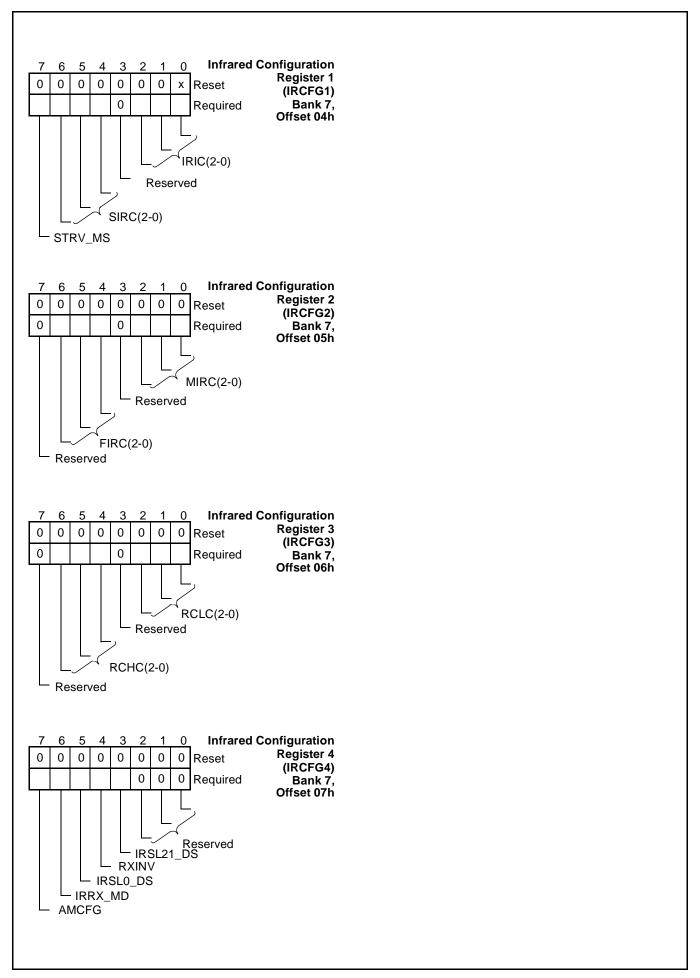

| 5.21.5 IRCFG [1–4] – Infrared Interface Configuration Registers                                                                                                                                                                                      | 179                      |

| 5.22 SERIAL COMMUNICATION CONTROLLER2 REGISTER BITMAPS                                                                                                                                                                                               | 182                      |

| 6.0 DMA and Interrupt Mapping                                                                                                                                                                                                                        |                          |

| 6.1 DMA SUPPORT                                                                                                                                                                                                                                      | 190                      |

| 6.1.1 Legacy Mode                                                                                                                                                                                                                                    | 190                      |

| 6.1.2 Plug and Play Mode                                                                                                                                                                                                                             | 190                      |

| 6.2 INTERRUPT SUPPORT                                                                                                                                                                                                                                | 191                      |

| 6.2.1 Legacy Mode                                                                                                                                                                                                                                    |                          |

| 6.2.2 Plug and Play Mode                                                                                                                                                                                                                             |                          |

| 7.0 Power Management                                                                                                                                                                                                                                 |                          |

| 7.1 POWER-DOWN STATE                                                                                                                                                                                                                                 | 194                      |

| 7.1.1 Recommended Power-Down Methods - Group 1                                                                                                                                                                                                       |                          |

| 7.1.2 Recommended Power-Down Methods - Group 2                                                                                                                                                                                                       |                          |

| 7.1.3 Special Power-Down Cases                                                                                                                                                                                                                       |                          |

| 7.2 POWER-UP                                                                                                                                                                                                                                         |                          |

| 7.2.1 The Clock Multiplier                                                                                                                                                                                                                           |                          |

| 7.2.2 Chip Power-Up Procedure                                                                                                                                                                                                                        |                          |

| 7.2.3 SCC1 and SCC2 Power-Up                                                                                                                                                                                                                         |                          |

| 7.2.4 FDC Power-Up                                                                                                                                                                                                                                   |                          |

| 8.0 Device Description                                                                                                                                                                                                                               |                          |

| 8.1 GENERAL ELECTRICAL CHARACTERISTICS                                                                                                                                                                                                               | 197                      |

| 8.1.1 Absolute Maximum Ratings                                                                                                                                                                                                                       | 197                      |

|                                                                                                                                                                                                                                                      | 197                      |

| 8.1.2 Capacitance                                                                                                                                                                                                                                    |                          |

| _                                                                                                                                                                                                                                                    | 197                      |

| 8.1.2 Capacitance                                                                                                                                                                                                                                    |                          |

| 8.1.2 Capacitance                                                                                                                                                                                                                                    | 198                      |

| 8.1.2 Capacitance 8.1.3 Electrical Characteristics 8.2 DC CHARACTERISTICS OF PINS, BY GROUP 8.2.1 Group 1                                                                                                                                            | 198                      |

| 8.1.2 Capacitance 8.1.3 Electrical Characteristics 8.2 DC CHARACTERISTICS OF PINS, BY GROUP 8.2.1 Group 1 8.2.2 Group 2                                                                                                                              | 198<br>198<br>198        |

| 8.1.2 Capacitance 8.1.3 Electrical Characteristics 8.2 DC CHARACTERISTICS OF PINS, BY GROUP 8.2.1 Group 1 8.2.2 Group 2 8.2.3 Group 3                                                                                                                | 198<br>198<br>198<br>198 |

| 8.1.2 Capacitance 8.1.3 Electrical Characteristics 8.2 DC CHARACTERISTICS OF PINS, BY GROUP 8.2.1 Group 1 8.2.2 Group 2 8.2.3 Group 3 8.2.4 Group 4                                                                                                  | 198<br>198<br>198<br>198 |

| 8.1.2 Capacitance 8.1.3 Electrical Characteristics  8.2 DC CHARACTERISTICS OF PINS, BY GROUP  8.2.1 Group 1  8.2.2 Group 2  8.2.3 Group 3  8.2.4 Group 4  8.2.5 Group 5                                                                              |                          |

| 8.1.2 Capacitance 8.1.3 Electrical Characteristics  8.2 DC CHARACTERISTICS OF PINS, BY GROUP 8.2.1 Group 1 8.2.2 Group 2 8.2.3 Group 3 8.2.4 Group 4 8.2.5 Group 5 8.2.6 Group 6                                                                     | 198198198198199199       |

| 8.1.2 Capacitance 8.1.3 Electrical Characteristics  8.2 DC CHARACTERISTICS OF PINS, BY GROUP  8.2.1 Group 1  8.2.2 Group 2  8.2.3 Group 3  8.2.4 Group 4  8.2.5 Group 5                                                                              |                          |

| 8.1.2 Capacitance 8.1.3 Electrical Characteristics  8.2 DC CHARACTERISTICS OF PINS, BY GROUP  8.2.1 Group 1  8.2.2 Group 2  8.2.3 Group 3  8.2.4 Group 4  8.2.5 Group 5  8.2.6 Group 6  8.2.7 Group 7                                                |                          |

| 8.1.2 Capacitance 8.1.3 Electrical Characteristics  8.2 DC CHARACTERISTICS OF PINS, BY GROUP 8.2.1 Group 1 8.2.2 Group 2 8.2.3 Group 3 8.2.4 Group 4 8.2.5 Group 5 8.2.6 Group 6 8.2.7 Group 7 8.2.8 Group 8                                         |                          |

| 8.1.2 Capacitance 8.1.3 Electrical Characteristics  8.2 DC CHARACTERISTICS OF PINS, BY GROUP  8.2.1 Group 1  8.2.2 Group 2  8.2.3 Group 3  8.2.4 Group 4  8.2.5 Group 5  8.2.6 Group 6  8.2.7 Group 7  8.2.8 Group 8  8.2.9 Group 9                  |                          |

| 8.1.2 Capacitance 8.1.3 Electrical Characteristics  8.2 DC CHARACTERISTICS OF PINS, BY GROUP  8.2.1 Group 1  8.2.2 Group 2  8.2.3 Group 3  8.2.4 Group 4  8.2.5 Group 5  8.2.6 Group 6  8.2.7 Group 7  8.2.8 Group 8  8.2.9 Group 9  8.2.10 Group 10 |                          |

| 8.3 AC ELECTRICAL CHARACTERISTICS |     |

|-----------------------------------|-----|

| 8.4 SWITCHING CHARACTERISTICS     | 203 |

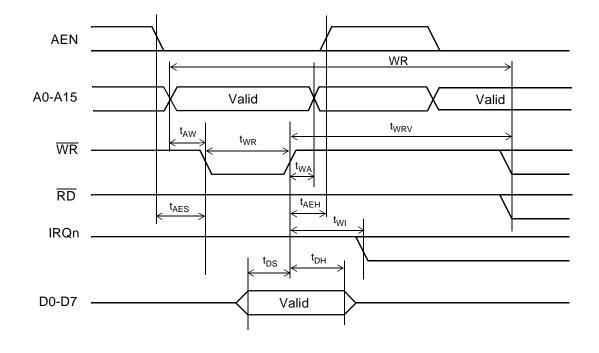

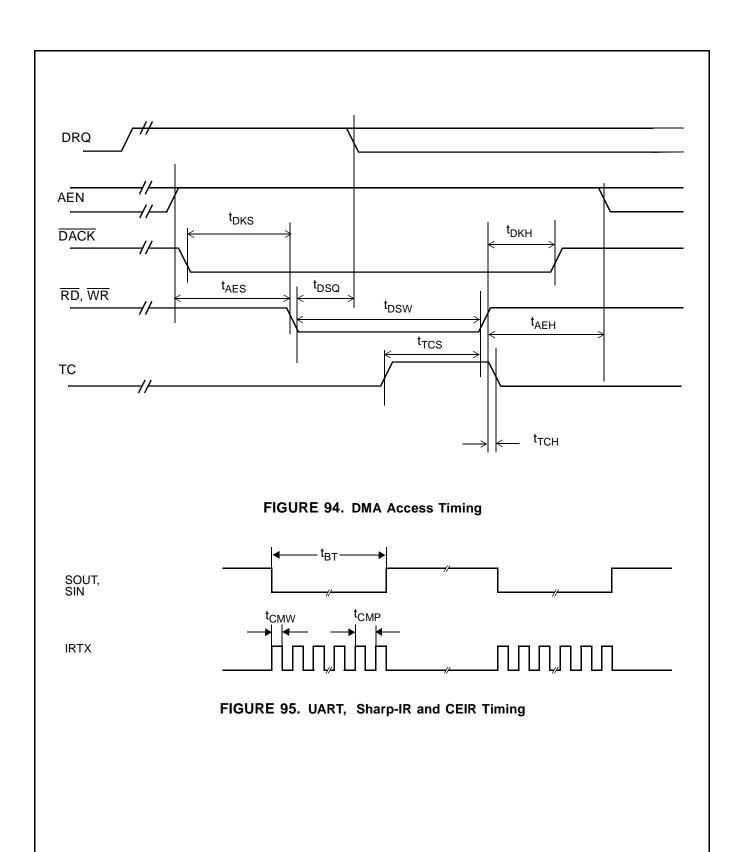

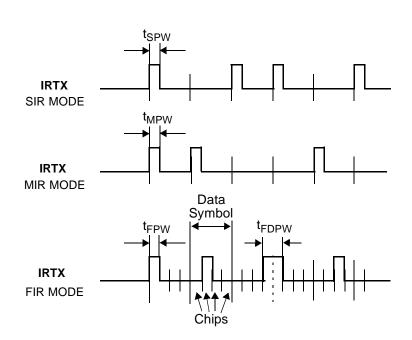

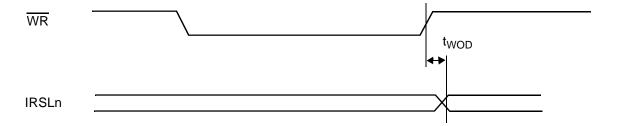

| 8.4.1 Timing Table                | 203 |

| 8.4.2 Timing Diagrams             |     |

| 9.0 Appendix A                    |     |

| COMPARISON OF PC87338 AND PC97338 | 216 |

|                                   |     |

www.national.com

## **List of Figures**

| FIGURE 1 Plug and Play Protocol Flowchart                                  | . 39 |

|----------------------------------------------------------------------------|------|

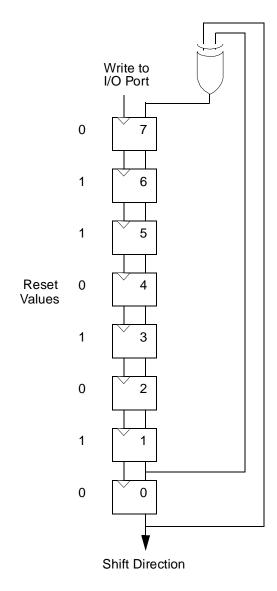

| FIGURE 2 LFSR Circuit                                                      | . 40 |

| FIGURE 3 FER Register Bitmap                                               | . 45 |

| FIGURE 4 FAR Register Bitmap                                               | . 47 |

| FIGURE 5 PTR Register Bitmap                                               | . 48 |

| FIGURE 6 FCR Register Bitmap                                               | . 48 |

| FIGURE 7 PCR Register Bitmap                                               | . 49 |

| FIGURE 8 PMC Register Bitmap                                               | . 50 |

| FIGURE 9 TUP Register Bitmap                                               | . 51 |

| FIGURE 10 SID Register Bitmap                                              | . 52 |

| FIGURE 11 ASC Register Bitmap                                              | . 52 |

| FIGURE 12 CS0LA Register Bitmap                                            | . 53 |

| FIGURE 13 CS0CF Register Bitmap                                            | . 53 |

| FIGURE 14 CS1LA Register Bitmap                                            | . 54 |

| FIGURE 15 CS1CF Register Bitmap                                            | . 54 |

| FIGURE 16 CS0HA Register Bitmap                                            | . 55 |

| FIGURE 17 CS1HA Register Bitmap                                            | . 55 |

| FIGURE 18 SCF0 Register Bitmap                                             | . 55 |

| FIGURE 19 SCF1 Register Bitmap                                             | . 56 |

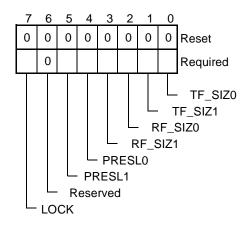

| FIGURE 20 PNP0 Register Bitmap                                             | . 57 |

| FIGURE 21 PNP1 Register Bitmap                                             | . 58 |

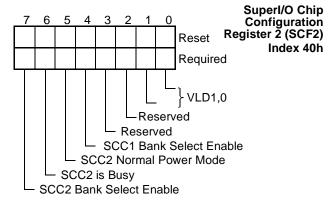

| FIGURE 22 SCF2 Register Bitmap                                             | . 58 |

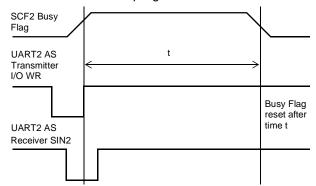

| FIGURE 23 Busy Flag Timing                                                 | . 59 |

| FIGURE 24 PNP2 Register Bitmap                                             | . 59 |

| FIGURE 25 PBAL Register Bitmap                                             | . 60 |

| FIGURE 26 PBAH Register Bitmap                                             | . 61 |

| FIGURE 27 S1BAL Register Bitmap                                            | . 61 |

| FIGURE 28 S1BAH Register Bitmap                                            | . 61 |

| FIGURE 29 S2BAL Register Bitmap                                            | . 61 |

| FIGURE 30 S2BAH Register Bitmap                                            | . 62 |

| FIGURE 31 FBAL Register Bitmap                                             | . 62 |

| FIGURE 32 FBAH Register Bitmap                                             | . 62 |

| FIGURE 33 SBAL Register Bitmap                                             | . 63 |

| FIGURE 34 SBAH Register Bitmap                                             | . 63 |

| FIGURE 35 SIRQ1 Register Bitmap                                            | . 63 |

| FIGURE 36 SIRQ2 Register Bitmap                                            | . 64 |

| FIGURE 37 SIRQ3 Register Bitmap                                            | . 65 |

| FIGURE 38 PNP3 Register Bitmap                                             | . 66 |

| FIGURE 39 SCF3 Register Bitmap                                             | . 67 |

| FIGURE 40 CLK Register Bitmap                                              | . 68 |

| FIGURE 41 FDC Functional Block Diagram                                     | . 69 |

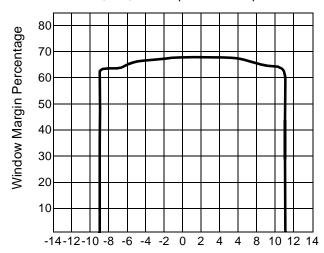

| FIGURE 42 PC87338/PC97338 Dynamic Window Margin Performance                | . 70 |

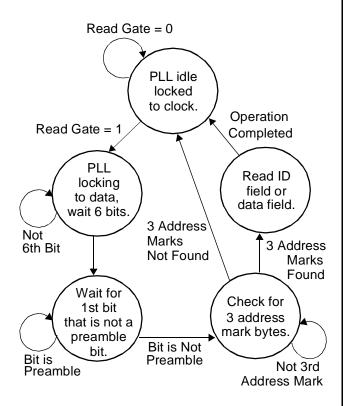

| FIGURE 43 Read Algorithm State Diagram                                     | .71  |

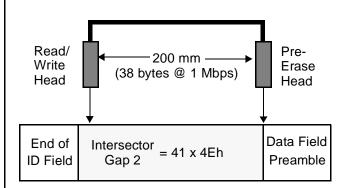

| FIGURE 44 Perpendicular Recording Drive Read/Write Head and Pre-Erase Head | .72  |

| FIGURE 45 SRA Register Bitmap                                              |      |

| FIGURE 46 SRB Register Bitmap                                              |      |

| FIGURE 47 DOR Register Bitmap                                              |      |

| FIGURE 48 TDR Register Bitmap                                              |      |

| FIGURE 49 MSR Register Bitmap                                              | . 81 |

|                                                                            |      |

| FIGURE 50 DOD Do 1sto Disease                                                   | 00  |

|---------------------------------------------------------------------------------|-----|

| FIGURE 50 DSR Register Bitmap                                                   |     |

| FIGURE 51 FDC Data Register Bitmap                                              |     |

| FIGURE 52 DIR Register Bitmap                                                   |     |

| FIGURE 53 CCR Register Bitmap                                                   |     |

| FIGURE 54 ST0 Result Phase Register Bitmap                                      |     |

| FIGURE 55 ST1 Result Phase Register Bitmap                                      |     |

| FIGURE 56 ST2 Result Phase Register Bitmap                                      |     |

| FIGURE 57 ST3 Result Phase Register                                             |     |

| FIGURE 58 IBM, Perpendicular, and ISO Formats Supported by FORMAT TRACK Command |     |

| FIGURE 59 PC87338/PC97338 Four Floppy Disk Drive Circuit                        |     |

| FIGURE 60 DTR Register Bitmap (SPP Mode)                                        |     |

| FIGURE 61 STR Register Bitmap (SPP Mode)                                        |     |

| FIGURE 62 CTR Register Bitmap (SPP Mode) in PC87338                             |     |

| FIGURE 63 CTR Register Bitmap (SPP Mode) in PC97338                             |     |

| FIGURE 64 DTR Register Bitmap (EPP Mode)                                        |     |

| FIGURE 65 STR Register Bitmap (EPP Mode)                                        |     |

| FIGURE 66 CTR Register Bitmap (EPP Mode)                                        |     |

| FIGURE 67 DTR Register Bitmap (EPP Mode)                                        |     |

| FIGURE 68 DTR Register Bitmap (EPP Mode)                                        |     |

| FIGURE 69 DTR Register Bitmap (EPP Mode)                                        |     |

| FIGURE 70 EPP Data Port 2 Bitmap                                                |     |

| FIGURE 71 EPP Data Port 3 Bitmap                                                |     |

| FIGURE 72 EPP 1.7 Address Write                                                 |     |

| FIGURE 73 EPP 1.7 Address Read                                                  |     |

| FIGURE 74 EPP Write with Zero Wait States                                       |     |

| FIGURE 75 EPP 1.9 Address Write                                                 |     |

| FIGURE 76 EPP 1.9 Address Read                                                  |     |

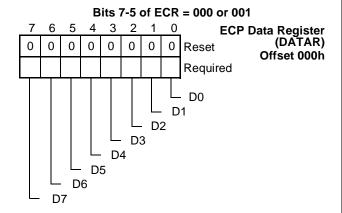

| FIGURE 77 DATAR Register Bitmap                                                 |     |

| FIGURE 78 AFIFO Register Bitmap                                                 |     |

| FIGURE 79 ECP DSR Register Bitmap                                               |     |

| FIGURE 80 DCR Register Bitmap                                                   |     |

| FIGURE 81 CFIFO Register Bitmap                                                 |     |

| FIGURE 82 DFIFO Register Bitmap                                                 | 139 |

| FIGURE 83 TFIFO Register Bitmap                                                 |     |

| FIGURE 84 CNFGA Register BitmapFIGURE 85 CNFGB Register Bitmap                  |     |

| · ·                                                                             |     |

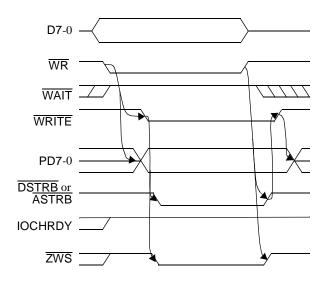

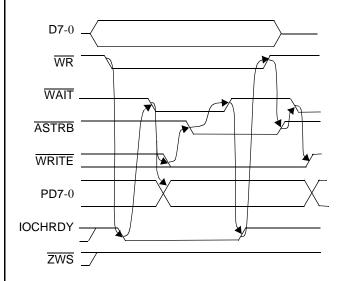

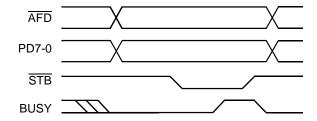

| FIGURE 86 ECR Register Bitmap FIGURE 87 ECP Forward Write Cycle                 |     |

| ·                                                                               |     |

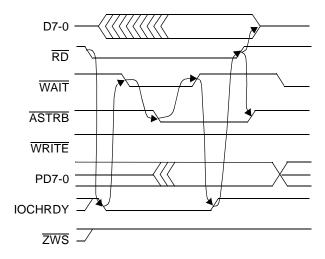

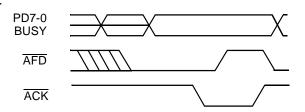

| FIGURE 88 ECP (Reverse) Read Cycle                                              |     |

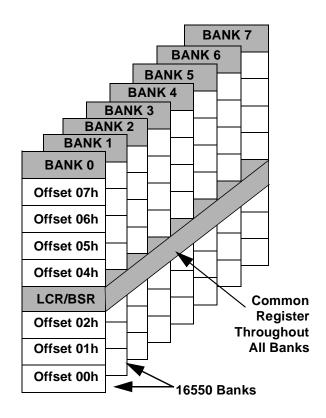

| FIGURE 88 Register Bank Architecture                                            |     |

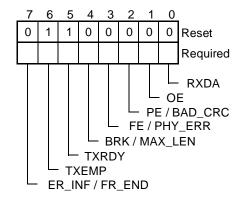

| FIGURE 88 Interrupt Enable Register                                             |     |

| FIGURE 88 Event Identification Register, Non-Extended Mode                      |     |

| FIGURE 88 Event Identification Register, Extended Mode                          |     |

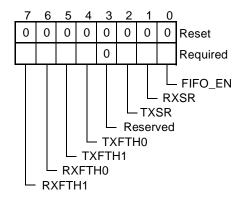

| FIGURE 88 FIFO Control Register                                                 |     |

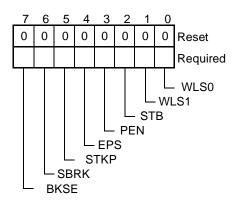

| FIGURE 88 Link Control Register                                                 |     |

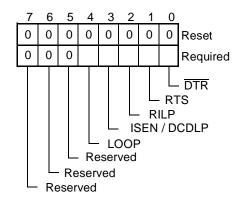

| FIGURE 88 Modem Control Register, Non-Extended Mode                             |     |

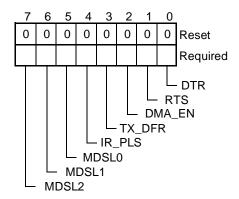

| FIGURE 88 Modern Control Register, Extended Modes                               |     |

| FIGURE 88 Link Status Register                                                  |     |

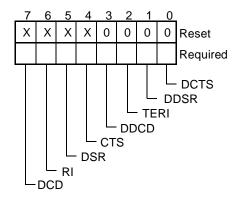

| FIGURE 88 Modem Status Register                                                 |     |

| FIGURE 88 Auxillary Status and Control Register                                 |     |

|                                                                                 |     |

| FIGURE 00 Faters de di Occatos I De misters 4                   | 400 |

|-----------------------------------------------------------------|-----|

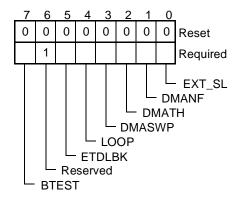

| FIGURE 88 Extended Control Register 1                           |     |

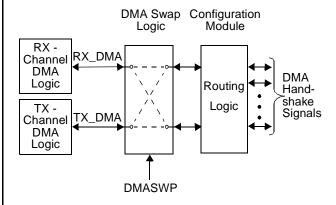

| FIGURE 88 DMA Control Signals Routing                           |     |

| FIGURE 88 Extended Control Register 2                           |     |

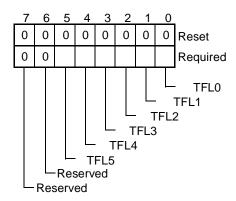

| FIGURE 88 Transmit FIFO Level                                   |     |

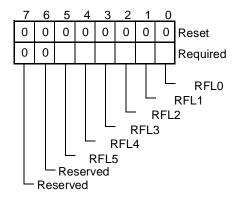

| FIGURE 88 Receive FIFO Level                                    |     |

| FIGURE 88 Infrared Control Register 1                           |     |

| FIGURE 88 Pipelined Mode Register                               |     |

| FIGURE 88 IInfrared Control Register 2                          |     |

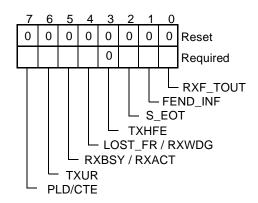

| FIGURE 88 Frame Status Byte Register                            |     |

| FIGURE 88 Infrared Control Register 3                           |     |

| FIGURE 88 MIR Pulse Width Register                              |     |

| FIGURE 88 SIR Pulse Width Register                              |     |

| FIGURE 88 Beginning Flags/Preamble Length Register              |     |

| FIGURE 88 Intrared Receiver Demodulator Control Register        |     |

| FIGURE 88 Intrared Transmitter Modulator Control Register       |     |

| FIGURE 88 CEIR Configuration Register                           |     |

| FIGURE 88 Infrared Configuration Register 1                     |     |

| FIGURE 88 Infrared Configuration Register 2                     |     |

| FIGURE 88 Infrared Configuration Register 3                     |     |

| FIGURE 88 Infrared Configuration Register 4                     |     |

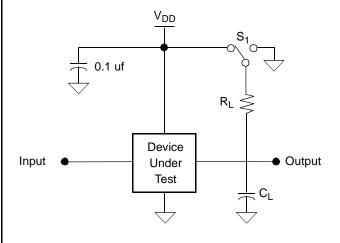

| FIGURE 89 Load Circuit                                          |     |

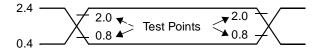

| FIGURE 90 Testing Specification Standard                        |     |

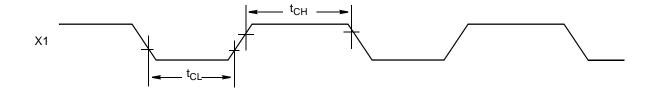

| FIGURE 91 Clock Timing                                          |     |

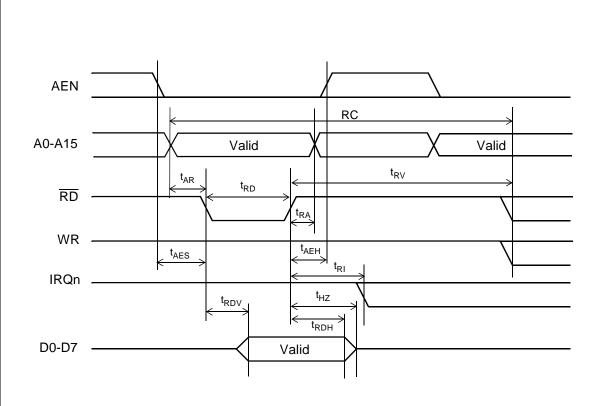

| FIGURE 92 CPU Read Timing                                       |     |

| FIGURE 93 CPU Write Timing                                      |     |

| FIGURE 94 DMA Access Timing                                     |     |

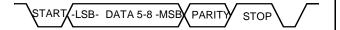

| FIGURE 95 UART, Sharp-IR and CEIR Timing                        |     |

| FIGURE 96 SIR, MIR and FIR Timing                               |     |

| FIGURE 97 IRSLn Write Timing                                    |     |

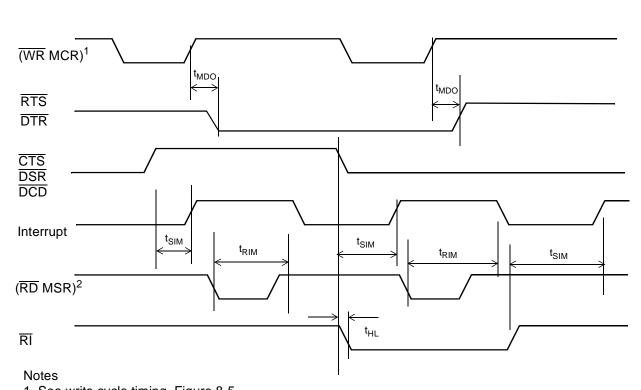

| FIGURE 98 Modem Control Timing                                  |     |

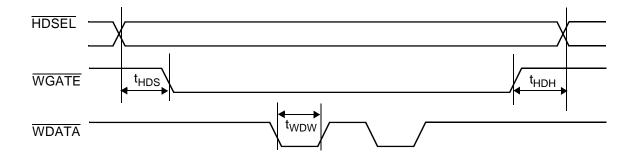

| FIGURE 99 FDC Write Data Timing                                 |     |

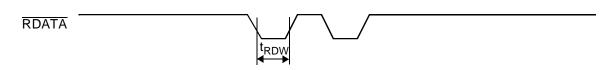

| FIGURE 100 FDC Read Data Timing                                 |     |

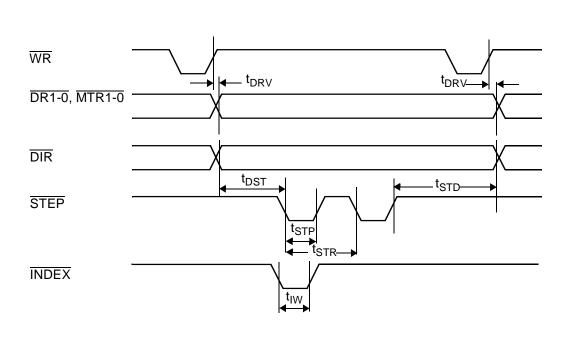

| FIGURE 101 FDC Control Signals Timing                           |     |

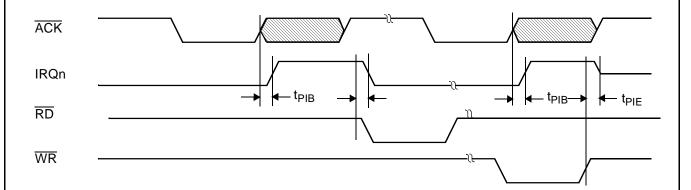

| FIGURE 102 Parallel Port Interrupt Timing (Compatible Mode)     |     |

| FIGURE 103 Parallel Port Interrupt Timing (Extended Mode)       |     |

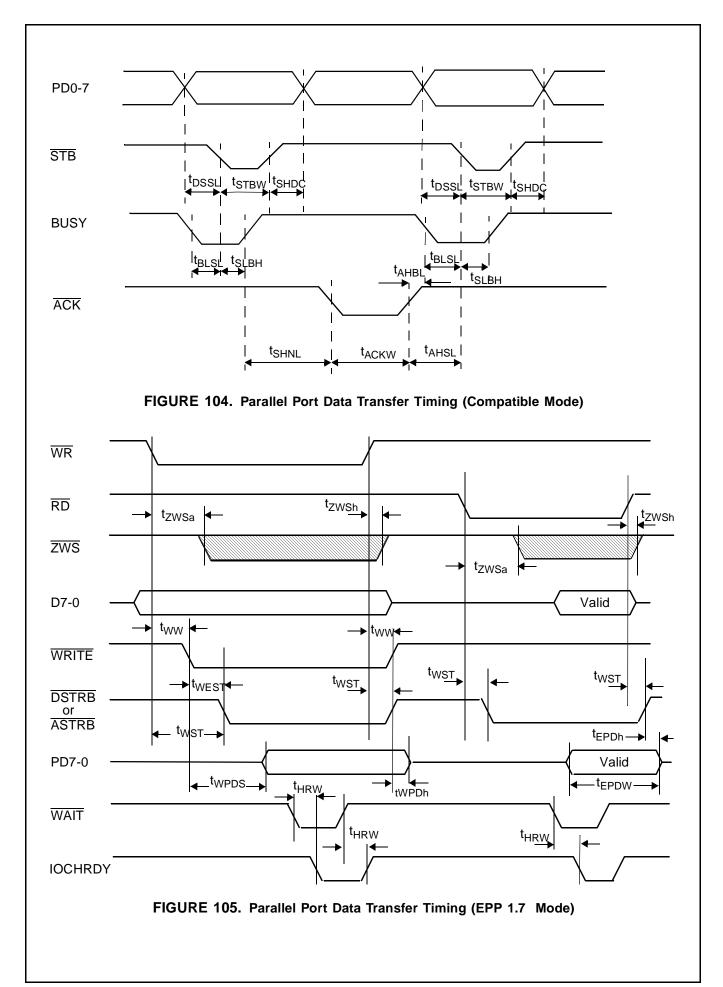

| FIGURE 104 Parallel Port Data Transfer Timing (Compatible Mode) |     |

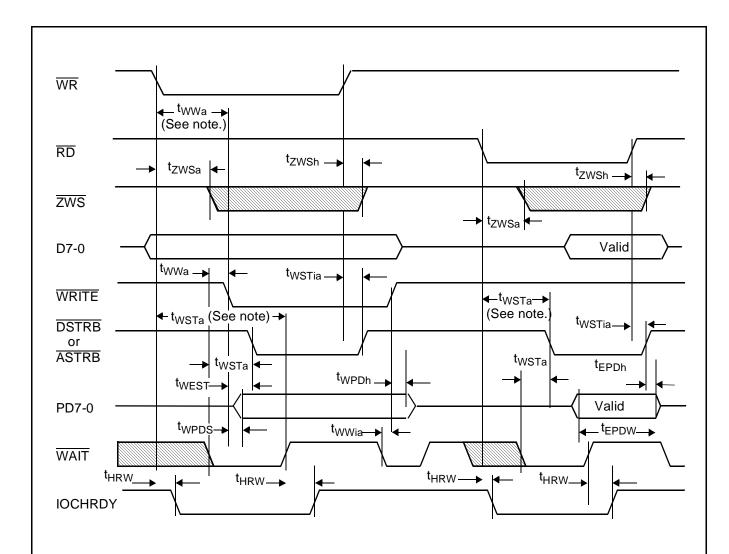

| FIGURE 105 Parallel Port Data Transfer Timing (EPP 1.7 Mode)    |     |

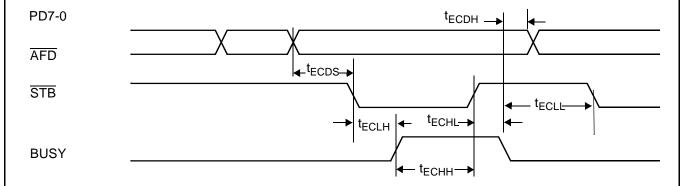

| FIGURE 106 Parallel Port Data Transfer Timing (EPP 1.9 Mode)    |     |

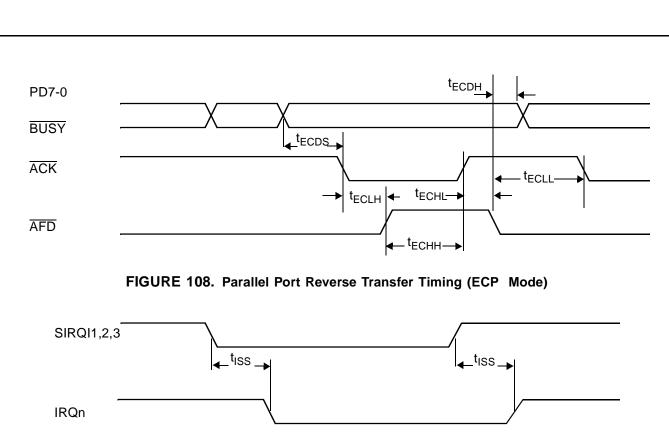

| FIGURE 107 Parallel Port Forward Transfer Timing (ECP Mode)     |     |

| FIGURE 108 Parallel Port Reverse Transfer Timing (ECP Mode)     |     |

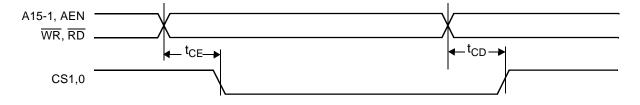

| FIGURE 109 System Interrupts Timing                             |     |

| FIGURE 110 CS1-0 Signals Timing                                 |     |

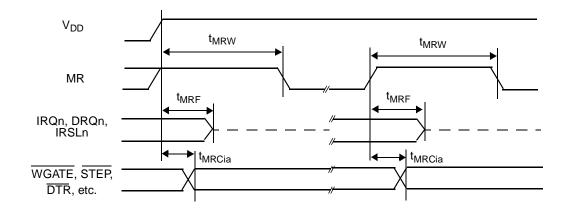

| FIGURE 111 Reset Timing                                         | 215 |

## **List of Tables**

| TABLE 1 Signal/Dip Description Table                                                                       | 22  |

|------------------------------------------------------------------------------------------------------------|-----|

| TABLE 1 Signal/Pin Description Table                                                                       |     |

| TABLE 2 Multi-Function Fins (Excluding Strap Fins)  TABLE 3 IRQ12, A15-11 / SCC2 / Infrared Pin Allocation |     |

| TABLE 4 SCC2 Mode Configurations 1                                                                         |     |

| TABLE 5 SCC2 Mode Configurations 2                                                                         |     |

| TABLE 6 Default Configurations Controlled by Hardware                                                      |     |

| TABLE 7 Configuration Registers                                                                            |     |

| TABLE 8 INDEX and DATA Register Address Options and Configuration Register Accessibility                   |     |

| TABLE 9 Primary and Secondary Drive Address Selection                                                      |     |

| TABLE 10 Encoded Drive and Motor Pin Information (Bit 4 of FER = 1)                                        |     |

| TABLE 11 Parallel Port Addresses                                                                           |     |

| TABLE 12 COM Port Selection for SCC1                                                                       |     |

| TABLE 13 COM Port Selection for SCC2                                                                       |     |

| TABLE 14 Address Selection for COM3 and COM4                                                               |     |

| TABLE 15 Parallel Port Mode                                                                                |     |

| TABLE 16 Bit Settings to Enable MRT1, IDLE or IRSL2                                                        |     |

| TABLE 17 Bit Settings to Enable DR1 or PD                                                                  |     |

| TABLE 18 ECP DMA Option Selection                                                                          |     |

| TABLE 19 Parallel Port Plug and Play DMA Settings                                                          |     |

| TABLE 20 Parallel Port Plug and Play Interrupt Assignment                                                  |     |

| TABLE 21 Parallel Port Plug and Play Interrupt Mapping                                                     |     |

| TABLE 22 TDR Bit 5 Values                                                                                  |     |

| TABLE 23 FDC Plug and Play Interrupt Mapping                                                               |     |

| TABLE 24 FDC Plug and Play DMA Settings                                                                    |     |

| TABLE 25 SBAL Reset Values                                                                                 |     |

| TABLE 26 SBAH Reset Values                                                                                 |     |

| TABLE 27 SIRQI1 Plug and Play Interrupt Mapping                                                            |     |

| TABLE 28 SIRQ1 Interrupt Settings                                                                          | 64  |

| TABLE 29 SIRQI2 Plug and Play Interrupt Mapping                                                            | • • |

| TABLE 30 Selecting MSEN1, DRATE1, CS0 or SIRQI2                                                            |     |

| TABLE 31 SIRQI3 Plug and Play Interrupt Mapping                                                            |     |

| TABLE 32 Selecting DRV2, DR23, PNF or SIRQI3                                                               |     |

| TABLE 33 SCC2 Receiver Channel Selection                                                                   |     |

| TABLE 34 SCC2 Transmission Channel Selection                                                               |     |

| TABLE 35 The FDC Registers and Their Addresses                                                             |     |

| TABLE 36 Drive and Motor Pin Encoding When FER 4 = 1                                                       |     |

| TABLE 37 Drive Enable Hexadecimal Values                                                                   |     |

| TABLE 38 TDR Bit Utilization and Reset Values in Different Drive Modes                                     |     |

| TABLE 39 Media Type Bit Settings                                                                           |     |

| TABLE 40 Data Transfer Rate Encoding                                                                       |     |

| TABLE 41 Write Precompensation Delays                                                                      |     |

| TABLE 42 Default Precompensation Delays                                                                    |     |

| TABLE 43 FDC Command Set Summary                                                                           |     |

| TABLE 44 Bytes per Sector Codes                                                                            |     |

| TABLE 45 Typical Values for PC Compatible Diskette Media                                                   |     |

| TABLE 46 Typical Gap Values                                                                                |     |

| TABLE 47 Multipliers and Head Settle Time Ranges for Different Data Transfer Rates                         |     |

| TABLE 48 DENSEL Encoding                                                                                   |     |

| TABLE 49 Effect of Drive Mode and Data Rate on FORMAT TRACK and WRITE DATA Commands                        |     |

|                                                                                                            |     |

| TABLE 50 Effect of GDC Bits on FORMAT TRACK and WRITE DATA Commands               |     |

|-----------------------------------------------------------------------------------|-----|

| TABLE 51 Skip Control Effect on READ DATA Command                                 |     |

| TABLE 52 Result Phase Termination Values with No Error                            |     |

| TABLE 53 SK Effect on READ DELETED DATA Command                                   |     |

| TABLE 54 Maximum RECALIBRATE Step Pulses for Values of R255 and ETR               |     |

| TABLE 55 The Effect of Scan Commands on the ST2 Register                          |     |

| TABLE 56 Interrupt Causes Reported by SENSE INTERRUPT                             |     |

| TABLE 57 Defining Bytes to Read or Write Using SET TRACK                          |     |

| TABLE 58 Constant Multipliers for Delay After Processing Factor and Delay Ranges  |     |

| TABLE 59 Constant Multipliers for Delay Before Processing Factor and Delay Ranges |     |

| TABLE 60 STEP Time Interval Calculation                                           |     |

| TABLE 61 VERIFY Command Termination Conditions                                    |     |

| TABLE 62 Parallel Port Reset States                                               |     |

| TABLE 63 Standard Parallel Port Registers                                         |     |

| TABLE 64 SPP Data Register Read and Write Modes                                   |     |

| TABLE 65 EPP Revision Selection                                                   |     |

| TABLE 66 Parallel Port Registers in EPP Modes                                     |     |

| TABLE 67 ECP Modes Encoding                                                       |     |

| TABLE 68 Parallel Port Registers in ECP Modes                                     |     |

| TABLE 69 ECP Mode DMA Selection                                                   |     |

| TABLE 70 ECP Mode Interrupt Selection                                             |     |

| TABLE 71 ECP Modes                                                                |     |

| TABLE 72 Parallel Port Pin Out                                                    | 144 |

| TABLE 73 Register Bank Summary                                                    | 153 |

| TABLE 74 Bank 0 Serial Controller Base Registers b                                | 153 |

| TABLE 75 Non-Extended Mode Interrupt Priorities                                   |     |

| TABLE 76 TX_FIFO Level Selection                                                  | 157 |

| TABLE 77 RX_FIFO Level Selection                                                  |     |

| TABLE 78 Word Length Select Encoding                                              | 158 |

| TABLE 79 Bit Settings for Parity Control                                          | 158 |

| TABLE 80 Bank Selection Encoding                                                  |     |

| TABLE 81 The Module Operation Modes                                               | 160 |

| TABLE 82 Bank 1 Register Set                                                      | 163 |

| TABLE 83 Bank 2 Register Set                                                      | 164 |

| TABLE 84 Baud Generator Divisor Settings                                          | 165 |

| TABLE 85 Bank 3 Register Set                                                      | 168 |

| TABLE 86 Bank 4 Register Set                                                      | 169 |

| TABLE 87 Bank 5 Register                                                          | 170 |

| TABLE 88 Bank 6 Register Set                                                      | 173 |

| TABLE 89 MIR Pulse Width Settings                                                 | 174 |

| TABLE 90 FIR Preamble Length                                                      | 174 |

| TABLE 91 MIR Beginning Flags                                                      | 175 |

| TABLE 92 Bank 7 Register Set                                                      | 175 |

| TABLE 93 CEIR, Low Speed Demodulator (RXHSC = 0) (Frequency Ranges in kHz)p       | 176 |

| TABLE 94 Consumer IR High Speed Demodulator Frequency Ranges in kHz (RXHSC = 1)   | 177 |

| TABLE 95 Sharp-IR Demodulator Frequency Ranges in kHz                             |     |

| TABLE 96 CEIR Carrier Frequency Encoding                                          |     |

| TABLE 97 Infrared Receiver Input Selection                                        | 182 |

| TABLE 98 DMA Support in Legacy Mode                                               |     |

| TABLE 99 DMA Support in Plug and Play Mode                                        | 190 |

| TABLE 100 Interrupt Support in Legacy Mode for IRQ3, 4, 6, 7, 9 10 and 11         | 191 |

|                                                                                   |     |

| TABLE 101 Interrupt Support in Legacy Mode for IRQ 5, 12 and 15                                                       |     |

|-----------------------------------------------------------------------------------------------------------------------|-----|

| TABLE 102 TRI-STATE Condition for Interrupts in Legacy Mode                                                           | 192 |

| TABLE 103 Interrupt Support in Plug and Play Mode for IRQ3, 4, 6, 7, 9, 10 or 11                                      |     |

| TABLE 104 Interrupt Support in Plug and Play Mode for IRQ 5, 12 or 15                                                 | 193 |

| TABLE 105 TRI-STATE Conditions for Interrupts in Plug and Play Mode                                                   | 193 |

| TABLE 106 Group 1 Power-Down                                                                                          | 194 |

| TABLE 107 Clock Multiplier Encoding Options                                                                           | 196 |

| TABLE 108 Capacitance: T <sub>A</sub> 0°C to 70°C, V <sub>DD</sub> = 5V +/- 10% or 3.3V +/- 10%, V <sub>SS</sub> = 0V | 197 |

| TABLE 109 Power Consumption                                                                                           | 197 |

| TABLE 110 DC Characteristics of Group 1 Pins                                                                          | 198 |

| TABLE 111 DC Characteristics of Group 2 Pins                                                                          |     |

| TABLE 112 DC Characteristics of Group 3 Pins                                                                          |     |

| TABLE 113 DC Characteristics of Group 4 Pins                                                                          | 199 |

| TABLE 114 DC Characteristics of Group 5 Pins                                                                          | 199 |

| TABLE 115 DC Characteristics of Group 6 Input Pins                                                                    | 200 |

| TABLE 116 DC Characteristics of Group 6 Output Pins                                                                   | 200 |

| TABLE 117 DC Characteristics of Group 7 Pins                                                                          | 200 |

| TABLE 118 DC Characteristics of Group 8 Pins                                                                          | 200 |

| TABLE 119 DC Characteristics of Group 9 Pins                                                                          | 201 |

| TABLE 120 DC Characteristics of Group 10 Pins                                                                         | 201 |

| TABLE 121 DC Characteristics of Group 11 Pins                                                                         | 201 |

| TABLE 122 DC Characteristics of Group 12 Pins                                                                         | 202 |

| TABLE 123 DC Characteristics of Group 13 Pins                                                                         | 202 |

#### 1.0 Pin Descriptions 1.1 CONNECTION DIAGRAMS Plastic Quad Flatpack (PQFP), EIAJ DRATE1/MSEN1/CS0/SIRQI2/DACK3 SOUT2/BOUT2/CFG0/IRTX DSR2/IRQ12/IRRX2/IRSL0 SOUT1/BOUT1/BADDR1 AFD/DSTRB/DENSEL IRQ15/SIRQI1/DRQ3 DRATEO/MSENO RTS1/BADDR0 SIN2/IRRX1 80 79 78 77 76 75 74 73 72 71 70 69 68 67 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52 51 SLIN/STEP/ASTRB SLCT/WGATE - DRV2/PNF/DR23/SIRQI3/IRSL2 82 PE/WDATA -83 - DENSEL/ADRATE1 48 BUSY/WAIT/MTR1 84 - INDEX 47 ACK/DR1 ■ MTR0 85 46 PD7/MSEN1 . 86 DR1/PD 45 PD6/DRATE0 -87 <u>− DR0</u> PD5/MSEN0 -MTR1/IDLE/IRSL2 PD4/DSKCHG -VSS 42 PC87338VLJ VSS - DIR 90 PD3/RDATA -STEP 40 PD2/WP -**WDATA** 92 39 PD1/TRK0 - WGATE 93 38 PD0/INDEX -TRK0 37 - WP STB/WRITE -95 36 RDATA IRQ7 96 35 - HDSEL IRQ6 97 34 IRQ5/ADRATE0 - DRQ1 98 DSKCHG VDD 99 IRQ4 - A10 **Order Number PC87338VLJ** See NS Package Number VLJ100A

### 1.2 SIGNAL/PIN DESCRIPTIONS

Table 1 lists the signals of the Chip in alphabetical order. It also shows the pin associated with each signal for the Plastic Quad Flatpack, (PQFP) and Thin Quad Flatpack (TQFP) options. The I/O column describes whether the pin is an input, output, or bidirectional pin (marked as I, O or I/O, respectively). This column also specifies which group in Section 8.2 describes the pin's DC characteristics.

Refer to the glossary for an explanation of abbreviations and terms used in this table and throughout this document. Use the Table of Contents to find more information about each register.

**TABLE 1. Signal/Pin Description Table**

| Symbol                                                                                             | PQFP<br>Pin                                                                                  | TQFP<br>Pin                                                                                  | I/O and<br>Group # | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0<br>A1<br>A2<br>A3<br>A4<br>A5<br>A6<br>A7<br>A8<br>A9<br>A10<br>A11<br>A12<br>A13<br>A14<br>A15 | 30<br>29<br>28<br>27<br>26<br>25<br>24<br>23<br>22<br>21<br>31<br>62<br>63<br>64<br>66<br>69 | 28<br>27<br>26<br>25<br>24<br>23<br>22<br>21<br>20<br>19<br>29<br>60<br>61<br>62<br>64<br>67 | l<br>Group 1       | Address. These address lines from the microprocessor determine which internal register is accessed. The values of A15-0 have no effect during DMA transfers.  If CFG0 = 0 during reset, A15-0 are used for address decoding.  If CFG0 = 1 during reset, only A10-0 are used for address decoding, and A15-11 are ignored (masked to 0).  In Legacy mode, A10 is used only for ECP decoding.  A15-11 are multiplexed with SCC2's signals.                                                     |

| ACK                                                                                                | 85                                                                                           | 83                                                                                           | I<br>Group 3       | <b>Acknowledge.</b> This parallel port input signal is pulsed low by an external printer to indicate it received data from the parallel port. This pin is internally connected to a nominal 25 K $\Omega$ pull-up resistor. $\overline{\text{ACK}}$ is multiplexed with $\overline{\text{DR1}}$ . (See Table 72 for more information).                                                                                                                                                       |

| ADRATE0<br>ADRATE1                                                                                 | 98<br>48                                                                                     | 96<br>46                                                                                     | O<br>Group 10      | Additional Data Rate signals 0 and 1. These FDC output signals are provided in addition to DRATE1,0 and have a similar function. They reflect the currently selected FDC data rate, (bits 0 and 1 in the Configuration Control Register (CCR) or the Data Rate Select Register (DSR), whichever was written to last).  ADRATE0 is configured when bit 0 of ASC is 1. ADRATE1 is configured when bit 4 of ASC is 1.  ADRATE0 is multiplexed with IRQ5 and ADRATE1 is multiplexed with DENSEL. |

| AEN                                                                                                | 20                                                                                           | 18                                                                                           | I<br>Group 1       | Address Enable. When set to 1, this pin enables DMA addressing and disables the microprocessor Address. The address lines disabled will be A15-0 or A10-0, depending on whether CFG0 was set to 0 or 1 during reset (respectively).  Access during DMA transfer is NOT affected by this pin.                                                                                                                                                                                                 |

| ĀFD                                                                                                | 78                                                                                           | 76                                                                                           | O<br>Group 11      | Automatic Feed XT. When low this parallel port signal indicates to the external printer that it should automatically line feed after each Carriage Return byte. This signal enters a TRI-STATE® condition within 10 nsec after a 0 is loaded into the Control Register bit. An external 4.7 K $\Omega$ pull-up resistor should be attached to this pin. $\overline{\text{AFD}}$ is multiplexed with $\overline{\text{DSTRB}}$ and DENSEL. See Table 72 for more information.                 |

www.national.com

| Symbol           | PQFP<br>Pin                      | TQFP<br>Pin                      | I/O and<br>Group # | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------|----------------------------------|----------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASTRB            | 81                               | 79                               | O<br>Group 11      | Address Strobe. This active-low signal is used in EPP mode as an address strobe.  ASTRB is multiplexed with SLIN and STEP. See Table 72 for more information.                                                                                                                                                                                                                                                                                                                                                                              |

| BADDR0<br>BADDR1 | 74<br>73                         | 72<br>71                         | I<br>Group 1       | SIO Base Address Straps 0 and 1. These bits must be externally strapped to determine which one of four base address options for the INDEX and DATA registers will be used by the system after reset. See Table 8.  If BADDR1 = 0 and BADDR0 = 1 during reset, the chip "wakes up" without a base address and the Plug and Play protocol should be applied. For more details see Section 2.                                                                                                                                                 |

|                  |                                  |                                  |                    | These pins are internally grounded by a 30 K $\Omega$ pull-down resistor. To strap these pins high, pull them up to $V_{cc}$ with a 10 K $\Omega$ resistor. BADDR0 is multiplexed with $\overline{RTS1}$ , and BADDR1 is multiplexed with SOUT1 (and BOUT1 in PC87338 only).                                                                                                                                                                                                                                                               |

| BOUT1<br>BOUT2   | 73 <i>(71)</i><br>65 <i>(63)</i> | 71 <i>(69)</i><br>63 <i>(61)</i> | O<br>Group 7       | SCC Baud Output signals 1 and 2. These multi-function pins provide the associated serial channel Baud Rate generator output signal for SCC1 or SCC2, if test mode is selected in the Power and Test Configuration Register (PTR) and the DLAB bit (LCR7) is set. BOUT1 is multiplexed with SOUT1 and BADDR1. BOUT2 is multiplexed with SOUT2, IRTX and CFG0 (in PC87338 only). BOUT1 is multiplexed with DTR1. BOUT2 is multiplexed with DTR2 and A12 (in PC97338 only).                                                                   |

| BUSY             | 84                               | 82                               | l<br>Group 2       | <b>Busy.</b> This parallel port signal is set high by the external printer when it cannot accept another character. This pin is internally grounded by a nominal 25 K $\Omega$ pull-down resistor. BUSY is multiplexed with $\overline{\text{MTR1}}$ and $\overline{\text{WAIT}}$ . (See Table 72 for more information).                                                                                                                                                                                                                   |

| CFG0             | 65                               | 63                               | I<br>Group 9       | <b>Configuration.</b> This CMOS input signal is externally strapped to select one of two default configurations in which the Chip powers up (see Table 6). This pin is internally grounded by a 30 K $\Omega$ pull-down resistor. To strap this pin high, pull it up to $V_{CC}$ with a 10 K $\Omega$ resistor. CFG0 is multiplexed with SOUT2 and IRTX.                                                                                                                                                                                   |

| CS0<br>CS1       | 51<br>3                          | 49<br>1                          | O<br>Group 8       | Programmable Chip Select signals 0 and 1. $\overline{CS1,0}$ are programmable chip select and/or latch enable and/or output enable signals that can be used as game port, I/O expander, etc.  The decoded address and the assertion conditions are configured via the Chip configuration registers, indexed by 0Ah-0Dh, 10h-11h, 03h and 4Dh. $\overline{CS1,0}$ are push-pull output signals. $\overline{CS0}$ is multiplexed with DRATE1, MSEN1, SIRQI2 and $\overline{DACK3}$ . $\overline{CS1}$ is multiplexed with $\overline{ZWS}$ . |

| Symbol                                       | PQFP<br>Pin                            | TQFP<br>Pin                           | I/O and<br>Group # | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |