### INTEGRATED CIRCUITS

Product specification File under Integrated Circuits, IC11

### **TDA5341**

#### FEATURES

- Full-wave commutation (using push-pull output stages) without position sensors

- · Built-in start-up circuitry

- Three push-pull MOS outputs:

- 1 A output current

- Low voltage drop

- Built-in current limiter

- Thermal protection

- · General purpose operational amplifier

- Reset generator

- · Motor brake facility

- Actuator driver (H-bridge current-controlled)

- Power-down detector

- · Automatic park and brake procedure

- Adjustable park voltage

- Sleep mode

- Speed control with Frequency-Locked Loop (FLL)

- Serial port

- Friction reduction prior to spin-up.

#### QUICK REFERENCE DATA

Measured over full voltage and temperature range.

#### SYMBOL MIN. TYP. MAX. UNIT PARAMETER $V_{DD}$ general supply voltage for logic and power 4.5 5.0 5.25 V motor output current 1.3 1.6 1.9 A I<sub>OMOT</sub> 1.1 Ω motor output resistance 1.56 R<sub>DS(MOT)</sub> 0.7 1.1 A I<sub>OACT</sub> actuator output current 1.4 actuator output resistance 2.0 2.5 Ω R<sub>DS(ACT)</sub>

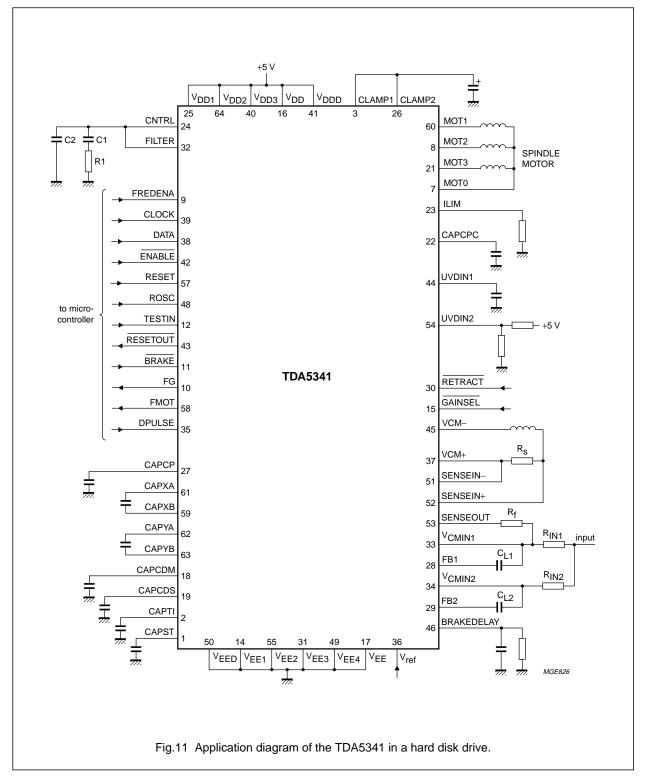

**APPLICATIONS**

motor.

the device.

Hard Disk Drive (HDD).

**GENERAL DESCRIPTION**

The TDA5341 is a BiCMOS integrated circuit used to drive

and is ideally suited as a drive circuit for a hard disk drive

brushless DC motors in full-wave mode. The device senses the rotor position using an EMF sensing technique

The TDA5341 also includes a Voice Coil Motor driver

(VCM), reset and park facilities and an accurate speed

regulator. In addition, a serial port facilitates the control of

#### **ORDERING INFORMATION**

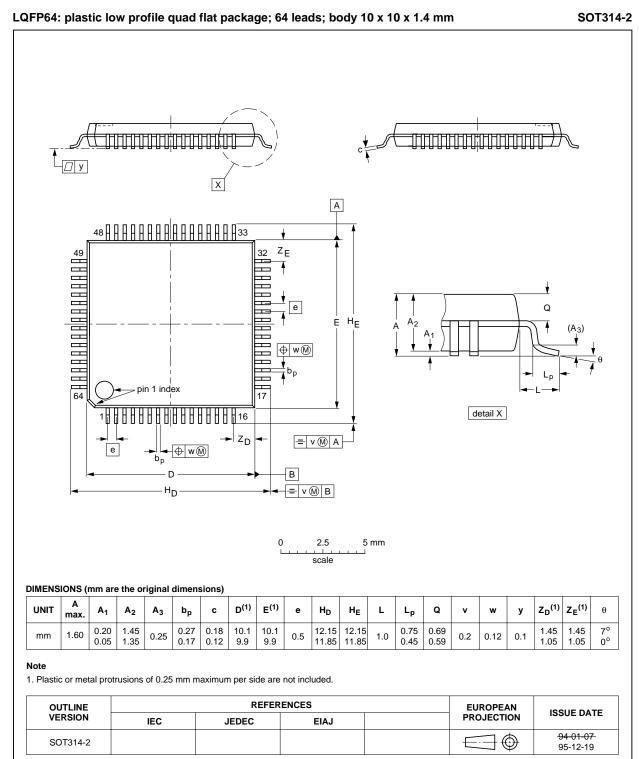

| TYPE     |        | PACKAGE                                                                            |          |  |  |  |

|----------|--------|------------------------------------------------------------------------------------|----------|--|--|--|

| NUMBER   | NAME   | DESCRIPTION                                                                        | VERSION  |  |  |  |

| TDA5341G | LQFP64 | plastic low profile quad flat package; 64 leads; body $10 \times 10 \times 1.4$ mm | SOT314-2 |  |  |  |

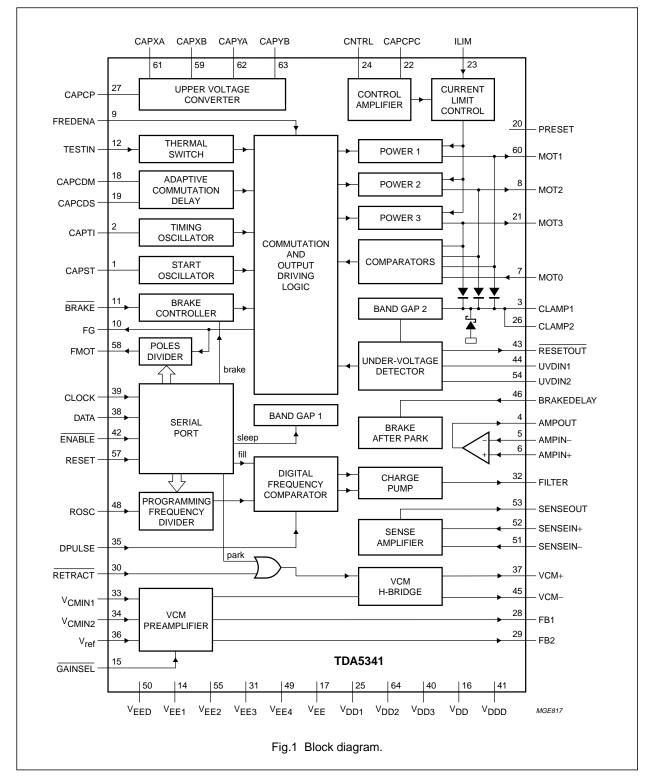

#### **BLOCK DIAGRAM**

1997 Jul 10

Product specification

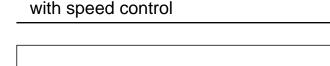

#### PINNING

| SYMBOL             | PIN | DESCRIPTION                                                                       |

|--------------------|-----|-----------------------------------------------------------------------------------|

| CAPST              | 1   | external capacitor for starting oscillator                                        |

| CAPTI              | 2   | external capacitor for timer circuit                                              |

| CLAMP1             | 3   | external capacitor used to park the heads; must be externally connected to CLAMP2 |

| AMPOUT             | 4   | uncommitted operational amplifier output                                          |

| AMPIN-             | 5   | uncommitted operational amplifier invert input                                    |

| AMPIN+             | 6   | uncommitted operational amplifier direct input                                    |

| MOT0               | 7   | motor centre tap input                                                            |

| MOT2               | 8   | motor driver output 2                                                             |

| FREDENA            | 9   | friction reduction mode enable input (active HIGH)                                |

| FG                 | 10  | frequency generator (tacho) output                                                |

| BRAKE              | 11  | brake input command (active LOW)                                                  |

| TESTIN             | 12  | test input for power output switch-off (active HIGH)                              |

| TP1                | 13  | test purpose 1 (should be left open-circuit)                                      |

| V <sub>EE1</sub>   | 14  | ground for the spindle motor drivers                                              |

| GAINSEL            | 15  | VCM gain adjustment input (switch ON when GAINSEL is LOW)                         |

| V <sub>DD</sub>    | 16  | general power supply                                                              |

| V <sub>EE</sub>    | 17  | general ground                                                                    |

| CAPCDM             | 18  | external capacitor for adaptive commutation delay (master)                        |

| CAPCDS             | 19  | external capacitor for adaptive commutation delay (slave)                         |

| PRESET             | 20  | set the motor drivers into a fixed state: MOT1 = F (floating), MOT2 = L, MOT3 = H |

| MOT3               | 21  | motor driver output 3                                                             |

| CAPCPC             | 22  | frequency compensation of the current control                                     |

| ILIM               | 23  | current limit control input                                                       |

| CNTRL              | 24  | motor control                                                                     |

| V <sub>DD1</sub>   | 25  | power supply 1 for the spindle motor drivers                                      |

| CLAMP2             | 26  | external capacitor used to park the heads; must be externally connected to CLAMP1 |

| CAPCP              | 27  | external capacitor for the charge pump output                                     |

| FB1                | 28  | output of the VCM preamplifiers                                                   |

| FB2                | 29  | switchable output of the VCM preamplifier                                         |

| RETRACT            | 30  | park input command (active LOW)                                                   |

| V <sub>EE3</sub>   | 31  | ground 3 for the actuator driver                                                  |

| FILTER             | 32  | charge pump output to be connected to an external filter                          |

| V <sub>CMIN1</sub> | 33  | VCM voltage control input                                                         |

| V <sub>CMIN2</sub> | 34  | switchable VCM voltage control input                                              |

|                    | 35  | data pulse input of the frequency comparator of the speed control                 |

| V <sub>ref</sub>   | 36  | voltage reference input                                                           |

| VCM+               | 37  | positive output of the VCM amplifier                                              |

| DATA               | 38  | input data of the serial port (active HIGH)                                       |

| CLOCK              | 30  | clock input signal to shift DATA into SERIALIN register (active HIGH)             |

|                    | 59  | ן טוטטא ווויףער פוקוומרוט פרוור באדא ווונט פרוזאבווי ופקופופר (מטוויפ דוופרו)     |

1997 Jul 10

Product specification

#### Product specification

# Brushless DC motor and VCM drive circuit with speed control

| SYMBOL           | PIN | DESCRIPTION                                                                           |

|------------------|-----|---------------------------------------------------------------------------------------|

| V <sub>DDD</sub> | 41  | digital power supply                                                                  |

| ENABLE           | 42  | enable input; enables the serial port, i.e. allows DATA to be shifted in (active LOW) |

| RESETOUT         | 43  | under-voltage detector output flag (active LOW)                                       |

| UVDIN1           | 44  | external capacitor for the RESETOUT duration                                          |

| VCM-             | 45  | negative output of the VCM amplifier                                                  |

| BRAKEDELAY       | 46  | delay control input for brake after park                                              |

| TP2              | 47  | test purpose 2 (should be left open-circuit)                                          |

| ROSC             | 48  | reference oscillator input for motor speed control                                    |

| V <sub>EE4</sub> | 49  | ground 4 for the actuator driver                                                      |

| V <sub>EED</sub> | 50  | digital ground                                                                        |

| SENSEIN-         | 51  | inverting input of the VCM sense amplifier                                            |

| SENSEN+          | 52  | non-inverting input of the VCM sense amplifier                                        |

| SENSEOUT         | 53  | output of the VCM sense amplifier                                                     |

| UVDIN2           | 54  | external voltage reference for the under-voltage detector                             |

| V <sub>EE2</sub> | 55  | ground 2 for the spindle motor drivers                                                |

| TP3              | 56  | test purpose 3 (should be left open-circuit)                                          |

| RESET            | 57  | reset input; forces all bits of the SERIALIN register to 0 (active HIGH)              |

| FMOT             | 58  | tachometer output (one pulse per mechanical revolution)                               |

| САРХВ            | 59  | external capacitor for the charge pump output                                         |

| MOT1             | 60  | motor driver output 1                                                                 |

| САРХА            | 61  | external capacitor for the charge pump output                                         |

| САРҮА            | 62  | external capacitor for the charge pump output                                         |

| САРҮВ            | 63  | external capacitor for the charge pump output                                         |

| V <sub>DD2</sub> | 64  | power supply for the spindle motor drivers                                            |

Brushless DC motor and VCM drive circuit

#### FUNCTIONAL DESCRIPTION

The TDA5341 offers a sensorless three-phase motor full-wave drive function. The device also offers protected outputs capable of handling high currents and can be used with star or delta connected motors.

The TDA5341 can easily be adapted for different motors and applications.

The TDA5341 offers the following features:

- · Sensorless commutation by using the motor EMF

- Built-in start-up circuit

- Optimum commutation, independent of motor type or motor loading

- Built-in flyback diodes

- Three-phase full-wave drive

- High output current (1.3 A)

- Low MOS R<sub>DSon</sub> (1 Ω)

- Outputs protected by current limitation and thermal protection of each output transistor

- Low current consumption

- · Additional uncommitted operational amplifier

- H-bridge actuator driver current controlled with an external series sense resistor

- Automatic retract procedure

- Adjustable park voltage

- Sleep mode

- Automatic brake (after park) procedure

- Speed control based on FLL technique

- Serial port DATAIN (24 bits)

- Friction reduction prior to spin-up.

#### **TDA5341 modes description**

The TDA5341 can be used in two main modes, depending on whether they are controlled or not.

The 'controlled modes' (user commands) are executed by the TDA5341 without delay or priority treatment, either by software via the serial port or by hardware. BRAKE is a hardware command whereas RETRACT can be controlled in both ways. If it is preferable to control the heads parking via the serial bus, the equivalent pin can be left open-circuit.

The sleep mode is controlled by software only; it results from the combination of the spindle and actuator being disabled. The spindle is turned off by bit SPINDLE DISABLE, whereas the actuator is disabled towards bit VCM DISABLE of the serial port (see Section "Serial port"). In addition, a special spin-up mode can be activated in the event of high head stiction

The 'uncontrolled modes' only result from different failures caused by either a too high internal temperature or an abnormally low power voltage, which will cause the actuator to retract and, after the spindle, to brake. The output signals mainly affected by those failures are RESETOUT, MOT1, 2 and 3, VCM+ and VCM–. This is summarised in Tables 1 and 2.

| HARDWARE/<br>SOFTWARE | MODE               | MOT1, 2 AND 3  | VCM+ AND<br>VCM–             | RESETOUT | EFFECT               |

|-----------------------|--------------------|----------------|------------------------------|----------|----------------------|

| Software              | spindle disable    | high impedance | high impedance               | HIGH     | spindle off          |

| Software              | VCM disable        | not affected   | high impedance               | HIGH     | spindle on; VCM off  |

| Hardware              | brake              | LOW            | not affected                 | HIGH     | spindle coils ground |

| Software/<br>hardware | retract            | not affected   | VCM- = 0.65 V;<br>VCM+ = 0 V | HIGH     | heads parked         |

| Hardware              | friction reduction | -              | not affected                 | HIGH     | heads in vibration   |

#### Table 1 Summary of controlled modes

### TDA5341

| FAILURE              | MOT1, 2 AND 3                    | VCM+ AND VCM-                | RESETOUT | EFFECT                   |

|----------------------|----------------------------------|------------------------------|----------|--------------------------|

| Thermal<br>shut-down | high impedance $\rightarrow$ LOW | VCM- = 0.65 V;<br>VCM+ = 0 V | LOW      | automatic park and brake |

| Voltage<br>shut-down | high impedance $\rightarrow$ LOW | VCM- = 0.65 V;<br>VCM+ = 0 V | LOW      | automatic park and brake |

#### Table 2 Summary of uncontrolled modes

#### Controlled modes

#### SPINDLE DISABLE

The spindle circuitry is switched off when bit 23 (SPINDLE DISABLE) of the serial port is pulled HIGH. In that mode, the reference band gap generator is cut off so that all internal current sources are disabled. Both the spindle and actuator outputs will be set to the high impedance state because the upper converter is also turned off.

It should be noted that the uncommitted operational amplifier is also disabled in that mode.

#### VCM DISABLE

The actuator will be disabled when bit 22 (VCM DISABLE) is set to logic 1; the spindle circuitry is not affected in that mode. The retract circuitry also remains active, so that the heads can be parked although the VCM is disabled. In that mode, the current consumption can be reduced by  $\pm 4$  mA.

#### SLEEP MODE

The sleep mode is obtained by pulling both the SPINDLE and VCM DISABLE bits of the serial port HIGH. The power monitor circuitry only remains active in sleep mode.

#### RETRACT

Retract is activated by pulling either bit 21 (PARK) HIGH or RETRACT (pin 30) LOW. When RETRACT is set LOW, a voltage of 0.65 V is applied to pin VCM– for parking.

It should be noted that the park voltage can be made adjustable by changing one of the interconnect masks. Accordingly, some different voltages, varying from 0.2 to 1.2 V, can quickly be obtained on customer demand. This mode does not affect the control of the spindle rotation.

#### BRAKE MODE

The brake mode is activated by pulling  $\overrightarrow{BRAKE}$  (pin 11) LOW. When a voltage of less than 0.8 V is applied to pin  $\overrightarrow{BRAKE}$ , the 3 motor outputs are short-circuited to ground, which results in a quick reduction of the speed until the motor stops completely.

1997 Jul 10

#### FRICTION REDUCTION

Pulling FREDENA HIGH activates the friction reduction mode of the TDA5341. In that mode, a clock signal fed via pin TESTIN will cause the MOT outputs to sequentially switch-on and switch-off at the same frequency and, as a result, generate an AC spindle torque high enough to overcome the head stiction.

Before start-up, the head stiction might be higher than normal due to condensation between the head(s) and the disk(s). Normal spin-up is not possible when this friction torque is higher than the start-up torque of the spindle motor. Spin-up is then only possible after friction has been reduced by breaking the head(s) free. Bringing a static friction system into mechanical resonance is an effective method to break static friction head(s) free.

The resonance frequency is:

$$f_{res} = \left(\frac{1}{2\pi}\right) \times 0.5 \left(\frac{C}{J}\right)$$

Where:

C = Stiffness of the head-spring(s) in direction of disk(s) rotation, (N/m)

J = Inertia of the disk(s), (kg/m<sup>2</sup>).

The external clock input frequency must be:

$$f_{clk} = \left(\frac{6}{2\pi}\right) \times 0.5 \left(\frac{C}{J}\right)$$

A burst of  $n \times 6$  clock pulse will bring the system into resonance and break the heads free (n > 2). Once the heads have been broken free, the normal spin-up procedure can be applied.

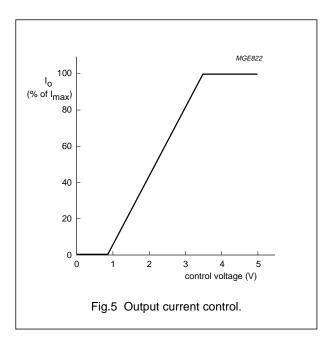

It should be noted that the clock frequency must be smaller than 40000/CAPCDM (nF).

### TDA5341

#### Uncontrolled modes

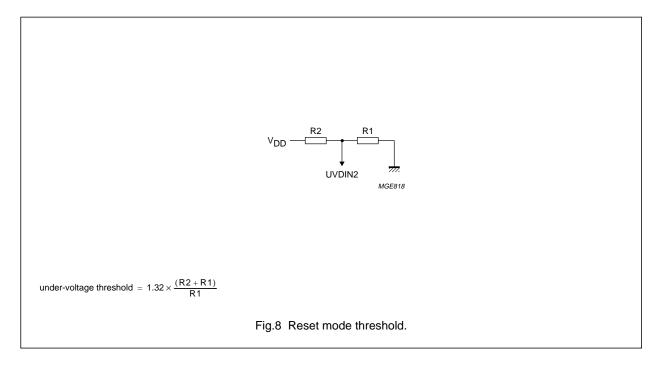

#### POWER SHUT-DOWN

If the power supply decreases to less than the voltage threshold determined by the ratio between R1 and R2 connected to UVDIN2 (see Fig.8) (for more than 1  $\mu$ s), the TDA5341 will issue a reset (RESETOUT goes LOW) and the following operation will start:

- Firstly, the MOT outputs are switched to the high impedance state so as to get back the rectified EMF issued from the motor itself. At the same time, the voltage upper converter is cut off in order to preserve the voltage on the charge pump capacitance at CAPCP. The energy supplied in that way is then used to park the heads in a safe position

- Secondly, after a certain period of time, depending on the RC constant of the device connected to BRAKEDELAY, the lower MOS drivers will be turned on in order to stop the motor completely.

#### THERMAL SHUT-DOWN

Should the temperature of the chip exceed +140  $\pm$ 10 °C, a shut-down operation will also be processed. The actions described for power shut-down will be sequenced in the same manner.

#### SPINDLE SECTION (see Fig.1)

Full-wave driving of a three-phase motor requires three push-pull output stages. In each of the six possible states two outputs are active, one sourcing current and one sinking current. The third output presents a high impedance to the motor which enables measurement of the motor EMF in the corresponding motor coil by the EMF comparator at each output. The commutation logic is responsible for control of the output transistors and selection of the correct EMF comparator.

The zero-crossing in the motor EMF (detected by the comparator selected by the commutation logic) is used to calculate the correct moment for the next commutation, i.e. the change to the next output state. The delay is calculated (depending on the motor loading) by the adaptive commutation delay block.

Because of high inductive loading the output stages contain flyback diodes. The output stages are also protected by a current limiting circuit and by thermal protection of the six output transistors.

The zero-crossings can be used to provide speed information such as the tacho signal (FG).

The system will only function when the EMF voltage from the motor is present. Consequently, a start oscillator is provided that will generate commutation pulses when no zero-crossings in the motor voltage are available.

A timing function is incorporated into the device for internal timing and for timing of the reverse rotation detection.

The TDA5341 also contains a control amplifier, directly driving output amplifiers.

The TDA5341 also provides access to the user of some of its internal test modes. Firstly, a PRESET mode can be used for prepositioning the three motor output drivers into a fixed state. By pulling pin PRESET to 0.75 V above  $V_{DD}$ , MOT3 goes HIGH, MOT2 goes LOW and MOT1 goes to the high impedance state.

In addition, when TESTIN is pulled HIGH (provided that FREDENA is LOW), the 3 motor output drivers are switched off. It should be noted that RESETOUT goes LOW in that particular event.

#### Adjustments

The system has been designed in such a way that the tolerances of the application components are not critical. However, the approximate values of the following components must still be determined:

- The start capacitor; this determines the frequency of the start oscillator

- The two capacitors in the adaptive commutation delay circuit; these are important in determining the optimum moment for commutation, depending on the type and loading of the motor

- The timing capacitor; this provides the system with its timing signals.

#### The start capacitor (CAPST)

This capacitor determines the frequency of the start oscillator. It is charged and discharged, with a current of  $5.5 \,\mu$ A, from 0.05 to 2.2 V and back to 0.05 V. The time taken to complete one cycle is given by:

$t_{start}$  = (0.78 × C); where C is given in  $\mu$ F.

The start oscillator is reset by a commutation pulse and so is only active when the system is in the start-up mode. A pulse from the start oscillator will cause the outputs to change to the next state (torque in the motor). If the movement of the motor generates enough EMF the TDA5341 will run the motor.

If the amount of EMF generated is insufficient, then the motor will move one step only and will oscillate in its new position. The amplitude of the oscillation must decrease sufficiently before the arrival of the next start pulse, to prevent the pulse arriving during the wrong phase of the oscillation. The oscillation of the motor is given by:

$$f_{osc} = \frac{0.5}{\Pi} \times \left(K_t \times I \times \frac{P}{J}\right)^{\frac{1}{2}}$$

Where:

$K_t$  = torque constant (N.m/A)

I = current (A)

p = number of magnetic pole-pairs

$J = inertia J (kg/m^2).$

Example: J =  $6.34 \times 10^{-7}$  kg/m<sup>2</sup>, K =  $4.5 \times 10^{-3}$  N.m/A, p = 6 and I = 0.48 A; thus f<sub>osc</sub> = 22.7 Hz. Without damping, a start frequency of 48.4 Hz can be chosen or t = 24 ms, thus C =  $0.024/0.78 = 0.031 \mu$ F, (choose 33 nF).

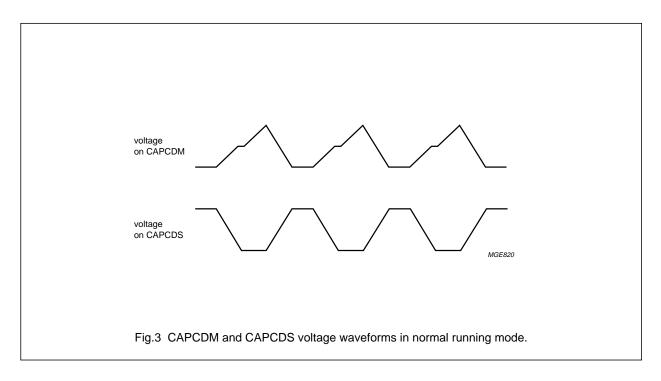

### The Adaptive Commutation Delay (CAPCDM and CAPCDS)

In this circuit capacitor CAPCDM is charged during one commutation period, with an interruption of the charging current during the diode pulse.

# During the next commutation period this capacitor (CAPCDM) is discharged at twice the charging current. The charging current is 10 $\mu$ A and the discharging current 20 $\mu$ A; the voltage range is from 0.87 to 2.28 V. The voltage must stay within this range at the lowest commutation frequency of interest, f<sub>C1</sub>:

$$C = \frac{10 \times 10^{-6}}{f \times 1.41} = \frac{7092}{f_{C1}}$$

Where C is in nF.

If the frequency is lower, then a constant commutation delay after the zero-crossing is generated by the discharge from 2.28 to 0.87 V at 20  $\mu$ A.

Maximum delay =  $(0.070 \times C)$  ms: Where C is in nF.

Example: nominal commutation frequency is 3240 Hz and the lowest usable frequency is 1600 Hz, thus CAPCDM = 7092/1600 = 4.43 (choose 4.7 nF)

The other capacitor, CAPCDS, is used to repeat the same delay by charging and discharging with 20  $\mu$ A. The same value can be chosen as for CAPCDM. Figure 3 illustrates typical voltage waveforms.

1997 Jul 10

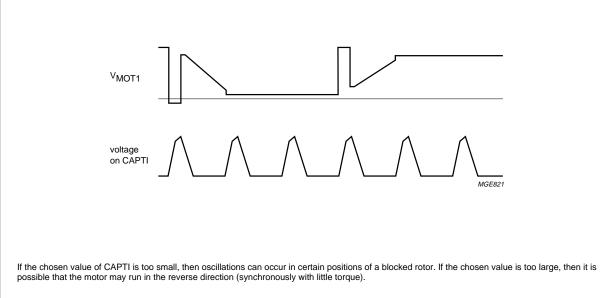

#### The Timing Capacitor (CAPTI)

Capacitor CAPTI is used for timing the successive steps within one commutation period; these steps include some internal delays.

The most important function is the watchdog time in which the motor EMF has to recover from a negative diode pulse back to a positive EMF voltage (or vice-versa). A watchdog timer is a guarding function that only becomes active when the expected event does not occur within a predetermined time.

The EMF usually recovers within a short time if the motor is running normally (<<ms). However, if the motor is motionless or rotating in the reverse direction, then the time can be longer (>>ms).

A watchdog time must be chosen so that it is long enough for a motor without EMF (still) and eddy currents that may stretch the voltage in a motor winding. However, it must be short enough to detect reverse rotation. If the watchdog time is made too long, then the motor may run in the wrong direction (with little torque). The capacitor is charged, with a current of 60  $\mu$ A, from 0.03 to 0.3 V. Above this level it is charged, with a current of 5  $\mu$ A, up to 2.2 V only if the selected motor EMF remains in the wrong polarity (watchdog function). At the end, or, if the motor voltage becomes positive, the capacitor is discharged with a current of 30  $\mu$ A. The watchdog time is the time taken to charge the capacitor, with a current of 5  $\mu$ A, from 0.3 to 2.2 V. The value of CAPTI is given by:

$$C = 5 \times 10^{-6} \times \frac{t_m}{1.9} = 2.63 t_m$$

Where: C is in nF and t is in ms.

Example: If, after switching off, the voltage from a motor winding is reduced, in 3.5 ms, to within 10 mV (the offset of the EMF comparator), then the value of the required timing capacitor is given by:

$C = 2.63 \times 3.5 = 9.2$  (choose 10 nF)

Typical voltage waveforms are illustrated by Fig.4.

#### Other design aspects

There are other design aspects concerning the application of the TDA5341 besides the commutation function. They are as follows:

- · Generation of the tacho signal FG

- Motor control

- Current limiting

- Thermal protection.

#### FG signal

The FG signal is generated in the TDA5341 by using the zero-crossing of the motor EMF from the three motor windings and the commutation signal.

Output FG switches from HIGH-to-LOW on all zero-crossings and LOW-to-HIGH on all commutations and can source more than 40  $\mu A$  and sink more than 1.6 mA.

Example: A three-phase motor with 6 magnetic pole-pairs at 1500 rpm and with a full-wave drive has a commutation frequency of  $25 \times 6 \times 6 = 900$  Hz and generates a tacho signal of 900 Hz.

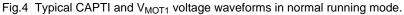

#### Motor control

Figure 5 shows the spindle transconductance by giving the relative output current as a function of the voltage applied to pin CNTRL.

#### 1997 Jul 10

#### Current limiting

Outputs MOT1 to MOT3 are protected against high currents in two ways; current limiting of the 'lower' output transistor and current limiting of the 'upper' one. This means that the current from and to the output stages is limited.

It is possible to adjust the limiting current externally by using an external resistor connected between pin ILIM and ground, the value is determined by the formula:

$$I_{\rm ILIM} = 10020 \times \frac{2.54}{\rm R}$$

Where R = R (min.) = 19.5 k $\Omega$  and I<sub>ILIM</sub> = 1.3 A.

If R < 19.5 k $\Omega$ , then I<sub>ILIM</sub> is internally limited for device protection purposes.

#### Thermal protection

Thermal protection of the six output transistors of the spindle section is achieved by each transistor having a thermal sensor that is active when the transistor is switched on. The transistors are switched off when the local temperature becomes too high. In that event, a RESET is automatically generated to the external world by pulling RESETOUT LOW.

#### **Reset section**

This circuit provides the following:

- An external signal that sends a RESETOUT (active LOW) to the disk drive circuitry at power-up and power-down

- · Causes actuator to retract (PARK).

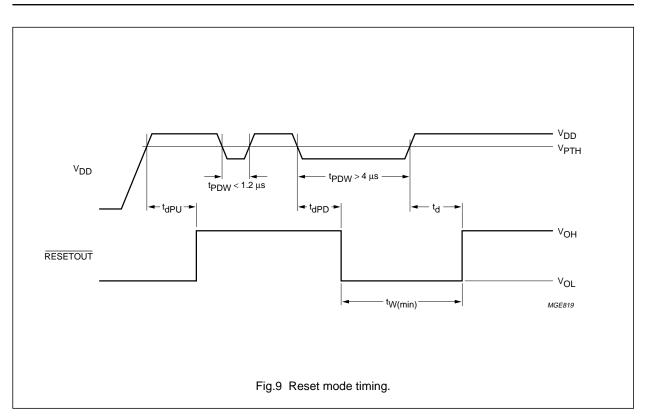

The power-up reset signal (RESETOUT) applied to external circuits as a digital output is typically 150 ms after power-up. In the same way, as soon as  $V_{DD}$  goes below a threshold that is externally set (UVDIN2), RESETOUT goes LOW. The under voltage detection threshold is adjustable with external resistors (see Fig.8).

The reset circuitry has a minimum output pulse (100 ms) even for brief power interruptions (higher than 1 ms). The pulse duration can be adjusted with an external capacitor (UVDIN1).

#### Product specification

TDA5341

# Brushless DC motor and VCM drive circuit with speed control

The power for retraction is received from the rectification of the EMF of the spindle before it is spun down. After retraction, a brake procedure is automatically settled. The time needed for retraction, prior to braking, can be precisely adjusted with the external RC device connected to pin BRAKEDELAY. The discharge of the capacitance across the resistance from  $V_{DD} - 0.7$  V down to 1 V will provide the desired time constant.

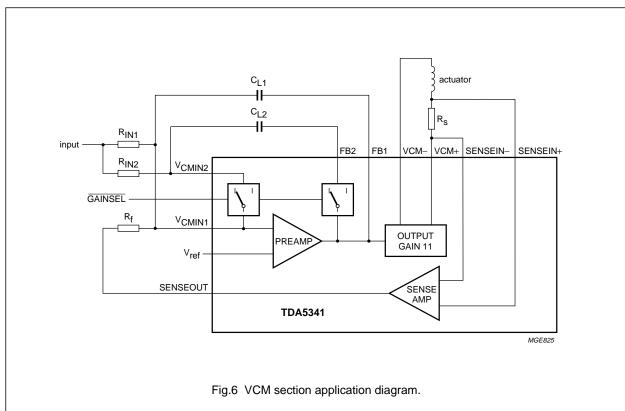

#### Actuator section

The actuator driver has a control input voltage that is proportional to the actuator current which is capable of a closed-loop band-pass frequency higher than 10 kHz.

#### TRANSFER FUNCTION

An operational amplifier input allows passive external components for compensation and gain setting. The compensation amplifier is able to be pulled out of a saturation state within 5  $\mu$ s and its output swing is  $V_{DD} - 1.5$  V.

An actuator current-sense amplifier is provided for use by the disc drive controller. The gain from current-sense resistor to sense the amplifier output is typically 10 ( $\pm$ 3%) and the output voltage swing is  $\pm$ 1.25 V. An input common mode range insures operation through all normal coil voltage excursions. Maximum recovery time from saturation is 20 µs (typ.).

$$T = -11 \times R_{f} \times Z_{L} \times \left(\frac{1}{R_{IN} \times (R_{f} \times R_{s} + R_{f} \times Z_{VCM} + 110 \times R_{s} \times Z_{L})}\right)$$

With  $\overline{\text{GAINSEL}}$  = HIGH;  $R_{IN} = R_{IN1}$

With

$$\overline{\text{GAINSEL}}$$

= LOW;  $R_{\text{IN}} = \frac{R_{\text{IN1}} \times R_{\text{IN2}}}{R_{\text{IN1}} + R_{\text{IN2}}}$

TDA5341

### Brushless DC motor and VCM drive circuit with speed control

#### Speed control function

Speed control is efficiently achieved by the frequency-locked loop circuitry which is enabled by bit D20 of the CONTROL register.

Its aim is to keep the tachometer signal set to a reference programmed by the user via the serial port (see Section "Serial port").

The FLL operates as follows:

When power is first applied to the circuit, the FILTER pin is pulled HIGH so that maximum output current can be sourced for optimum torque.

FG pulses will appear rapidly so as to provide a 'clean' clock signal (FMOT) that will issue one pulse per mechanical revolution. This may be used for speed regulation, by re-entering the signal through the DPULSE pin. Then, after it has been synchronised to the ROSC clock, it is compared to an accurate reference derived from the ROSC clock and programmed by the user via the serial port. The resulting variation in frequency generates a speed error term that will switch a charge-pump up or down in order to charge or discharge an external RC filter (FILTER). The voltage at the FILTER pin is then used as an input to the current control amplifier that regulates the current in both upper and lower NMOS transistors.

A velocity regulation based upon (maximum) one corrective action per mechanical revolution may be considered insufficient in some applications. That is the reason why the second input of the FLL circuitry was intentionally left open-circuit and directly accessible to the external world via pin DPULSE. In that way, total freedom is given to the user to use any signal coming out of the microcontroller in order to regulate the motor velocity with a finer accuracy.

Moreover, a mixed regulation is also possible: firstly, the FMOT signal is fed via DPULSE into the FLL circuitry and then once data is read out off the disc, it is switched to another clock signal with a higher frequency than FMOT. Simultaneously, a new division factor is programmed via the serial port.

It should be noted that there is no need for external synchronization. However, it is recommended to change the division factor and the DPULSE clock rate during the period when FMOT is HIGH.

#### Serial port

The serial port operates as follows:

When ENABLE is HIGH, the serial port is disabled, which means the TDA5341 functions regardless of any change at pins DATA and CLOCK.

When  $\overline{\text{ENABLE}}$  is set LOW some set-up time before the falling edge of CLOCK, the serial port is enabled, i. e. data is serially shifted into the 24-bit shift register on the falling edge of the CLOCK signal. The least significant bit (LSB = DATA 0) is the first in, DATA(23) the MSB is the last in.

When ENABLE goes HIGH, the contents of the shift register are loaded into the internal fixed register (CONTROL register), it will not change until the next rising edge of ENABLE.

It should be noted that when RESET goes HIGH it will force all bits of the shift register and the control register to logic 0. However, there is no reset effect on both power-up and power-down i.e there is no correlation between RESET and RESETOUT.

CLOCK can be stopped (either in the HIGH or LOW state) once RESET or ENABLE have been asserted.

The 24-bit control register is organized as follows:

- D23: SPINDLE DISABLE

- When LOW, the spindle circuitry is enabled

- D22: VCM DISABLE

- When LOW, the actuator circuitry is enabled

- D21: PARK

- When HIGH, it enables the head retraction. This has the same effect as pin RETRACT pulled LOW

- D20: FLL ENABLE

- When HIGH, it closes the complete speed regulation loop

- When LOW, it will set the output of the charge pump (FILTER) to the high impedance state

- D19 and D18

- The combination of these bits fixes the division factor to apply on the FG signal with respect to the number of poles.

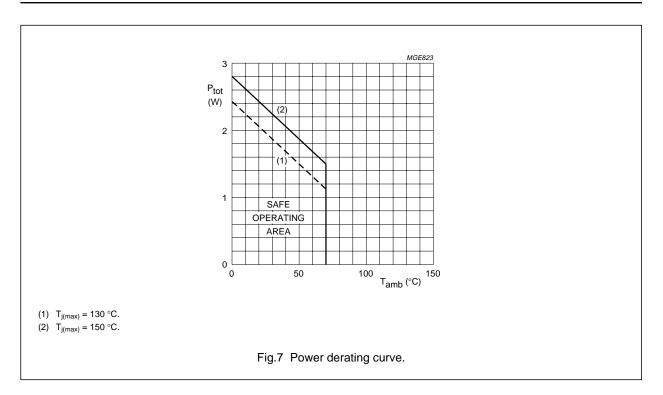

T<sub>amb</sub>

HANDLING

P<sub>tot</sub>

### THERMAL CHARACTERISTICS

| SYMBOL              | PARAMETER                                               | VALUE | UNIT |

|---------------------|---------------------------------------------------------|-------|------|

| R <sub>th j-a</sub> | thermal resistance from junction to ambient in free air | 54    | K/W  |

Every pin withstands the ESD test in accordance with MIL-STD-883C. Method 3015 (HBM 1900 Ω, 100 pF) 3 pulses

positive and 3 pulses negative on each pin with reference to ground. Class 1 : 0 to 1999 V.

1997 Jul 10

Example: for a motor speed of 3600 rpm and a reference oscillation ROSC of 16 MHz, the division factor that has to be programmed via the bus, will be:

$$\mathsf{DIV} = 7.5 \times \frac{16 \times 10^{-6}}{3600} = 33333$$

The resulting error will be less than 0.04 rpm.

0

| In accordance w        | ith the Absolute Maximum Rating System (IEC 134).  |       |                       |      |

|------------------------|----------------------------------------------------|-------|-----------------------|------|

| SYMBOL                 | PARAMETER                                          | MIN.  | MAX.                  | UNIT |

| V <sub>DD</sub>        | positive supply voltage                            | -     | 5.5                   | V    |

| Vi                     | input voltage (all pins)                           | -0.3  | V <sub>DD</sub> + 0.3 | V    |

| V <sub>60,8,21</sub>   | output voltage pins MOT1, MOT2 and MOT3            | -0.25 | +5.5                  | V    |

| V <sub>45,37,53</sub>  | output voltage pins VCM-, VCM+ and SENSEOUT        | 0.7   | V <sub>DD</sub> + 0.7 | V    |

| V <sub>1,2,18,19</sub> | input voltage pins CAPST, CAPTI, CAPCDM and CAPCDS | -     | 2.5                   | V    |

| T <sub>stg</sub>       | IC storage temperature                             | -55   | +150                  | °C   |

| Table 3         Division factor |     |            |  |  |  |  |

|---------------------------------|-----|------------|--|--|--|--|

| D19                             | D18 | POLE PAIRS |  |  |  |  |

| 0                               | 0   | 4          |  |  |  |  |

| 0                               | 1   | 6          |  |  |  |  |

| 1                               | 0   | 8          |  |  |  |  |

| 1                               | 1   | 12         |  |  |  |  |

• D17 to D0

These bits program the division factor to apply to the ROSC signal so as to generate a reference that will precisely control the spindle rotation;

- The division factor can range from 8 (DIV = 1) to  $8 \times [2^{18} - 1] = 2097144$  (DIV = 3FFFF)

- The relationship between this division factor, ROSC and the motor frequency is as follows:

DIVISION FACTOR = 7.5 × ROSC/MOTOR speed where the MOTOR speed is given in rpm and ROSC in Hz.

#### L

operating ambient temperature

total power dissipation

### TDA5341

°C

+70

see Fig.7

TDA5341

# Brushless DC motor and VCM drive circuit with speed control

#### **CHARACTERISTICS (SPINDLE FUNCTION)**

$V_{DD}$  = 5 V;  $V_{DD1}$  and  $V_{DD2}$  >  $V_{DD}$  is not allowed;  $T_{amb}$  = 25 °C; unless otherwise specified.

| SYMBOL             | PARAMETER                                                 | CONDITIONS      | MIN. | TYP.                 | MAX. | UNIT |

|--------------------|-----------------------------------------------------------|-----------------|------|----------------------|------|------|

| Supply             |                                                           |                 |      |                      |      |      |

| V <sub>DD</sub>    | general supply voltage                                    |                 | 4.5  | 5.0                  | 5.25 | V    |

| V <sub>DD1</sub>   | supply voltage 1 for the spindle motor drivers            |                 | 4.5  | 5.0                  | 5.25 | V    |

| V <sub>DD2</sub>   | supply voltage 2 for the spindle motor drivers            |                 | 4.5  | 5.0                  | 5.25 | V    |

| V <sub>DD3</sub>   | supply voltage for the actuator driver                    |                 | 4.5  | 5.0                  | 5.25 | V    |

| I <sub>DD</sub>    | general supply current                                    |                 | -    | 11                   | 15   | mA   |

| I <sub>q(sm)</sub> | quiescent current in sleep mode                           |                 | -    | 1.4                  | 2    | mA   |

| Thermal pro        | otection                                                  |                 |      |                      |      |      |

| T <sub>SD</sub>    | local temperature at temperature sensor causing shut-down |                 | 130  | 140                  | 150  | °C   |

| ΔΤ                 | reduction in temperature before switch-on                 | after shut-down | -    | T <sub>SD</sub> – 30 | -    | °C   |

| V <sub>so</sub>    | test pin switch-off voltage                               |                 | 2.5  | -                    | -    | V    |

| SYMBOL                 | PARAMETER                                                      | CONDITIONS                                           | MIN. | TYP. | MAX.                  |    |

|------------------------|----------------------------------------------------------------|------------------------------------------------------|------|------|-----------------------|----|

| МОТ0                   |                                                                | 1                                                    | 1    | 1    |                       | 1  |

| V <sub>i</sub>         | input voltage level                                            |                                                      | -0.3 | -    | V <sub>DD</sub> – 1.7 | V  |

| I <sub>bias</sub>      | input bias current                                             |                                                      | _1   | -    | 0                     | μA |

| V <sub>CSW</sub>       | comparator switching voltage level                             | note 1                                               | ±6.8 | ±9.2 | ±11.6                 | mV |

| $\Delta V_{CWS}$       | variation in comparator switching voltage levels within one IC |                                                      | -3.4 | -    | +3.4                  | mV |

| MOT1, MOT              | 2 and MOT3; pins 60, 8 and 21                                  | 1                                                    | 1    | -1   | -1                    |    |

| V <sub>DO</sub>        | drop-out voltage                                               | I <sub>o</sub> = 250 mA                              | _    | -    | 0.34                  | V  |

| 20                     |                                                                | I <sub>o</sub> = 250 mA;<br>T <sub>amb</sub> = 70 °C | -    | -    | 0.39                  | V  |

| t <sub>r</sub>         | output rise time                                               | from 0.2 to 0.8V <sub>DD</sub>                       | 10   | 25   | 35                    | μs |

| t <sub>f</sub>         | output fall time                                               | from 0.8 to 0.2V <sub>DD</sub>                       | 10   | 25   | 35                    | μs |

| Output cur             | rent limiting circuit; V <sub>ILIM</sub> = 5 V; pin            | 23                                                   | •    |      |                       | •  |

| I <sub>ILIM</sub>      | limiting current (estimation)                                  | $R_{ILIM} = 20 \text{ k}\Omega$                      | 1.15 | 1.25 | 1.35                  | A  |

| VILIM                  | input voltage                                                  | I <sub>ILIM</sub> = 100 μA                           | 2.43 | 2.51 | 2.60                  | V  |

| I <sub>ILIM(CR)</sub>  | limiting current control range<br>(estimation)                 | $I_{\rm ILIM} = \frac{I_{\rm o}}{10000}$             | 0.01 | -    | 1.3                   | A  |

| Output cur             | rent control circuit; pin 24                                   |                                                      | 1    |      |                       | 1  |

| V <sub>CNTRL</sub>     | input voltage level                                            |                                                      | 0    | -    | V <sub>DD</sub>       | V  |

| C <sub>CPC</sub>       | control loop stability capacitor                               |                                                      | -    | 100  | -                     | nF |

| CAPCPC; p              | bin 22                                                         | •                                                    | 4    | •    | •                     | 1  |

| I <sub>o(sink)</sub>   | output sink current                                            |                                                      | 30   | 40   | 50                    | μA |

| I <sub>o(source)</sub> | output source current                                          |                                                      | -5.5 | -3.5 | -1.5                  | μA |

| CAPCP; pir             | n 27                                                           |                                                      |      |      |                       |    |

| C <sub>extCP</sub>     | external output capacitor for the charge pump                  | note 2                                               | 22   | -    | -                     | nF |

| I <sub>o(sink)</sub>   | output sink current                                            | $V_{DD} = 0 V;$<br>$V_{clamp} = 1.2 V$               | -    | 1    | 2.5                   | μA |

| V <sub>CP</sub>        | charge pump voltage                                            |                                                      | 9.0  | 9.9  | 10.8                  | V  |

| CAPST; pin             | 1                                                              | •                                                    |      | •    | •                     |    |

| I <sub>o(sink)</sub>   | output sink current                                            |                                                      | 4.5  | 6.0  | 7.5                   | μA |

| I <sub>o(source)</sub> | output source current                                          |                                                      | -7.0 | -5.5 | -4.0                  | μA |

| V <sub>SW(L)</sub>     | lower switching level                                          |                                                      | -    | 0.20 | -                     | V  |

| V <sub>SW(M)</sub>     | middle switching level                                         |                                                      | -    | 0.30 | -                     | V  |

| V <sub>SW(H)</sub>     | upper switching level                                          |                                                      | -    | 2.20 | -                     | V  |

| Product specification |

|-----------------------|

|                       |

TDA5341

| SYMBOL                  | PARAMETER                                          | CONDITIONS              | MIN.  | TYP. | MAX.            | UNIT |

|-------------------------|----------------------------------------------------|-------------------------|-------|------|-----------------|------|

| CAPTI; pin              | 2                                                  |                         | •     |      | •               | •    |

| I <sub>o(sink)</sub>    | output sink current                                |                         | 25    | 35   | 45              | μA   |

| I <sub>oH(source)</sub> | HIGH level output source current                   |                         | -85   | -70  | -55             | μA   |

| oL(source)              | LOW level lower source current                     |                         | -7.5  | -5.0 | -2.5            | μA   |

| V <sub>SW(L)</sub>      | lower switching level                              |                         | -     | 30   | -               | mV   |

| V <sub>SW(M)</sub>      | middle switching level                             |                         | -     | 0.3  | -               | V    |

| V <sub>SW(H)</sub>      | upper switching level                              |                         | -     | 2.2  | -               | V    |

| CAPCDM; p               | bin 18                                             |                         | •     |      | •               | •    |

| o(sink)                 | output sink current                                |                         | 13    | 20   | 27              | μA   |

| o(source)               | output source current                              |                         | -13.5 | -10  | -6.5            | μA   |

| sink/Isource            | ratio of sink-to-source current                    |                         | -2.2  | -2.0 | -1.8            |      |

| VIL                     | LOW level input voltage                            |                         | 0.82  | 0.87 | 0.92            | V    |

| V <sub>IH</sub>         | HIGH level input voltage                           |                         | 2.20  | 2.28 | 2.37            | V    |

| CAPCDS; p               | bin 19                                             |                         | •     |      | •               | •    |

| o(sink)                 | output sink current                                |                         | 13    | 20   | 27              | μA   |

| o(source)               | output source current                              |                         | -27   | -20  | -13             | μA   |

| sink/Isource            | ratio of sink-to-source current                    |                         | -1.1  | -1.0 | -0.9            | μA   |

| V <sub>IL</sub>         | LOW level input voltage                            |                         | 0.82  | 0.87 | 0.92            | V    |

| V <sub>IH</sub>         | HIGH level input voltage                           |                         | 2.20  | 2.28 | 2.37            | V    |

| FG; pin 10              |                                                    |                         |       |      |                 |      |

| V <sub>OL</sub>         | LOW level output voltage                           | I <sub>o</sub> = 0 μA   | -     | -    | 0.5             | V    |

| OL                      | LOW level output current                           | V <sub>OL</sub> = 1 V   | 3.3   | 5.3  | -               | mA   |

| ОН                      | HIGH level output current                          | V <sub>OH</sub> = 4.5 V | -     | -83  | -40             | mA   |

| R <sub>F</sub>          | ratio of FG frequency and<br>commutation frequency |                         | -     | 1    | -               |      |

| δ                       | duty factor                                        |                         | -     | 50   | -               | %    |

| BRAKE; pir              | n 11                                               | •                       | •     |      |                 | •    |

| NM                      | normal mode current                                | V <sub>NM</sub> = 2.8 V | -40   | -27  | -               | μA   |

| V <sub>NM</sub>         | normal mode voltage                                |                         | 2.65  | -    | V <sub>DD</sub> | V    |

| V <sub>BM</sub>         | brake mode voltage                                 |                         | -     | -    | 2.35            | V    |

| BM                      | brake mode current                                 |                         | -40   | -24  | -               | μA   |

| Upper conv              | verter; pins 61 and 62                             |                         |       |      |                 |      |

| C <sub>XA</sub>         | external pump capacitor pin 61                     |                         | -     | 10   | -               | nF   |

| C <sub>YA</sub>         | external pump capacitor pin 62                     |                         | _     | 10   | _               | nF   |

#### Notes

1. Switching levels with respect to MOT1, MOT2 and MOT3.

2. CAPCP value is dependant of the powerless park and brake operations.

#### **CHARACTERISTICS (RESET FUNCTION)**

$V_{DD}$  = 5 V;  $V_{DD1}$  and  $V_{DD2}$  >  $V_{DD}$  is not allowed;  $T_{amb}$  = 25 °C; unless otherwise specified.

| SYMBOL              | PARAMETER                                                      | CONDITIONS                  | MIN.  | TYP.  | MAX.  | UNIT |

|---------------------|----------------------------------------------------------------|-----------------------------|-------|-------|-------|------|

| UVDIN1; pin 4       | 4                                                              |                             |       | -     |       | -    |

| I <sub>UVDIN1</sub> | load capacitance current to control the reset pulse width      |                             | -2.3  | -1.7  | -1.3  | μA   |

| V <sub>UVDIN1</sub> | input voltage threshold to activate the reset output           |                             | 2.4   | 2.55  | 2.75  | V    |

| UVDIN2; pin 5       | 4                                                              | ·                           | •     |       | ·     | •    |

| V <sub>UVDIN2</sub> | comparator voltage for<br>power-up and power-down<br>detection | see Fig.8                   | 1.280 | 1.315 | 1.340 | V    |

| I <sub>UVDIN2</sub> | input current                                                  | V <sub>UVDIN2</sub> = 1.6 V | -0.5  | -     | +0.5  | μA   |

| RESETOUT; p         | in 43                                                          |                             |       |       |       |      |

| V <sub>PTH</sub>    | power threshold voltage                                        | see Fig.9                   | -     | 4.25  | -     | V    |

| t <sub>dPU</sub>    | power-up reset delay                                           | C = 0.1 μF;<br>see Fig.9    | 100   | 150   | 200   | ms   |

| t <sub>dPD</sub>    | power-down reset delay                                         | see Fig.9                   | -     | -     | 4     | μs   |

| t <sub>PDW</sub>    | power-down reset pulse width                                   | see Fig.9                   | 1.0   | -     | 4     | μs   |

| t <sub>W(min)</sub> | minimum output pulse width                                     | C = 0.1 μF                  | 100   | -     | -     | ms   |

| R <sub>pu</sub>     | pull-up resistance                                             |                             | 6     | 10    | 14    | kΩ   |

| V <sub>OL</sub>     | LOW level output voltage                                       | I <sub>OL</sub> = 8.5 mA    | -     | -     | 0.5   | V    |

TDA5341

# Brushless DC motor and VCM drive circuit with speed control

#### **CHARACTERISTICS (VCM FUNCTION)**

$V_{DD}$  = 5 V;  $V_{DD1}$  and  $V_{DD2}$  >  $V_{DD}$  is not allowed;  $T_{amb}$  = 25 °C; unless otherwise specified.

| SYMBOL                    | PARAMETER                     | CONDITIONS                      | MIN. | TYP.                   | MAX.            | UNIT     |

|---------------------------|-------------------------------|---------------------------------|------|------------------------|-----------------|----------|

| SENSEIN- ar               | nd SENSEIN+; pins 51 and 52   | 1                               |      |                        |                 | <b>!</b> |

| V <sub>CS</sub>           | common input sense voltage    |                                 | 0    | -                      | V <sub>DD</sub> | V        |

| I <sub>ISENSE</sub>       | input sense current           |                                 | -250 | -                      | +250            | μA       |

| SENSEOUT;                 | pin 53                        |                                 |      |                        |                 |          |

| $\Delta V_{\text{SENSE}}$ | differential output voltage   | V <sub>ref</sub> = 1.9 to 2.6 V | 0.5  | V <sub>ref</sub> ±1.25 | 4.0             | V        |

| I <sub>oSENSE</sub>       | output sense current          |                                 | -250 | _                      | +250            | μA       |

| G <sub>SENSE</sub>        | sense amplifier gain          |                                 | 9.9  | 10.2                   | 10.5            |          |

| f <sub>co</sub>           | cross-over frequency          |                                 | _    | 40                     | -               | MHz      |

| V <sub>o(os)</sub>        | output offset voltage         | I <sub>SENSEIN</sub> = 0        | -66  | -                      | +66             | mV       |

| t <sub>RSA</sub>          | recovery time from saturation |                                 | -    | 20                     | -               | μs       |

| V <sub>ref</sub> ; pin 36 |                               | -                               |      |                        | •               | •        |

| V <sub>ref</sub>          | reference input voltage       |                                 | 1.9  | -                      | 2.6             | V        |

| I <sub>ref</sub>          | reference input current       |                                 | -5   | -                      | +5              | μA       |

| SYMBOL             | PARAMETER                             | CONDITIONS                               | MIN.                   | TYP. | MAX.                | UNIT |

|--------------------|---------------------------------------|------------------------------------------|------------------------|------|---------------------|------|

| VCM+ and V         | CM–; pins 37 and 45                   |                                          | 1                      | 1    | 1                   |      |

| V <sub>CMdo</sub>  | drop-out voltage                      | l <sub>o</sub> = 400 mA                  | -                      | 0.8  | 1.0                 | V    |

| I <sub>oLIM</sub>  | output current limiting               |                                          | 0.7                    | 1.15 | 1.5                 | А    |

| G <sub>v</sub>     | power amplifier voltage gain          |                                          | 9                      | -    | 12                  |      |

| V <sub>oPARK</sub> | output park voltage                   | $R_L = 40 \Omega$ ; note 1               | -                      | 0.75 | _                   | V    |

| VCMIN1 and         | VCMIN2                                |                                          |                        |      |                     |      |

| Vi                 | input voltage level                   |                                          | 1.9                    | -    | 2.6                 | V    |

| I <sub>ibias</sub> | input bias current                    |                                          | -                      | _    | 0.25                | μA   |

| I <sub>i(os)</sub> | input offset current                  |                                          | -                      | 25   | -                   | nA   |

| GAINSEL; pi        | n 15                                  |                                          |                        |      |                     |      |

| V <sub>IH</sub>    | HIGH level input voltage              |                                          | 2                      | -    | -                   | V    |

| V <sub>IL</sub>    | LOW level input voltage               |                                          | -                      | -    | 0.8                 | V    |

| I <sub>IH</sub>    | HIGH level input current              |                                          | -10                    | -    | +10                 | μA   |

| IIL                | LOW level input current               |                                          | -20                    | -    | +10                 | μA   |

| R <sub>SW</sub>    | switch resistance                     | $\overline{\text{GAINSEL}} = \text{LOW}$ | -                      | -    | 40                  | Ω    |

|                    |                                       | GAINSEL = HIGH                           | 10                     | -    | -                   | MΩ   |

| FB1 and FB2        | 2; pins 28 and 29                     |                                          |                        |      |                     |      |

| V <sub>i(os)</sub> | input offset voltage                  |                                          | -5                     | -    | +5                  | mV   |

| $\Delta V_{FB}$    | feed-back differential output voltage | V <sub>DD</sub> = 5.25 V                 | ±0.4                   | -    | $\pm V_{DD} - 0.45$ | V    |

| f <sub>co</sub>    | cross-over frequency                  |                                          | -                      | 10   | -                   | MHz  |

| I <sub>oFB</sub>   | feed-back output current              |                                          | -250                   |      | +250                | μA   |

| t <sub>RSB</sub>   | recovery time from saturation         |                                          | -                      | 5    | -                   | μs   |

| R <sub>SW</sub>    | switch resistance                     | $\overline{\text{GAINSEL}}$ = LOW        | -                      | -    | 40                  | Ω    |

|                    |                                       | GAINSEL = HIGH                           | 10                     | -    | _                   | MΩ   |

| RETRACT; p         | in 30                                 |                                          |                        |      |                     |      |

| V <sub>IH</sub>    | HIGH level input voltage              |                                          | 2                      | -    | -                   | V    |

| VIL                | LOW level input voltage               |                                          | -                      | -    | 0.8                 | V    |

| I <sub>IH</sub>    | HIGH level input current              |                                          | -10                    | -    | +10                 | μA   |

| IIL                | LOW level input current               |                                          | -20                    | -    | +10                 | μA   |

| BRAKEDELA          | AY; pin 46                            |                                          |                        |      |                     |      |

| V <sub>BM</sub>    | brake mode threshold voltage          |                                          | -                      | 0.75 | 1.0                 | V    |

| V <sub>NM</sub>    | normal mode voltage                   |                                          | V <sub>DD</sub> – 0.85 | _    | _                   | V    |

### TDA5341

| SYMBOL               | PARAMETER                         | CONDITIONS                | MIN. | TYP. | MAX. | UNIT |

|----------------------|-----------------------------------|---------------------------|------|------|------|------|

| Uncommitted          | l operational amplifier; pins 4 t | 0 6                       |      | •    |      | •    |

| V <sub>i(os)</sub>   | input offset voltage              |                           | -3.5 | -    | +3.5 | mV   |

| I <sub>i(bias)</sub> | input bias current                |                           | -250 | -    | +250 | nA   |

| I <sub>i(os)</sub>   | input offset current              |                           | -    | 25   | -    | nA   |

| V <sub>CM</sub>      | common mode voltage               |                           | 1.7  | -    | 2.6  | V    |

| G <sub>OL</sub>      | open loop gain                    |                           | -    | 68   | -    | dB   |

| f <sub>co</sub>      | cross-over frequency              |                           | -    | 10   | -    | MHz  |

| V <sub>OL</sub>      | LOW level output voltage          | I <sub>OL</sub> = 250 μA  | -    | -    | 0.7  | V    |

| V <sub>OH</sub>      | HIGH level output voltage         | I <sub>OH</sub> = -250 μA | 4.3  | -    | -    | V    |

#### Note

1. This is the PARK default value. Other values can be obtained with a metal mask change.

#### CHARACTERISTICS (SPEED CONTROL FUNCTION)

$V_{DD}$  = 5 V;  $V_{DD1}$  and  $V_{DD2}$  >  $V_{DD}$  is not allowed;  $T_{amb}$  = 25 °C; unless otherwise specified.

| SYMBOL                                 | PARAMETER                       | CONDITIONS | MIN. | TYP. | MAX. | UNIT     |

|----------------------------------------|---------------------------------|------------|------|------|------|----------|

| FILTER; pin 32                         | 2                               |            | -    | •    |      |          |

| I <sub>o(sink)</sub>                   | output sink current             |            | 80   | 100  | 120  | μA       |

| I <sub>o(source)</sub>                 | output source current           |            | -110 | -90  | -70  | μA       |

| I <sub>sink</sub> /I <sub>source</sub> | ratio of sink-to-source current |            | 0.9  | 1.1  | 1.2  |          |

| I <sub>LO</sub>                        | charge pump leakage current     |            | -5   | -    | +5   | nA       |

| DATA, RESET                            | and ENABLE; pins 38, 57 and 42  |            |      |      |      |          |

| V <sub>IL</sub>                        | LOW level input voltage         |            | -    | -    | 0.8  | V        |

| V <sub>IH</sub>                        | HIGH level input voltage        |            | 2.4  | -    | -    | V        |

| li                                     | input current                   |            | -    | 0    | -    | μA       |

| CLOCK; pin 3                           | 9                               |            |      | •    |      |          |

| V <sub>IL</sub>                        | LOW level input voltage         |            | -    | -    | 0.8  | V        |

| V <sub>IH</sub>                        | HIGH level input voltage        |            | 2.4  | -    | -    | V        |

| f <sub>clk</sub>                       | clock frequency                 |            | -    | _    | 18   | MHz      |

| ROSC; pin 48                           |                                 |            | •    | ·    |      |          |

| V <sub>IL</sub>                        | LOW level input voltage         |            | -    | -    | 0.8  | V        |

| V <sub>IH</sub>                        | HIGH level input voltage        |            | 2.4  | -    | -    | V        |

| f <sub>refOSC</sub>                    | reference oscillator frequency  |            | 1    | _    | 20   | MHz      |

| DPULSE; pin                            | 35                              |            | •    | ·    |      | <b>.</b> |

| V <sub>IL</sub>                        | LOW level input voltage         |            | -    | -    | 0.8  | V        |

| V <sub>IH</sub>                        | HIGH level input voltage        |            | 2.4  | _    | -    | V        |

| f <sub>DPULSE</sub>                    | data pulse frequency            |            | -    | _    | 10   | MHz      |

Timing; see Fig.10

δ

t<sub>su1</sub>

### Brushless DC motor and VCM drive circuit with speed control

ENABLE set-up time

#### SYMBOL CONDITIONS MIN. TYP. MAX. PARAMETER FMOT; pin 58 LOW level output voltage $V_{OL}$ $I_{OL} = 500 \ \mu A$ 0.1 \_ \_ duty factor 50

\_

8

| t <sub>su2</sub> | DATA set-up time |                      | 6  | -   | -      | ns |

|------------------|------------------|----------------------|----|-----|--------|----|

| t <sub>h</sub>   | DATA hold time   |                      | 10 | -   | -      | ns |

|                  | CLOCK            |                      | ·  |     |        |    |

|                  | SHIFTED DATA     |                      |    | · · | MGE824 |    |

|                  | Fi               | g.10 Timing diagram. |    |     |        |    |

#### 1997 Jul 10

UNIT

V

%

ns

\_

\_

\_

#### APPLICATION INFORMATION

TDA5341

# Brushless DC motor and VCM drive circuit with speed control

#### PACKAGE OUTLINE

#### SOLDERING

#### Introduction

There is no soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and surface mounted components are mixed on one printed-circuit board. However, wave soldering is not always suitable for surface mounted ICs, or for printed-circuits with high population densities. In these situations reflow soldering is often used.

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our "IC Package Databook" (order code 9398 652 90011).

#### **Reflow soldering**

Reflow soldering techniques are suitable for all LQFP packages.

Reflow soldering requires solder paste (a suspension of fine solder particles, flux and binding agent) to be applied to the printed-circuit board by screen printing, stencilling or pressure-syringe dispensing before package placement.

Several techniques exist for reflowing; for example, thermal conduction by heated belt. Dwell times vary between 50 and 300 seconds depending on heating method. Typical reflow temperatures range from 215 to 250 °C.

Preheating is necessary to dry the paste and evaporate the binding agent. Preheating duration: 45 minutes at 45 °C.

#### Wave soldering

Wave soldering is **not** recommended for LQFP packages. This is because of the likelihood of solder bridging due to closely-spaced leads and the possibility of incomplete solder penetration in multi-lead devices. If wave soldering cannot be avoided, the following conditions must be observed:

- A double-wave (a turbulent wave with high upward pressure followed by a smooth laminar wave) soldering technique should be used.

- The footprint must be at an angle of 45° to the board direction and must incorporate solder thieves downstream and at the side corners.

### Even with these conditions, do not consider wave soldering LQFP packages LQFP48 (SOT313-2), LQFP64 (SOT314-2) or LQFP80 (SOT315-1).

During placement and before soldering, the package must be fixed with a droplet of adhesive. The adhesive can be applied by screen printing, pin transfer or syringe dispensing. The package can be soldered after the adhesive is cured.

Maximum permissible solder temperature is 260 °C, and maximum duration of package immersion in solder is 10 seconds, if cooled to less than 150 °C within 6 seconds. Typical dwell time is 4 seconds at 250 °C.

A mildly-activated flux will eliminate the need for removal of corrosive residues in most applications.

#### **Repairing soldered joints**

Fix the component by first soldering two diagonallyopposite end leads. Use only a low voltage soldering iron (less than 24 V) applied to the flat part of the lead. Contact time must be limited to 10 seconds at up to 300 °C. When using a dedicated tool, all other leads can be soldered in one operation within 2 to 5 seconds between 270 and 320 °C.

TDA5341

#### DEFINITIONS

| Data sheet status                                                                                             |                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Objective specification                                                                                       | This data sheet contains target or goal specifications for product development.                                                                                                                                                                                                                                                                 |  |  |  |

| Preliminary specification This data sheet contains preliminary data; supplementary data may be published late |                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| Product specification This data sheet contains final product specifications.                                  |                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| Limiting values                                                                                               |                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| more of the limiting values n<br>of the device at these or at a                                               | accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or<br>hay cause permanent damage to the device. These are stress ratings only and operation<br>any other conditions above those given in the Characteristics sections of the specification<br>imiting values for extended periods may affect device reliability. |  |  |  |

| Application information                                                                                       |                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

Where application information is given, it is advisory and does not form part of the specification.

#### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.

### Philips Semiconductors – a worldwide company