1.25Gbits/sec Gigabit Ethernet Transceiver

#### **Features**

- Gigabit Ethernet Transceiver @ 1.25Gb/s

- Compliant to IEEE 802.3Z PMA

- TTL Interface Compatible to PMA-TBI

- Monolithic Clock Synthesis and Clock Recovery - No External Components

- 125MHz TTL Reference Clock

- Low Power Operation 700 mW

- Suitable for Both Coaxial or Optical Link Applications

- 64 Pin, 14mm or 10mm Standard PQFP

- Single +3.3V Supply

### **General Description**

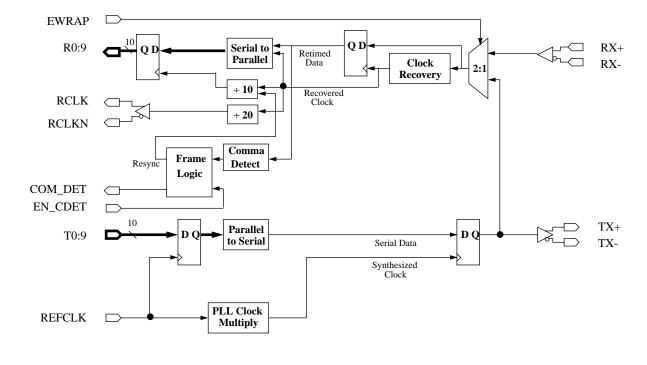

The VSC7135 is a 1.25Gb/s Ethernet Transceiver optimized for Gigabit Ethernet or 1000Base-X applications. It accepts 10-bit 8B/10B encoded transmit data, latches it on the rising edge of REFCLK and serializes it onto the TX PECL differential outputs at a baud rate which is ten times the REFCLK frequency. The VSC7135 also samples serial receive data on the RX PECL differential inputs, recovers the clock and data, deserializes it onto the 10-bit receive data bus, outputs two recovered clocks at one-twentieth of the incoming baud rate and detects "Comma" characters. The VSC7135 contains on-chip PLL circuitry for synthesis of the baud-rate transmit clock, and extraction of the clock from the received serial stream. These circuits are fully monolithic and require no external components.

## VSC7135 Block Diagram

Data Sheet VSC7135

### Functional Description

#### **Clock Synthesizer**

The VSC7135 clock synthesizer multiplies the reference frequency provided on the REFCLK pin by 10 to achieve a baud rate clock at nominally 1.25GHz. The clock synthesizer contains a fully monolithic PLL which does not require any external components.

#### Serializer

The VSC7135 accepts TTL input data as a parallel 10 bit character on the T0:9 bus which is latched into the input latch on the rising edge of REFCLK. This data will be serialized and transmitted on the TX PECL differential outputs at a baud rate of ten times the frequency of the REFCLK input, with bit T0 transmitted first. User data should be encoded for transmission using the 8B/10B block code described in the Fibre Channel specification, or an equivalent, edge rich, DC-balanced code.

#### **Transmission Character Interface**

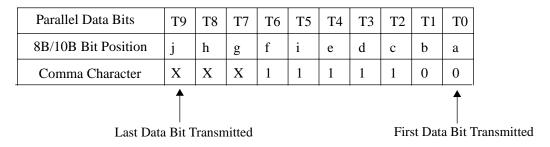

An encoded byte is 10 bits and is referred to as a transmission character. The 10 bit interface on the VSC7135 corresponds to a transmission character. This mapping is illustrated in Figure 2.

Figure 1: Transmission Order and Mapping of an 8B/10B Character

#### **Clock Recovery**

The VSC7135 accepts differential high speed serial inputs on the RX+/RX- pins, extracts the clock and retimes the data. The serial bit stream should be encoded so as to provide DC balance and limited run length by an 8B/10B transmitter or equivalent. The VSC7135 clock recovery circuitry is completely monolithic and requires no external components. For proper operation, the baud rate of the data stream to be recovered should be within 0.01% of ten times the REFCLK frequency. For example if the REFCLK used is 125MHz, then the incoming serial baud rate must be 1.25 gigabaud  $\pm 0.01\%$ .

#### Deserializer

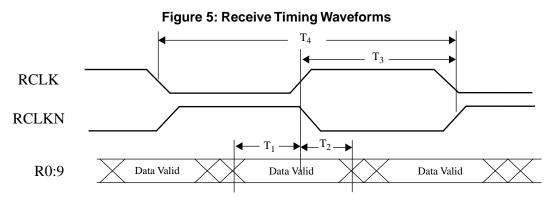

The retimed serial bit stream is converted into a 10-bit parallel output character. The VSC7135 provides complementary TTL recovered clocks, RCLK and RCLKN, which are at one-twentieth of the serial baud rate. This architecture is designed to simplify demultiplexing of the 10-bit data characters into a 20-bit half-word in the downstream controller chip. The clocks are generated by dividing down the high-speed clock which is phase locked to the serial data. The serial data is retimed by the internal high-speed clock, and deserialized. The result-

1.25Gbits/sec Gigabit Ethernet Transceiver

ing parallel data will be captured by the adjoining protocol logic on the rising edges of RCLK and RCLKN. In order to maximize the setup and hold times available at this interface, the parallel data is loaded into the output register at a point nominally midway between the transition edges of RCLK and RCLKN.

If serial input data is not present, or does not meet the required baud rate, the VSC7135 will continue to produce a recovered clock so that downstream logic may continue to function. The RCLK and RCLKN output frequency under these circumstances may differ from their expected frequency by no more than  $\pm 1\%$ .

#### **Word Alignment**

The VSC7135 provides 7-bit comma character recognition and data word alignment. Word synchronization is enabled by asserting EN\_CDET HIGH. When synchronization is enabled, the VSC7135 constantly examines the serial data for the presence of the "Comma" character. This pattern is "0011111XXX", where the leading zero corresponds to the first bit received. The comma sequence is not contained in any normal 8B/10B coded data character or pair of adjacent characters. It occurs only within special characters, known as K28.1, K28.5 and K28.7, which are defined specifically for synchronization purposes. Improper alignment of the comma character is defined as any of the following conditions:

- 1) The comma is not aligned within a the 10-bit transmission character such that T0...T6 = "0011111"

- 2) The comma straddles the boundary between two 10-bit transmission characters.

- 3) The comma is properly aligned but occurs in the received character presented during the rising edge of RCLK rather than RCLKN.

When EN\_CDET is HIGH and an improperly aligned comma is encountered, the internal data is shifted in such a manner that the comma character is aligned properly in R0:9. This results in proper character and half-word alignment. When the parallel data alignment changes in response to a improperly aligned comma pattern, some data which would have been presented on the parallel output port may be lost. However, the synchronization character and subsequent data will be output correctly and properly aligned. When EN\_CDET is LOW, the current alignment of the serial data is maintained indefinitely, regardless of data pattern.

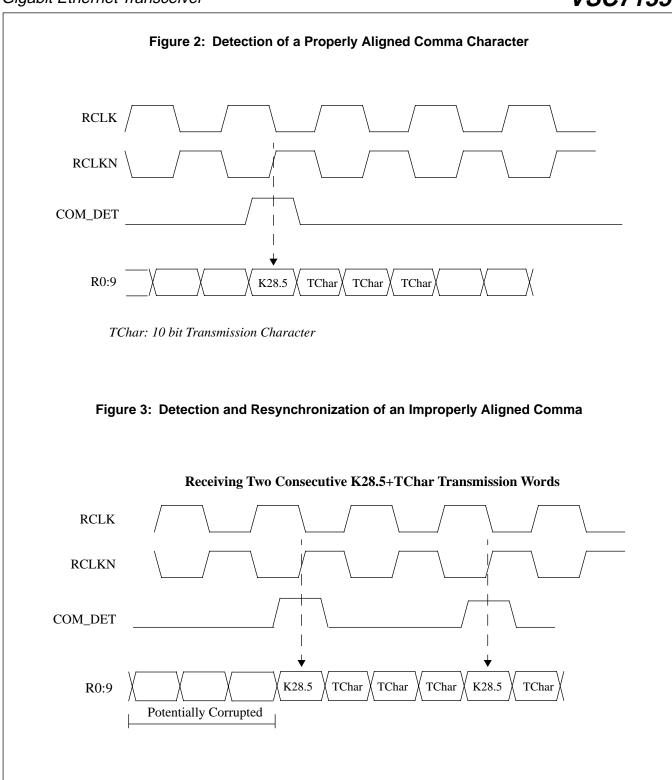

On encountering a comma character, COM\_DET is driven HIGH to inform the user that realignment of the parallel data field may have occurred. The COM\_DET pulse is presented simultaneously with the comma character and has a duration equal to the data, or half of an RCLK period. The COM\_DET signal is timed such that it can be captured by the adjoining protocol logic on the rising edge of RCLKN. Functional waveforms for synchronization are given in Figure 3 and Figure 4. Figure 3 shows the case when a comma character is detected and no phase adjustment is necessary. It illustrates the position of the COM\_DET pulse in relation to the comma character on R0:9. Figure 4 shows the case where the K28.5 is detected, but it is out of phase and a change in the output data alignment is required. Note that up to three characters prior to the comma character may be corrupted by the realignment process.

# Data Sheet VSC7135

1.25Gbits/sec Gigabit Ethernet Transceiver

### AC Characteristics

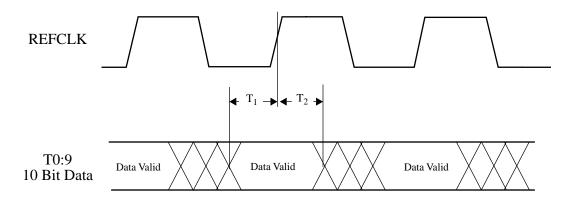

Figure 4: Transmit Timing Waveforms

**Table 1: Transmit AC Characteristics**

| Parameters                         | Description                                                    | Min           | Max        | Units | Conditions                                                               |

|------------------------------------|----------------------------------------------------------------|---------------|------------|-------|--------------------------------------------------------------------------|

| T <sub>1</sub>                     | T0:9 Setup time to the rising edge of REFCLK                   | 1.5           | _          | ns.   | Measured between thevalid data level of T0:9 to the 1.4V point of REFCLK |

| $T_2$                              | T0:9 hold time after the rising edge of REFCLK                 | 1.0           | _          | ns.   |                                                                          |

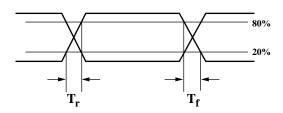

| T <sub>SDR</sub> ,T <sub>SDF</sub> | TX+/TX- rise and fall time                                     | _             | 300        | ps.   | 20% to 80%, 75 Ohm load to Vss, Tested on a sample basis                 |

| $T_{LAT}$                          | Latentcy from rising edge of REFCLK to T0 appearing on TX+/TX- | 11bc - 1ns    |            | ns.   | bc = Bit clocks<br>ns = Nano second                                      |

|                                    | Transmit                                                       | ter Output Ji | tter Alloc | ation |                                                                          |

| $T_{\mathrm{J}}$                   | Total data output jitter (p-p)                                 |               | 192        | ps.   | IEEE 802.3Z Clause 38.68, tested on a sample basis                       |

| $T_{\mathrm{DJ}}$                  | Serial data output<br>deterministic jitter (p-p)               | _             | 80         | ps.   | IEEE 802.3Z Clause 38.69, tested on a sample basis                       |

# Data Sheet VSC7135

**Table 2: Receive AC Characteristics**

| Parameters        | Description                                                                                                  | Min.       | Max.       | Units | Conditions                                                  |

|-------------------|--------------------------------------------------------------------------------------------------------------|------------|------------|-------|-------------------------------------------------------------|

| T <sub>1</sub>    | Data or COM_DET Valid prior to RCLK/RCLKN rise                                                               | 3.0        | _          | ns.   | Measured between the 1.4V point of RCLK or RCLKN            |

| T <sub>2</sub>    | Data or COM_DET Valid<br>after RCLK or RCLKN<br>rise                                                         | 2.0        | _          | ns.   | and a valid level of R0:9. All outputs driving 10pF load.   |

| T <sub>3</sub>    | Deviation of RCLK rising edge to RCLKN rising edge delay from nominal. $delay = \frac{f_{baud}}{10} \pm T_3$ | -500       | 500        | ps.   | Nominal delay is 10 bit times.<br>Tested on sample basis    |

| T <sub>4</sub>    | Deviation of RCLK, RCLKN frequency from nominal. $f_{RCLK} = \frac{f_{REFCLK}}{2} \pm T_4$                   | -1.0       | 1.0        | %     | Whether or not locked to serial data                        |

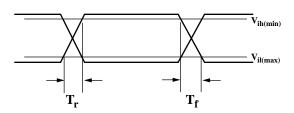

| $T_R, T_F$        | R0:9, COM_DET, RCLK, RCLKN rise and fall time                                                                | _          | 2.4        | ns.   | Between $V_{il(max)}$ and $V_{ih(min)}$ , into 10 pf. load. |

| R <sub>lat</sub>  | Latency from RX to R0:9                                                                                      | 15bc + 2ns | 34bc + 2ns |       | bc = Bit clock<br>ns = Nano second                          |

| T <sub>LOCK</sub> | Data acquisition lock time @ 1.25 Gb/s                                                                       | _          | 2.0        | μs.   | 8B/10B IDLE pattern.<br>Tested on a sample basis            |

| T <sub>jtd</sub>  | Total receive data jitter tolerance (p-p)                                                                    |            | 599        | ps    | IEEE 802.3Z Clause 38.68, tested on a sample basis          |

| D <sub>jtd</sub>  | Total deterministic data<br>jitter tolerance (p-p)                                                           |            | 370        | ps    | IEEE 802.3Z Clause 38.69, tested on a sample basis          |

NOTE: Probability of Recovery for data acquisition is 95% per section 5.3 of the FC-PH rev. 4.3.

1.25Gbits/sec Gigabit Ethernet Transceiver

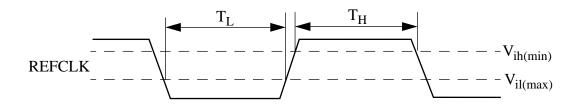

Figure 6: REFCLK Timing Waveforms

**Table 3: Reference Clock Requirements**

| Parameters            | Description                                          | Min  | Max | Units | Conditions                                                                                              |

|-----------------------|------------------------------------------------------|------|-----|-------|---------------------------------------------------------------------------------------------------------|

| FR                    | Frequency Range                                      | 123  | 127 | MHz   | Range over which both transmit<br>and receive reference clocks on any<br>link may be centered           |

| FO                    | Frequency Offset                                     | -200 | 200 | ppm.  | Maximum frequency offset<br>between transmit and receive<br>reference clocks on one link                |

| DC                    | REFCLK duty cycle                                    | 30   | 70  | %     | Measured at 1.5V                                                                                        |

| $T_{RCR}$ , $T_{RCF}$ | REFCLK rise and fall time                            | _    | 2.0 | ns.   | Between V <sub>il(max)</sub> and V <sub>ih(min)</sub>                                                   |

| REFCLK<br>Jitter      | REFCLK Jitter Power $5MHz$ $\int PhaseNoise$ $100Hz$ | _    | 40  | ps.   | dbc, RMS for 10 <sup>-12</sup> Bit Error Ratio with zero length external path. Tested on a sample basis |

# Data Sheet VSC7135

### **DC Characteristics** (Over recommended operating conditions).

| Parameters                    | Description                                                 | Min  | Тур | Max  | Units | Conditions                                                                             |

|-------------------------------|-------------------------------------------------------------|------|-----|------|-------|----------------------------------------------------------------------------------------|

| V <sub>OH</sub>               | Output HIGH voltage (TTL)                                   | 2.4  | _   | _    | V     | $I_{OH} = -1.0 \text{ mA}$                                                             |

| V <sub>OL</sub>               | Output LOW voltage (TTL)                                    | _    | _   | 0.5  | V     | $I_{OL} = +1.0 \text{ mA}$                                                             |

| $\Delta V_{OUT75}^{1}$        | TX Output differential peak-<br>to-peak voltage swing       | 1200 | _   | 2200 | mVp-p | $75\Omega$ to $V_{DD}$ – $2.0$ V (TX+ - TX-)                                           |

| $\Delta V_{\rm OUT50}^{-1}$   | TX Output differential peak-<br>to-peak voltage swing       | 1200 | _   | 2200 | mVp-p | $\begin{array}{c} 50\Omega \text{ to V}_{DD} - 2.0 \text{ V} \\ (TX+-TX-) \end{array}$ |

| $\Delta V_{\mathrm{IN}}^{-1}$ | Receiver differential peak-to-<br>peak Input Sensitivity RX | 400  | _   | 3200 | mVp-p | Internally biased to Vdd/2 (RX+ - RX-)                                                 |

| $V_{\mathrm{IH}}$             | Input HIGH voltage (TTL)                                    | 2.0  | _   | 5.5  | V     |                                                                                        |

| $V_{\rm IL}$                  | Input LOW voltage (TTL)                                     | 0    |     | 0.8  | V     | _                                                                                      |

| $I_{IH}$                      | Input HIGH current (TTL)                                    | _    | 50  | 500  | μΑ    | V <sub>IN</sub> =2.4V                                                                  |

| $I_{\mathrm{IL}}$             | Input LOW current (TTL)                                     | _    | _   | -500 | μΑ    | V <sub>IN</sub> =0.5V                                                                  |

| $V_{\mathrm{DD}}$             | Supply voltage                                              | 3.14 | _   | 3.47 | V     | 3.3V±5%                                                                                |

| $P_{\mathrm{D}}$              | Power dissipation                                           | _    | 625 | 900  | mW    | Outputs open,<br>$V_{DD} = V_{DD}$ max                                                 |

| I <sub>DD</sub>               | Supply Current                                              | _    | 190 | 260  | mA    | Outputs open,<br>$V_{DD} = V_{DD}$ max                                                 |

Note: (1) Refer to Application Note, AN-37, for differential measurement techniques.

## Absolute Maximum Ratings (1)

| Power Supply Voltage, (V <sub>DD</sub> ) | 0.5V to +4V                         |

|------------------------------------------|-------------------------------------|

| DC Input Voltage (PECL inputs)           | 0.5V to $V_{DD} + 0.5V$             |

| DC Input Voltage (TTL inputs)            | 0.5V to 5.5V                        |

| DC Output Voltage (TTL Outputs)          | 0.5V to $V_{DD} + 0.5V$             |

| Output Current (TTL Outputs)             | +/-50mA                             |

| Output Current (PECL Outputs)            | +/-50mA                             |

| Case Temperature Under Bias.             | 55° to $+125$ °C                    |

| Storage Temperature                      | $-65^{\circ}$ C to $+150^{\circ}$ C |

| Maximum Input ESD (Human Body Model)     |                                     |

## **Recommended Operating Conditions**

| Power Supply Voltage, (V <sub>DD</sub> ) | +3.3V±5% |

|------------------------------------------|----------|

| Operating Temperature Range              |          |

#### Notes

<sup>(1)</sup> CAUTION: Stresses listed under "Absolute Maximum Ratings" may be applied to devices one at a time without causing permanent damage. Functionality at or above the values listed is not implied. Exposure to these values for extended periods may affect device reliability.

1.25Gbits/sec Gigabit Ethernet Transceiver

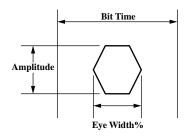

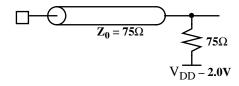

Figure 7: Parametric Measurement Information

#### Serial Input Rise and Fall Time

#### **TTL Input and Output Rise and Fall Time**

#### **Receiver Input Eye Diagram Jitter Tolerance Mask**

#### **Parametric Test Load Circuit**

#### **Serial Output Load**

#### TTL A.C. Output Load

## Data Sheet

## VSC7135

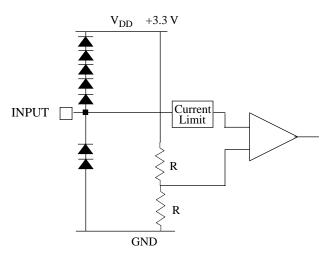

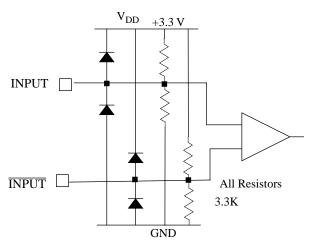

## Input Structures

Figure 8: Input Structures

**REFCLK and TTL Inputs**

Α

High Speed Differential Input (RX+/RX-)

В

1.25Gbits/sec Gigabit Ethernet Transceiver

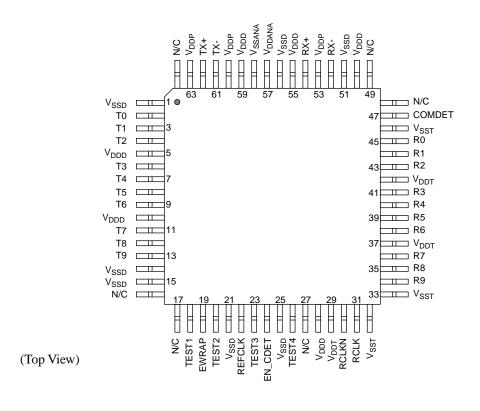

### Package Pin Descriptions

Figure 9: Pin Diagram

**Table 4: Pin Identification**

| Pin#                    | Name     | Description                                                                                                                                                             |

|-------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2-4, 6-9,<br>11-13      | Т0:9     | INPUTS - TTL 10-bit transmit character. Parallel data on this bus is clocked in on the rising edge of REFCLK. The data bit corresponding to T0 is transmitted first.    |

| 22                      | REFCLK   | INPUT - TTL This rising edge of this clock latches T0:9 into the input register. It also provides the reference clock, at one tenth the baud rate to the PLL.           |

| 62, 61                  | TX+, TX- | OUTPUTS - Differential PECL (AC Coupling recommended) These pins output the serialized transmit data when EWRAP is LOW. When EWRAP is HIGH, TX+ is HIGH and TX- is LOW. |

| 45-43, 41-<br>38, 36-34 | R0:9     | OUTPUTS - TTL 10-bit received character. Parallel data on this bus is clocked out on the rising edges of RCLK and RCLKN. R0 is the first bit received on RX+/RX         |

# Data Sheet VSC7135

| Pin#                            | Name                    | Description                                                                                                                                                                                                                           |

|---------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19                              | EWRAP                   | INPUT - TTL  LOW for Normal Operation. When HIGH, an internal loopback path from the transmitter to the receiver is enabled and the TX outputs are held HIGH.                                                                         |

| 54, 52                          | RX+, RX-                | INPUTS - Differential PECL (AC Coupling recommended) The serial receive data inputs selected when EWRAP is LOW. Internally biased tot VDD/2, with $3.3 \mathrm{K}\Omega$ resistors from each input pin to VDD and GND.                |

| 31, 30                          | RCLK,<br>RCLKN          | OUTPUT - Complementary TTL  Recovered clocks derived from one twentieth of the RX+/- data stream. Each rising transition of RCLK or RCLKN corresponds to a new word on R0:9.                                                          |

| 24                              | EN_CDET                 | INPUT - TTL Enables COMDET and word resynchronization when HIGH. When LOW, keeps current word alignment and disables COMDET.                                                                                                          |

| 47                              | COMDET                  | OUTPUT - TTL This output goes HIGH for half of an RCLK period to indicate that R0:9 contains a Comma Character ('0011111XXX'). COMDET will go HIGH only during a cycle when RCLKN is rising. COMDET is enabled by EN_CDET being HIGH. |

| 18,20,23                        | TEST1<br>TEST2<br>TEST3 | INPUT These signals are used for factory test. For normal operation, tie to VDD.                                                                                                                                                      |

| 26                              | TEST4                   | OUTPUT This signal is used for factory test. For normal operation, leave open.                                                                                                                                                        |

| 57                              | VDDANA                  | Analog Power Supply                                                                                                                                                                                                                   |

| 58                              | VSSANA                  | Analog Ground                                                                                                                                                                                                                         |

| 5, 10, 28,<br>50, 55, 59        | VDDD                    | Digital Logic Power Supply                                                                                                                                                                                                            |

| 1, 14, 15,<br>21, 25,<br>51, 56 | VSSD                    | Digital Logic Ground                                                                                                                                                                                                                  |

| 29, 37, 42                      | VDDT                    | TTL Output Power Supply                                                                                                                                                                                                               |

| 32, 33, 46                      | VSST                    | TTL Output Ground                                                                                                                                                                                                                     |

| 53, 60, 63                      | VDDP                    | PECL I/O Power Supply                                                                                                                                                                                                                 |

| 16,17,27,<br>48,49,64           | N/C                     | No Connection. These pins are not internally connected.                                                                                                                                                                               |

1.25Gbits/sec Gigabit Ethernet Transceiver

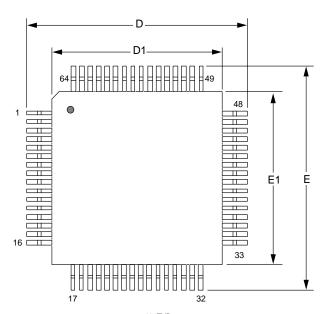

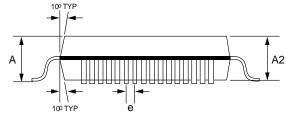

## Package Information

#### **64 PQFP Package Dimensions**

| Item | 10 mm   | 14 mm | Tolerance |

|------|---------|-------|-----------|

| A    | 2.45    | 2.35  | MAX       |

| A2   | 2.00    | 2.00  | +.10/05   |

| D    | 13.20   | 17.20 | ±.25      |

| D1   | 10.00   | 14.00 | ±.10      |

| Е    | 13.20   | 17.20 | ±.25      |

| E1   | 10.00   | 14.00 | ±.10      |

| b    | 0.22    | 0.35  | ±.05      |

| e    | 0.50    | 0.80  | BASIC     |

| L    | 0.88    | 0.88  | ±.15/10   |

| θ    | 0° - 7° |       |           |

#### NOTES:

All drawings not to scale All units in mm unless otherwise noted. 10 x 10 mm Package # 101-266-1 14 x 14 mm Package # 101-262-1

Data Sheet VSC7135

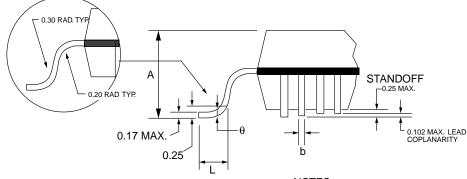

### Package Thermal Considerations

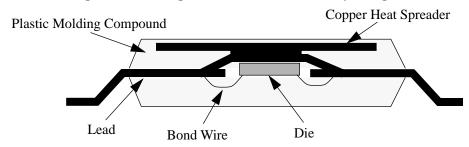

The VSC7135 is packaged in a 14 mm conventional PQFP with an internal heat spreader. This package use an industry-standard EIAJ footprint, but have been enhanced to improve thermal dissipation. The construction of the packages are as shown in Figure 12.

Figure 10: Package Cross Section - 14 mm package

**Table 5: Thermal Resistance**

| Symbol                   | Description                                                                                  | 10mm Value | 14mm Value | Units |

|--------------------------|----------------------------------------------------------------------------------------------|------------|------------|-------|

| $\theta_{ m jc}$         | Thermal resistance from junction to case                                                     | 10.0       | 9.5        | °C/W  |

| $\theta_{ca}$            | Thermal resistance from case to ambient in still air including conduction through the leads. | 50.8       | 29         | °C/W  |

| θ <sub>ca-100</sub>      | Thermal resistance from case to ambient with 100 LFM airflow                                 | 41.2       | 26.1       | °C/W  |

| $\theta_{\text{ca-200}}$ | Thermal resistance from case to ambient with 200 LFM airflow                                 | 36.9       | 23.8       | °C/W  |

| $\theta_{\text{ca-400}}$ | Thermal resistance from case to ambient with 400 LFM airflow                                 | 31.8       | 20.5       | °C/W  |

| $\theta_{\text{ca-}600}$ | Thermal resistance from case to ambient with 600 LFM airflow                                 | 27.8       | 17.9       | °C/W  |

The VSC7135 is designed to operate with a junction temperature up to  $105^{\circ}$ C. The user must guarantee that the temperature specification is not violated. With the Thermal Resistances shown above, the 10x10 PQFP can operate in still air ambient temperatures of  $55^{\circ}$ C [ $55^{\circ}$ C= $110^{\circ}$ C-0.9W\*( $10^{\circ}$ C/W+ $50.8^{\circ}$ C/W)] while the 14x14 PQFP can operate in still air ambient temperatures of  $75^{\circ}$ C [ $75^{\circ}$ C= $110^{\circ}$ C-0.9W\*( $9.5^{\circ}$ C/W+ $29^{\circ}$ C/W)]. If the ambient air temperature exceeds these limits then some form of cooling through a heatsink or an increase in airflow must be provided.

#### **Moisture Sensitivity Level**

This device is rated with a moisture sensitivity level 3 rating. Refer to Application Note AN-20 for appropriate handling procedures.

1.25Gbits/sec Gigabit Ethernet Transceiver

### **Ordering Information**

The part number for this product is formed by a combination of the device number and the package style:

|                                | <u>VSC7135xx</u> |

|--------------------------------|------------------|

| Device Type:                   |                  |

| VSC7135: 1.25 Gbps Transceiver |                  |

| Package Style (64-pin)         |                  |

| QN: 14x14mm PQFP               |                  |

| QU: 10x10mm PQFP               |                  |

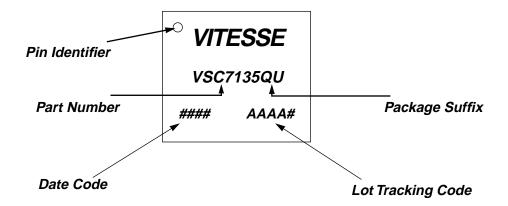

### **Marking Information**

The package is marked with three lines of text as shown below (QU Package):

#### **Notice**

Vitesse Semiconductor Corporation reserves the right to make changes in its products, specifications or other information at any time without prior notice. Therefore the reader is cautioned to confirmation that this datasheet is current prior to placing any orders. The company assumes no responsibility for any circuitry described other than circuitry entirely embodied in a Vitesse product.

#### Warning

5/28/98

Vitesse Semiconductor Corporation's product are not intended for use in life support appliances, devices or systems. Use of a Vitesse product in such applications without the written consent is prohibited.

| 1.25Gbits/sec                | Data Sheet |

|------------------------------|------------|

| Gigabit Ethernet Transceiver | VSC7135    |

|                              |            |

|                              |            |

|                              |            |

|                              |            |

|                              |            |

|                              |            |

|                              |            |

|                              |            |

|                              |            |

|                              |            |

|                              |            |

|                              |            |

|                              |            |

|                              |            |

|                              |            |

|                              |            |

|                              |            |

|                              |            |

|                              |            |

|                              |            |

|                              |            |

|                              |            |

|                              |            |

|                              |            |

|                              |            |

|                              |            |

|                              |            |

|                              |            |