# **Gigabit Ethernet Transceiver Chip**

# Preliminary Technical Data

# HDMP-1636 Transceiver HDMP-1646 Transceiver

#### **Features**

- IEEE 802.3z Gbit Ethernet Compatible, Supports 1250 MBd Gigabit Ethernet

- Based on X3T11 "10 Bit Specification"

- Low Power Consumption

- Transmitter and Receiver Functions Incorporated onto a Single IC

- Two Package Sizes Available:

- 10 mm PQFP (HDMP-1636)

- 14 mm PQFP (HDMP-1646)

- 10-Bit Wide Parallel TTL Compatible I/Os

- Single +3.3 V Power Supply

- 5-Volt Tolerant I/Os

- 2 KV ESD Protection

## **Applications**

- 1250 MBd Gigabit Ethernet Interface

- High Speed Proprietary Interface

- Backplane Serialization

- Bus Extender

## **Description**

The HDMP-1636/46 transceiver is a single silicon bipolar integrated circuit packaged in a plastic QFP package. It provides a low-cost, low-power physical layer solution for 1250 MBd Gigabit Ethernet or proprietary link interfaces. It

provides complete Serialize/ Deserialize for copper transmission, incorporating both the Gigabit Ethernet transmit and receive functions into a single device.

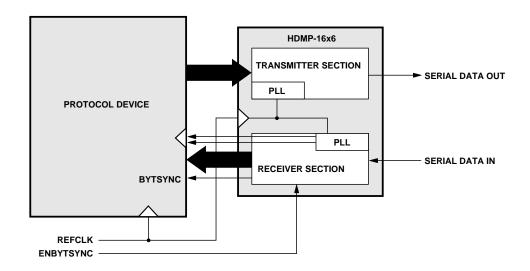

This chip is used to build a high speed interface (as shown in Figure 1) while minimizing board space, power and cost. It is compatible with the IEEE 802.3z specification.

The transmitter section accepts 10-bit wide parallel TTL data and multiplexes this data into a high speed serial data stream. The parallel data is expected to be 8B/10B encoded data, or equivalent. This parallel data is latched into the input register of the transmitter section on the rising edge of the 125 MHz reference clock (used as the transmit byte clock).

The transmitter section's PLL locks to this user supplied 125 MHz byte clock. This clock is then multiplied by 10, to generate the 1250 MHz serial signal clock used to generate the high speed output. The high speed outputs are capable of interfacing directly to copper cables for electrical transmission or to a separate fiber optic module for optical transmission.

The receiver section accepts a serial electrical data stream at 1250 MBd and recovers the original 10-bit wide parallel data. The receiver PLL locks onto the incoming serial signal and recovers the high speed serial clock and data. The serial data is converted back into 10-bit parallel data, recognizing the 8B/10B comma character to establish byte alignment.

The recovered parallel data is presented to the user at TTL compatible outputs. The receiver section also recovers two 62.5 MHz receiver byte clocks which are 180 degrees out of phase with each other. The parallel data is properly aligned with the rising edge of alternating clocks.

For test purposes, the transceiver provides for on-chip local loopback functionality, controlled through an external input pin. Additionally, the byte

(5/97) 711

Figure 1. Typical Application Using the HDMP-16x6.

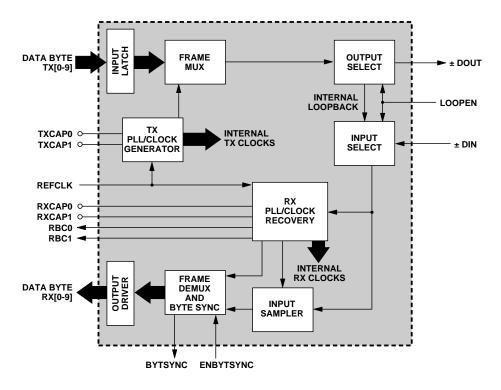

Figure 2. HDMP-16x6 Transceiver Block Diagram.

synchronization feature may be disabled. This may be useful in proprietary applications which use alternative methods to align the parallel data.

## HDMP-1636/46 Block Diagram

The HDMP-1636/46 was designed to transmit and receive 10-bit wide parallel data over a single high-speed line. The parallel data applied to the transmitter is expected to be encoded per the Gigabit Ethernet specification, which uses an 8B/10B encoding scheme with special reserve characters for link management purposes. In order to accomplish this task, the HDMP-1636/46 incorporates the following:

- TTL Parallel I/O's

- High Speed Phase Lock Loops

- Clock Generation/Recovery Circuitry

- Parallel to Serial Converter

- High Speed Serial Clock and Data Recovery Circuitry

- Comma Character Recognition Circuitry

- Byte Alignment Circuitry

- Serial to Parallel Converter

#### **INPUT LATCH**

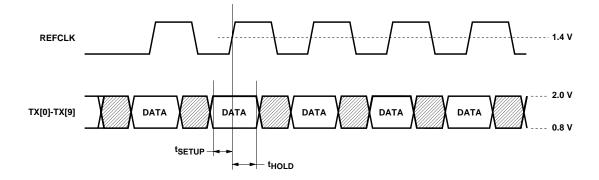

The transmitter accepts 10-bit wide TTL parallel data at inputs TX[0..9]. The user-provided reference clock signal, REFCLK, is also used as the transmit byte clock. The TX[0..9] and REFCLK signals must be properly aligned, as shown in Figure 3.

#### TX PLL/CLOCK GENERATOR

The transmitter Phase Lock Loop and Clock Generator (TX PLL/ CLOCK GENERATOR) block is responsible for generating all internal clocks needed by the transmitter section to perform its functions. These clocks are based on the supplied reference byte clock (REFCLK). REFCLK is used as both the frequency reference clock for the PLL and the transmit byte clock for the incoming data latches. It is expected to be 125 MHz and properly aligned to the incoming parallel data (see Figure 3). This clock is then multiplied by 10 to generate the 1250 MHz clock necessary for the high speed serial outputs.

#### FRAME MUX

The FRAME MUX accepts the 10-bit wide parallel data from the INPUT LATCH. Using internally generated high speed clocks, this parallel data is multiplexed into the 1250 MBd serial data stream. The data bits are transmitted sequentially, from the least significant bit (TX[0]) to the most significant bit (TX[9]).

### **OUTPUT SELECT**

The OUTPUT SELECT block provides for an optional internal loopback of the high speed serial signal, for testing purposes.

In normal operation, LOOPEN is set low and the serial data stream is placed at +/- DOUT. When wrap-mode is activated by setting

LOOPEN high, the +/- DOUT pins are held static at logic 1 and the serial output signal is internally wrapped to the INPUT SELECT box of the receiver section.

#### INPUT SELECT

The INPUT SELECT block determines whether the signal at +/- DIN or the internal loop-back serial signal is used. In normal operation, LOOPEN is set low and the serial data is accepted at +/- DIN. When LOOPEN is set high, the high speed serial signal is internally looped-back from the transmitter section to the receiver section. This feature allows for loop back testing exclusive of the transmission medium.

### RX PLL/CLOCK RECOVERY

The RX PLL/CLOCK RECOVERY block is responsible for frequency and phase locking onto the incoming serial data stream and recovering the bit and byte clocks. An automatic locking feature allows the Rx PLL to lock onto the input data stream without external controls. It does this by continually frequency locking onto the 125 MHz clock, and then phase locking onto the input data stream. An internal signal detection circuit monitors the presence of the input, and invokes the phase detection as the data stream appears. Once bit locked, the receiver generates the high speed sampling clock at 1250 MHz for the input sampler, and recovers the two 62.5 Mhz

receiver byte clocks (RBC1/RBC0). These clocks are 180 degrees out of phase with each other, and are alternately used to clock the 10-bit parallel output data.

#### INPUT SAMPLER

The INPUT SAMPLER is responsible for converting the serial input signal into a re-timed serial bit stream. In order to accomplish this, it uses the high speed serial clock recovered from the RX PLL/CLOCK RECOVERY block. This serial bit stream is sent to the FRAME DEMUX and BYTE SYNC block.

# FRAME DEMUX AND BYTE SYNC

The FRAME DEMUX AND BYTE SYNC block is responsible for restoring the 10-bit parallel data from the high speed serial bit stream. This block is also responsible for recognizing the comma character (or a K28.5 character) of positive disparity (00111111xxx). When recognized, the FRAME DEMUX AND BYTE SYNC block works with the RX PLL/CLOCK RECOVERY block to properly align the receive byte clocks to the parallel data. When a comma character is detected and realignment of the receiver byte clocks (RBC1/RBC0) is necessary, these clocks are stretched, not slivered, to the

next possible correct alignment position. These clocks will be fully aligned by the start of the second 2-byte ordered set. The second comma character received shall be aligned with the rising edge of RBC1. Comma characters should not be transmitted in consecutive bytes to allow the receiver byte clocks to maintain their proper recovered frequencies.

#### **OUTPUT DRIVERS**

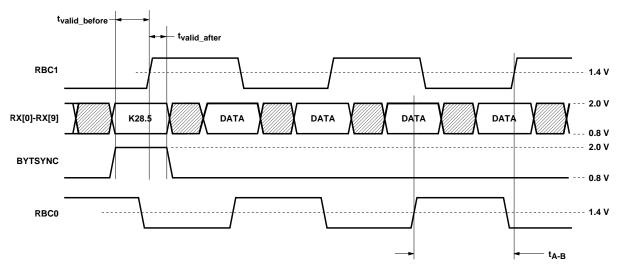

The OUTPUT DRIVERS present the 10-bit parallel recovered data byte properly aligned to the receive byte clocks (RBC1/RBC0), as shown in Figure 5. These output data buffers provide TTL compatible signals.

## HDMP-1636/46 (Transmitter Section)

### **Timing Characteristics**

$T_A = 0$ °C to +60°C,  $V_{CC} = 3.15$  V to 3.45 V

| Symbol                 | Parameter           | Units | Min. | Typ. | Max. |

|------------------------|---------------------|-------|------|------|------|

| $t_{ m setup}$         | Setup Time          | nsec  | 2    |      |      |

| $t_{ m hold}$          | Hold Time           | nsec  | 1    |      |      |

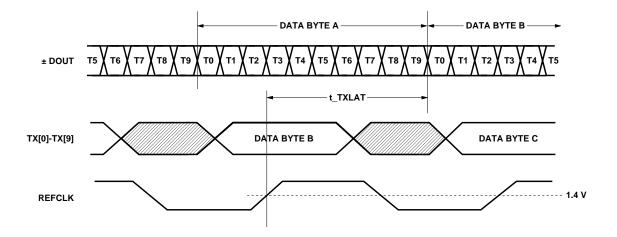

| t_txlat <sup>[1]</sup> | Transmitter Latency | nsec  |      | TBD  |      |

|                        |                     | bits  |      | TBD  |      |

#### Note:

<sup>1.</sup> The transmitter latency, as shown in Figure 4, is defined as the time between the latching in of the parallel data word (as triggered by the rising edge of the transmit byte clock, REFCLK) and the transmission of the first serial bit of that parallel word (defined by the rising edge of the first bit transmitted).

Figure 3. Transmitter Section Timing.

Figure 4. Transmitter Latency.

# HDMP-1636/46 (Receiver Section)

## **Timing Characteristics**

$T_A$  = 0°C to +70°C,  $V_{CC}$  = 3.15 V to 3.45 V

| Symbol                    | Parameter                                 | Units | Min. | Typ. | Max. |

|---------------------------|-------------------------------------------|-------|------|------|------|

| b_sync <sup>[1,2]</sup>   | Bit Sync Time                             | bits  |      |      | 2500 |

| t <sub>valid_before</sub> | Time Data Valid Before Rising Edge of RBC | nsec  | 2.5  | TBD  |      |

| $t_{ m valid\_after}$     | Time Data Valid After Rising Edge of RBC  | nsec  | 1.5  | TBD  |      |

| $t_{ m duty}$             | RBC Duty Cycle                            | %     | 40   |      | 60   |

| t <sub>A-B</sub>          | Rising Edge Time Difference               | nsec  | 7.5  | 7.9  | 8.5  |

| t_rxlat <sup>[3]</sup>    | Receiver Latency                          | nsec  |      | 22.4 |      |

|                           |                                           | bits  |      | 28   |      |

#### Notes:

- 1. This is the recovery time for input phase jumps, per the Fibre Channel Specification X3.230-1994 FC-PH Standard, Sec 5.3.

- 2. Tested using  $C_{PLL} = 0.1 \mu F$ .

- 3. The receiver latency, as shown in Figure 6, is defined as the time between receiving the first serial bit of a parallel data word (defined as the first edge of the first serial) and the clocking out of that parallel word (defined by the rising edge of the receive byte clock, either RBC1 or RBC0).

Figure 5. Receiver Section Timing.

## **HDMP-1636/46 (TRx)**

## **Absolute Maximum Ratings**

$T_A = 25$ °C, except as specified. Operation in excess of any one of these conditions may result in permanent damage to this device.

| Symbol                | Parameter                      | Units                | Min. | Max.               |

|-----------------------|--------------------------------|----------------------|------|--------------------|

| V <sub>CC</sub>       | Supply Voltage                 | V                    | -0.5 | 5.0                |

| $V_{\rm IN,TTL}$      | TTL Input Voltage              | V                    | -0.7 | $V_{\rm CC} + 0.7$ |

| V <sub>IN,HS_IN</sub> | HS_IN Input Voltage            | V                    | 2.0  | $V_{\rm CC}$       |

| I <sub>O,TTL</sub>    | TTL Output Source Current      | mA                   |      | 13                 |

| T <sub>stg</sub>      | Storage Temperature            | $^{\circ}\mathrm{C}$ | -40  | +130               |

| Tj                    | Junction Operating Temperature | °C                   | 0    | +130               |

## HDMP-1636/46 (TRx)

## **Guaranteed Operating Rates**

$T_A = 0$ °C to +70°C,  $V_{CC} = 3.15$  V to 3.45 V

| Parallel Clo | Parallel Clock Rate (MHz) |      | Rate (MBaud) |

|--------------|---------------------------|------|--------------|

| Min.         | Max.                      | Min. | Max.         |

| 124.0        | 126.0                     | 1240 | 1260         |

## **HDMP-1636/46 (TRx)**

# **Transceiver Reference Clock Requirements**

$T_A = 0$ °C to +70°C,  $V_{CC} = 3.15$  V to 3.45 V

| Symbol    | Parameter                                           | Unit | Min. | Тур. | Max. |

|-----------|-----------------------------------------------------|------|------|------|------|

| f         | Nominal Frequency (for Gigabit Ethernet Compliance) | MHz  |      | 125  |      |

| $F_{tol}$ | Frequency Tolerance                                 | ppm  | -100 |      | +100 |

| Symm      | Symmetry (Duty Cycle)                               | %    | 40   |      | 60   |

## HDMP-1636/46 (TRx) DC Electrical Specifications

$T_A$ = 0°C to +70°C,  $V_{CC}$  = 3.15 V to 3.45 V

| Symbol                    | Parameter                                                | Unit | Min. | Typ.  | Max.            |

|---------------------------|----------------------------------------------------------|------|------|-------|-----------------|

| $V_{\mathrm{IH,TTL}}$     | TTL Input High Voltage Level, Guaranteed High Signal     | V    | 2    |       | $V_{\rm CC}$    |

|                           | for All Inputs                                           |      |      |       |                 |

| $V_{\rm IL,TTL}$          | TTL Input Low Voltage Level, Guaranteed Low Signal for   | V    | 0    |       | 0.8             |

|                           | All Inputs                                               |      |      |       |                 |

| V <sub>OH,TTL</sub>       | TTL Output High Voltage Level, $I_{OH} = -400 \mu A$     | V    | 2.2  |       | V <sub>CC</sub> |

| $V_{\mathrm{OL,TTL}}$     | TTL Output Low Voltage Level, $I_{OL} = 1 \text{ mA}$    | V    | 0    |       | 0.6             |

| $I_{\mathrm{IH,TTL}}$     | Input High Current (Magnitude), $V_{IN} = V_{CC}$        | μΑ   |      | 0.003 | 40              |

| I <sub>IL-TTL</sub>       | Input Low Current (Magnitude), V <sub>IN</sub> = 0 Volts | μΑ   |      | -366  | -600            |

| I <sub>CC,TRx</sub> [1,2] | Transceiver $V_{CC}$ Supply Current, $T_A = 25$ °C       | mA   |      | 205   |                 |

#### Notes:

- 1. Measurement Conditions: Tested sending 1250 MBd PRBS  $2^7$ -1 sequence from a serial BERT with both DOUT outputs biased with 150  $\Omega$  resistors.

- 2. Typical specified with  $V_{CC}$  = 3.3 volts, maximum specified with  $V_{CC}$  = 3.45 volts.

# **HDMP-1636/46 (TRx)**

# **AC Electrical Specifications**

$T_A = 0$ °C to +70°C,  $V_{CC} = 3.15$  V to 3.45 V

| Symbol                     | Parameter                                          | Units | Min. | Тур. | Max. |

|----------------------------|----------------------------------------------------|-------|------|------|------|

| $t_{r,TTLin}$              | Input TTL Rise Time, 0.8 to 2.0 Volts              | nsec  |      | 2    |      |

| $t_{f,TTLin}$              | Input TTL Fall Time, 2.0 to 0.8 Volts              | nsec  |      | 2    |      |

| $t_{r,TTLout}$             | Output TTL Rise Time, 0.8 to 2.0 Volts, 10 pF Load | nsec  |      | 1.5  | 2.4  |

| t <sub>f,TTLout</sub>      | Output TTL Fall Time, 2.0 to 0.8 Volts, 10 pF Load | nsec  |      | 1.1  | 2.4  |

| ${ m t_{rs,HS\_OUT}}$      | HS_OUT Single-Ended (+DOUT) Rise Time              | psec  | 85   | TBD  | 327  |

| t <sub>fs,HS_OUT</sub>     | HS_OUT Single-Ended (+DOUT) Fall Time              | psec  | 85   | TBD  | 327  |

| $t_{\rm rd,HS\_OUT}$       | HS_OUT Differential Rise Time                      | psec  | 85   |      | 327  |

| t <sub>fd,HS_OUT</sub>     | HS_OUT Differential Fall Time                      | psec  | 85   |      | 327  |

| V <sub>IP,HS_IN</sub>      | HS_IN Input Peak-to-Peak Differential Voltage      | mV    | 200  | 1200 | 2000 |

| V <sub>OP,HS_OUT</sub> [1] | HS_OUT Output Peak-to-Peak Differential Voltage    | mV    | 1200 | 1580 | 2200 |

#### Note:

<sup>1.</sup> Output Peak-to-Peak Differential Voltage specified as DOUT+ minus DOUT-.

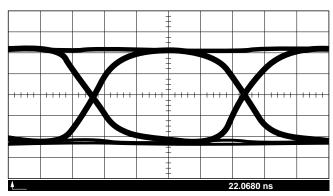

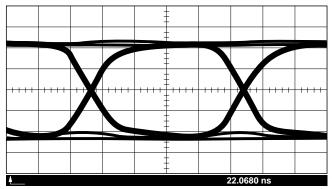

Yaxis = 400 mV/DIV

### a. Differential HS\_OUT Output (Dout+ Minus Dout-).

Yaxis = 200 mV/DIV

b. Single-Ended  $HS_OUT$  Output (Dout+).

Eye Diagrams of the High-Speed Serial Outputs from the HDMP-1636/46 as Captured on the HP 83480A Digital Communications Analyzer. Tested with PRBS =  $2^7$ -1.

Figure 7. Transmitter DOUT Eye Diagrams.

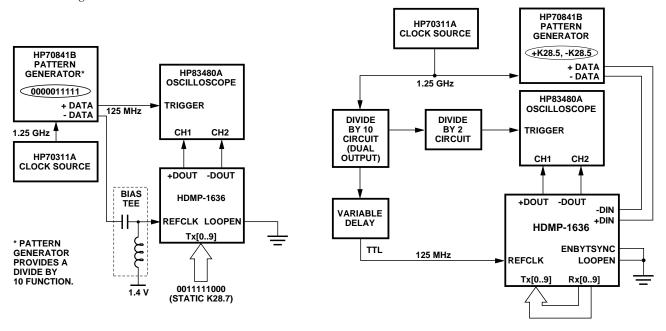

## HDMP-1636/46 (Transmitter Section) Output Jitter Characteristics

$T_A = 0$ °C to +70°C,  $V_{CC} = 3.15$  V to 3.45 V

| Symbol | Parameter                                                                 | Units | Typ. |

|--------|---------------------------------------------------------------------------|-------|------|

| RJ[1]  | Random Jitter at DOUT, the High Speed Electrical Data Port, specified as  | ps    | 8    |

|        | 1 sigma deviation of the 50% crossing point (RMS)                         |       |      |

| DJ[1]  | Deterministic Jitter at DOUT, the High Speed Electrical Data Port (pk-pk) | ps    | 15   |

#### Note:

1. Defined by Fibre Channel Specification X3.230-1994 FC-PH Standard, Annex A, Section A.4 and tested using measurement method shown in Figure 8.

a. Block Diagram of RJ Measurement Method.

b. Block Diagram of DJ Measurement Method.

Figure 8. Transmitter Jitter Measurement Method.

# HDMP-1636/46 (TRx)

## **Thermal and Power Temperature Characteristics**

$T_A = 0$ °C to +70°C,  $V_{CC} = 3.15$  V to 3.45 V

| Symbol                       | Parameter                                            |           | Units   | Тур. | Max. |

|------------------------------|------------------------------------------------------|-----------|---------|------|------|

| P <sub>D,TRx</sub> [1,2]     | Transceiver Power Dissipation, Outputs               | mW        | 630     | 850  |      |

|                              | has 5 Ones and 5 Zeroes                              |           |         |      |      |

| P <sub>D,TRx</sub> [1,2,3]   | Transceiver Power Dissipation, Outputs Connected per |           | mW      | 685  | 900  |

|                              | Recommended Bias Terminations with                   |           |         |      |      |

| $\Theta_{\mathrm{jc}}^{[4]}$ | Thermal Resistance, Junction to Case                 | HDMP-1636 | °C/Watt | 10   |      |

|                              |                                                      | HDMP-1646 |         | 7    |      |

#### Notes:

- P<sub>D</sub> is obtained by multiplying the max V<sub>CC</sub> by the max I<sub>CC</sub> and subtracting the power dissipated outside the chip at the high speed bias resistors.

- 2. Typical value specified with  $V_{CC} = 3.3$  volts, maximum value specified with  $V_{CC} = 3.45$  volts.

- 3. Specified with high speed outputs biased with 150  $\Omega$  resistors and receiver TTL outputs driving 10 pF loads.

- 4. Based on independent package testing by HP.  $\Theta_{ja}$  for these devices is 48°C/Watt for the HDMP-1636 and 44°C/Watt for the HDMP-1646.  $\Theta_{ja}$  is measured on a standard 3x3" FR4 PCB in a still air environment. To determine the actual junction temperature in a given application, use the value as described as follows:  $T_j = T_C + (\Theta_{jc} \times Pd)$ , where  $T_C$  is the case temperature measured on the top center of the package and  $P_D$  is the power being dissipated.

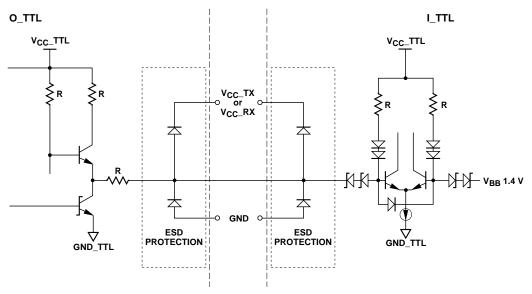

# I/O Type Definitions

| I/O Type | Definition                            |  |

|----------|---------------------------------------|--|

| I-TTL    | Input TTL, Floats High When Left Open |  |

| O-TTL    | Output TTL                            |  |

| HS_OUT   | High Speed Output, ECL Compatible     |  |

| HS_IN    | High Speed Input                      |  |

| С        | External Circuit Node                 |  |

| S        | Power Supply or Ground                |  |

## HDMP-1636/46 (TRx) Pin Input Capacitance

| Symbol      | Parameter                           | Units | Typ. | Max. |

|-------------|-------------------------------------|-------|------|------|

| $C_{INPUT}$ | Input Capacitance on TTL Input Pins | pF    | 1.6  |      |

Figure 9. O-TTL and I-TTL Simplified Circuit Schematic.

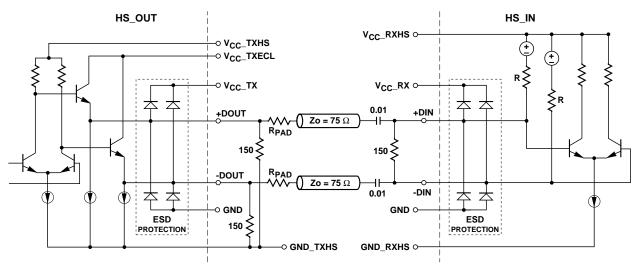

Figure 10.  $HS_OUT$  and  $HS_IN$  Simplified Circuit Schematic.

#### Notes

- 1. HS\_IN inputs should never be connected to ground as permanent damage to the device may result.

- 2. The optional series padding resistors (Rpad) help dampen load reflections. Typical Rpad values for mismatched loads range between 25-75  $\Omega$ .

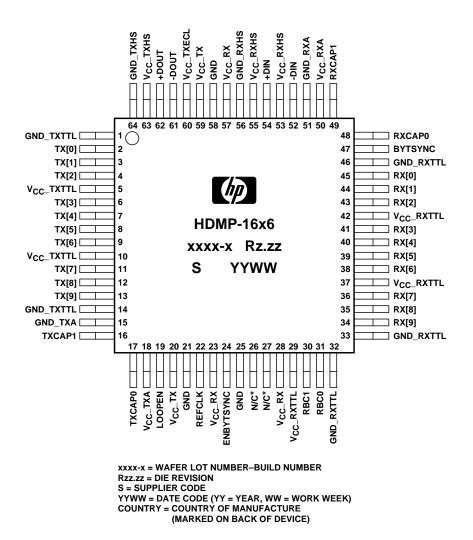

Figure 11. HDMP-1636/46 (TRx) Package Layout and Marking, Top View.

\*Note: Pins 26 and 27 are designated as "no connect" pins and must be left unconnected.

# TRx I/O Definition

| Name           | Pin            | Туре   | Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|----------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BYTSYNC        | 47             | O-TTL  | <b>Byte Sync Output:</b> An active high output. Used to indicate detection of a comma character (0011111XXX). It is only active when ENBYTSYNC is enabled.                                                                                                                                                                                                                                                                                            |

| -DIN           | 52             | HS_IN  | <b>Serial Data Inputs:</b> High-speed inputs. Serial data is accepted from the                                                                                                                                                                                                                                                                                                                                                                        |

| +DIN           | 54             |        | ± DIN inputs when LOOPEN is low.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| -DOUT<br>+DOUT | 61<br>62       | HS_OUT | <b>Serial Data Outputs:</b> High-speed outputs. These lines are active when LOOPEN is set low. When LOOPEN is set high, these outputs are held static at logic 1.                                                                                                                                                                                                                                                                                     |

| ENBYTSYNC      | 24             | I-TTL  | Enable Byte Sync Input: When high, turns on the internal byte sync function to allow clock synchronization to a comma character, (0011111XXX). When the line is low, the function is disabled and will not reset registers and clocks, or strobe the BYTSYNC line.                                                                                                                                                                                    |

| GND            | 21<br>25<br>58 | S      | <b>Logic Ground:</b> Normally 0 volts. This ground is used for internal PECL logic. It should be isolated from the noisy TTL ground as well as possible.                                                                                                                                                                                                                                                                                              |

| GND_RXA        | 51             | S      | <b>Analog Ground:</b> Normally 0 volts. Used to provide a clean ground plane for the receiver PLL and high-speed analog cells.                                                                                                                                                                                                                                                                                                                        |

| GND_RXHS       | 56             | S      | Ground: Normally 0 volts.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| GND_RXTTL      | 32<br>33<br>46 | S      | <b>TTL Receiver Ground:</b> Normally 0 volts. Used for the TTL output cells of the receiver section.                                                                                                                                                                                                                                                                                                                                                  |

| GND_TXA        | 15             | S      | <b>Analog Ground:</b> Normally 0 volts. Used to provide a clean ground plane for the PLL and high-speed analog cells.                                                                                                                                                                                                                                                                                                                                 |

| GND_TXHS       | 64             | S      | Ground: Normally 0 volts.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| GND_TXTTL      | 1              | S      | TTL Transmitter Ground: Normally 0 volts. Used for the TTL input                                                                                                                                                                                                                                                                                                                                                                                      |

|                | 14             |        | cells of the transmitter section.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| LOOPEN         | 19             | I-TTL  | <b>Loopback Enable Input:</b> When set high, the high-speed serial signal is internally wrapped from the transmitter's serial loopback outputs back to the receiver's loopback inputs. Also, when in loopback mode, the $\pm$ DOUT outputs are held static at logic 1. When set low, $\pm$ DOUT outputs and $\pm$ DIN inputs are active.                                                                                                              |

| RBC1<br>RBC0   | 30 31          | O-TTL  | Receiver Byte Clocks: The receiver section recovers two 62.5 MHz receive byte clocks. These two clocks are 180 degrees out of phase. The receiver parallel data outputs are alternately clocked on the rising edge of these clocks. The rising edge of RBC1 aligns with the output of the comma character (for byte alignment) when detected.                                                                                                         |

| REFCLK         | 22             | I-TTL  | Reference Clock and Transmit Byte Clock: A 125 MHz clock supplied by the host system. The transmitter section accepts this signal as the frequency reference clock. It is multiplied by 10 to generate the serial bit clock and other internal clocks. The transmit side also uses this clock as the transmit byte clock for the incoming parallel data TX[0]TX[9]. It also serves as the reference clock for the receive portion of the transceiver. |

| N/C            | 26,27          |        | These pins are factory test pins and must be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                        |

TRx I/O Definition (cont'd.)

| Name                                    | Pin | Туре  | Signal                                                                             |

|-----------------------------------------|-----|-------|------------------------------------------------------------------------------------|

| RX[0]                                   | 45  | O-TTL | <b>Data Outputs:</b> One 10 bit data byte. RX[0] is the first bit received.        |

| RX[1]                                   | 44  |       | RX[0] is the least significant bit.                                                |

| RX[2]                                   | 43  |       |                                                                                    |

| RX[3]                                   | 41  |       |                                                                                    |

| RX[4]                                   | 40  |       |                                                                                    |

| RX[5]                                   | 39  |       |                                                                                    |

| RX[6]                                   | 38  |       |                                                                                    |

| RX[7]                                   | 36  |       |                                                                                    |

| RX[8]                                   | 35  |       |                                                                                    |

| RX[9]                                   | 34  |       |                                                                                    |

|                                         |     | C     | I Dilla Carra A la Cila DI I                                                       |

| RXCAP0                                  | 48  | C     | Loop Filter Capacitor: A loop filter capacitor for the internal PLL must           |

| RXCAP1                                  | 49  |       | be connected across the RXCAP0 and RXCAP1 pins. (typical value = $0.1 \mu F$ ).    |

| TX[0]                                   | 2   | I-TTL | <b>Data Inputs:</b> One 10 bit, 8B/10B-encoded data byte. TX[0] is the first       |

| TX[1]                                   | 3   |       | bit transmitted. TX[0] is the least significant bit.                               |

| TX[2]                                   | 4   |       |                                                                                    |

| TX[3]                                   | 6   |       |                                                                                    |

| TX[4]                                   | 7   |       |                                                                                    |

| TX[5]                                   | 8   |       |                                                                                    |

| TX[6]                                   | 9   |       |                                                                                    |

| TX[7]                                   | 11  |       |                                                                                    |

| TX[8]                                   | 12  |       |                                                                                    |

| TX[9]                                   | 13  |       |                                                                                    |

|                                         |     | C     | Loop Filter Capacitor: A loop filter capacitor must be connected across            |

| TXCAP1                                  | 16  |       |                                                                                    |

| TXCAP0                                  | 17  |       | the TXCAP1 and TXCAP0 pins (typical value = $0.1 \mu F$ ).                         |

| V <sub>CC</sub> _RX                     | 23  | S     | <b>Logic Power Supply:</b> Normally 3.3 volts. Used for internal receiver          |

|                                         | 28  |       | PECL logic. It should be isolated from the noisy TTL supply as well as             |

|                                         | 57  |       | possible.                                                                          |

| V <sub>CC</sub> _RXA                    | 50  | S     | Analog Power Supply: Normally 3.3 volts. Used to provide a clean                   |

| .00                                     |     |       | supply line for the PLL and high-speed analog cells.                               |

| Vac DVUC                                | 53  | S     | High-Speed Supply: Normally 3.3 volts. Used only for the high-speed                |

| V <sub>CC</sub> _RXHS                   |     | 8     |                                                                                    |

|                                         | 55  |       | receiver cell (HS_IN). Noise on this line should be minimized for best             |

|                                         |     |       | operation.                                                                         |

| $V_{CC}$ RXTTL                          | 29  | S     | TTL Power Supply: Normally 3.3 volts. Used for all TTL receiver output             |

|                                         | 37  |       | buffer cells.                                                                      |

|                                         | 42  |       |                                                                                    |

| V <sub>CC</sub> _TX                     | 20  | S     | <b>Logic Power Supply:</b> Normally 3.3 volts. Used for internal transmitter PECL  |

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 59  |       | logic. It should be isolated from the noisy TTL supply as well as possible.        |

| V TV                                    |     | C     |                                                                                    |

| V <sub>CC</sub> _TXA                    | 18  | S     | Analog Power Supply: Normally 3.3 volts. Used to provide a clean                   |

|                                         |     |       | supply line for the PLL and high-speed analog cells.                               |

| V <sub>CC</sub> _TXECL                  | 60  | S     | <b>High-Speed ECL Supply:</b> Normally 3.3 volts. Used only for the last stage     |

|                                         |     |       | of the high-speed transmitter output cell (HS_OUT) as shown in                     |

|                                         |     |       | Figure 10. Due to high current transitions, this V <sub>CC</sub> should be well    |

|                                         |     |       | bypassed to a ground plane.                                                        |

| V <sub>CC</sub> _TXHS                   | 63  | S     | <b>High-Speed Supply:</b> Normally 3.3 volts. Used by the transmitter side for the |

| 100_12110                               |     |       | high-speed circuitry. Noise on this line should be minimized for best operation.   |

| \$7                                     | -   | -     | -                                                                                  |

| V <sub>CC</sub> _TXTTL                  | 5   | S     | TTL Power Supply: Normally 3.3 volts. Used for all TTL                             |

| I                                       | 10  |       | transmitter input buffer cells.                                                    |

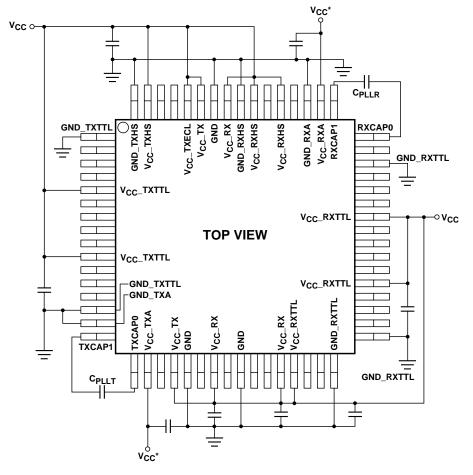

$^*$  SUPPLY VOLTAGE INTO VCC\_RXA AND VCC\_TXA SHOULD BE FROM A LOW NOISE SOURCE. ALL BYPASS CAPACITORS AND PLL FILTER CAPACITORS ARE 0.1  $\mu F.$

Figure 12. Power Supply Bypass.

### **Start-up Procedure:**

The transceiver start-up procedure(s) use the following conditions:  $V_{CC} = +3.3 \text{ V} \pm 5\%$  and REFCLK = 125 MHz  $\pm$  100 ppm.

After the above conditions have been met, apply valid data using a balanced code such as 8B/10B. Frequency lock occurs within 500 µs. After frequency lock, phase lock occurs within 2500 bit times.

## Transceiver Power Supply Bypass and Loop Filter Capacitors

Bypass capacitors should be liberally used and placed as close as possible to the appropriate power supply pins of the HDMP-1636/46 as shown on the schematic of Figure 12. All bypass chip capacitors are  $0.1 \mu F$ . The  $V_{CC}$ RXA and V<sub>CC</sub>\_TXA pins are the analog power supply pins for the PLL sections. The voltage into these pins should be clean with minimum noise. The PLL loop filter capacitors and their pin locations are also shown on Figure 12. Notice that only two capacitors are required: C<sub>PLLT</sub> for the transmitter and CPLLR for the receiver. Nominal capacitance is  $0.1~\mu F$ . The voltage across the capacitors is on the order of 1 volt, so the capacitor can be a low voltage type and physically small. The PLL capacitors are placed physically close to the appropriate pins on the HDMP-1636/46. Keeping the lines short will prevent them from picking up stray noise from surrounding lines or components.

# PRE-RELEASE PRODUCT DISCLAIMER:

This product is in development at the Hewlett-Packard CSSD in San Jose, California. Until Hewlett-Packard releases this product for general sales, HP reserves the right to alter specifications, features, capabilities, functions, manufacturing release dates, and even general availability of the product at any time.

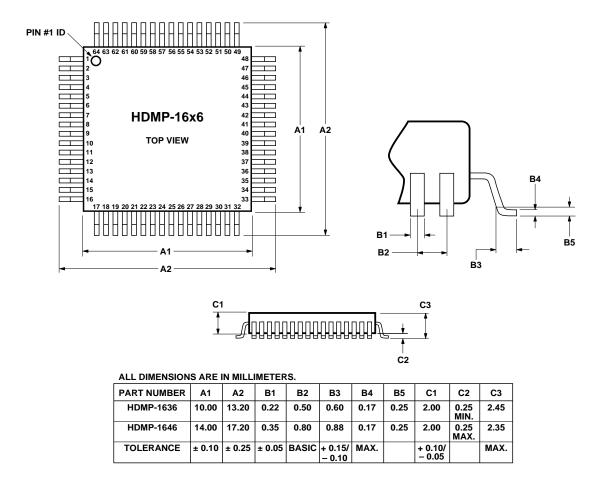

# **Package Information**

| Item                  | Details               |

|-----------------------|-----------------------|

| Package Material      | Plastic               |

| Lead Finish Material  | 85% Tin, 15% Lead     |

| Lead Finish Thickness | 300-800 μm            |

| Lead Coplanarity      | HDMP-1636 0.08 mm max |

|                       | HDMP-1646 0.10 mm max |

# **Mechanical Dimensions**

Figure 13. Mechanical Dimensions of HDMP-1636/46.