# Agilent HDMP-0450 Quad Port Bypass Circuit for Fibre Channel Arbitrated Loops Data Sheet

### Description

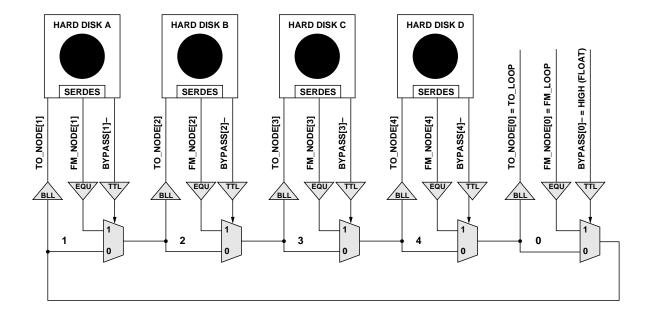

The HDMP-0450 is a Quad Port Bypass Circuit (PBC) which provides a low-cost, low-power physical-layer solution for Fibre Channel Arbitrated Loop (FC-AL) disk array configurations. By using a PBC such as the HDMP-0450, hard disks may be pulled out or swapped while other disks in the array are available to the system.

A PBC consists of multiple 2:1 multiplexers daisy chained together. Each port has two modes of operation: "disk in loop" and "disk bypassed." When the "disk in loop" mode is selected, the loop goes into and out of the disk drive at that port. For example, data goes from the HDMP-0450's TO\_NODE[n]± differential output pins to the Disk Drive Transceiver IC's (e.g., an HDMP-1636A) Rx differential input pins. Data from the Disk Drive Transceiver IC's Tx differential outputs goes to the HDMP-0450's FM NODE[n] $\pm$  differential input

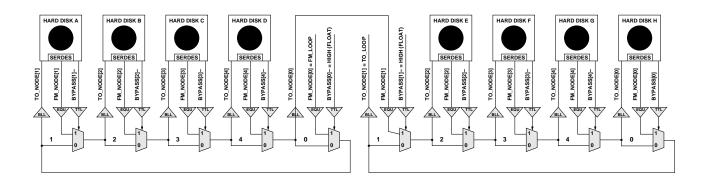

pins. Figure 2 shows connection diagrams for disk drive array applications. When the "disk bypassed" mode is selected, the disk drive is either absent or nonfunctional and the loop bypasses the hard disk.

The "disk bypassed" mode is enabled by pulling the BYPASS[n]pin low. Leave BYPASS[n]floating to enable the "disk in loop" mode. HDMP-0450s may be cascaded with other members of the HDMP-04XX/HDMP-05XX family through the appropriate  $FM_NODE[n] \pm$  and TO NODE[n] $\pm$  pins to accommodate any number of hard disks (see Figure 3). The unused cells in the HDMP-0450 may be bypassed by using pulldown resistors on the BYPASS[n]- pins for these cells.

An HDMP-0450 may also be configured as five 1:1 buffers, as two 2:1 multiplexers, or as two 1:2 buffers.

### Features

- Supports 1.0625 GBd Fibre Channel operation

- Supports 1.25 GBd Gigabit Ethernet (GE) operation

- Quad PBC in one package

- Signal detect on FM\_NODE[0] input

- · Equalizers on all inputs

- High speed LVPECL I/O

- Buffered Line Logic (BLL) outputs (no external bias resistors required)

- 0.5 W typical power at V<sub>CC</sub> = 3.3 V

- 44 Pin, 10 mm, low-cost plastic QFP package

### **Applications**

- RAID, JBOD, BTS cabinets

- Two 2:1 muxes

- Two 1:2 buffers

- 1 => N gigabit serial buffer

- N => 1 gigabit serial mux

*CAUTION:* As with all semiconductor ICs, it is advised that normal static precautions be taken in the handling and assembly of this component to prevent damage and/or degradation which may be induced by electrostatic discharge (ESD).

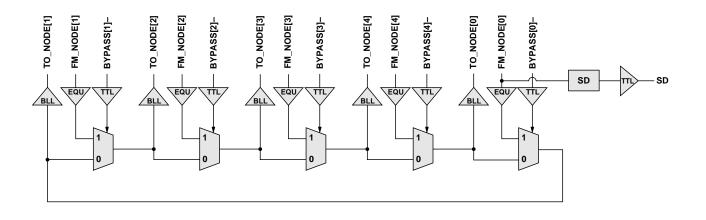

Figure 1. Block diagram of HDMP-0450.

### HDMP-0450 Block Diagram BLL OUTPUT

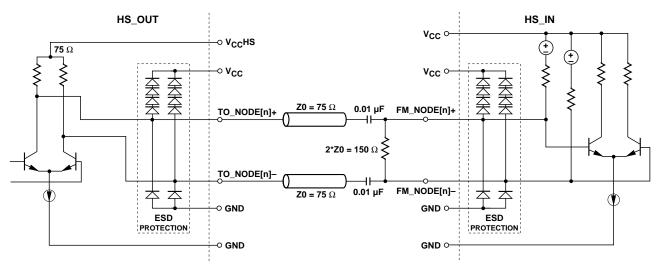

All TO\_NODE[n]± high-speed differential outputs are driven by a Buffered Line Logic (BLL) circuit that has on-chip source termination, so no external bias resistors are required. The BLL outputs on the HDMP-0450 are of equal strength and can drive in lengthy FR-4 PCB trace.

Unused outputs should not be left unconnected. Ideally, unused outputs should have their differential pins shorted together with a short PCB trace. If longer traces or transmission lines are connected to the output pins, the lines should be differentially terminated with an appropriate resistor. The value of the termination resistor should match the PCB trace differential impedance.

### **EQU INPUT**

All FM\_NODE[n]± high-speed differential inputs have an Equalization (EQU) buffer to offset the effects of skin loss and dispersion on PCBs. An external termination resistor is required across all high-speed inputs. The value of the termination resistor should match the PCB trace differential impedance. Alternatively, instead of a single resistor, two resistors in series, with an AC ground between them, can be connected differentially across the FM NODE[n]± inputs. The latter configuration attenuates high-frequency common mode noise.

#### BYPASS[n]- INPUT

The active low BYPASS[n]- inputs control the data flow through the HDMP-0450. All BYPASS pins are LVTTL and contain internal pullup circuitry. To bypass a port, the appropriate BYPASS[n]- pin should be connected to GND through a 1 k $\Omega$  resistor. Otherwise, the BYPASS[n]-inputs should be left to float, as the internal pull-up circuitry will force them high.

#### **SD OUTPUT**

The Signal Detect (SD) block detects if the incoming data on FM NODE [0]± is valid by examining the differential amplitude of that input. The incoming data is considered valid, and SD is driven high, as long as the amplitude is greater than 400 mV (differential peak-topeak). SD is driven low as long as the amplitude of the input signal is less than 100 mV (differential peak-to-peak). When the amplitude of the input signal is between 100-400 mV (differential peak-to-peak), the SD output is undefined.

Figure 2. Connection diagram for Disk Array applications.

Figure 3. Connection diagram for multiple HDMP-0450s.

# I/O Type Definitions

| I/O Type | Definition                           |

|----------|--------------------------------------|

| I-LVTTL  | LVTTL Input                          |

| 0-LVTTL  | LVTTL Output                         |

| HS_OUT   | High Speed Output. LVPECL Compatible |

| HS_IN    | High Speed Input                     |

| С        | External Circuit Note                |

| S        | Power Supply or Ground               |

# **Pin Definitions**

| Pin Name    | Pin | Pin Type | Pin Description                                                                      |

|-------------|-----|----------|--------------------------------------------------------------------------------------|

| TO_NODE[0]+ | 24  | HS_OUT   | Serial Data Outputs: High-speed outputs to a hard disk drive or to a cable.          |

| TO_NODE[0]- | 25  | —        |                                                                                      |

| TO_NODE[1]+ | 07  |          |                                                                                      |

| TO_NODE[1]– | 06  |          |                                                                                      |

| TO_NODE[2]+ | 44  |          |                                                                                      |

| TO_NODE[2]– | 43  |          |                                                                                      |

| TO_NODE[3]+ | 38  |          |                                                                                      |

| TO_NODE[3]– | 37  |          |                                                                                      |

| TO_NODE[4]+ | 31  |          |                                                                                      |

| TO_NODE[4]– | 30  |          |                                                                                      |

| FM_NODE[0]+ | 10  | HS_IN    | Serial Data Inputs: High-speed inputs from a hard disk drive or from a cable.        |

| FM_NODE[0]- | 09  |          |                                                                                      |

| M_NODE[1]+  | 04  |          |                                                                                      |

| FM_NODE[1]- | 03  |          |                                                                                      |

| FM_NODE[2]+ | 41  |          |                                                                                      |

| FM_NODE[2]— | 40  |          |                                                                                      |

| FM_NODE[3]+ | 35  |          |                                                                                      |

| FM_NODE[3]– | 34  |          |                                                                                      |

| FM_NODE[4]+ | 28  |          |                                                                                      |

| FM_NODE[4]– | 27  |          |                                                                                      |

| BYPASS[0]–  | 14  | I-LVTTL  | Bypass Inputs: For "disk bypassed" mode, connect BYPASS[n]- to GND through           |

| BYPASS[1]-  | 15  |          | a 1 k $\Omega$ resistor. For "disk in loop" mode, float HIGH.                        |

| BYPASS[2]-  | 16  |          |                                                                                      |

| BYPASS[3]-  | 17  |          |                                                                                      |

| BYPASS[4]-  | 18  |          |                                                                                      |

| SD          | 20  | 0-LVTTL  | Signal Detect: Indicates acceptable signal amplitude on the FM_NODE[0] $\pm$ inputs. |

|             |     |          | If (FM_NODE[0]+ - FM_NODE[0]-) >= 400 mV peak-to-peak, SD = 1                        |

|             |     |          | If 400 mV > (FM_NODE[0]+ - FM_NODE[0]-) > 100 mV, SD = undefined                     |

|             |     |          | If 100 mV >= (FM_NODE[0]+ - FM_NODE[0]-), SD = 0                                     |

| GND      | 01 | S | Ground: Normally 0 volts. See Figure 9 for Recommended Power Supply Filtering. |

|----------|----|---|--------------------------------------------------------------------------------|

|          | 08 |   | , 5 11, 5                                                                      |

|          | 11 |   |                                                                                |

|          | 12 |   |                                                                                |

|          | 13 |   |                                                                                |

|          | 19 |   |                                                                                |

|          | 22 |   |                                                                                |

|          | 23 |   |                                                                                |

|          | 33 |   |                                                                                |

|          | 39 |   |                                                                                |

| VCCHS[0] | 26 | S | High Speed Supply: Normally 3.3 volts. Used only for high-speed outputs        |

| VCCHS[1] | 05 | S | (TO_NODE[n]). See Figure 9 for Recommended Power Supply Filtering.             |

| VCCHS[2] | 42 | S |                                                                                |

| VCCHS[3] | 36 | S |                                                                                |

| VCCHS[4] | 29 | S |                                                                                |

| VCC      | 02 | S | Logic Power Supply: Normally 3.3 volts. Used for internal logic.               |

|          | 21 |   | See Figure 9 for Recommended Power Supply Filtering.                           |

|          | 32 |   |                                                                                |

## **Pin Definitions, continued**

### **Absolute Maximum Ratings**

T<sub>A</sub> = 25°C, except as specified. Operation in excess of any of these conditions may result in permanent damage to this device. Continuous operation at these minimum or maximum ratings is not recommended.

| Symbol                 | Parameter                          | Units | Min. | Max.                                 |

|------------------------|------------------------------------|-------|------|--------------------------------------|

| V <sub>CC</sub>        | Supply Voltage                     | V     | -0.5 | 4.0                                  |

| V <sub>IN,LVTTL</sub>  | LVTTL Input Voltage                | V     | -0.5 | V <sub>CC</sub> + 0.5 <sup>[1]</sup> |

| V <sub>IN,HS</sub> _IN | HS_IN Input Voltage (Differential) | mV    | 200  | 2000                                 |

| I <sub>0,LVTTL</sub>   | LVTTL Output Sink/Source Current   | mA    |      | ±13                                  |

| T <sub>stg</sub>       | Storage Temperature                | °C    | -65  | +150                                 |

| Tj                     | Junction Temperature               | °C    | 0    | +125                                 |

Note:

1. Must remain less than or equal to absolute maximum  $V_{CC}$  voltage of 4.0 V.

### **DC Electrical Specifications**

| $V_{CC} = 3.15$ | V to 3.45 V |  |

|-----------------|-------------|--|

| Symbol                | Parameter                                                          | Units | Min. | Тур. | Max.            |

|-----------------------|--------------------------------------------------------------------|-------|------|------|-----------------|

| V <sub>IH,LVTTL</sub> | LVTTL Input High Voltage Range                                     | V     | 2.0  |      |                 |

| V <sub>IL,LVTTL</sub> | LVTTL Input Low Voltage Range                                      | V     |      |      | 0.8             |

| V <sub>OH,LVTTL</sub> | LVTTL Output High Voltage Range, I <sub>OH</sub> = –400 μA         | V     | 2.2  |      | V <sub>CC</sub> |

| V <sub>OL,LVTTL</sub> | LVTTL Output Low Voltage Level, $I_{OL} = 1 \text{ mA}$            | V     | 0    |      | 0.6             |

| I <sub>IH,LVTTL</sub> | Input High Current (Magnitude), V_{IN} = 2.4 V, V_{CC} = 3.45 V    | μA    |      |      | 40              |

| I <sub>IL,LVTTL</sub> | Input Low Current (Magnitude), $V_{IN}$ = 0.4 V, $V_{CC}$ = 3.45 V | μA    |      |      | -600            |

| Icc                   | Total Supply Current, $T_A = 25^{\circ}C$                          | mA    |      | 150  | 185             |

### **AC Electrical Specifications**

$V_{CC} = 3.15 \text{ V} \text{ to } 3.45 \text{ V}$

| Symbol                 | Parameter                                                                     | Units | Min. | Тур. | Max. |

|------------------------|-------------------------------------------------------------------------------|-------|------|------|------|

| T <sub>LOOP_LAT</sub>  | Total Loop Latency from FM_NODE[0] to TO_NODE[0]                              | ns    |      | 2.0  |      |

| T <sub>CELL_LAT</sub>  | Per Cell Latency from FM_NODE[4] to TO_NODE[0]                                | ns    |      | 0.8  |      |

| t <sub>r,LVTTLin</sub> | Input LVTTL Rise Time Requirement, 0.8 V to 2.0 V                             | ns    |      | 2.0  |      |

| t <sub>f,LVTTLin</sub> | Input LVTTL Fall Time Requirement, 2.0 V to 0.8 V                             | ns    |      | 2.0  |      |

| t <sub>r,LVTTout</sub> | Output TTL Rise Time, 0.8 V to 2.0 V, 10 pF Load                              | ns    |      | 1.7  | 3.3  |

| t <sub>f,LVTTout</sub> | Output TTL Fall Time, 2.0 V to 0.8 V, 10 pF Load                              | ns    |      | 1.7  | 2.4  |

| t <sub>rs,HS_OUT</sub> | HS_OUT Single-Ended Rise Time, 20%-80%                                        | ps    |      | 200  | 300  |

| t <sub>fs,HS_OUT</sub> | HS_OUT Single-Ended Fall Time, 20%-80%                                        | ps    |      | 200  | 300  |

| t <sub>rd,HS_OUT</sub> | HS_OUT Differential Rise Time, 20%-80%                                        | ps    |      | 200  | 300  |

| t <sub>fd,HS_OUT</sub> | HS_OUT Differential Fall Time, 20%-80%                                        | ps    |      | 200  | 300  |

| V <sub>IP,HS_IN</sub>  | HS_IN Required Peak-to-Peak Differential Input Voltage                        | mV    | 200  | 1200 | 2000 |

| V <sub>OP,HS_OUT</sub> | HS_OUT Peak-to-Peak Differential Output Voltage (Z0 = 75 $\Omega$ , Figure 6) | mV    | 1100 | 1400 | 2000 |

#### **Guaranteed Operating Rates** Vcc = 3 15 V to 3 45 V

| $\frac{V_{CC} = 3.15 \ V \ to}{FC \ Serial \ Clock}$ |       | GE Serial Clock | c Rate (MBd) |

|------------------------------------------------------|-------|-----------------|--------------|

| Min.                                                 | Max.  | Min.            | Max.         |

| 1,040                                                | 1,080 | 1,240           | 1,260        |

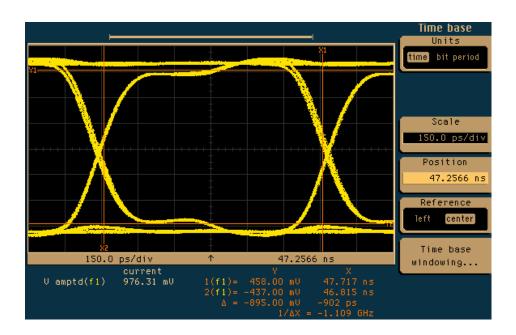

Figure 4. Eye diagram of TO\_NODE[1]± high speed differential output (50  $\Omega$  termination). Note: Measurement taken with a 2^7-1 PRBS input to FM\_NODE[1]±.

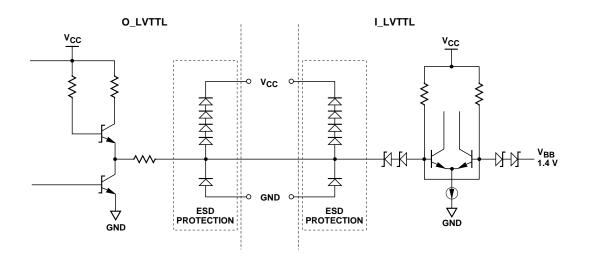

Figure 5. O-LVTTL and I-LVTTL simplified circuit schematic.

NOTE:

FM\_NODE[n] INPUTS SHOULD NEVER BE CONNECTED TO GROUND AS PERMANENT DAMAGE TO THE DEVICE MAY RESULT.

Figure 6. HS\_OUT and HS\_IN simplified circuit schematic.

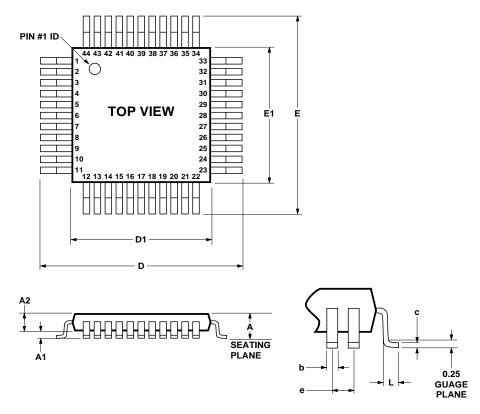

### **Package Information**

### **Power Dissipation and Thermal Resistance**

V<sub>CC</sub> = 3.15 V to 3.45 V

| Symbol                         | Parameter                            | Units | Тур. | Max. |

|--------------------------------|--------------------------------------|-------|------|------|

| PD                             | Power Dissipation                    | mW    | 500  | 640  |

| θ <sub>jc</sub> <sup>[1]</sup> | Thermal Resistance, Junction to Case | °C/W  | 7    |      |

Note:

Based on independent package testing by Agilent. θ<sub>ja</sub> for this device is 57°C/W. θ<sub>ja</sub> is measured on a standard 3x3" FR4 PCB in a still air environment. To determine the actual junction temperature in a given application, use the following equation:

$T_j = T_c + (\theta_{jc} \times P_D)$ , where  $T_c$  is the case temperature measured on the top center of the package and  $P_D$  is the power being dissipated.

| ltem                             | Details              |

|----------------------------------|----------------------|

| Package Material                 | Plastic              |

| Lead Finish Material             | 85% Tin, 15% Lead    |

| Lead Finish Thickness            | 200-800 micro-inches |

| Lead Skew                        | 0.33 mm max.         |

| Lead Coplanarity (Seating Plane) | 0.10 mm max.         |

### **Mechanical Dimensions**

| ALL DIMENSIONS | ARE IN | METERS | 5 |

|----------------|--------|--------|---|

|                |        |        |   |

| PART NUMBER | E1/D1  | E/D    | b      | е     | L                 | с    | A2                | A1     | Α    |

|-------------|--------|--------|--------|-------|-------------------|------|-------------------|--------|------|

| HDMP-0450   | 10.00  | 13.20  | 0.35   | 0.80  | 0.88              | 0.23 | 2.00              | 0.25   | 2.45 |

| TOLERANCE   | ± 0.10 | ± 0.20 | ± 0.05 | BASIC | + 0.15/<br>– 0.10 | MAX. | + 0.10/<br>- 0.05 | ± 0.25 | MAX. |

Figure 7. HDMP-0450 package drawing.

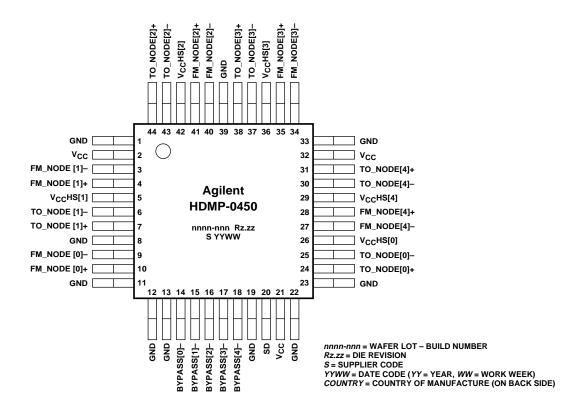

### Pin Diagram and Recommended Supply Filtering

Figure 8. HDMP-0450 package layout and marking, top view.

Figure 9. Recommended power supply filtering.

### www.agilent.com/semiconductors

For product information and a complete list of distributors, please go to our web site. For technical assistance call: Americas/Canada: +1 (800) 235-0312 or (408) 654-8675 Europe: +49 (0) 6441 92460 China: 10800 650 0017 Hong Kong: (+65) 6271 2451 India, Australia, New Zealand: (+65) 6271 2394 Japan: (+81 3) 3335-8152(Domestic/International), or 0120-61-1280(Domestic Only) Korea: (+65) 6271 2194 Malaysia, Singapore: (+65) 6271 2054 Taiwan: (+65) 6271 2654 Data subject to change. Copyright © 2002 Agilent Technologies, Inc. August 26, 2002 5988-7490EN

🗧 Agilent Technologies