# TOSCATM INTEGRATED ADSL CMOS ANALOG FRONT-END CIRCUIT

- FULLY INTEGRATED AFE FOR ADSL

- OVERALL 12 BIT RESOLUTION, 1.1MHz SIGNAL BANDWIDTH

- 8.8MS/s ADC

- 8.8MS/s DAC

- THD: -60dB @FULL SCALE

- 4-BIT DIGITAL INTERFACE TO/FROM THE DMT MODEM

- 1V FULL SCALE INPUT

- DIFFERENTIAL ANALOG I/O

- ACCURATE CONTINUOUS-TIME CHANNEL FILTERING

- 3rd & 4th ORDER TUNABLE CONTINUOUS TIME LP FILTERS

- 0.5 WATT AT 3.3V

- 0.5µm HCMOS5 LA TECHNOLOGY

- 64 PIN TQFP PACKAGE

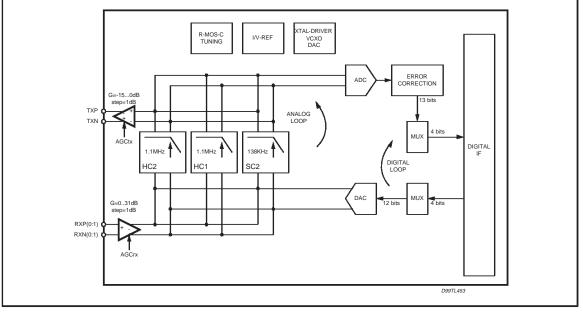

#### DESCRIPTION

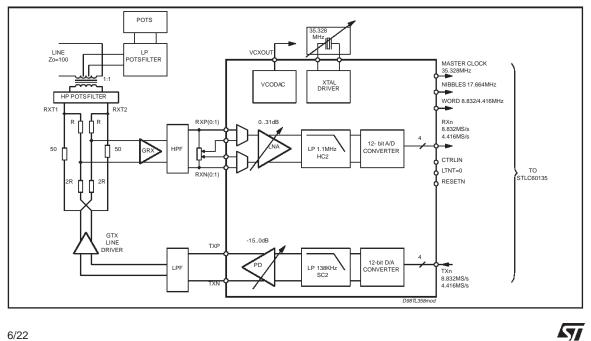

STLC60134S is the Analog Front End of the STMicroelectronics Tosca<sup>™</sup> ADSL chipset and when coupled with STLC60135 (DTM modem) al-

#### Figure 1. Block Diagram

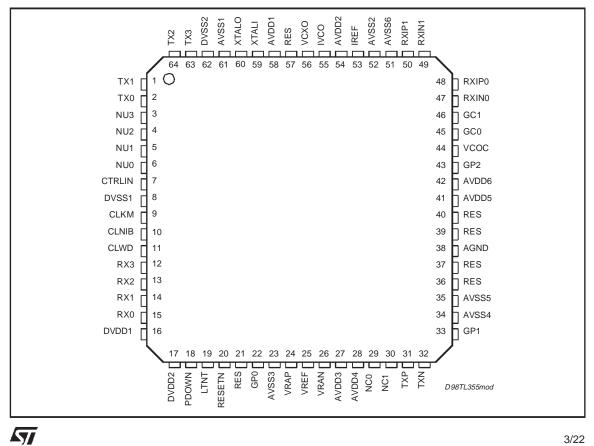

TQFP64

**ORDERING NUMBER: STLC60134S**

lows to get a T1.413 Issue 2 compliant solution.

The STLC60134S analog front end handles 2 transmission channels on a balanced 2 wire interconnection; a 16 to 640Kbit/s upstream channel and a 1.536 to 8.192Mbit/s downstream channel.

A 256 carrier DMT coding (frequency spacing 4.3125kHz) transforms the downstream channel to a 1MHz bandwidth analog signal (tones 32-255) and the upstream channel (tones 8-31) to a 100kHz bandwidth signal on the line.

This asymmetrical data transmission system uses high resolution, high speed analog to digital and digital to analog conversion and high order analog filtering to reduce the echo and noise in both

#### August 1999

1/22

the ATU-C/ATU-R receivers and transmitters. External low noise driver and input stage used with STLC60134S guarantee low noise performances.

The STLC60134S chip can be used at ATU-C and ATU-R ends (behaviour set by LTNT pin). The selection consists mainly of a filter interchange between the RX and TX path. The filters (with a programmable cutoff frequency) use automatic Continuous Time Tuning to avoid time varying phase characteristic which can be of dramatic consequence for DMT modem. It requires few external components, uses a 3.3V supply (a separate 3.0V supply of the digital part is possible) and is packaged in a 64-pin TQFP in order to reduce PCB area.

## The Receiver (RX) part

The DMT signal coming from the line to the STLC60134S is first filtered by the two following external filters:

| POTS HP filter: | Attenuation of speech and POTS signalling           |

|-----------------|-----------------------------------------------------|

| Channel filter: | Attenuation of echo signal to<br>improve RX dynamic |

An analog multiplexer allows the selection between two input ports which can be used to select an attenuated (0, 10dB for ex.) version of the signal in case of short loop or large echo. The signal is amplified by a low noise gain stage (0-31dB) then low-pass filtered to avoid anti-aliasing and to ease further digital processing by removing unwanted high frequency out-of-band noise.

A 12-bit A/D converter samples the data at 8.832MS/s (or 4.416MS/s in alternative mode), transforms the signal into a digital representation and sends it to the DMT signal processor via the digital interface.

#### The Transmitter (TX) part

The 12-bit data words at 8.832MS/s (or 4.416MS/s) coming from the DMT signal processor through the digital interface are transformed by D/A converter into a analog signal.

This signal is then filtered to decrease DMT sidelobes level and meet the ANSI transmitter spectral response but also to reduce the out-of-band noise (which can be echoed to the RX path) to an acceptable level. The pre-driver buffers the signal for the external line driver and in case of short loop provide attenuation (-15...0dB).

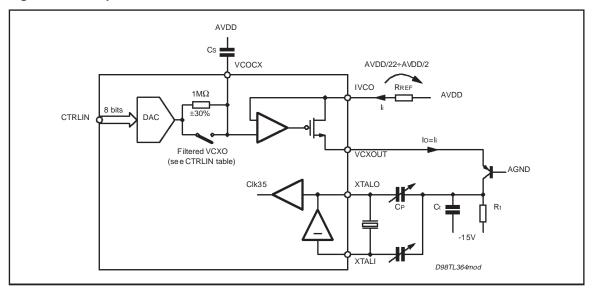

## The VCXO part

The VCXO is divided in a XTAL driver and a auxiliary 8 bits DAC for timing recovery.

The XTAL driver is able to operate at 35.328MHz and provides an amplitude regulation mechanism to avoid temperature / supply / technology dependent frequency pulling.

The DAC which is driven by the CTRLIN pin provides a current output with 8-bit resolution and can be used to tune the XTAL frequency with the help of external components. A time constant between DAC input and VCXO output can be introduced (via the CTLIN interface) and programmed with the help of an external capacitor (on VCOC pin).

See chapter 'VCXO' for the external circuit related to the VCXO.

#### The Digital Interface part

The digital part of the STLC60134S can be divided in 3 sections:

- The data interface converts the multiplexed data from/to the DMT signal processor into valid representation for the TX DAC and RX ADC. It performs also the error correction mechanism needed at the (redundant) ADC output.

- The control interface allows the board processor to configure the STLC60134S paths (RX/TX gains, filter band, ...) or settings (OSR, vcodac enable, digital / analog loopback,...).

- The test interface to enable digital (Full Scan, nandtree, loop backs, functional,...) or analog (TIN, TOUT assignation) tests to be performed.

#### **DMT Signal**

A DMT signal is basically the sum of N independently QAM modulated signals, each carried over a distinct carrier. The frequency separation of each carrier is 4.3125kHz with a total number of 256 carriers (ANSI). For N large, the signal can be modelled by a gaussian process with a certain amplitude probability density function. Since the maximum amplitude is expected to arise very rarely, we decide to clip the signal and to tradeoff the resulting SNR loss against AD/DA dynamic. A clipping factor (Vpeak/Vrms = "crest factor") of 5 will be used resulting in a maximum SNR of 75dB.

ADSL DMT signals are nominally sent at -40dBm/Hz

$\pm$ 3dB (-3.65dBm/carrier) with a maximal power of 100mW for down link transmitter and 15.7mW for uplink transmitter.

DMT symbols are transmitted without 'windowing' causing sin (x)/x like sidelobes. For spectral response shaping, the 1st sidelobe level is assumed to be 13dB under the carrier level with an attenuation of -20dB/dec.

The minimum SNR + D needed for DMT carrier demodulation is about  $(3 \cdot N + 20)$  dB with a minimum of 38dB were N is the constellation size of a carrier (in bits).

#### Maximum / minimum signal levels

The following table gives the transmitted and received signal levels for both ATU-R and ATU-C sides. All the levels are referred to the line voltages (i.e. after hybrid and transformers in TX direction, before hybrid and transformer in RX direction).

Note that signal amplitudes shown below are for illustration purpose and depending on the trans-

Table 1. Target Signal Levels (on the line).

mit power and line impedance signal amplitudes can differ from these values.

The reference line impedance for all power calculations is  $100\Omega$ .

#### PACKAGE

The STLC60134S is packaged in a 64-pin TQFP package (body size 10x10mm, pitch 0.5mm).

| Parameter     | ATU - C    |            | eter ATU - C ATU - R |            | J - R |

|---------------|------------|------------|----------------------|------------|-------|

|               | RX         | ТΧ         | RX                   | ΤХ         |       |

| Max level     | 839 mVpdif | 15.8 Vpdif | 3.95 Vpdif           | 3.4 Vpdif  |       |

| Max RMS level | 168 mVrms  | 3.16 Vrms  | 791 mVrms            | 671 mVrms  |       |

| Min level     | 54 mVpdif  | 3.95 Vpdif | 42 mVpdif            | 839 mVpdif |       |

| Min RMS level | 11 mVrms   | 791 mVrms  | 8 mVrms              | 168 mVrms  |       |

Table 2. Total Signal Level (on the line).

| Parameter              | ATU - C             |    | ATU - R                |    |

|------------------------|---------------------|----|------------------------|----|

|                        | RX                  | ТХ | RX                     | ТΧ |

| Max level for receiver | 4 Vpdif (Long line) |    | 4.2 Vpdif (Short line) |    |

#### **Figure 2. Pin Connection**

## STLC60134S

## Table 3. Pin Functions.

| Ν.                       | Name      | Function                                                               | PCB connection                       | Supply |

|--------------------------|-----------|------------------------------------------------------------------------|--------------------------------------|--------|

| ANALC                    | G INTERF  | ACE                                                                    |                                      |        |

| 24                       | VRAP      | positive voltage reference ADC                                         | Decoupling network                   | AVDD3  |

| 25                       | VREF      | ground reference ADC                                                   | Decoupling network                   |        |

| 26                       | VRAN      | negative voltage reference ADC                                         | Decoupling network                   | AVDD3  |

| 31                       | TXP       | pre driver output                                                      | Line driver input                    | AVDD4  |

| 32                       | TXN       | pre driver output                                                      | Line driver input                    | AVDD4  |

| 38                       | AGND      | virtual analog ground (AVDD/2 = 1.65V)                                 | Decoupling network                   | AVDD5  |

| 44                       | VCOC      | VCODAC time constant capacitor                                         | VCODAC cap.                          | AVDD5  |

| 45                       | GC0       | External gain control output LSB                                       |                                      | AVDD5  |

| 46                       | GC1       | External gain control output MSB                                       |                                      | AVDD5  |

| 47                       | RXN0      | analog receive negative input Gain 0                                   | Echo filter output                   | AVDD5  |

| 48                       | RXP0      | analog receive positive input Gain 0                                   | Echo filter output                   | AVDD5  |

| 49                       | RXN1      | analog receive negative input Gain 1 (most sensitive input)            | Echo filter output                   | AVDD5  |

| 50                       | RXP1      | analog receive positive input Gain 1 (most sensitive input)            | Echo filter output                   | AVDD5  |

| 53                       | IREF      | current reference TX DAC/DACE                                          | Decoupling network                   | AVDD2  |

| 55                       | IVCO      | current reference VCO DAC                                              | VCO bias network                     | AVDD1  |

| 56                       | VCXO      | VXCO control current                                                   | VCXO filter                          | AVDD1  |

| 59                       | XTALI     | XTAL oscillator input pin                                              | Crystal + varicap                    | AVDD1  |

| 60                       | XTALO     | XTAL oscillator output pin                                             | Crystal + varicap                    | AVDD1  |

| DIGITA                   | L INTERFA | CE                                                                     |                                      | •      |

| 1                        | TX1       | digital transmit input, parallel data                                  |                                      | DVDD2  |

| 2                        | TX0       | digital transmit input, parallel data                                  |                                      | DVDD2  |

| 7                        | CTRLIN    | serial data input (settings)                                           | Async Interface                      | DVDD2  |

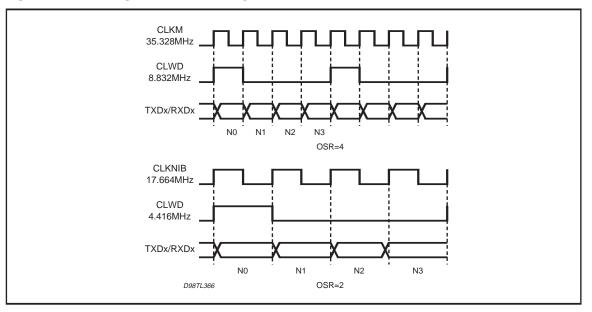

| 9                        | CLKM      | master clock output, f = 35.328MHz                                     | Load = CL<30pF                       | DVDD2  |

| 10                       | CLNIB     | nibble clock output, f = 17.664MHz (OSR = 2) or ground (OSR = 4)       | Load = CL<30pF                       | DVDD2  |

| 11                       | CLWD      | word clock output, f = 8.832/4.416MHz                                  | Load = CL<30pF                       | DVDD2  |

| 12                       | RX3       | digital receive output, parallel data                                  | Load = CL<30pF                       | DVDD2  |

| 13                       | RX2       | digital receive output, parallel data                                  | Load = CL<30pF                       | DVDD2  |

| 14                       | RX1       | digital receive output, parallel data                                  | Load = CL<30pF                       | DVDD2  |

| 15                       | RX0       | digital receive output, parallel data                                  | Load = CL<30pF                       | DVDD2  |

| 18                       | PDOWN     | power down select, "1" = power down                                    | Power down input                     | DVDD2  |

| 19                       | LTNT      | ATU-R / ATU-C select pin $^{1}$ , ATU-R = 0 /ATU-C = 1 / test mode MSB | VDD in ATU-C mode                    | DVDD2  |

| 20                       | RESETN    | reset pin (active low)                                                 | RC- reset                            | DVDD2  |

| 22                       | GP0       | General purpose output 0 (on AVDD 1)                                   | Echo filter output                   | AVDD   |

| 33                       | GP1       | General purpose output 1 (on AVDD 1)                                   | Echo filter output                   | AVDD   |

| 43                       | GP2       | General purpose output 2 (on AVDD 1)                                   | Echo filter output                   | AVDD   |

| 63                       | TX3       | digital transmit input, parallel data                                  | Load = CL<30pF                       | DVDD2  |

| 64                       | TX2       | digital transmit input, parallel data                                  | Load = CL<30pF                       | DVDD2  |

| 21                       | RES       | RESERVED                                                               | Must be connected<br>to DVSS (input) |        |

| 36,<br>37, 39,<br>40, 57 | RES       | RESERVED                                                               | Must be connected to AVSS (input)    |        |

| SUPPL                    | Y VOLTAG  | ES                                                                     |                                      |        |

| 8                        | DVSS1     |                                                                        | DVSS                                 |        |

| 16                       | DVDD1     | Digital I/O supply voltage                                             | DVDD                                 | İ      |

| 17                       | DVDD2     | digital internal supply voltage                                        | DVDD                                 | İ      |

| 23                       | AVSS3     |                                                                        | AVSS                                 |        |

| 27                       | AVDD3     | ADC supply voltage                                                     | AVDD                                 | 1      |

4/22

| 28    | AVDD4 | TX pre - drivers supply        | AVDD |

|-------|-------|--------------------------------|------|

| 34    | AVSS4 |                                | AVSS |

| 35    | AVSS5 |                                | AVSS |

| 41    | AVDD5 | CT filter supply               | AVDD |

| 42    | AVDD6 | LNA supply                     | AVDD |

| 51    | AVSS6 |                                | AVSS |

| 52    | AVSS2 |                                | AVSS |

| 54    | AVDD2 | DAC and support circuit        | AVDD |

| 58    | AVDD1 | XTAL oscillator supply voltage | AVDD |

| 61    | AVSS1 |                                | AVSS |

| 62    | DVSS2 |                                | DVSS |

| SPARE | S     |                                |      |

| 3     | NU3   | Not used inputs                | DVSS |

| 4     | NU2   | Not used inputs                | DVSS |

| 5     | NU1   | Not used inputs                | DVSS |

| 6     | NU0   | Not used inputs                | DVSS |

| 29    | NC0   |                                |      |

| 30    | NC1   |                                |      |

#### Table 3. Pin Functions (continued)

<sup>1</sup> LT  $\leftrightarrow$  AUT-C; NT  $\leftrightarrow$  ATU-R

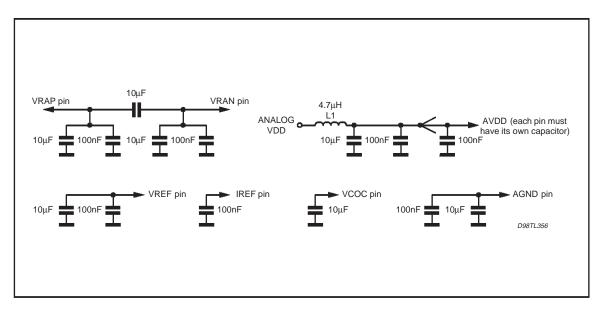

Figure 3. Grounding and Decoupling Networks.

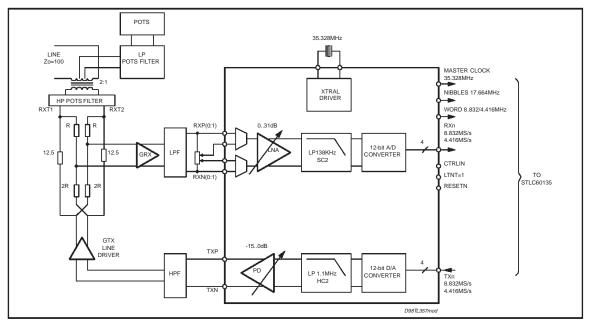

## ATU-C END: BLOCK DIAGRAM

The transformer at ATU-C side has 1:2 ratio. The termination resistors are  $12.5\Omega$  in case of  $100\Omega$  lines.

The hybrid bridge resistors should be <  $2.5k\Omega$  for low-noise.

An HP filter must be used on the TX path to re-

duce DMT sidelobes and out of band noise influence on the receiver. On the RX path, a LP filter must be used in order to reduce the echo signal level and to avoid saturation of the input stage of the receiver.

The POTS filter is used in both directions to reduce crosstalk between STLC60134S signals and POTS speech and signalling.

## ATU-R END: BLOCK DIAGRAM

The ATU-R side block diagram is equal to the ATU-C side block diagram with the following differences:

- The transformer ratio is 1:1

- Termination resistors are  $50\Omega$  for  $100\Omega$  lines.

An LP filter may be used on the TX path to re-

duce DMT sidelobes and out of band noise influence on the receiver. On the RX path, a HP filter must be used in order to reduce the echo signal level and to avoid saturation of the input stage of the receiver.

The POTS filter is used in both directions to reduce crosstalk between ADSL signals and POTS speech and signalling. Low pass POTS filter can be very simple for Lite - ADSL application

### **RX PATH**

#### **Speech filter**

An external bi-directional LC filter for up and downstream POTS service splits the speech signal from the ADSL signal to the POTS circuits on ATU-C.

The ADSL analog front end integrated circuit does not contain any circuitry for the POTS service but it guarantees that bandwidth is not disturbed by spurious signals from the ADSL-spectrum.

#### **Channel Filters**

The external analog circuits provide partial echo cancellation by an analog filtering of the receive signal for both ATU-R (Reception of downstream channel) and ATU-C (Reception of upstream channel). This is feasible because the upstream and the downstream data can be modulated on separate carriers (FDM).

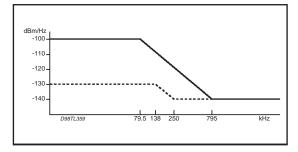

#### Line Noise Model

The power spectral density of the crosstalk noise sources as described in ANSI document is given in the figure below (no HDB3 interferer signals). Also given in dotted line, is the noise model used in this document to specify the sensivity requirements which are stronger than the original ones.

#### Figure 6. Crosstalk PSD.

#### Signal to Noise Performance

**RX- PATH SENSITIVITY AT MAXIMUM GAIN**

The RX path sensitivity at the maximal RX-AGC of the ATU-R receiver is defined at -140dBm/Hz (for  $100\Omega$  ref) on the line. This figure corresponds to the equivalent input noise of  $31nVHz^{1/2}$  seen on the line.

The sensitivity at the maximal RX - gain of the ATU-C receiver is defined at -130dBm/Hz (for 100 $\Omega$  ref) on the line. The figure corresponds to the equivalent input noise of 100nVHz<sup>1/2</sup> seen on the line.

Both noise figures include the noise of the hybrid. It is the equivalent average thermal noise over

the frequency band of interest. The maximum noise density within the pass band can exceed the average value as follows:

ATU-R RX path (max AGC setting):

<100nVHz<sup>1/2</sup> @ 138kHz

<31nVHz<sup>1/2</sup> for 250kHz < f

ATU-C RX path (max AGC setting):

<100nVHz<sup>1/2</sup> for 34.5kHz < f <138kHz

#### **RX-PATH NOISE AT MINIMUM GAIN**

At the minimum AGC the total average thermal noise of the analog RX-path at the ADC input should be lower than the ADC quantisation noise. The maximum noise density within the pass band can exceed the average value as follows:

ATU-R RX path (min AGC setting):

<500nVHz<sup>1/2</sup> @ 138kHz < f

ATU-C RX path (min AGC setting):

$<1.5\mu$ VHz<sup>-1/2</sup> @ 34.5kHz < f < 138kHz

These noise specifications correspond with 10bit resolution of the complete RX-path.

#### Table 4. RX Common-mode Voltage

| Description                                               | Value/Unit             |

|-----------------------------------------------------------|------------------------|

| Common mode signal V <sub>CM</sub><br>at RXIN1 and RXIN2: | $1.6V < V_{CM} < 1.7V$ |

#### AGC of RX path

The AGC gain in the RX-path is controlled through a 5-bits digital code.

Four inputs are provided for RX input and the selection is made with the RXMUX bits of the CTRLIN interface. This can be used to make lower gain paths in case of high input signal.

#### Table 5. AGC Characteristics.

| Description                         | Value/Unit                |

|-------------------------------------|---------------------------|

| Input referred noise<br>(max. gain) | 20nVHz <sup>-1/2</sup>    |

| Max. input level                    | 1Vpd                      |

| Max. output level                   | 1Vpd                      |

| Gain range                          | 0 to 31dB with step = 1dB |

| Gain and step accuracy              | ± 0.3dB                   |

#### **RX Filters**

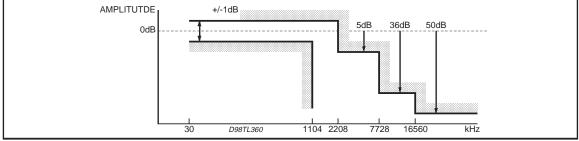

The combination of the external filter (an LC ladder filter typically) with the integrated lowpass filter must provide:

- echo reduction to improve dynamic range

- DMT sidelobe and out of band (anti-aliasing) attenuation.

- Anti alias filter (60dB rejection @ image freq.)

#### **ATU-R RX Filters**

The integrated filter have the following characteristics: **Table 6. Integrated HC Filter Characteristics**

| Description                                                                                              | Value/Unit                                                                                                                  |

|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Input referred noise                                                                                     | 100nVHz <sup>-1/2</sup>                                                                                                     |

| Max. input level                                                                                         | 1Vpd                                                                                                                        |

| Max. output level                                                                                        | 1Vpd                                                                                                                        |

| Туре                                                                                                     | 3rd order butterworth                                                                                                       |

| Frequency band                                                                                           | 1.104MHz (0%setting, see below)                                                                                             |

| Frequency tuning                                                                                         | -43.75% ->+0%                                                                                                               |

| Max. in-band ripple                                                                                      | 1dB                                                                                                                         |

| Matlab Model<br>Default cut off frequency @ -3dB<br>Actual cut off @ -3dB<br>HC Freq. selection register | [B, A] = butter (3, w0, 's')<br>F0 = 1560KHz<br>w0 = 2 * pi * F0/((20 + n)/16)<br>n = -4,,3<br>see (AFE settings ,Table 22) |

#### **Table 7. Phase Characteristic**

| Description                            | Value/Unit                     |

|----------------------------------------|--------------------------------|

| Total RX filter group delay            | < 50μs @ 138kHz < f < 1.104MHz |

| Total RX filter group delay distortion | < 15µs @ 138kHz < f < 1.104MHz |

#### Figure 7. HC Filter Mask for ATU-R RX and ATU-C TX

Note: The total ATU\_R RX path (including ADC) group delay distortion is 16µs (i.e. = 15µs + 1µs of ADC)

#### ATU-C RX filter

This filter is the same as the one used for ATU-R TX.

#### Linearity of RX

Linearity of the RX analog path is defined by the IM3 product of two sinusoidal signals with frequencies f1 and f2 and each with 0.5Vpd amplitude (total  $\leq$  1Vpd) at the output of the RX - AGC amplifier (i.e: before the ADC) for the case of minimal AGC setting.

The following tables 8 and 9 list the RX path intermodulation distortion (as S/IM3 ratio) in downstream and upstream bandwidth.

## Table 8. Linearity of ATU-R RX

| f1 (0.5Vpd)       | 300kHz                                                                   | 500kHz                             | 700kHz                             |

|-------------------|--------------------------------------------------------------------------|------------------------------------|------------------------------------|

| f2 (0.5Vpd)       | 200kHz                                                                   | 400kHz                             | 600kHz                             |

| S/IM3 (AGC = 0dB) | 59.5dB @ 100kHz<br>53.5dB @ 400kHz<br>43.5dB @ 700kHz<br>42.5dB @ 800kHz | 59.5dB @ 300kHz<br>48.0dB @ 600kHz | 48.0dB @ 500kHz<br>42.5dB @ 800kHz |

<u>لرکم</u>

8/22

### Table 9. Linearity of ATU-C RX

| f1 (0.5Vpd)           f2 (0.5Vpd)           S/IM3 (AGC = 20 dB)         2f2 - f1           2f1 - f2 | 80kHz<br>70kHz<br>56.5dB @ 60kHz<br>56.5dB @ 90kHz |

|-----------------------------------------------------------------------------------------------------|----------------------------------------------------|

|-----------------------------------------------------------------------------------------------------|----------------------------------------------------|

## Table 10. RX Filter to A/D Interface

| RX filter to A/D maximal level: | 1Vpd = full scale of A/D |

|---------------------------------|--------------------------|

|---------------------------------|--------------------------|

## Table 11. A/D Convertors (A pipeline architecture is used for A/D convertors).

| Numbers of bits:                        | 12bits                                 |  |  |  |  |

|-----------------------------------------|----------------------------------------|--|--|--|--|

| Minimum resolution of the A/D convertor | 11bits                                 |  |  |  |  |

| Linearity error of the A/D convertor    | <1LSB (out of 12bits)                  |  |  |  |  |

| Full scale input range:                 | 1 Vpdif ±5%                            |  |  |  |  |

| Sampling rate:                          | 8.832MHz (or 4.416MHz in OSR = 2 mode) |  |  |  |  |

| Maximum attenuation at 1.1MHz:          | <0.5dB without in-band ripple          |  |  |  |  |

| Maximum group delay:                    | <3µs                                   |  |  |  |  |

| Maximum group delay distortion:         | <1µs                                   |  |  |  |  |

## **Power Supply Rejection**

The noise on the power supplies for the RX  $\,$  path must be lower than the following: <50mVrms in band white noise for any AVDD.

In this case, PSR (power supply rejection) of STLC60134SRX path is lower than -43dB.

## TX PATH

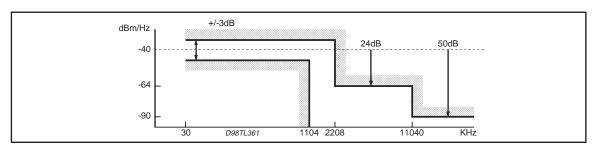

## **Transmitter Spectral Response**

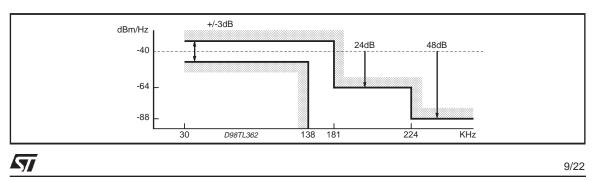

The two figures below show the ANSI spectral response mask for ATU-C and ATU-R transmitters

## Figure 8. ATU-C TX spectral response mask

Figure 9. ATU-R TX spectral response mask

#### Table 12. AGC of TX Path (from filter output to TXP and TXN).

| Output noise                     | 25mVHz <sup>-1/2</sup> |

|----------------------------------|------------------------|

| Input level (nominal)            | 1Vpd                   |

| Output level nominal, full-scale | 1.5Vpd                 |

| Maximum Output Load              | > 500Ω; <10pF          |

| AGC range:                       | -15dBdB                |

| AGC step:                        | 1dB                    |

| Gain and step accuracy           | ±0.3dB                 |

Minimum code (0000) stands for AGC = -15dB and maximum (1111 - MSB left) for AGC = 0dB (See Tx setting, Table22).

#### **TX Pre-driver Capability**

The pre-driver drives an external line power amplifier which transmits the required power to the line.

## Table 13. TX Pre-driver

| TX drive level to the external line driver for max. AGC setting |                                                                                        | 1.5 Vpdif        |

|-----------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------|

| External line driver input impedance:                           | resistive capacitive                                                                   | > 500Ω<br>< 30pF |

| Pre-driver characteristics:                                     |                                                                                        |                  |

| closed loop gain:                                               | -15dB0dB with step = 1dB                                                               |                  |

| ooutput impedance:                                              |                                                                                        |                  |

| output offset voltage (0dB)                                     | < 10mV                                                                                 |                  |

| input noise voltage (0dB)                                       | < 20nVHz <sup>-1/2</sup> @ f > 250kΩ<br>< 50nVHz <sup>-1/2</sup> @ 34.5K < f<br><138kΩ |                  |

| output common mode voltage:                                     | 1.6V < Vcm < 1.7V                                                                      |                  |

## **TX Filter**

The TX filters act not only to suppress the DMT sidebands but also as smoothing filters on the D/A convertor's output to suppress the image spectrum. For this reason they must be realized in a continuous time approach.

#### **ATU-R TX Filter**

The purpose of this filter is to remove out-of-band noise of the ATU-R TX path echoed to the ATU-R RX path. In order to meet the transmitter spectral response, an additional filtering must be (digitally) performed. The integrated filter has the following characteristics:

#### Table 14. Integrated SC Filter Characteristics

| Description                                                                                              | Value/Unit                                                                                                                                       |  |  |  |  |

|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Input referred noise                                                                                     | 100nVHz <sup>-1/2</sup>                                                                                                                          |  |  |  |  |

| Max. input level                                                                                         | 1Vpd                                                                                                                                             |  |  |  |  |

| Max. output level                                                                                        | 1Vpd                                                                                                                                             |  |  |  |  |

| Туре                                                                                                     | 4th order chebytchef                                                                                                                             |  |  |  |  |

| Frequency band                                                                                           | 138kHz (0% setting see below)                                                                                                                    |  |  |  |  |

| Frequency tuning                                                                                         | -25% -> +25%                                                                                                                                     |  |  |  |  |

| Max. in-band ripple                                                                                      | 1dB                                                                                                                                              |  |  |  |  |

| Matlab Model<br>Default cut-off frequency @ -3dB<br>Actual cut-off @ -3dB<br>SC Freq. selection register | $ [B,A] = cheby1 (4,0.5,W0,'s') \ \{ripple = 0.5\} \\ F0 = 151.8kHz \\ W0 = 2^*pi^*F0/((17+n)/16) \\ n = -4,,3 \\ see (AFE settings, Table 22) $ |  |  |  |  |

#### Table 15. Phase characteristics

| Description                            | Value/Unit                   |

|----------------------------------------|------------------------------|

| Total TX filter group delay            | <50µs @ 34.5kHz < f < 138kHz |

| Total TX filter group delay distortion | <20µs @ 34.5kHz < f < 138kHz |

Note: The total ATU-R TX path (including DAC) group delay distortion is 16µs (i.e. = 15µs + 1µs of DAC)

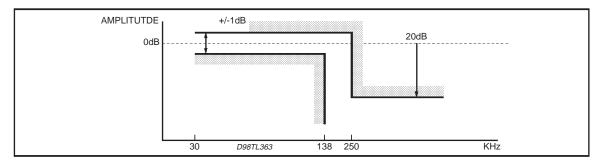

### Figure 10. SC Filter Mask for ATU-CRX and ATU-R TX

#### Table 16. D/A Convertor (A current steering architecture is used).

| Description                              | Value/Unit                                |  |  |  |

|------------------------------------------|-------------------------------------------|--|--|--|

| Numbers of bits:                         | 12bits                                    |  |  |  |

| Minimum resolution of the D/A convertors | 11bits                                    |  |  |  |

| Linearity error of the A/D convertor     | <1LSB (out of 12bits)                     |  |  |  |

| Full scale input range:                  | 1 Vpdif ±5%                               |  |  |  |

| Sampling rate:                           | 8.832MHz (or 4.416MHz in compatible mode) |  |  |  |

| Maximum group delay:                     | <3µs                                      |  |  |  |

| Maximum group delay distortion:          | <1µs                                      |  |  |  |

### Linearity of ATU-C TX

Linearity of the TX is defined by the IM3 product of two sinusoidal signals with frequencies f1 and f2 and each with 0.5Vpd amplitude (total  $\leq$  1Vpd) at the output of the pre-driver for the case of a total AGC = 0dB.

#### Table 17. Linearity of ATU-C TX

| f1 (0.5Vpd)       | 300kHz                                                                   | 500kHz                             | 700kHz                             |  |  |

|-------------------|--------------------------------------------------------------------------|------------------------------------|------------------------------------|--|--|

| f2 (0.5Vpd)       | 200kHz                                                                   | 400kHz                             | 600kHz                             |  |  |

| S/IM3 (AGC = 0dB) | 59.5dB @ 100kHz<br>53.5dB @ 400kHz<br>43.5dB @ 700kHz<br>42.5dB @ 800kHz | 59.5dB @ 300kHz<br>48.0dB @ 600kHz | 48.0dB @ 500kHz<br>42.5dB @ 800kHz |  |  |

57

### Linearity of ATU-R TX Table 18. Linearity of ATU-R TX

| f1 (0.5Vpd)        | 80kHz                   |

|--------------------|-------------------------|

| f2 (0.5Vpd)        | 70kHz                   |

| S/IM3 (AGC = 0 dB) | 59.5dB (@ 60KHz, 90KHz) |

#### TX IDLE CHANNEL NOISE

#### ATU-C TX idle channel noise

The idle channel noise specifications correspond with 11bit resolution of the complete TX-path. ATU-C TX idle channel output noise on TX.

#### Table 19. ATU-C TX idle channel noise

| For max AGC setting (0dB)                                                                                                                      |  |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| In-band noise         500nVHz <sup>-1/2</sup> @ 138kHz -1.104MHz           Out-of-band noise         500nVHz <sup>-1/2</sup> @ 34.5kHz -138kHz |  |  |  |  |  |  |  |  |

| For min AGC setting (=-15dB)                                                                                                                   |  |  |  |  |  |  |  |  |

| In-band noise 80nVHz <sup>-1/2</sup> @ 138kHz -1.104MHz                                                                                        |  |  |  |  |  |  |  |  |

## ATU-R TX idle channel noise

ATU-R TX idle channel output noise on TXP, TXN Table 20. ATU-R TX idle channel noise

| For max AGC setting (0dB)                             |                                                                               |                                                     |  |  |  |  |  |  |  |

|-------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------|--|--|--|--|--|--|--|

| In-band noise<br>Out-of-band noise                    | 1.6μVHz <sup>-1/2</sup><br>1.6μVHz <sup>-1/2</sup><br>150nVHz <sup>-1/2</sup> | @ 34.5kHz -138kHz<br>@ 138kHz<br>@ 250kHz -1.104MHz |  |  |  |  |  |  |  |

| For min AGC setting (=-15dB)                          |                                                                               |                                                     |  |  |  |  |  |  |  |

| In-band noise 500nVHz <sup>-1/2</sup> @ 34kHz -138kHz |                                                                               |                                                     |  |  |  |  |  |  |  |

#### **Power Supply Rejection**

The noise on the power supplies for the TX-path must be lower than the following:

- < 50mVrms in-band white noise for AVDD.

- < 15mVrms in-band white noise for Pre-driver AVDD.

#### VCXO

A voltage controlled crystal oscillator driver is integrated in STLC60134S. The nominal frequency is 35.328MHz. The quartz crystal is connected between the pins XTALI and XTALO. The principle of the VCXO control is shown in figure 11.

The information coming from the digital processor via the CTRLIN path is used to drive an 8-bit DAC which generates a control current. This current is externally converted and filtered to generate the required control voltage (range:-15V to 0.5V) for the varicap. The VCXO circuit characteristics are given in Table 21.

#### Table 21. VCXO circuit Characteristics

| Symbol | Parameter                   | Min.   | Nominal   | Max.   | Note                         |

|--------|-----------------------------|--------|-----------|--------|------------------------------|

| fabs   | Absolute frequency accuracy | -15ppm | 35.328MHz | +15ppm |                              |

| frange | Frequency Tuning Range      |        | ±50ppm    |        |                              |

| lo     | VCXO Output Current         |        | 100μΑ     |        | Rref = 16.5kΩ<br>AVDD = 3.3V |

| li     | Reference Input Current     | 100µA  |           | 1mA    | AVDD = 3.3V                  |

N.B: frequency tuning range is proportional to the crystal dynamic capacitance Cm.

#### Figure 11. Principle of VCXO control

The tuning must be monotonic with 8-bit resolution with the worst-case tuning step of <2ppm/LSB (8-bit). The time constant of the tuning must be variable from 5s to 10s through an external capacitor Cs (R =  $1M\Omega \pm 30\%$ ). This determines the speed of the VCXO in normal operation (slow speed in "show time") with filtered VCXO. For faster tracking, the previous filter is not used and the speed depends on CtRt.

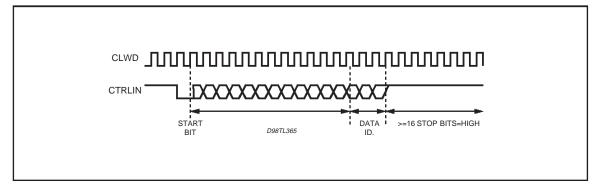

## DIGITAL INTERFACE

#### **Control Interface**

The digital setting codes for the STLC60134S configuration are sent over a serial line (CTRLIN) using the word clock (CLWD).

The data burst is composed of 16 bits from which the first bit is used as start bit ('0'), the three LSBs being used to identify the data contained in the 12 remaining bits. Test related data are overruled by the normal settings if the TEST pin is low.

Table 22. Control Interface Bit Mapping

| M<br>S<br>B |             |             |             |             |             |        |        |        |        |        |        | L<br>S<br>B | RX SETTINGS |        |        |                                                            |

|-------------|-------------|-------------|-------------|-------------|-------------|--------|--------|--------|--------|--------|--------|-------------|-------------|--------|--------|------------------------------------------------------------|

| b<br>1<br>5 | b<br>1<br>4 | b<br>1<br>3 | b<br>1<br>2 | b<br>1<br>1 | b<br>1<br>0 | b<br>9 | b<br>8 | b<br>7 | b<br>6 | b<br>5 | b<br>4 | b<br>3      | b<br>2      | b<br>1 | b<br>0 |                                                            |

| 0           | х           |             |             |             |             |        |        |        |        |        |        |             | 0           | 0      | 0      | External Gain Control GC1 (init = 0)                       |

| 0           |             | х           |             |             |             |        |        |        |        |        |        |             | 0           | 0      | 0      | External Gain Control GC0 (init = 0)                       |

| 0           |             |             | 0           |             |             |        |        |        |        |        |        |             | 0           | 0      | 0      | Rx input selected = RXIN0, RXIP0 (init)                    |

| 0           |             |             | 1           |             |             |        |        |        |        |        |        |             | 0           | 0      | 0      | Rx input selected = RXIN1, RXIP1                           |

| 0           |             |             |             | 0           | 0           | 0      | 0      | 0      |        |        |        |             | 0           | 0      | 0      | AGC RX Gain setting 0dB (init)                             |

| 0           |             |             |             | 0           | 0           | 0      | 0      | 1      |        |        |        |             | 0           | 0      | 0      | AGC RX Gain setting 1dB                                    |

| 0           |             |             |             | х           | х           | х      | х      | х      |        |        |        |             | 0           | 0      | 0      | AGC RX Gain setting XdB                                    |

| 0           |             |             |             | 1           | 1           | 1      | 1      | 1      |        |        |        |             | 0           | 0      | 0      | AGC RX Gain setting 31dB                                   |

| 0           |             |             |             |             |             |        |        |        | 0      | 0      |        |             | 0           | 0      | 0      | Normal mode Filter selection see LTNT pin (init)           |

| 0           |             |             |             |             |             |        |        |        | 0      | 1      |        |             | 0           | 0      | 0      | In ATU-C conf, force HC2 for RX path, TX grounded          |

| 0           |             |             |             |             |             |        |        |        | 1      | 0      |        |             | 0           | 0      | 0      | In ATU-C conf, force HC1 for RX path                       |

| 0           |             |             |             |             |             |        |        |        | 1      | 1      |        |             | 0           | 0      | 0      | Normal mode Filter selection see LTNT pin                  |

| b<br>1<br>5 | b<br>1<br>4 | b<br>1<br>3 | b<br>1<br>2 | b<br>1<br>1 | b<br>1<br>0 | b<br>9 | b<br>8 | b<br>7 | b<br>6 | b<br>5 | b<br>4 | b<br>3      | b<br>2      | b<br>1 | b<br>0 | TX SETTINGS                                                |

| 0           | 0           | 0           | 0           | 0           |             |        |        |        |        |        |        |             | 0           | 0      | 1      | Transmit TX - AGC setting -15dB (init)                     |

| 0           | 0           | 0           | 0           | 1           |             |        |        |        |        |        |        |             | 0           | 0      | 1      | Transmit TX - AGC setting -14dB                            |

| 0           | х           | х           | х           | х           |             |        |        |        |        |        |        |             | 0           | 0      | 1      | Transmit TX - AGC setting (X - 15) dB                      |

| 0           | 1           | 1           | 1           | 1           |             |        |        |        |        |        |        |             | 0           | 0      | 1      | Transmit TX - AGC setting 0dB                              |

| 0           |             |             |             |             | 0           | 0      | 0      | 0      |        |        |        |             | 0           | 0      | 1      | Not used (init)                                            |

| 0           |             |             |             |             | 0           | 0      | 0      | 0      |        |        |        |             | 0           | 0      | 1      | Not used (init)                                            |

| 0           |             |             |             |             | 0           | 0      | 0      | 0      |        |        |        |             | 0           | 0      | 1      | Not used (init)                                            |

| 0           |             |             |             |             | 0           | 0      | 0      | 0      |        |        |        |             | 0           | 0      | 1      | Not used (init)                                            |

| 0           |             |             |             |             |             |        |        |        | х      | х      | х      |             | 0           | 0      | 1      | General Purpose Output (GPO) setting (init = 000)          |

| b<br>1<br>5 | b<br>1<br>4 | b<br>1<br>3 | b<br>1<br>2 | b<br>1<br>1 | b<br>1<br>0 | b<br>9 | b<br>8 | b<br>7 | b<br>6 | b<br>5 | b<br>4 | b<br>3      | b<br>2      | b<br>1 | b<br>0 | AFE SETTINGS                                               |

| 0           | 0           |             |             |             |             |        |        |        |        |        |        |             | 0           | 1      | 0      | Normal Mode (Digital path) (init)                          |

| 0           | 1           |             |             |             |             |        |        |        |        |        |        |             | 0           | 1      | 0      | Digital Loopback (digital TX to digital RX - DAC not used) |

| 0           |             | 0           |             |             |             |        |        |        |        |        |        |             | 0           | 1      | 0      | Normal Mode (Analog path)                                  |

| 0           |             | 1           |             |             |             |        |        |        |        |        |        |             | 0           | 1      | 0      | Analog loopback (RXi to TXi - ADC not used) 1) (init)      |

| 0           |             |             | 0           |             |             |        |        |        |        |        |        |             | 0           | 1      | 0      | VCO DAC disabled                                           |

| 0           |             |             | 1           |             |             |        |        |        |        |        |        |             | 0           | 1      | 0      | VCO DAC enabled (init)                                     |

| 0           |             |             |             | 0           |             |        |        |        |        |        |        |             | 0           | 1      | 0      | HC filter enabled (init)                                   |

| 0           |             |             |             | 1           |             |        |        |        |        |        |        |             | 0           | 1      | 0      | HC filter enabled                                          |

1) After initialization, this bit has to be cleared (0) to make the device properly operate.

| b<br>1<br>5 | b<br>1<br>4 | b<br>1<br>3 | b<br>1<br>2 | b<br>1<br>1 | b<br>1<br>0 | b<br>9 | b<br>8 | b<br>7 | b<br>6 | b<br>5 | b<br>4 | b<br>3 | b<br>2 | b<br>1   | b<br>0 | AFE SETTINGS                                  |

|-------------|-------------|-------------|-------------|-------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|----------|--------|-----------------------------------------------|

| 0           |             |             |             |             | 0           |        |        |        |        |        |        |        | 0      | 1        | 0      | OSR set to 4 (init)                           |

| 0           |             |             |             |             | 1           |        |        |        |        |        |        |        | 0      | 1        | 0      | OSR set to 2                                  |

| 0           |             |             |             |             |             | 1      | 1      | 1      |        |        |        |        | 0      | 1        | 0      | SC freq. selection: Fc = 138kHz (init) (*)    |

| 0           |             |             |             |             |             | 0      | 1      | 1      |        |        |        |        | 0      | 1        | 0      | SC freq. selection: Fc ~ 110kHz (*)           |

| 0           |             |             |             |             |             | 1      | 0      | 1      |        |        |        |        | 0      | 1        | 0      | SC freq. selection: Fc ~ 170kHz (*)           |

| 0           |             |             |             |             |             |        |        |        | 1      | 0      | 0      |        | 0      | 1        | 0      | HC freq. selection: Fc = 1.104MHz (init) (*)  |

| 0           |             |             |             |             |             |        |        |        | 0      | 1      | 1      |        | 0      | 1        | 0      | HC freq. selection: Fc ~ 768kHz (*)           |

| 0           |             |             |             |             |             |        |        |        |        |        |        | 0      | 0      | 1        | 0      | VCXO output NOT filtered ("show-time") (init) |

| 0           |             |             |             |             |             |        |        |        |        |        |        | 1      | 0      | 1        | 0      | VCXO output filtered                          |

| b<br>1<br>5 | b<br>1<br>4 | b<br>1<br>3 | b<br>1<br>2 | b<br>1<br>1 | b<br>1<br>0 | b<br>9 | b<br>8 | b<br>7 | b<br>6 | b<br>5 | b<br>4 | b<br>3 | b<br>2 | b<br>  1 | b<br>0 | VCO DAC VALUE SETTINGS                        |

| 0           | 0           | 0           | 0           | 0           | 0           | 0      | 0      | 0      |        |        |        |        | 0      | 1        | 1      | VCO DAC CURRENT value @ MINIMUM               |

| 0           | х           | х           | х           | х           | х           | х      | х      | х      |        |        |        |        | 0      | 1        | 1      | VCO DAC CURRENT value @ X                     |

| 0           | 1           | 1           | 1           | 1           | 1           | 1      | 1      | 1      |        |        |        |        | 0      | 1        | 1      | VCO DAC CURRENT value @ MAXIMUM               |

| b<br>1<br>5 | b<br>1<br>4 | b<br>1<br>3 | b<br>1<br>2 | b<br>1<br>1 | b<br>1<br>0 | b<br>9 | b<br>8 | b<br>7 | b<br>6 | b<br>5 | b<br>4 | b<br>3 | b<br>2 | b<br>1   | b<br>0 | POWER DOWN ANALOG BLOCK SETTINGS              |

| 0           | 0           |             |             |             |             |        |        |        |        |        |        |        | 1      | 0        | 0      | TXD Active (init)                             |

| 0           | 1           |             |             |             |             |        |        |        |        |        |        |        | 1      | 0        | 0      | TXD in powerdown                              |

| 0           |             | 0           |             |             |             |        |        |        |        |        |        |        | 1      | 0        | 0      | N.U. (init)                                   |

| 0           |             | 1           |             |             |             |        |        |        |        |        |        |        | 1      | 0        | 0      | N.U.                                          |

| 0           |             |             | 0           |             |             |        |        |        |        |        |        |        | 1      | 0        | 0      | ADC Active (init)                             |

| 0           |             |             | 1           |             |             |        |        |        |        |        |        |        | 1      | 0        | 0      | ADC in powerdown                              |

| 0           |             |             |             | 0           |             |        |        |        |        |        |        |        | 1      | 0        | 0      | HFC2 Active (init)                            |

| 0           |             |             |             | 1           |             |        |        |        |        |        |        |        | 1      | 0        | 0      | HFC2 in powerdown                             |

| 0           |             |             |             |             | 0           |        |        |        |        |        |        |        | 1      | 0        | 0      | HFC1 Active (init)                            |

| 0           |             |             |             |             | 1           |        |        |        |        |        |        |        | 1      | 0        | 0      | HFC1 in powerdown                             |

| 0           |             |             |             |             |             | 0      |        |        |        |        |        |        | 1      | 0        | 0      | SCF2 Active (init)                            |

| 0           |             |             |             |             |             | 1      |        |        |        |        |        |        | 1      | 0        | 0      | SCF2 in powerdown                             |

| 0           |             |             |             |             |             |        | 0      |        |        |        |        |        | 1      | 0        | 0      | SCF1 Active (init)                            |

| 0           |             |             |             |             |             |        | 1      |        |        |        |        |        | 1      | 0        | 0      | SCF1 in powerdown                             |

| 0           |             |             |             |             |             |        |        | 0      |        |        |        |        | 1      | 0        | 0      | LNA Active (init)                             |

| 0           |             |             |             |             |             |        |        | 1      |        |        |        |        | 1      | 0        | 0      | LNA in powerdown                              |

| 0           |             |             |             |             |             |        |        |        | 0      |        |        |        | 1      | 0        | 0      | DAC Active (init)                             |

| 0           |             |             |             |             |             |        |        |        | 1      |        |        |        | 1      | 0        | 0      | DAC in powerdown                              |

| 0           |             |             |             |             |             |        |        |        |        | 0      |        |        | 1      | 0        | 0      | DACE Active (init)                            |

| 0           |             |             |             |             |             |        |        |        |        | 1      |        |        | 1      | 0        | 0      | DACE in powerdown                             |

| 0           |             |             |             |             |             |        |        |        |        |        | 0      |        | 1      | 0        | 0      | VCODAC Active (init)                          |

| 0           |             |             |             |             |             |        |        |        |        |        | 1      |        | 1      | 0        | 0      |                                               |

| 0           |             |             |             |             |             |        |        |        |        |        |        | 0      | 1      | 0        | 0      | XTAL Active (init)                            |

| 0           |             |             |             |             |             |        |        |        |        |        |        | 1      | 1      | 0        | 0      | XTAL in powerdown                             |

| b<br>1<br>5 | b<br>1<br>4 | b<br>1<br>3 | b<br>1<br>2 | b<br>1<br>1 | b<br>1<br>0 | b<br>9 | b<br>8 | b<br>7 | b<br>6 | b<br>5 | b<br>4 | b<br>3 | b<br>2 | b<br>1   | b<br>0 | RESERVED                                      |

| 0           | х           | х           | х           | х           | х           | х      | х      | х      | х      | х      | х      | х      | 1      | 0        | 1      | RESERVED                                      |

| 0           | х           | х           | х           | х           | х           | х      | х      | х      | х      | х      | х      | х      | 1      | 1        | 0      | RESERVED                                      |

| 0           | х           | х           | х           | х           | х           | х      | х      | х      | х      | х      | х      | х      | 1      | 1        | 1      | RESERVED                                      |

## Table 22. Control Interface Bit Mapping (continued)

(\*) For each filter, 8 possible frequency values (see table 6 and table 14). Notation is 2's complement range from -4 = 100b +3 = 011b. Fc is the frequency band (-1dB)

## STLC60134S

#### **Control Interface Timing**

The word clock (CLWD) is used to sample at negative going edge the control information. The start bit b15 is transmitted first followed by bits b[14:0] and at least 16 stop bits need to be provided to validate the data.

#### Figure 12. Control Interface.

Data set-up and hold time versus falling edge CLWD must be greater than 10nsec.

#### **Receive / Transmit Interface**

**RECEIVE / TRANSMIT PROTOCOL**

The digital interface is based on 4 x 8.832MHz (35.328MHz) data lines in the following manner:

If OSR = 2 (OSR bit set to 1) is selected, CLKNIB is used as nibble clock (17.664MHz, disabled in normal mode), and all the RXi, TXi, CLKWD periods are twice as long as in normal mode. This ensures a compatibility with lower speed products.

## **TX Signal Dynamic**

The dynamic of data signal for both TX DACs is 12 bits extracted from the available signed 16 bit representation coming from the digital processor.

The maximal positive number is  $2^{14}$ -1, the most negative number is  $-2^{14}$ , the 3 LSBs are filled with '0'. Any signal exceeding these limits is clamped to the maximum value.

|--|

| BIT MAP/NIBBLE | N0                    | N1         | N2         | N3          |

|----------------|-----------------------|------------|------------|-------------|

| TXD0           | not used              | data bit 1 | data bit 5 | data bit 9  |

| TXD1           | not used              | data bit 2 | data bit 6 | data bit 10 |

| TXD2           | not used              | data bit 3 | data bit 7 | data SIGN   |

| TXD3           | d0 = data bit 0 (LSB) | data bit 4 | data bit 8 | data SIGN   |

#### Table 24. TX bit map

| _ |      | Ν    | 3   |    |    | N  | 2  |    |    | Ν  | 1  |    |    | N    | 10   |      |

|---|------|------|-----|----|----|----|----|----|----|----|----|----|----|------|------|------|

|   | sign | sign | d10 | d9 | d8 | d7 | d6 | d5 | d4 | d3 | d2 | d1 | d0 | n.u. | n.u. | n.u. |

The two sign bits must be identical.

16/22

#### **RX Signal Dynamic**

The dynamic of the signal from the ADC is limited to 13bits. Those bits are converted to a signed (2's complement) representation with a maximal positive number of  $2^{14}$  -1 and a most negative number - $2^{14}$ . The 2 LSBs are filled with '0'.

#### Table 25.

| BIT MAP/NIBBLE | N0                    | N1         | N2         | N3          |

|----------------|-----------------------|------------|------------|-------------|

| RXD0           | 0                     | data bit 2 | data bit 6 | data bit 10 |

| RXD1           | 0                     | data bit 3 | data bit 7 | data bit 11 |

| RXD2           | d0 = data bit 0 (LSB) | data bit 4 | data bit 8 | data SIGN   |

| RXD3           | data bit 1            | data bit 5 | data bit 9 | data SIGN   |

#### Table 26. RX bit map

|      | N    | 3   |     |    | N  | 2  |    |    | Ν  | 1  |    |    | N  | 0 |   |

|------|------|-----|-----|----|----|----|----|----|----|----|----|----|----|---|---|

| sign | sign | d11 | d10 | d9 | d8 | d7 | d6 | d5 | d4 | d3 | d2 | d1 | d0 | 0 | 0 |

The two sign bits must be identical.

#### Figure 13. TX/ RX Digital Interface Timing

#### Receive / Transmit interface timing

The interface is a triple (RX, TX) nibble - serial interface running at 8.8MHz sampling (normal mode). The data are represented in 16bits format, and transferred in groups of 4 bits (nibbles). The LSBs are transferred first. The STLC60134S generates a nibble clock (CLKM master clock in normal mode, CLKNIB in OSR = 2 mode) and word signals shared by the three interfaces.

Data is transmitted on the rising edge of the master clock (CLKM/CLKNIB) and sampled on the falling edge of CLKM/CLKNIB. This holds for the data stream from STLC60134S and from the digital processor.

Data, CLWD setup and hold times are 5ns with reference to the falling edge of CLKM/CLKNIB. (not floating).

## STLC60134S

Data is transmitted on the rising edge of the master clock (CLKM/CLKNIB) and sampled on the low going edge of CLKM/CLKNIB. This holds for the data stream from STLC60134S and from the digital processor. Data, CLWD setup and hold times are 5ns with reference to the falling edge of CLKM/CLKNIB. (not floating).

#### **POWER DOWN**

When pin Pdown = "1", the chip is set in power down mode. As the Pdown signal is synchronously sampled, minimum duration is 2 periods of the 35MHz clock. In this mode all analog functional blocks are deactivated except: preamplifiers (TX), clock circuits for output clock CLKM.  $P_{down}$  will not affect the digital part of the chip. Anyway, after a Pdown transition, the digital part status, is updated after 3 clock periods (worst case)

The chip is activated when Pdown = "0".

In power down mode the following conditions hold:

- Output voltages at TXP/TXN = AGND

- Preamplifier is on with maximum gain setting (0dB), (digital gain setting coefficients are overruled)

- The XTAL output clock on pin CLKM keeps running.

- All digital setting are retained.

- Digital output on pins RXDx don't care (not floating).

- In power-down mode the power consumption is 100mW.

Following external conditions are added:

- Clock pin CLW is running.

- CTRLIN signals can still be allowed.

- AGND remains at AVDD/2 (circuit is powered up)

- Input signal at TXDx inputs are not strobed.

The Pdown signal controls asynchronously the power-down of each analog module:

- After a few  $\mu s$  the analog channel is functional

- After about 100ms the analog channel delivers full performance

#### **RESET FUNCTION**

The reset function is implied when the RESETN pin is at a low voltage input level. In this condition, the reset function can be easily used for power up reset conditions.

### **Detailed Description**

During reset: (reset is asynchronous, tenths of ns are enough to put the IC in reset)

All clock outputs are deactivated and put to logical "1" (except for the XTAL and master clock CLKM)

After reset: (4 clock periods after reset transition, as worst case)

- OSR = 4

- All analog gains (RX, TX) are set to minimum value

- Nominal filter frequency bands (138kHz, 1.104Hz)

- LNA input = "11" (max. attenuation)

- VCO dac disabled

- Depending of the LTNT pin value the following configuration is chosen:

'0' (ATU-R)

```

RX:

LNA -> HC2 -> ADC

TX:

DAC -> SC2 -> TX

'1' (ATU-C)

RX:

LNA -> SC2 -> ADC

TX:

DAC -> HC2 -> TX

```

18/22

**\_**//

Digital outputs are placed in don't care condition (non-floating).

**N.B.** If a Xtal oscillator is used, the RESET must be released at last  $10\mu s$  after power-on, to ensure a correct duty cycle for the clk35 clock signal.

## ELECTRICAL RATINGS AND CHARACTERISTICS Table 27. Absolute Maximum Ratings

| Symbol            | Parameter                                       | Min   | Мах                  | Unit |

|-------------------|-------------------------------------------------|-------|----------------------|------|

| Vdd               | Any VDD Supply Voltage, related to substrate    | - 0.5 | 5                    | V    |

| Vin               | Voltage at any input pin                        | -0.5  | V <sub>DD</sub> +0.5 | V    |

| T <sub>stg</sub>  | Storage Temperature                             | -40   | 125                  | °C   |

| ΤL                | Lead Temperature (10 second soldering)          |       | 300                  | °C   |

| ILU               | Latch - up current @80°C                        | 100   |                      | mA   |

| I <sub>AVDD</sub> | Analog Supply Current @ 3.6V - normal operation |       | 165                  | mA   |

| I <sub>AVDD</sub> | Analog Supply Current @ 3.6V - power down       |       | 30                   | mA   |

| I <sub>DVDD</sub> | Analog Supply Current @ 3.6V - normal operation |       | 56                   | mA   |

| I <sub>DVDD</sub> | Analog Supply Current @ 3.6V - power down       |       | 50                   | mA   |

#### Table 28. Thermal Data

| Symbol    | Parameter                    | Value | Unit |

|-----------|------------------------------|-------|------|

| Rth j-amb | Thermal and Junction ambient | 50    | °C/W |

#### Table 29. Operating Conditions

(Unless specified, the characteristic limits of 'Static Characteristics' in this document apply over an  $T_{op} = -40$  to 80 °C; VDD within the range 3 to 3.6V ref. to substrate.

| Symbol    | Parameter                                 | Min | Мах | Unit |

|-----------|-------------------------------------------|-----|-----|------|

| AVDD      | AVDD Supply Voltage, related to substrate | 3.0 | 3.6 | V    |

| DVDD      | DVDD Supply Voltage, related to substrate | 2.7 | 3.6 | V    |

| Vin /Vout | Voltage at any input and output pin       | 0   | Vdd | V    |

| Pd        | Power Dissipation                         | 0.4 | 0.6 | W    |

| Tamb      | Ambient Temperature                       | -40 | 80  | °C   |

| Tj        | Junction Temperature                      | -40 | 110 | °C   |

## STATIC CHARACTERISTICS

## Table 30. Digital Inputs

Schmitt-trigger inputs: TXi, CTRLIN, PDOWN, LTNT, RESETN, TEST

| Symbol           | Parameter                | Test Condition | Min.       | Тур. | Max.       | Unit |

|------------------|--------------------------|----------------|------------|------|------------|------|

| VIL              | Low Level Input Voltage  |                |            |      | 0.3 · DVDD | V    |

| VIH              | High Level Input Voltage |                | 0.7 · DVDD |      |            | V    |

| V <sub>H</sub>   | Hysteresis               |                | 1.0        |      | 1.3        | V    |

| C <sub>imp</sub> | Input Capacitance        |                |            |      | 3          | pF   |

## Table 31. Digital Outputs

Hard Driven Outputs: RXi

| Symbol            | Parameter                 | Test Condition | Min.        | Тур. | Max.        | Unit |

|-------------------|---------------------------|----------------|-------------|------|-------------|------|

| V <sub>OL</sub>   | Low Level Output Voltage  | lout = -4mA    |             |      | 0.15 · DVDD | V    |

| V <sub>OH</sub>   | High Level Output Voltage | lout = 4mA     | 0.85 · DVDD |      |             | V    |

| C <sub>load</sub> | Load Capacitance          |                |             |      | 30          | pF   |

## Clock Driver Output: CLKM, CLNIB, CLKWD

| Symbol          | Parameter                 | Test Condition          | Min.        | Тур. | Max.        | Unit |

|-----------------|---------------------------|-------------------------|-------------|------|-------------|------|

| V <sub>OL</sub> | Low Level Output Voltage  | l <sub>out</sub> = -4mA |             |      | 0.15 · DVDD | V    |

| V <sub>OH</sub> | High Level Output Voltage | l <sub>out</sub> = 4mA  | 0.85 · DVDD |      |             | V    |

| Cload           | Load Capacitance          |                         |             |      | 30          | pF   |

| DC              | Duty Cycle                |                         | 45          |      | 55          | %    |

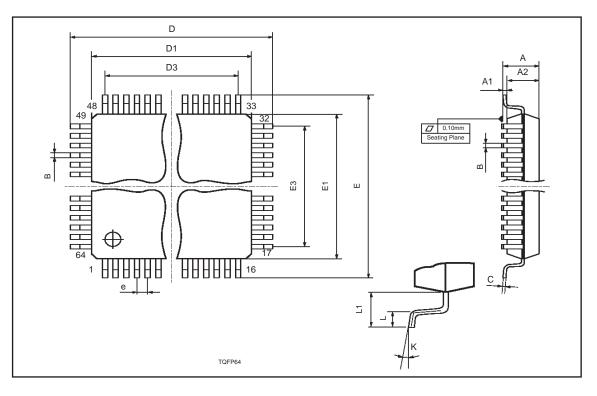

| DIM. | mm                 |       |      | inch   |        |        |

|------|--------------------|-------|------|--------|--------|--------|

|      | MIN.               | TYP.  | MAX. | MIN.   | TYP.   | MAX.   |

| А    |                    |       | 1.60 |        |        | 0.063  |

| A1   | 0.05               |       | 0.15 | 0.002  |        | 0.006  |

| A2   | 1.35               | 1.40  | 1.45 | 0.053  | 0.055  | 0.057  |

| В    | 0.18               | 0.23  | 0.28 | 0.007  | 0.009  | 0.011  |

| С    | 0.12               | 0.16  | 0.20 | 0.0047 | 0.0063 | 0.0079 |

| D    |                    | 12.00 |      |        | 0.472  |        |

| D1   |                    | 10.00 |      |        | 0.394  |        |

| D3   |                    | 7.50  |      |        | 0.295  |        |

| е    |                    | 0.50  |      |        | 0.0197 |        |

| E    |                    | 12.00 |      |        | 0.472  |        |

| E1   |                    | 10.00 |      |        | 0.394  |        |

| E3   |                    | 7.50  |      |        | 0.295  |        |

| L    | 0.40               | 0.60  | 0.75 | 0.0157 | 0.0236 | 0.0295 |

| L1   |                    | 1.00  |      |        | 0.0393 |        |

| к    | 0°(min.), 7°(max.) |       |      |        |        |        |

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics are are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics. The ST logo is a trademark of STMicroelectronics

Tosca<sup>™</sup> is trademark of STMicroelectronics

© 1999 STMicroelectronics and Alcatel Alsthom, Paris - Printed in Italy - All Rights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - Morocco -Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A.

http://www.st.com

<u>لرکم</u>