# **AMD-640**<sup>™</sup>

# **System Controller**

**Data Sheet**

#### **Preliminary Information**

#### © 1997 Advanced Micro Devices, Inc. All rights reserved.

Advanced Micro Devices, Inc. ("AMD") reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

The information in this publication is believed to be accurate at the time of publication, but AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication or the information contained herein, and reserves the right to make changes at any time, without notice. AMD disclaims responsibility for any consequences resulting from the use of the information included in this publication.

This publication neither states nor implies any representations or warranties of any kind, including but not limited to, any implied warranty of merchantability or fitness for a particular purpose. AMD products are not authorized for use as critical components in life support devices or systems without AMD's written approval. AMD assumes no liability whatsoever for claims associated with the sale or use (including the use of engineering samples) of AMD products except as provided in AMD's Terms and Conditions of Sale for such product.

#### **Trademarks**

AMD, the AMD logo, and combinations thereof are trademarks of Advanced Micro Devices, Inc.

AMD-640, AMD-645, K86, AMD-K5, AMD-K6, and the AMD-K6 logo are trademarks of Advanced Micro Devices, Inc.

MMX is a trademark of the Intel Corporation.

Microsoft and Windows are registered trademarks, and Windows NT is a trademark of Microsoft Corporation.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

21090C/0-June 1997

# **Contents**

| 1 | Features  |         |                                          | 1-1         |

|---|-----------|---------|------------------------------------------|-------------|

|   |           | 1.1     | Processor Interface                      | 1-1         |

|   |           | 1.2     | Integrated Cache Controller              | 1-1         |

|   |           | 1.3     | Integrated Memory Controller             | 1-2         |

|   |           | 1.4     | PCI Bus Controller                       | 1-3         |

| 2 | Overview  | 1       |                                          | <b>2-</b> 1 |

|   |           | 2.1     | System                                   | 2-1         |

|   |           | 2.2     | AMD-640 System Controller Buffers        | 2-4         |

|   |           | 2.3     | Definitions, Conventions, and References | 2-5         |

|   |           |         | 2.3.1 DataData2.3.2 Related Publications |             |

| 3 | Ordering  | Infor   | nation                                   | 3-1         |

| 4 | Signal De | scripti | ions                                     | 4-1         |

|   |           | 4.1     | Processor Interface Signals              | 4-1         |

|   |           | 4.2     | PCI Interface Signals                    | 4-5         |

|   |           | 4.3     | DRAM Interface Signals                   | 4-8         |

|   |           | 4.4     | Cache Controller Interface Signals       | . 4-10      |

|   |           | 4.5     | Clocks and Reset                         | . 4-12      |

| 5 | Functional Ope | ration |                                   | 5-1            |

|---|----------------|--------|-----------------------------------|----------------|

|   | 5.1            | Proces | ssor Interface                    | . 5-1          |

|   |                | 5.1.1  | Write Posting                     | . 5-1          |

|   |                |        | Read Buffer                       |                |

|   |                | 5.1.3  | Read-Around-Writes                | . 5-5          |

|   | 5.2            | Cache  | Controller                        | 5-5            |

|   |                | 5.2.1  | Cache Organization                | . 5-5          |

|   |                | 5.2.2  | Cache Operation                   |                |

|   |                | 5.2.3  | Write Buffers                     | 5-13           |

|   |                | 5.2.4  | Cacheable Region                  | 5-13           |

|   |                | 5.2.5  | Cache Parameters                  |                |

|   |                | 5.2.6  | Cache Snooping                    | 5-14           |

|   | 5.3            | DRAN   | A Controller                      | . <b>5-1</b> 5 |

|   |                | 5.3.1  | Mixing Memory                     | 5-16           |

|   |                |        | Error Correction Code             |                |

|   |                | 5.3.3  | DRAM Refresh                      | 5-19           |

|   |                | 5.3.4  | Shadow RAM                        | 5-21           |

|   |                | 5.3.5  | EDO DRAM                          | 5-22           |

|   |                | 5.3.6  | Synchronous DRAM                  | 5-25           |

|   | 5.4            | PCI B  | us Controller                     | . 5-30         |

|   |                | 5.4.1  | PCI-to-CPU (Read) Transactions    | 5-31           |

|   |                | 5.4.2  | CPU-to-PCI (Write) Transactions   |                |

|   |                | 5.4.3  | PCI Arbitration                   |                |

|   |                | 5.4.4  | PCI Configuration                 | 5-36           |

|   |                | 5.4.5  | PCI Transaction Examples          | 5-38           |

|   |                | 5.4.6  | PCI Accesses by Another initiator | 5-51           |

|   |                |        | PCI Fast Back to Back cycles      |                |

|   |                |        | PCI Sideband Signals              |                |

|   |                |        | Power Management                  |                |

| 6 | Initialization |        |                                   | 6-1            |

*iv* Table of Contents

| 7 | <b>Configuration R</b> | Registers                                                                                                                                                                                                                                                                                                                                                                                                                      | 7-1                                                                           |

|---|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

|   | 7.1                    | PCI Configuration Mechanism                                                                                                                                                                                                                                                                                                                                                                                                    | . 7-1                                                                         |

|   | 7.2                    | Register Overview                                                                                                                                                                                                                                                                                                                                                                                                              | . 7-3                                                                         |

|   | 7.3                    | PCI Configuration Space Registers                                                                                                                                                                                                                                                                                                                                                                                              | . 7-5                                                                         |

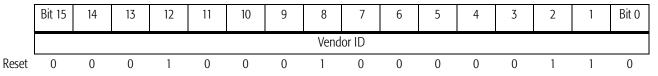

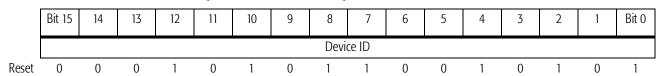

|   |                        | 7.3.1 Vendor ID (Offset 01h–00h) 7.3.2 Device ID (Offset 03h–02h) 7.3.3 Command (Offset 05h–04h) 7.3.4 Status (Offset 07h–06h) 7.3.5 Revision ID (Offset 08h) 7.3.6 Programming Interface (Offset 09h) 7.3.7 Sub Class Code (Offset 0Ah) 7.3.8 Base Class Code (Offset 0Bh) 7.3.9 Cache Line Size (Offset 0Ch) 7.3.10 Latency Timer (Offset 0Dh) 7.3.11 Header Type (Offset 0Eh) 7.3.12 Built-In Self Test (BIST) (Offset 0Fh) | . 7-5<br>. 7-6<br>. 7-7<br>. 7-8<br>. 7-9<br>. 7-9<br>. 7-9<br>. 7-10<br>7-10 |

|   | 7.4                    | Cache Control Registers                                                                                                                                                                                                                                                                                                                                                                                                        | 7-11                                                                          |

|   |                        | 7.4.1 Cache Control Register 1 (Offset 50h)                                                                                                                                                                                                                                                                                                                                                                                    | 7-12<br>7-13<br>7-14<br>7-15                                                  |

|   | 7.5                    | DRAM Control Registers                                                                                                                                                                                                                                                                                                                                                                                                         | <b>7-1</b> 6                                                                  |

|   |                        | 7.5.1 DRAM Configuration Register #1 (Offset 58h) 7.5.2 DRAM Configuration Register #2 (Offset 59h) 7.5.3 DRAM Bank 0 Ending Address (Offset 5Ah) 7.5.4 DRAM Type (Offset 60h) 7.5.5 Shadow RAM Control Register #1 (Offset 61h) 7.5.6 Shadow RAM Control Register #2 (Offset 62h) 7.5.7 Shadow RAM Control Register #3 (Offset 63h) 7.5.8 DRAM Timing (Offset 64h) 7.5.9 DRAM Control Register #1 (Offset 65h)                | 7-17 7-19 7-20 7-21 7-21 7-22 7-23                                            |

|   |                        | 7.5.10 DRAM Control Register #2 (Offset 66h)                                                                                                                                                                                                                                                                                                                                                                                   |                                                                               |

Table of Contents v

| 7.6             | 7.5.11 32-Bit DRAM Width Control Register (Offset 67h) 7.5.12 DRAM Refresh Counter (Offset 6Ah) 7.5.13 DRAM Refresh Control Register (Offset 6Bh) 7.5.14 SDRAM Control Register (Offset 6Ch) 7.5.15 DRAM Drive Strength Control Register (Offset 6Dh) 7.5.16 ECC Control Register (Offset 6Eh) 7.5.17 ECC Status Register (Offset 6Fh)  PCI Bus Control Registers  7.6.1 PCI Buffer Control Register (Offset 70h) 7.6.2 Processor-to-PCI Flow Control Register #1 (Offset 71h) 7.6.3 Processor-to-PCI Flow Control Register #2 (Offset 72h) 7.6.4 PCI Target Control Register (Offset 73h) | 7-27<br>7-28<br>7-28<br>7-29<br>7-30<br>7-31<br>7-32<br>7-33<br>7-35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | 7.6.5 PCI Initiator Control Register (Offset 74h)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7-38<br>7-39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Electrical Data |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 8.1             | Absolute Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 8-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8.2             | Operating Ranges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 8-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8.3             | DC Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 8-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8.4             | Power Dissipation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 8-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Switching Chara | acteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 9.1             | CLK Switching Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 9-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 9.2             | Valid Delay, Float, Setup, and Hold Timings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>. 9-</b> 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 9.3             | Processor Interface Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 9-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 9.4             | PCI Interface Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 9-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 9.5             | DRAM Interface Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 9-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 9.6             | L2 Cache Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 9-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 | Electrical Data  8.1  8.2  8.3  8.4  Switching Chara  9.1  9.2  9.3  9.4  9.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7.5.12 DRAM Refresh Counter (Offset 6Ah) 7.5.13 DRAM Refresh Control Register (Offset 6Bh) 7.5.14 SDRAM Control Register (Offset 6Ch) 7.5.15 DRAM Drive Strength Control Register (Offset 6Dh) 7.5.16 ECC Control Register (Offset 6Eh) 7.5.17 ECC Status Register (Offset 6Eh) 7.5.18 ECC Status Register (Offset 6Eh) 7.5.19 ECC Status Register (Offset 6Fh)  7.6 PCI Bus Control Registers  7.6.1 PCI Buffer Control Register (Offset 70h) 7.6.2 Processor-to-PCI Flow Control Register #1 (Offset 71h) 7.6.3 Processor-to-PCI Flow Control Register #2 (Offset 72h) 7.6.4 PCI Target Control Register (Offset 73h) 7.6.5 PCI Initiator Control Register (Offset 75h) 7.6.6 PCI Arbitration Control Register #1 (Offset 75h) 7.6.7 PCI Arbitration Control Register #2 (Offset 76h)  Electrical Data  8.1 Absolute Ratings 8.2 Operating Ranges 8.3 DC Characteristics 8.4 Power Dissipation  Switching Characteristics  9.1 CLK Switching Characteristics  9.2 Valid Delay, Float, Setup, and Hold Timings  9.3 Processor Interface Timing  9.4 PCI Interface Timing  9.5 DRAM Interface Timing |

vi Table of Contents

| 10 | IBIS Models      |                                      | 10-1 |

|----|------------------|--------------------------------------|------|

|    | 10.1             | Selectable Drive Strength            | 10-1 |

|    | 10.2             | I/O Buffer Model                     | 10-2 |

|    | 10.3             | I/O Model Application Note           | 10-3 |

|    | 10.4             | I/O Buffer AC and DC Characteristics | 10-3 |

|    | 10.5             | References                           | 10-3 |

| 11 | Pin Descriptions | 3                                    | 11-1 |

|    | 11.1             | Electrical Considerations            | 11-1 |

|    | 11.2             | Pin Numbering                        | 11-1 |

| 12 | Package Specific | cations                              | 12-1 |

Table of Contents vii

21090C/0-June 1997

*viii* Table of Contents

# **List of Figures**

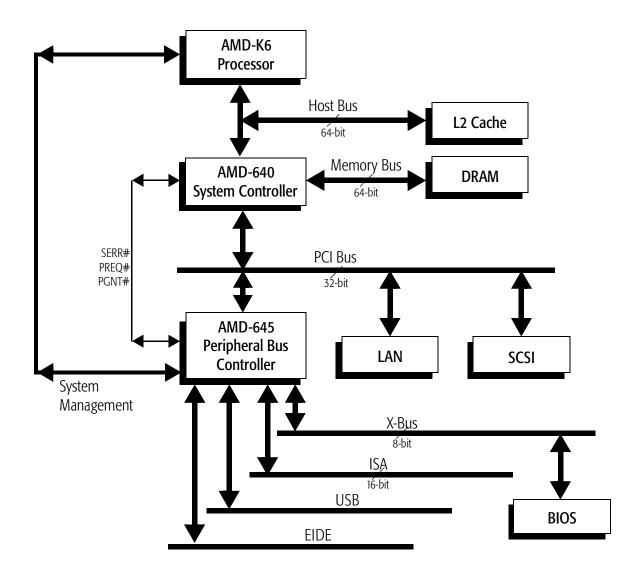

| Figure 1-1.  | AMD-640 Chipset System Block Diagram                 | 1-4  |

|--------------|------------------------------------------------------|------|

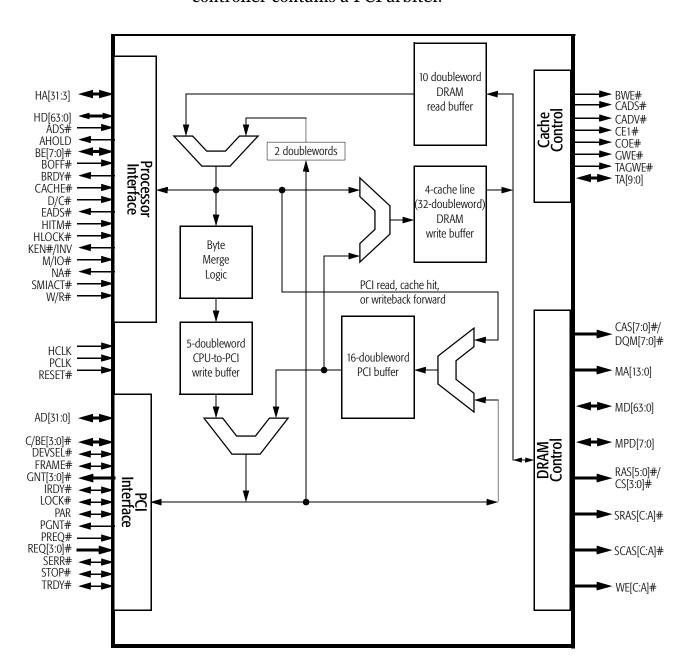

| Figure 2-1.  | AMD-640 System Controller Block Diagram              | 2-3  |

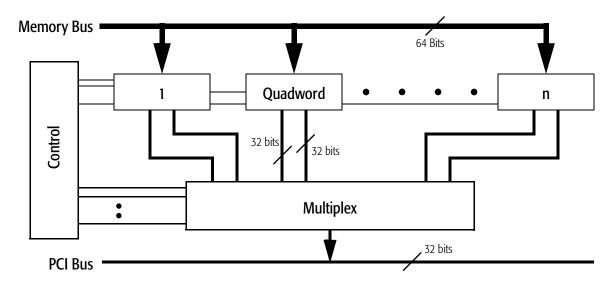

| Figure 2-2.  | Memory-to-PCI Buffer                                 |      |

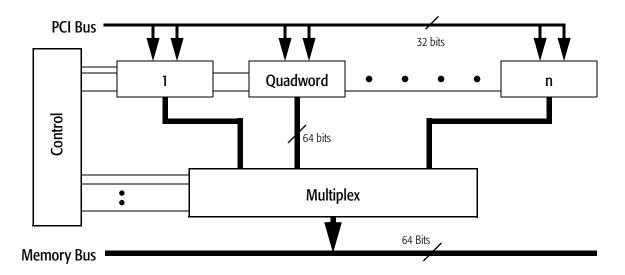

| Figure 2-3.  | PCI-to-Memory Buffer                                 | 2-4  |

| Figure 5-1.  | Posted Write Buffer Organization                     |      |

| Figure 5-2.  | Read Buffers                                         |      |

| Figure 5-3.  | 8-Bit Tag Cache Connections                          | 5-6  |

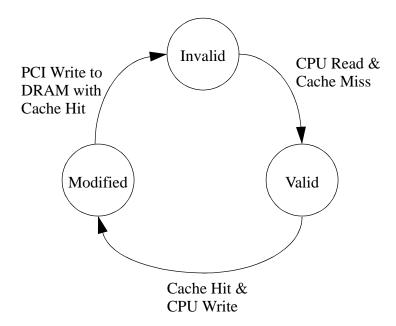

| Figure 5-4.  | Cache State Transitions                              |      |

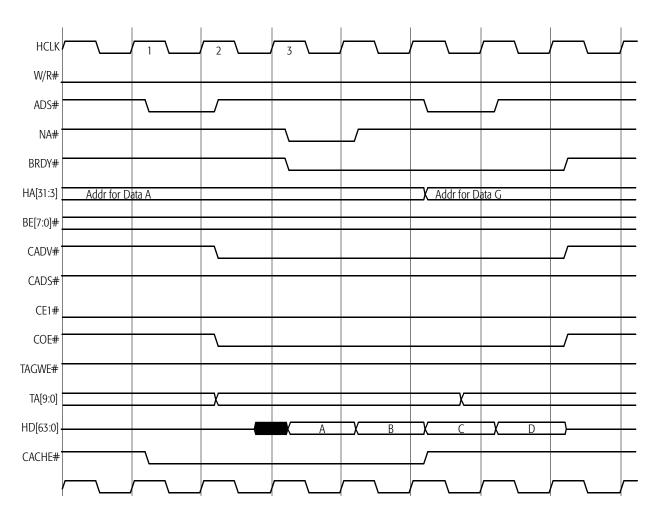

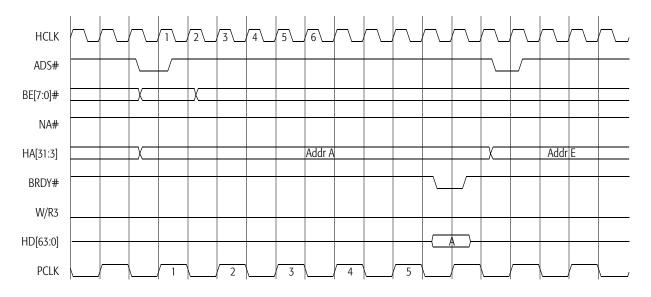

| Figure 5-5.  | Pipelined Burst Read Cycle                           | 5-11 |

| Figure 5-6.  | Pipelined Burst Write Cycle                          | 5-12 |

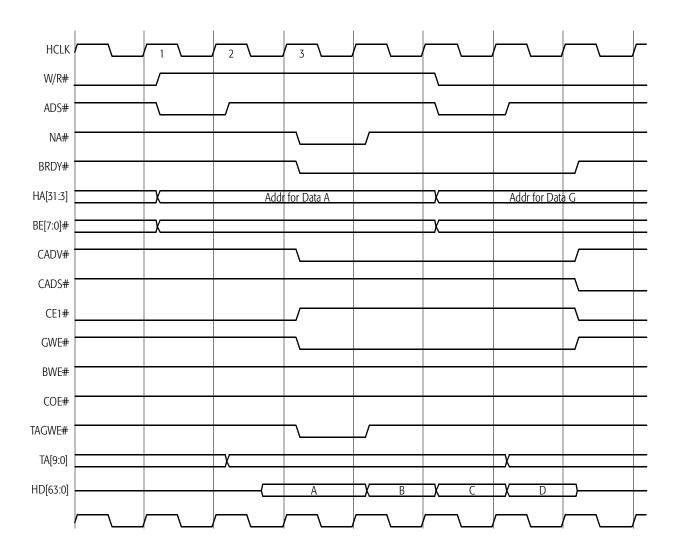

| Figure 5-7.  | EDO DRAM Interface Example                           | 5-16 |

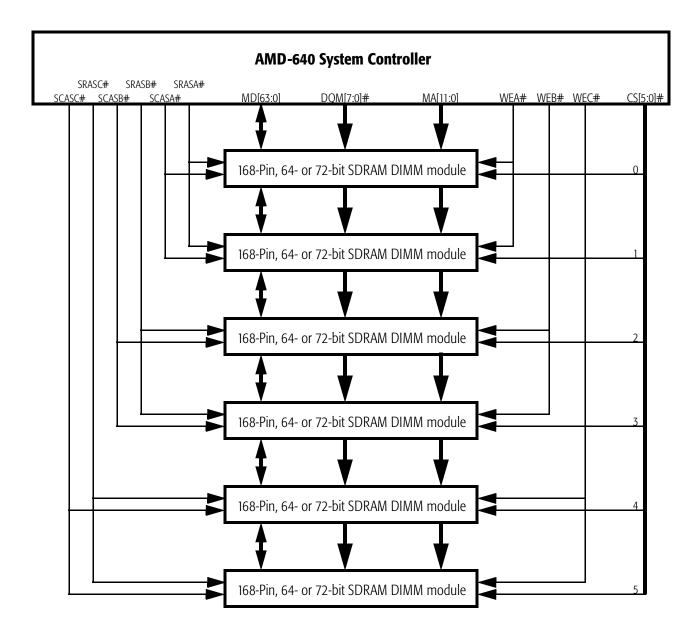

| Figure 5-8.  | SDRAM Interface Example                              | 5-17 |

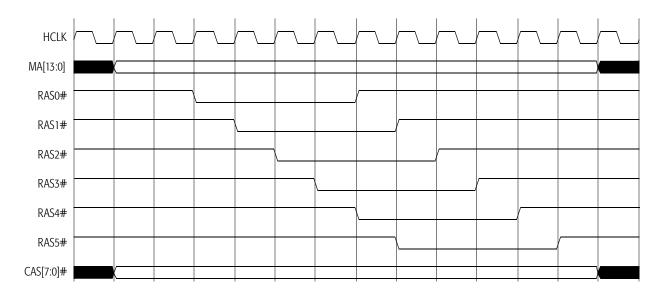

| Figure 5-9.  | Refresh Timing                                       |      |

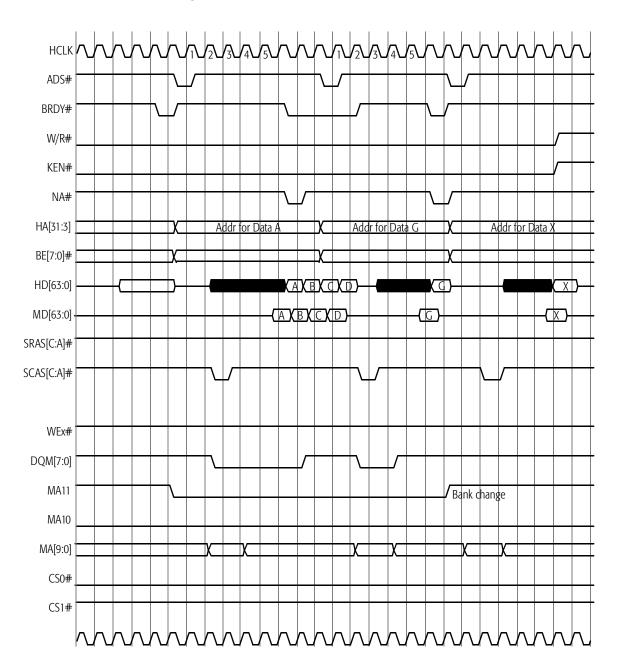

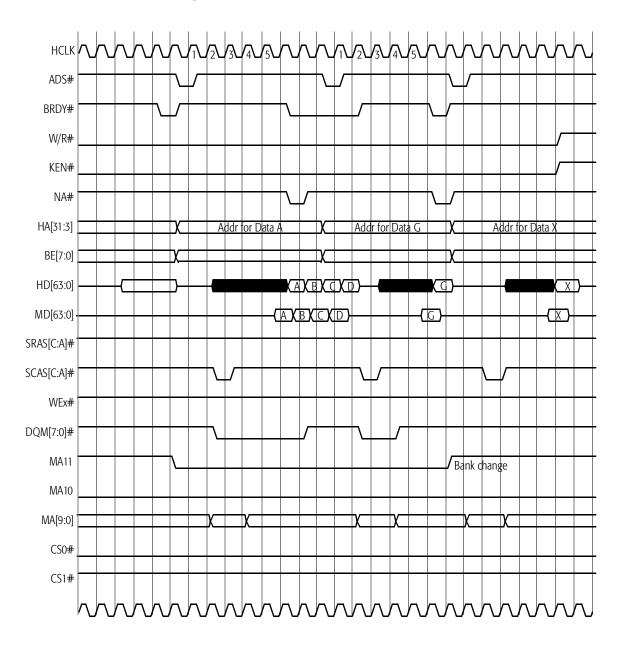

| Figure 5-10. | Pipelined EDO Read (5-2-2-2, 3-2-2-2)                | 5-23 |

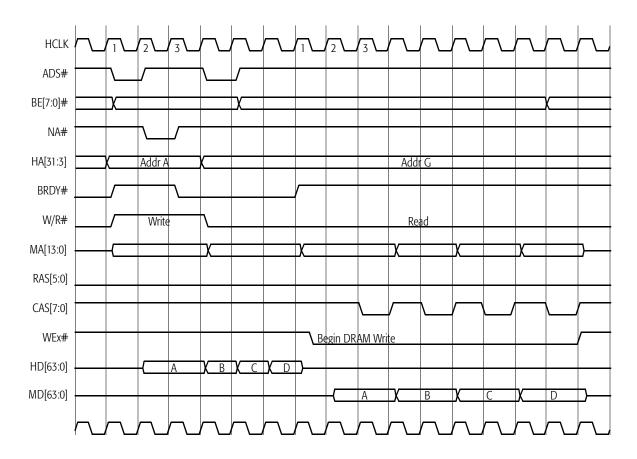

| Figure 5-11. | EDO Posted Write (2-2-2-2)                           | 5-24 |

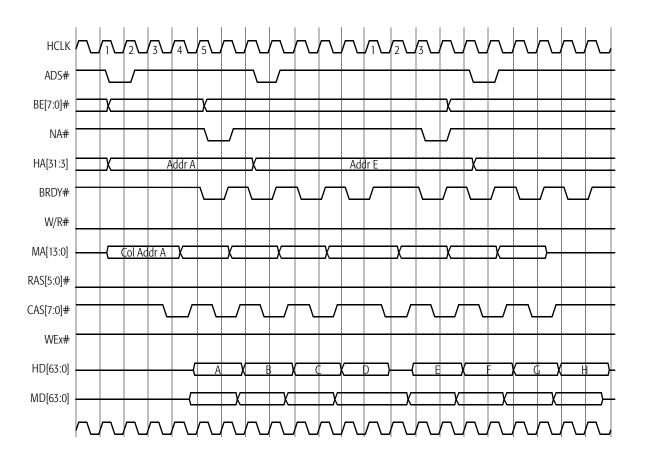

| Figure 5-12. | SDRAM Burst Read Cycle                               | 5-26 |

| Figure 5-13. | SDRAM Write Cycle                                    | 5-27 |

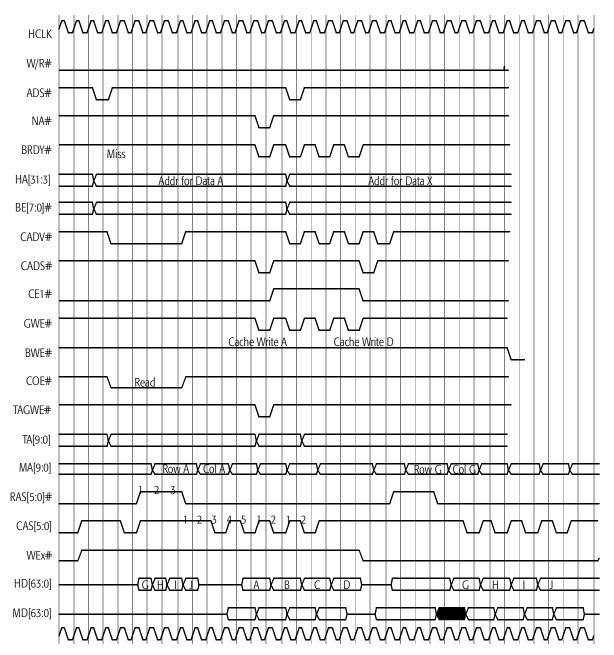

| Figure 5-14. | CPU Read Miss                                        | 5-28 |

| Figure 5-15. | Read Miss With Modified L2 Cache Line                | 5-29 |

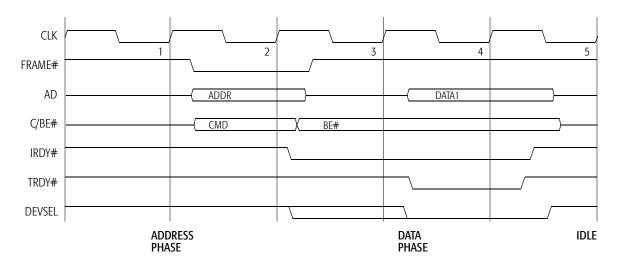

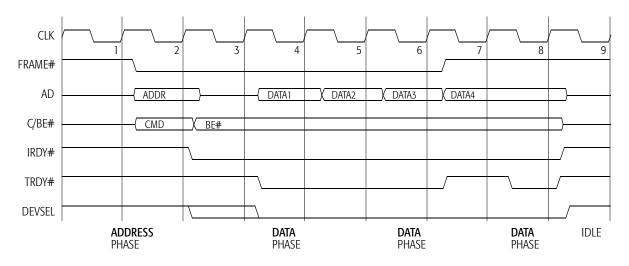

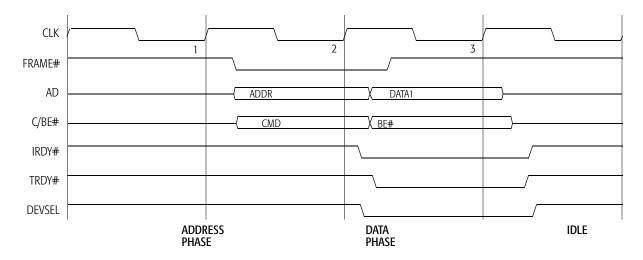

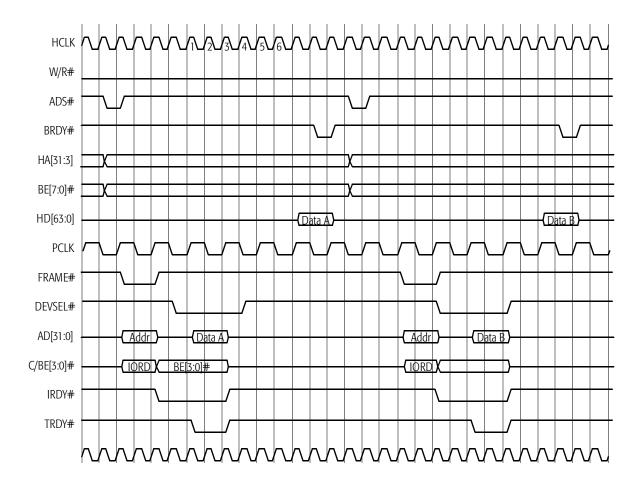

| Figure 5-16. | Basic PCI Read Operation                             | 5-32 |

| Figure 5-17. | PCI Burst Read Operation                             | 5-32 |

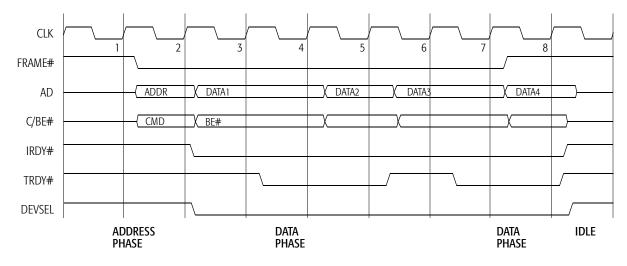

| Figure 5-18. | PCI Write                                            | 5-35 |

| Figure 5-19. | PCI Burst Write                                      | 5-35 |

| Figure 5-20. | Configuration Write                                  | 5-37 |

| Figure 5-21. | Configuration Read                                   | 5-37 |

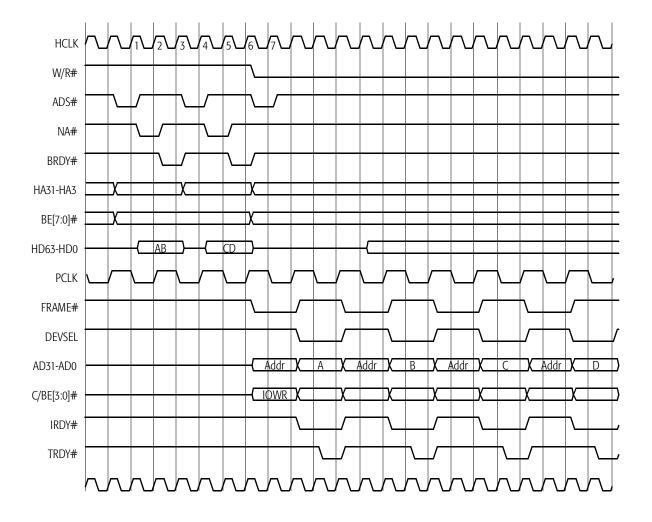

| Figure 5-22. | Processor Read from PCI Target                       | 5-38 |

| Figure 5-23. | Processor Write to PCI Target                        | 5-39 |

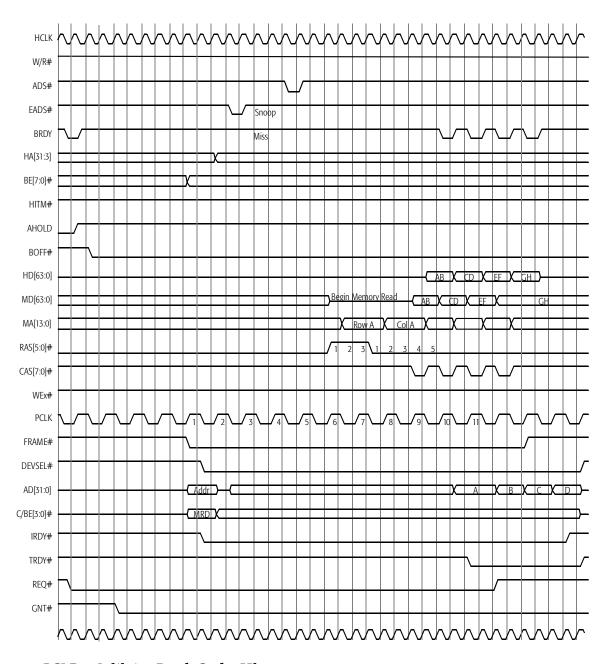

| Figure 5-24. | PCI Bus Initiator Read: Cache Miss                   | 5-41 |

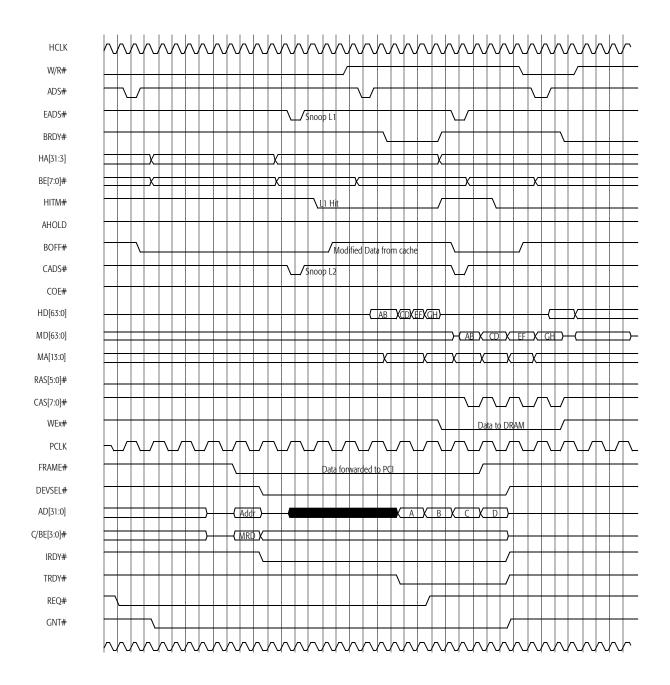

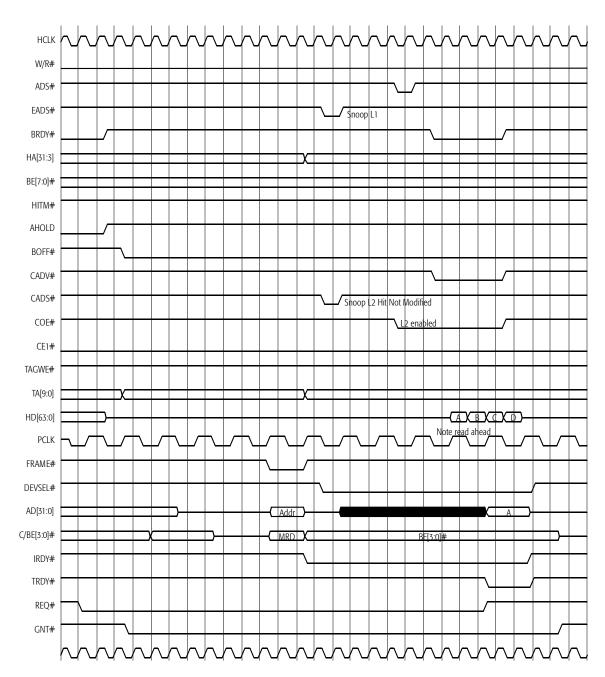

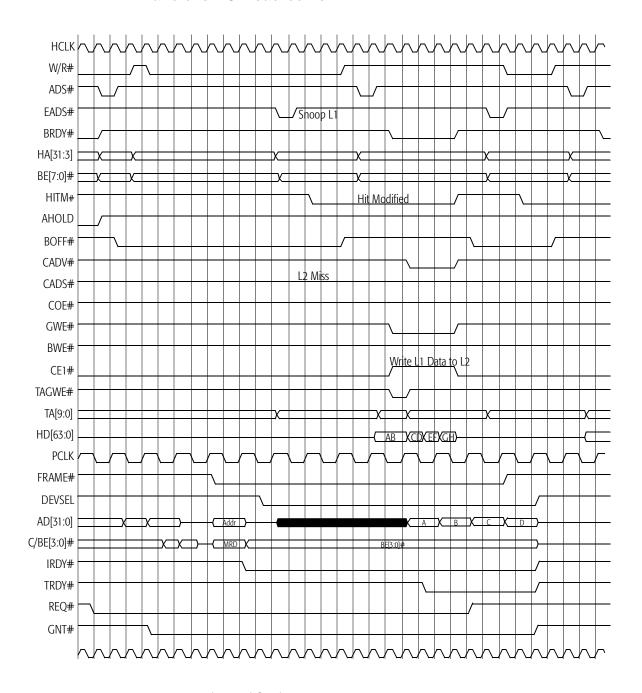

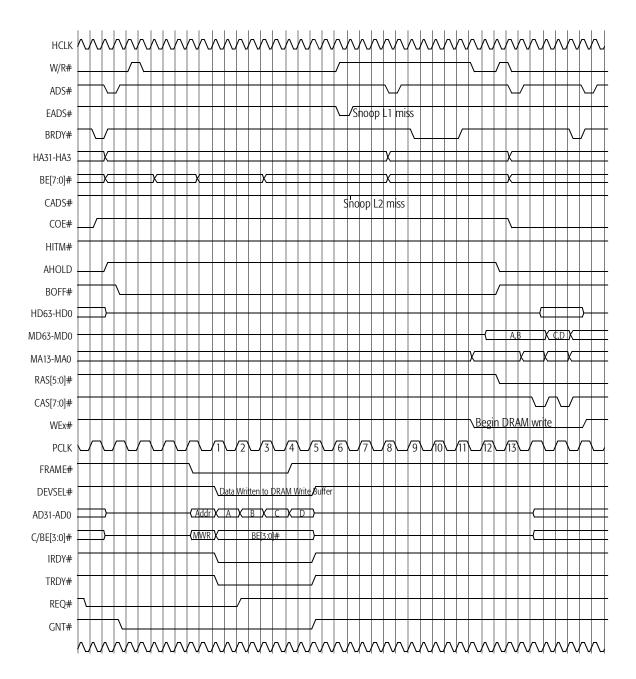

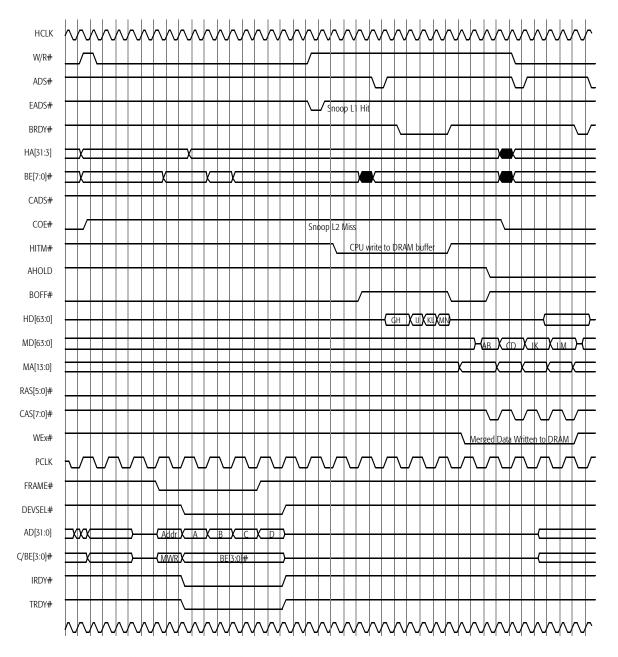

| Figure 5-25. | PCI Bus Initiator Read: Modified L1 Hit, L2 Miss     | 5-43 |

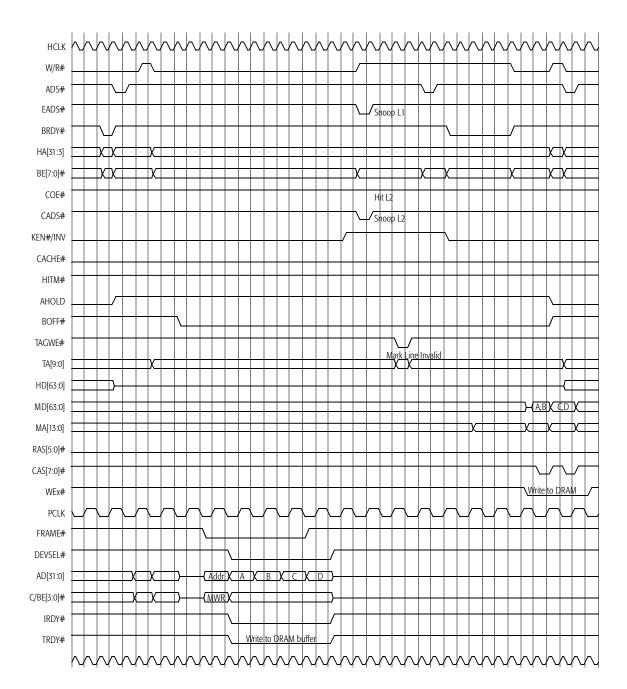

| Figure 5-26. | PCI Bus Initiator Read: L1 Miss, Unmodified L2 Hit . | 5-44 |

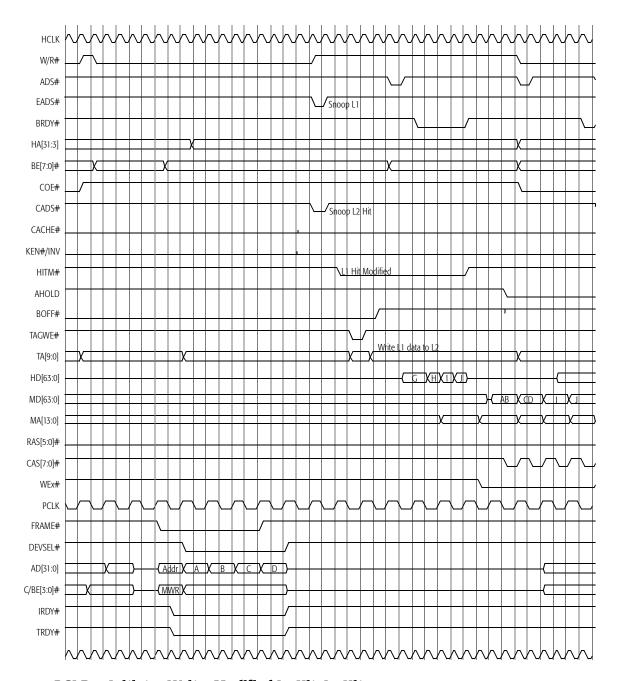

| Figure 5-27. | PCI Bus Initiator Read: Modified L1 Hit              | 5-45 |

| Figure 5-28. | PCI Bus Initiator Write: Cache Miss                  | 5-46 |

| Figure 5-29. | PCI Bus Initiator Write: L1 Hit, L2 Miss             | 5-47 |

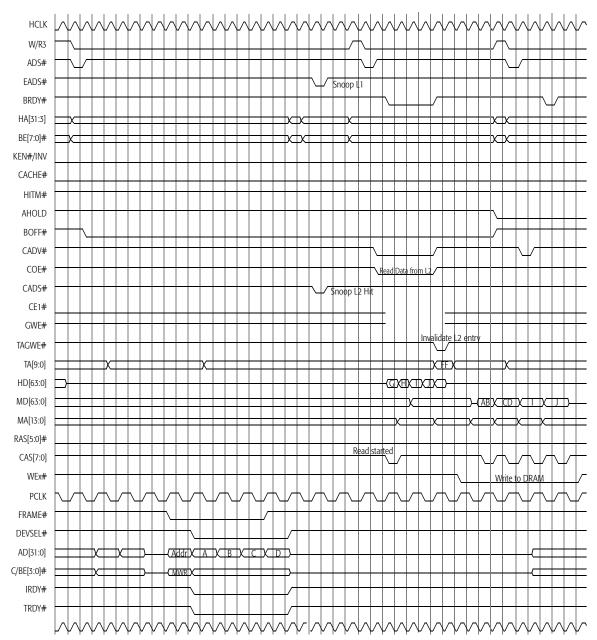

| Figure 5-30. | PCI Bus Initiator Write: L1 Miss, Unmodified L2 Hit. | 5-48 |

| Figure 5-31. | PCI Bus Initiator Write: Modified L1 Hit, L2 Hit     | 5-49 |

| Figure 5-32. | PCI Bus Initiator Write: L1 Miss, Modified L2 Hit    | 5-50 |

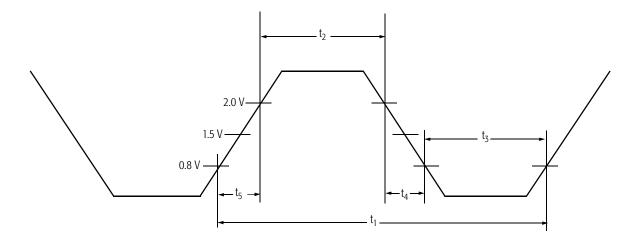

| Figure 9-1.  | CLK Waveform                                         | 9-3  |

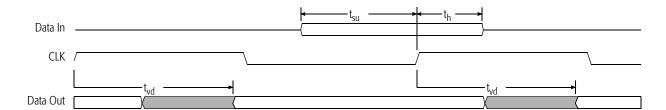

| Figure 9-2.  | Setup, Hold, and Valid Delay Timing Diagram          | 9-4  |

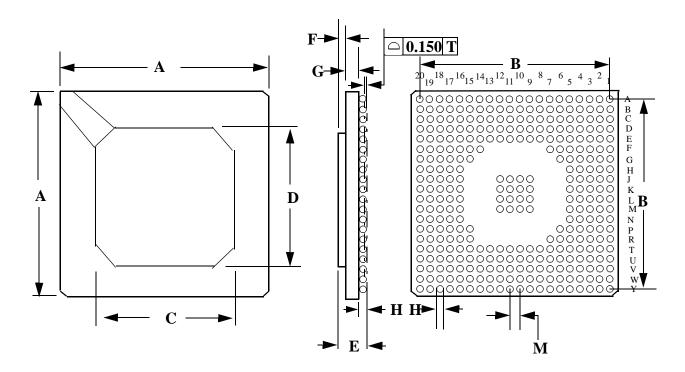

| Figure 12-1. | 328-Pin BGA Package Preliminary Specification        | 12-2 |

List of Figures ix

21090C/0-June 1997

x List of Figures

# **List of Tables**

| Table 5-1.  | Common 8-Bit Tag Configurations                        | . 5-6 |

|-------------|--------------------------------------------------------|-------|

| Table 5-2.  | Writeback Configurations for 7-Bit Tag with Modify Bit | . 5-7 |

| Table 5-3.  | Cache Hit Action Taken                                 | . 5-8 |

| Table 5-4.  | Cache Miss Action Taken                                | . 5-9 |

| Table 5-5.  | Cache States vs. Bit Conditions                        | . 5-9 |

| Table 5-6.  | SRAMs vs. Bus Speeds                                   | 5-14  |

| Table 6-1.  | Configuration Space Header Registers                   | . 6-1 |

| Table 6-2.  | Configuration Space Cache Control Registers            | . 6-2 |

| Table 6-3.  | Configuration Space DRAM Control Registers             | . 6-3 |

| Table 6-4.  | Configuration Space PCI Control Registers              | . 6-4 |

| Table 7-1.  | Configuration Port Register Summary                    | . 7-2 |

| Table 7-2.  | Configuration Space Header Registers                   | . 7-3 |

| Table 7-3.  | Configuration Space Cache Control Registers            | . 7-3 |

| Table 7-4.  | Configuration Space DRAM Control Registers             | . 7-4 |

| Table 7-5.  | Configuration Space PCI Control Registers              | . 7-5 |

| Table 7-6.  | Mapping Host Address Lines to Memory Address Lines     | 7-18  |

| Table 7-7.  | Ending Address Register Settings                       | 7-19  |

| Table 7-8.  | CAS# Pulse Width                                       | 7-23  |

| Table 7-9.  | PBSRAM Timing                                          | 7-26  |

|             | Functions of Pins N17 and M17                          |       |

| Table 7-11. | PCI Burst Control Bits                                 | 7-33  |

| Table 8-1.  | Absolute Ratings                                       |       |

| Table 8-2.  | Operating Ranges                                       | . 8-2 |

| Table 8-3.  | DC Characteristics                                     | . 8-3 |

| Table 8-4.  | Typical and Maximum Power Dissipation                  | . 8-4 |

| Table 9-1.  | HCLK Switching Characteristics for 66-MHz Bus          |       |

|             | Operation                                              | . 9-2 |

| Table 9-2.  | HCLK Switching Characteristics for 60-MHz Bus          |       |

|             | Operation                                              | . 9-2 |

| Table 9-3.  | PCLK Switching Characteristics for 33-MHz PCI Bus      | . 9-3 |

| Table 9-4.  | Processor Cycle Timing                                 | . 9-5 |

| Table 9-5.  | PCI Interface Timing                                   | . 9-6 |

| Table 9-6.  | DRAM Interface Timing                                  | . 9-7 |

| Table 9-7.  | L2 Cache Timing                                        | . 9-8 |

| Table 11-1. | Functional Grouping                                    | 11-2  |

| Table 11-2. | AMD-640 System Controller Pin Diagram (Top View)       | 11-4  |

| Table 12-1. | 328-Pin BGA Package Preliminary Specification          | 12-1  |

List of Tables xi

21090C/0-June 1997

xii List of Tables

# 1 Features

The AMD-640™ chipset is a highly integrated system solution that delivers superior performance for the AMD-K5™ processor, AMD-K6™ MMX™ enhanced processor, and other Socket 7-compatible processors. The AMD-640 chipset consists of the AMD-640 system controller in a 328-pin BGA package and the AMD-645TM peripheral bus controller in a 208-pin PQFP package. The AMD-640 system controller features the 64-bit Socket 7 interface, integrated writeback cache controller, system memory controller, and PCI bus controller.

This document describes the features and operation of the AMD-640 system controller. For a description of the AMD-645 peripheral bus controller, see the *AMD-645 Peripheral Bus Controller Data Sheet*, order# 21095A. Key features of the AMD-640 system controller are provided in this section.

### 1.1 Processor Interface

- Supports all 64-bit AMD-K5 processors and AMD-K6 processors

- Operates at processor bus speeds up to 66 MHz

- Supports processors with internal (L1) writeback cache write allocate feature

- Supports processor bus NA# pipeline protocol

- Low voltage 3.3-V processor interface

- System management interrupt, memory remap, and STPCLK#

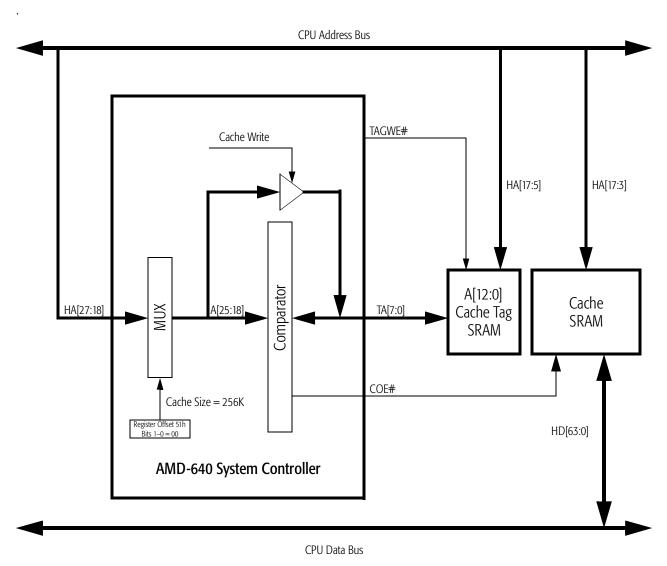

# 1.2 Integrated Cache Controller

- Direct-mapped writeback or writethrough secondary cache

- Global write enable to support pipelined burst synchronous SRAM (PBSRAM) cache access

- Flexible cache size 0, 256 Kbytes, 512 Kbytes, 1 Mbyte, and 2 Mbytes

Features 1-1

- 32-byte line size compatible with L1 cache

- Integrated 10-bit tag comparator

- 3-1-1-1 read/write timing for PBSRAM access at 66 MHz

- 3-1-1-1-1-1 back-to-back read timing for PBSRAM access at 66 MHz

- Sustained three-cycle access to PBSRAM, DRAM write buffer, and PCI write buffer at 66 MHz

- Data streaming for simultaneous primary and secondary cache line fills

- Cacheable, write-protected system and video BIOS

- Programmable cacheable region and cache timing

# 1.3 Integrated Memory Controller

- Supports the following combination of DRAM types:

- Fast page mode (FPM), extended data out (EDO), and synchronous DRAM (SDRAM)

- 1-, 2-, 4-, and 16-Mbit by n-bit DRAMs in one to six banks up to a total of 768 Mbytes

- 32-bit and 64-bit data widths

- Flexible row and column addressing

- 3.3-V and 5-V operation with no external buffers

- Bank-by-bank error correcting code options

- Two interleave options:

- Two-bank interleaving for 16-Mbit SDRAMs

- Two- and four-bank interleaving for 64-Mbit SDRAMs

- Four cache lines (16 quadwords) of processor-to-DRAM posted write buffers with full read-around and combine-and-store capability

- Concurrent DRAM writeback, read-around-write, and speculative DRAM read ahead

- Burst reads and writes

- Supports the following timings using 60 ns DRAM:

- EDO DRAMs on a 50-MHz or 60-MHz bus: 4-2-2-2 on-page, 7-2-2-2 start-page, and 9-2-2-2 page-miss

**1-2** Features

- EDO DRAMs on a 66-MHz bus:

- 5-2-2-2 on-page, 8-2-2-2 start-page, 11-2-2-2 page-miss, and 5-2-2-3-2-2-2 back-to-back access

- -15 SDRAMs on a 60-MHz bus, CAS latency = 2:

- 5-1-1-1 on-page, 8-1-1-1 start-page, 10-1-1-1 page-miss, and 5-1-1-3-1-1 back-to-back access

- -12/-10 SDRAMs on a 100-MHz bus, CAS latency = 3:

- 6-1-1-1 on-page, 9-1-1-1 start-page, 11-1-1-1 page-miss, and 6-1-1-3-1-1 back-to-back access

- Supports BIOS shadowing on 16-Kbyte boundaries

- Decoupled and burst DRAM refresh with staggered RAS timing

- Provides the following refresh options:

- Programmable refresh rate

- CAS-before-RAS

- Populated banks only

### 1.4 PCI Bus Controller

- Support for five PCI masters

- 32-bit 3.3-V and 5-V PCI interface

- Synchronous PCI bus operation up to 33 MHz

- PCI initiator snoop-ahead and snoop filtering

- PCI initiator peer concurrence

- Automatic processor-to-PCI burst cycle detection

- Five-doubleword processor-to-PCI post write buffer

- 48-doubleword PCI-to-DRAM post write buffer (16 + 32)

- 26-doubleword DRAM-to-PCI prefetch buffer (10 +16)

- Byte merging on processor-to-PCI posted writes to reduce the number of PCI write cycles

- Zero wait state PCI initiator and target burst transfers

- PCI-to-DRAM data streaming up to 132 Mbytes per second

- Full compliance with *PCI Bus Specification*, *Revision 2.1*

- Enhanced PCI command optimization (MRL, MRM, MWI)

- Timer-enforced fair arbitration between PCI initiators

Features 1-3

Figure 1-1. AMD-640 Chipset System Block Diagram

**1-4** Features

# 2 Overview

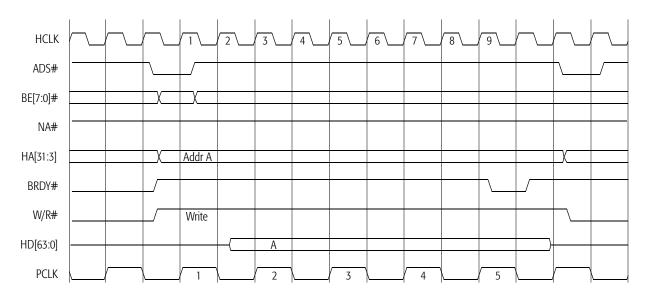

The AMD-640 system controller optimizes the interaction between the processor, optional synchronous L2 cache, DRAM, and the PCI bus with pipelined burst and concurrent transactions. It provides 3-1-1-1-1-1-1 timing for both read and write transactions with pipelined burst synchronous SRAMs running at 66 MHz. The AMD-640 system controller includes four cache lines (16 quadwords) of processor-to-DRAM or cache-to-DRAM write buffering with concurrent writeback capability to accelerate writeback and write miss cycles.

# 2.1 System

The local bus is a non-multiplexed bus based on AMD and Intel processors. The AMD-640 system controller is capable of performing I/O, single memory, and block memory transactions. The AMD-640 system controller memory controller can perform zero wait state memory reads and writes using an advanced data buffering design. However, in the event of a buffer miss, the memory controller inserts wait states using the BRDY# wait procedure. The controller responds only to I/O cycles within its configuration register space and memory requests as defined in its configuration registers. All cycle timing on the local bus is derived from the CPU clock (CCLK). This same signal drives the AMD-640 system controller host clock (HCLK) input, from which the controller derives all of its timing.

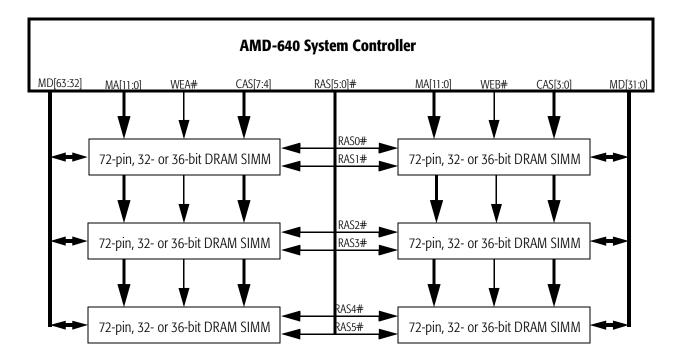

The AMD-640 system controller incorporates a high-performance, flexible 64-bit DRAM controller that provides the DRAM interface for either an AMD-K5 or AMD-K6 processor. The memory controller can perform zero wait state reads or writes through the use of a prefetch read buffer or a deep write buffer, respectively. It can address up to six banks of DRAMs in various combinations of 1 Mbit, 2 Mbit, 4 Mbit, and 16 Mbit by 32 or 64 bits, up to a total of 768 Mbytes. The DRAM can be any combination of fast page mode (FPM) DRAM, extended data out (EDO) DRAM, and Synchronous DRAM (SDRAM). Synchronous DRAM allows zero wait state

Overview 2-1

bursting between the DRAM and the controller's internal data buffers at 66 MHz. The DRAM controller can be configured to implement error correction code (ECC) data integrity checking. The BIOS must determine the type of memory installed and program the configuration registers accordingly.

The AMD-640 system controller supports shadowing to accelerate video and system BIOS accesses. The shadow RAM can also be configured to be cacheable and write-protected. The unused portion of DRAM can be relocated to increase overall system size. In addition, the AMD-640 system controller can be programmed to perform writes to flash EPROM, enabling field BIOS upgrades.

The AMD-640 system controller is fully compatible with the PCI Local Bus Specification, Revision 2.1. It can operate at either 3.3 V or 5 V, and offers 64-bit to 32-bit data conversion. A fivedoubleword posted write buffer enables concurrent processor and PCI operation. Consecutive processor addresses are converted into burst PCI cycles with byte-merging capability for optimal processor-to-PCI throughput. A 48-doubleword PCI post write buffer and a 32-doubleword PCI prefetch buffer facilitate concurrent PCI, DRAM, and cache transactions. Enhanced PCI bus commands such as Memory-Read-Line, Memory-Read-Multiple, and Memory-Write-Invalid maximize data throughput. The AMD-640 system controller employs a variety of techniques to minimize PCI initiator read latency and DRAM access, including snoop ahead, snoop filtering, forwarding L1 writebacks to the PCI initiator, and merging L1 writebacks into the PCI posted write buffers. These techniques minimize PCI initiator read latency and DRAM utilization. The combination of these features allows a PCI initiator to achieve the full 133-Mbyte burst transfer rate.

Figure 2-1 illustrates the full complement of features and functions built into the AMD-640 system controller's system logic. The configuration of the AMD-640 system controller can be programmed via I/O-mapped configuration registers. A PCI-to-CPU read buffer can assemble up to eight bytes of data. A five-doubleword CPU-to-PCI write buffer allows the processor to post up to five writes without adding delay on the local bus for PCI to complete the cycles. A 26-doubleword DRAM-to-PCI read buffer enables the controller logic to prefetch data, eliminating stalls on PCI while waiting for data from DRAM. A

2-2 Overview

48-doubleword PCI-to-DRAM write buffer allows PCI initiators to post writes to memory without adding delay on either the PCI or processor bus. In addition, the AMD-640 system controller contains a PCI arbiter.

Figure 2-1. AMD-640 System Controller Block Diagram

Overview 2-3

# 2.2 AMD-640 System Controller Buffers

Figure 2-2 and Figure 2-3 show the basic construction of the buffers in the AMD-640 system controller. Figure 2-2 shows a path from a 64-bit bus to a 32-bit bus (memory-to-PCI). Figure 2-3 shows a path from a 32-bit bus to a 64-bit bus (PCI-to-memory). The control logic assembles 32-bit words into 64-bit words or disassembles 64-bit words into 32-bit words.

Figure 2-2. Memory-to-PCI Buffer

Figure 2-3. PCI-to-Memory Buffer

2-4 Overview

### 2.3 Definitions, Conventions, and References

- Active-Low Signals—Signal names containing a pound sign, such as ADS#, indicate active-low signals. They are asserted in their low-voltage state and negated in their high-voltage state.

- Reserved Bits and Signals—Signals or bus bits marked reserved must be driven inactive or left unconnected, as indicated in the signal descriptions. These bits and signals are reserved by AMD for future implementations. When software reads registers with reserved bits, the reserved bits must be masked. When software writes such registers, it must first read the register and change only the non-reserved bits before writing back to the register.

- Three-State—In timing diagrams, signal ranges that are high impedance are shown as a straight horizontal line halfway between the high and low levels.

- Invalid and Don't Care—In timing diagrams, signal ranges that are invalid or don't care are filled with a screen pattern.

Overview 2-5

#### 2.3.1 Data

- Quantities—A word is two bytes (16 bits), a dword or doubleword is four bytes (32 bits), and a qword or quadword is eight bytes (64 bits).

- Addressing—Memory is addressed as a series of bytes on eight-byte (64-bit) boundaries, in which each byte can be separately enabled.

- Abbreviations—The following notation is used for bits and bytes:

kilo k......as in 4 kbytes/pageMega M.....as in 4 Mbits/sec

Giga G.....as in 4 Gbytes of memory space

- Little-Endian Convention—The byte with the address xx...xx00 is in the least-significant byte position (little end). In byte diagrams, bit positions are numbered from right to left: the little end is on the right and the big end is on the left. Data structure diagrams in memory show small addresses at the bottom and high addresses at the top. When data items are aligned, bit notation on a 64-bit data bus maps directly to bit notation in 64-bit-wide memory. Because byte addresses increase from right to left, strings appear in reverse order when illustrated.

- Bit Ranges—In a range of bits, the highest and lowest bit numbers are separated by a dash, as in 63–00.

- Bit Values—Bits can either be set to 1 or cleared to 0.

- Hexadecimal and Binary Numbers—Unless the context makes interpretation clear, hexadecimal numbers are followed by an h, binary numbers are followed by a b, and decimal numbers are followed by a d.

2-6 Overview

#### 2.3.2 Related Publications

The following books discuss various aspects of computer architecture that may be useful for your understanding of AMD products:

**AMD Publications** AMD-K5 Processor Data Sheet, order# 18522

AMD-K5 Processor Technical Reference Manual, order# 18524

AMD-K6 MMX Enhanced Processor Data Sheet, order# 20695

AMD-645 Peripheral Bus Controller Data Sheet, order# 21095

**Bus Architecture** PCI Local Bus Specification, Revision 2.1, PCI Special Interest

Group, Hillsboro, Oregon, 1993.

AT Bus Design, Edward Solari, IEEE P996 Compatible,

Annabooks, San Diego, CA, 1990.

**x86 Architecture** *Programming the 80386*, John Crawford and Patrick Gelsinger,

Sybex, San Francisco, 1987.

80x86 Architecture & Programming, Rakesh Agarwal, Volumes I

and II, Prentice-Hall, Englewood Cliffs, NJ, 1991.

General References Computer Architecture, John L. Hennessy and David A.

Patterson, Morgan Kaufman Publishers, San Mateo, CA, 1990.

Overview 2-7

21090C/0-June 1997

2-8 Overview

# **3 Ordering Information**

AMD standard products are available in several packages and operating ranges. The order number (valid combination) is formed by a combination of the elements below. Contact your AMD representative for detailed ordering information.

#### **Valid Combinations**

|           | Package Type | Operating Voltage | Case Temperature |

|-----------|--------------|-------------------|------------------|

| AMD-640AC | 328-pin PBGA | 4.75 V-5.25 V     | 70°C             |

#### Notes:

Ordering Information 3-1

Valid Combinations lists configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly-released combinations.

21090C/0-June 1997

**3-2** Ordering Information

# **4** Signal Descriptions

# 4.1 Processor Interface Signals

#### ADS# Address Strobe Input

ADS# indicates to the AMD-640 system controller that a new bus cycle is starting. When ADS# is asserted, the AMD-640 system controller latches the address bus and all cycle definition signals corresponding to this bus cycle on the rising edge of HCLK.

#### AHOLD Address Hold Output

The AMD-640 system controller asserts AHOLD off the rising edge of HCLK while a PCI initiator accesses main memory to perform an inquire cycle. The host processor responds by floating HA[31:3] to allow the AMD-640 system controller to drive the address bus. See the timing diagrams in Section 6 for example cycles.

#### BE[7:0]# Byte Enables Inputs

The AMD-640 system controller samples BE[7:0]# to determine the valid data bytes during a write cycle and the requested data bytes during a read cycle. The eight byte enable signals correspond to the eight bytes of the data bus as follows:

BE7#: D[63:56]

BE6#: D[55:48]

BE5#: D[47:40]

BE4#: D[39:32]

BE3#: D[31:24]

BE2#: D[23:16]

BE1#: D[15:8]

BE0#: D[7:0]

#### **BOFF#** Backoff Output

The AMD-640 system controller asserts BOFF# to acquire the host bus during PCI-to-DRAM cycles in order to perform snoop cycles and access the L1 and L2 caches in the event of a cache hit. The processor unconditionally aborts any cycles in

Signal Descriptions 4-1

progress and transitions to a bus hold state by floating the following signals:

A[31:3]

CACHE#

ADS#

D[63:0]

M/IO#

BE[7:0]#

D/C#

W/R#

These signals remain floated until BOFF# is negated.

#### BRDY# Burst Ready Output

The AMD-640 system controller asserts BRDY# to the host processor off the rising HCLK edge. During a read cycle, asserting BRDY# indicates that the data bus is being driven with valid data. During a write cycle, it indicates that the data bus has been latched.

#### CACHE# Cacheable Access Input

The host processor asserts CACHE# during a cacheable read cycle to indicate that it will perform a burst line fill. It asserts CACHE# during a cacheable write cycle to indicate that it will perform a burst writeback cycle. When the AMD-640 system controller samples CACHE# low, it stores processor read or write data in the L2 cache.

#### D/C# Data/Control Input

When the AMD-640 system controller samples D/C# low, it generates a command on the C/BE[3:0]# PCI bus signals in the command phase of processor-to-PCI bus cycles.

#### **EADS#** External Address Strobe Output

The AMD-640 system controller asserts EADS# off the rising HCLK edge to snoop each cache line transferred during all PCI-to-DRAM cycles. EADS# strobes the snoop address into the L1 cache. On L1 cache hits, the processor invalidates unmodified data during writes, and sources (drives) modified data during PCI initiator reads and writes.

#### HA[31:3] Host Address Bus Input/Output

The AMD-640 system controller samples addresses driven by the processor on HA[31:3] during memory and I/O cycles and

**4-2** Signal Descriptions

forwards them to the PCI bus or DRAM, depending on the address range.

During PCI-to-DRAM cycles, the AMD-640 system controller drives the address bus to snoop the processor's cache and the L2 cache.

#### HD[63:0] Host Data Bus Bidirectional

HD[63:0] connects to the host processor's 64-bit data bus. Each of the eight bytes of data that comprise this bus is qualified by a corresponding byte enable signal (BE[7:0]#).

#### HITM# Inquire Cycle Hit To Modified Line Input

The AMD-640 system controller samples HITM# to determine if an L1 cache snoop has found a modified line. A low on HITM# indicates that a cache line write by the processor is imminent. HITM# is deasserted after the line is written.

#### HLOCK# Host Bus Lock Input

The host processor asserts HLOCK# to indicate that it requires exclusive access to the local bus during a sequence of bus cycles. When the AMD-640 System Controller samples HLOCK# low, it withholds bus grants to other PCI initiators. If a grant has already been issued to a PCI initiator, the AMD 640 will not assert BOFF# for L1 snoops. These actions effectively suspend a PCI-DRAM transfer until HLOCK# is deasserted.

#### KEN#/INV Cache Enable/Invalidate Output

During host processor read cycles, KEN#/INV functions as the cache enable signal (KEN#), indicating a cacheable address when low and a non-cacheable address when high. KEN#/INV is driven off the rising HCLK edge.

During inquire cycles, KEN#/INV functions as the invalidate signal (INV), which determines whether an addressed cache line that is found in the host processor's L1 cache transitions to the invalid or shared state.

#### M/IO# Memory or I/O Input

The AMD-640 System Controller samples M/IO# during a bus cycle to determine whether the host processor is addressing

Signal Descriptions 4-3

memory or I/O space. When M/IO# is high, the AMD-640 System Controller enables accesses to DRAM and the L2 cache. When the access is not targeted to the cache or the DRAM, the AMD-640 system controller uses M/IO# to generate the PCI commands on C/BE[3:0] during the command phase of CPU-to-PCI cycles.

#### NA# Next Address Output

The AMD-640 system controller asserts NA# off the rising HCLK edge to indicate to the host processor that it is ready to accept a pipelined address.

#### SMIACT# System Management Interrupt Acknowledge Input

When SMIACT# from the host processor is sampled asserted, it indicates to the AMD-640 system controller that the processor has entered system management mode (SMM). If configuration register 63h bit, 1 is set, asserted SMIACT# redirects memory accesses from 30000h:3FFFFh to B0000h:BFFFFh. Accesses to this memory area are passed through to the PCI bus when SMIACT# is high, as this is normally the Video Buffer area.

#### W/R# Write/Read Input

The AMD-640 system controller samples W/R# to determine whether the current processor cycle is a write or a read.

4-4 Signal Descriptions

# 4.2 PCI Interface Signals

#### AD[31:0] PCI Address/Data Bus Bidirectional

AD[31:0] contain the PCI address during the first clock cycle in which FRAME# is asserted, and contain data during subsequent clock cycles. As an initiator, the AMD-640 system controller drives these lines with the address of the target. As a target, the AMD-640 system controller decodes these lines to determine what area of memory to read or write.

#### **C/BE[3:0]#** *PCI Command/Byte Enables Bidirectional*

C/BE[3:0]# contain the PCI command during the first clock cycle that FRAME# is asserted. These lines serve as byte enable signals for subsequent cycles.

#### **DEVSEL#** *PCI Device Select Bidirectional*

The AMD-640 system controller samples DEVSEL# when it is the initiator in a PCI cycle to determine if the target device has responded. The AMD-640 system controller asserts DEVSEL# when it is the targeted device in a PCI cycle.

#### FRAME# PCI Cycle Frame Bidirectional

The AMD-640 system controller asserts FRAME# at the beginning of a PCI cycle when it is the initiator, and holds it low until the beginning of the last data transfer in the cycle.

If the AMD-640 system controller is the targeted PCI device, it samples and latches the C/BE[3:0]# and AD[31:3] signals and asserts DEVSEL# at the first PCLK edge on which it samples FRAME# asserted.

#### GNT[3:0]# PCI Bus Grant Outputs

As the PCI bus arbiter, the AMD-640 system controller asserts one of these device-specific bus grant signals off the rising clock edge to indicate to an initiator that it has been granted control of the PCI bus.

Signal Descriptions 4-5

21090C/0-June 1997

#### **IRDY#** Initiator Ready Bidirectional

IRDY# indicates that a PCI initiator is ready to complete the current data phase of the transaction. During a read cycle, asserted IRDY# indicates the master is ready to accept the data. During a write cycle, asserted IRDY# indicates that write data is valid on AD31:AD0. Data is transferred on the PCI bus on each PCLK in which both IRDY# and TRDY# are asserted. Wait states are inserted on the bus until both IRDY# and TRDY# are asserted together.

IRDY# is an output when the AMD-640 system controller is the PCI initiator. The AMD-640 system controller drives IRDY# low one PCLK after it asserts FRAME# and holds it low until one cycle before the end of all transactions.

IRDY# is an input when the AMD-640 system controller is a PCI target. The AMD-640 system controller does not terminate a read or write cycle until it samples both IRDY# and TRDY# low.

#### LOCK# PCI Bus Lock Bidirectional

As a PCI initiator, the AMD-640 system controller asserts LOCK# to prevent other devices from accessing the target device during atomic CPU-to-PCI transactions.

#### PAR PCI Bus Parity Bidirectional

The AMD-640 system controller drives PAR as a PCI initiator one clock after the address phase and each data write phase to generate even parity across AD[31:3] and C/BE3:0]#. It drives PAR as a PCI target one clock after each data read phase.

#### **PGNT#** PCI Grant to AMD-645 Peripheral Bus Controller Output

PGNT# is asserted off the rising clock edge and grants control of the PCI bus to the PCI-ISA/IDE bridge functions implemented in the AMD-645 peripheral bus controller.

#### PREQ# PCI Request from AMD-645 Peripheral Bus Controller Input

The AMD-640 system controller samples PREQ# to determine if the AMD-645 peripheral bus controller needs PCI bus access.

**4-6** Signal Descriptions

#### **REQ[3:0]** *PCI Bus Request Inputs*

As the PCI bus arbiter, the AMD-640 system controller samples these device-specific bus request signals to determine if another agent requires control of the PCI bus.

#### SERR# System Error Output

A PCI agent (the AMD-640 system controller or other device) asserts SERR# off the rising clock edge one clock after it detects a system error. SERR# is an input to the AMD-645 peripheral bus controller, which can be programmed to generate an NMI.

#### STOP# PCI Bus Stop Input

As a PCI initiator, the AMD-640 system controller samples STOP# to determine if the target device requires it to abort or retry a transaction.

#### TRDY# Target Ready Bidirectional

As a PCI initiator, the AMD-640 system controller samples TRDY# to determine when the target agent is able to complete the data phase of a transaction.

As a PCI target, the AMD-640 system controller asserts TRDY# to indicate that it has latched the data on AD31:AD0 during a write phase or driven data on AD31:AD0 during a read phase.

Signal Descriptions 4-7

21090C/0-June 1997

### 4.3 DRAM Interface Signals

#### CAS[7:0]#/ DQM[7:0]#

#### Column Address Strobe/ Data Mask

#### **Outputs**

CAS[7:0]# generate column address strobes for FPM and EDO DRAM during processor-to-DRAM and PCI-to-DRAM cycles. CAS7# connects to the most-significant byte of each bank, and CAS0# connects to the least-significant byte. The width and delay of these signals are adjustable.

For SDRAM, these lines function as data masks DQM[7:0]# for each byte during SDRAM write cycles.

#### MA[13:0]

#### **Memory Address**

#### Outputs

The multiplexed row and column address bits MA[13:0] connect to the system DRAMs. They can address any size DRAM from 256 Kbits to 16 Mbits by n bits.

#### **MD**[63:0]

#### Memory Data

#### **Bidirectional**

MD[63:0] connect to the DRAM data bus. They are driven by the DRAM when reading. They are driven by the AMD-640 system controller during writes.

#### MPD[7:0]

#### Memory ECC

#### **Bidirectional**

MPD[7:0] carry error correction codes for the eight bytes of data on MD[63:0]. They are inputs to the AMD-640 system controller during DRAM read cycles and outputs during DRAM write cycles.

#### RAS[5:0]#/ CS[5:0]#

#### Row Address Strobe 5:0/ Chip Selects 5:0

#### **Outputs**

RAS[5:0]# generate row address strobes for the DRAM banks, either during CPU-to-DRAM or PCI-to-DRAM accesses or in sequence during DRAM refresh cycles.

CS[5:0]# function as chip select lines for SDRAMs if bits 5–4 in configuration register 60h select SDRAM.

**4-8** Signal Descriptions

21090C/0-June 1997

WEC#

AMD-640 System Controller Data Sheet

SCASA#, SCASB#, Synchronous DRAM Outputs

**SCASC#** Column Address Strobe

SCASA#, SCASB#, and SCASC# are column address strobe pins for synchronous DRAM. They operate in parallel to drive greater loads than a single pin can support.

SRASA#, SRASB#, Synchronous DRAM Outputs

SRASC# Row Address Strobe

SRASA#, SRASB#, and SRASC# are row address strobe pins for synchronous DRAM. They operate in parallel to drive greater loads than a single pin can support.

WEA# Synchronous DRAM Outputs

WEB# Memory Write Enable

WEA#, WEB#, and WEC# are write enable pins for all DRAM. They operate in parallel to drive greater loads than a single pin can support.

Signal Descriptions 4-9

# 4.4 Cache Controller Interface Signals

#### BWE# Byte Write Enable Output

BWE# connects to the BWE# input on each of the L2 cache SRAMs. When the AMD-640 system controller L2 cache controller asserts BWE# off the rising clock edge during cache writes, data on the processor bus (D[63:0]) is written to those bytes of the cache SRAM whose byte-enable lines (BE[7:0]#) are asserted.

### **CADS#** Cache Address Strobe Output

The AMD-640 system controller normally drives CADS# high. It enables CADS# to be asserted when it acquires the host processor bus by asserting BOFF#, and asserts CADS# off the rising clock edge during PCI-to-DRAM cycles that hit the L2 cache.

### CADV# Cache Advance Output

CADS# connects to the ADS# inputs of the L2 cache SRAMs. The AMD-640 system controller asserts CADS# off the rising clock edge during L2 cache line read and write hits as well as during line fills and line writebacks, incrementing the SRAM's internal counters to advance to the next quadword in the cache line.

#### CE1# Chip Enable 1 Output

The CE1# chip select signal enables the L2 cache for both reads and writes. It is asserted off the rising clock edge.

#### COE# Cache SRAM Output Enable Output

The AMD-640 system controller asserts COE# off the rising clock edge of a cache read hit or writeback cycle and holds it low for the duration of the cycle to enable cache SRAM output. It also asserts COE# during the first two clock cycles of CPU-to-PCI memory reads, non-cacheable reads, or read misses without writeback.

**4-10** Signal Descriptions

AMD-640 System Controller Data Sheet

### **GWE#** Global Write Enable Output

GWE# connects to the global write inputs of the cache SRAMs. The AMD-640 system controller asserts GWE# off the rising clock edge during L2 cache line fills to enable the SRAMs to receive each quadword of the line being returned by the DRAM controller.

### **TA[9:0]** Tag Address Bidirectional

TA[9:0] are used to read and write the cache page number to and from external tag RAM. They function as outputs during L2 cache line fills and as inputs at all other times.

#### TAGWE# TAG Write Enable Output

The AMD-640 system controller asserts TAGWE# on the rising edge of HCLK to enable the L2 cache tag SRAMs to receive the next tag address.

Signal Descriptions 4-11

21090C/0-June 1997

# 4.5 Clocks and Reset

### HCLK Host Clock Input

HCLK receives a buffered host clock. It is used by all of the AMD-640 system controller logic in the host clock domain. It is the primary reference for all bus cycles on the processor and memory buses as well as most of the internal logic.

### PCLK PCI Clock Input

PCLK receives a buffered host clock divided by two. It is used by all of the AMD-640 system controller logic in the PCI clock domain.

# RESET# Reset Input

Asserting RESET# resets the AMD-640 system controller and sets all register bits to their default values. Bidirectional pins are three-stated and outputs are driven inactive. This signal is driven by the PCIRST# signal from the AMD-645 peripheral bus controller.

**4-12** Signal Descriptions

# 5 Functional Operation

# **5.1** Processor Interface

The AMD-640 system controller responds to CPU-generated bus signals and activates the PCI, DRAM, and cache state machines according to the command type and address range. On memory cycles it drives the processor address onto the memory bus from its integrated DRAM controller. For PCI target cycles it drives the PCI bus from its integrated PCI buffers and control logic.

The AMD-640 system controller maintains coherency of the processor primary (L1) cache with the rest of the system using the KEN#, EADS#, and HITM# pins. It monitors the CACHE# signal from the processor to determine burst cycles and returns KEN# asserted when data is cacheable. KEN# is normally active during a memory read cycle unless the processor address lies outside the cacheable region. In this case, the AMD-640 system controller deasserts KEN# before the completion of the first burst transfer so that the data is not written to the L1 cache. The AMD-640 system controller does not write data to the secondary (L2) cache when CACHE# is inactive unless it is programmed to do so by setting bit 2 of register 52h. It asserts the EADS# signal during DMA and PCI initiator cycles to snoop the L1 cache. The processor responds to a cache hit by asserting the HITM# line. This action notifies the AMD-640 system controller that a modified cache line must be written back to the system before the intended memory access can be performed. A snoop filtering mechanism in the AMD-640 system controller minimizes snoop overhead by ensuring that consecutive accesses to the same cache line are snooped only once.

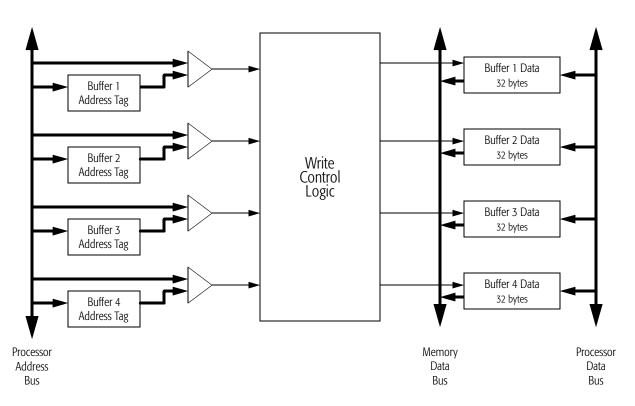

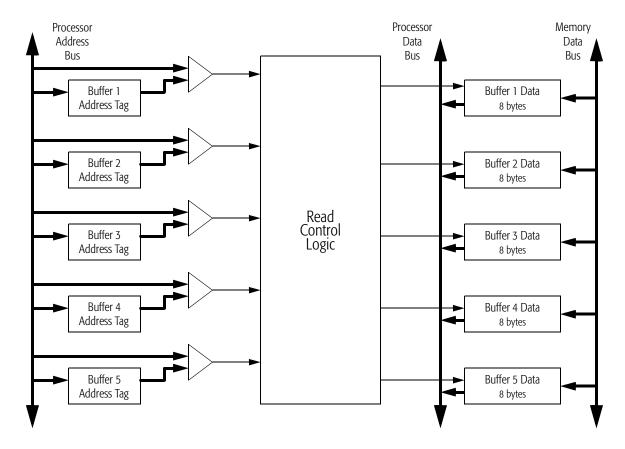

# 5.1.1 Write Posting

The AMD-640 system controller contains four write buffers to enhance memory write performance. Each buffer can hold one entire cache line, also referred to as a data block, which is 32