# **AMD-751**<sup>™</sup>

# **System Controller**

**Data Sheet**

Publication # 21910 Rev: E Issue Date: March 2000

#### © 2000 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

#### **Trademarks**

AMD, the AMD logo, AMD Athlon, and combinations thereof, AMD-750, AMD-751, and AMD-756 are trademarks, and AMD-K6 is a registered trademark of Advanced Micro Devices, Inc.

Alpha is a trademark of Digital Equipment Corporation.

Microsoft is a registered trademark of Microsoft Corporation.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

# **Contents**

|     | Revision       | Histor  | у                                                                                                                                                                                                                                                                                                              | xiii                         |

|-----|----------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 1   | Features       |         |                                                                                                                                                                                                                                                                                                                | 1                            |

|     |                | 1.1     | AMD Athlon <sup>TM</sup> System Bus                                                                                                                                                                                                                                                                            | 2                            |

|     |                | 1.2     | Integrated Memory Controller                                                                                                                                                                                                                                                                                   | 2                            |

|     |                | 1.3     | PCI Bus Controller                                                                                                                                                                                                                                                                                             | 4                            |

|     |                | 1.4     | AGP Features                                                                                                                                                                                                                                                                                                   | 4                            |

|     |                | 1.5     | Power Management                                                                                                                                                                                                                                                                                               | 5                            |

| 2   | Overview       | 1       |                                                                                                                                                                                                                                                                                                                | 7                            |

|     |                | 2.1     | System                                                                                                                                                                                                                                                                                                         | 7                            |

|     |                |         | 2.1.1 Processor Interface                                                                                                                                                                                                                                                                                      | 8<br>9<br>10<br>12           |

|     |                | 2.2     | Interface Levels                                                                                                                                                                                                                                                                                               | . 13                         |

|     |                | 2.3     | Clocking                                                                                                                                                                                                                                                                                                       | . 14                         |

| 3   | Ordering       | Inforr  | nation                                                                                                                                                                                                                                                                                                         | 15                           |

| 4   | Signal De      | scripti | ons                                                                                                                                                                                                                                                                                                            | 17                           |

|     |                | 4.1     | Processor Interface Signals                                                                                                                                                                                                                                                                                    | . 17                         |

|     |                |         | 4.1.1 CLKFWDRST (Clock Forward Reset) 4.1.2 CONNECT (Connect) 4.1.3 PROCRDY (Processor Ready) 4.1.4 SADDIN[14:2]# (Address/Command) 4.1.5 SADDINCLK# (System Address In Clock) 4.1.6 SADDOUT[14:2]# (System Address Out) 4.1.7 SADDOUTCLK# (System Address Out Clock) 4.1.8 SCHECK[7:0]# (Data Bus Check Byte) | . 17<br>. 18<br>. 18<br>. 18 |

| Tab | le of Contents |         |                                                                                                                                                                                                                                                                                                                | iii                          |

|     | 4.1.9 SDATA[63:0]# (Processor Data Channel) 20      |

|-----|-----------------------------------------------------|

|     | 4.1.10 SDATAINCLK[3:0]# (System Data In Clock) 20   |

|     | 4.1.11 SDATAINVAL# (System Data In Valid) 2:        |

|     | 4.1.12 SDATAOUTCLK[3:0]# (System Address Out        |

|     | Clock)                                              |

|     | 4.1.13 SYSCLK (System Clock)                        |

|     |                                                     |

| 4.2 | PCI Interface Signals 22                            |

|     | 4.2.1 AD[31:0] (PCI Address/Data Bus)               |

|     | 4.2.2 C/BE[3:0]# (PCI Command/Byte Enables)         |

|     | 4.2.3 DEVSEL# (PCI Device Select)                   |

|     | 4.2.4 FRAME# (PCI Cycle Frame)                      |

|     |                                                     |

|     | 4.2.5 GNT[4:0]# (PCI Bus Grant)                     |

|     | 4.2.6 IRDY# (Initiator Ready)                       |

|     | 4.2.7 LOCK# (PCI Bus Lock)                          |

|     | 4.2.8 PAR (PCI Bus Parity)                          |

|     | 4.2.9 PCLK (PCI Clock)                              |

|     | 4.2.10 PGNT# (PCI Grant to Peripheral Bus           |

|     | Controller)                                         |

|     | 4.2.11 PREQ# (PCI Request from Peripheral Bus       |

|     | Controller)                                         |

|     | 4.2.12 REQ[4:0]# (PCI Bus Request) 2'               |

|     | 4.2.13 RESET# (Reset)                               |

|     | 4.2.14 SERR# (System Error)                         |

|     | 4.2.15 STOP# (PCI Bus Stop)                         |

|     | 4.2.16 TRDY# (Target Ready)                         |

|     | 4.2.17 WSC# (Write Snoop Complete)                  |

|     |                                                     |

| 4.3 | DRAM Interface Signals 30                           |

|     | 4.3.1 CS[5:0]# (Chip Selects)                       |

|     | 4.3.2 DQM[7:0]# (Data Mask)                         |

|     | 4.3.3 MAdA[14:0] and MAdB[14:0] (Memory Address) 30 |

|     | 4.3.4 MCKE[2:0] (SDRAM Clock Enable)                |

|     | 4.3.5 MDAT[63:0] (Memory Data)                      |

|     | 4.3.6 MECCD[7:0] (Memory ECC)                       |

|     |                                                     |

|     | 4.3.7 SCAS[2:0]# (SDRAM Column Address Strobes) 32  |

|     | 4.3.8 SDRAM Clk_In                                  |

|     | 4.3.9 SDRAM Clk_Out                                 |

|     | 4.3.10 SRAS[2:0]# (SDRAM Row Address Strobes)       |

|     | 4.3.11 WE[2:0]# (SDRAM Memory Write Enables) 33     |

| 4.4 | AGP/PCI Signals 34                                  |

|     |                                                     |

|     | 4.4.1 A_AD[31:0] (Address/Data Bus) 34              |

|     | 4.4.2 A_C/BE[3:0]# (PCI Command/Byte Enables) 35    |

*iv* Table of Contents

|   |                | 4.4.3 A_CLK (AGP Clock)               | 35                         |

|---|----------------|---------------------------------------|----------------------------|

|   |                | 4.4.4 A_DEVSEL# (PCI Device Select)   |                            |

|   |                | 4.4.5 A_FRAME# (PCI Cycle Frame)      | 36                         |

|   |                | 4.4.6 A_GNT# (AGP Bus Grant)          |                            |

|   |                | 4.4.7 A_IRDY# (Initiator Ready)       |                            |

|   |                | 4.4.8 A_PAR (PCI Bus Parity)          | 37                         |

|   |                | 4.4.9 A_REQ# (AGP Bus Request)        | 38                         |

|   |                | 4.4.10 A_SERR# (System Error)         | 38                         |

|   |                | 4.4.11 A_STOP# (AGP Bus Stop)         |                            |

|   |                | 4.4.12 A_TRDY# (Target Ready)         | 38                         |

|   | 4.5            | AGP-Only Signals                      | 40                         |

|   |                | 4.5.1 ADSTB[1:0] (AD Bus Strobe)      | 40                         |

|   |                | 4.5.2 PIPE# (APG Pipeline)            | 40                         |

|   |                | 4.5.3 RBF# (Read Buffer Full)         | 41                         |

|   |                | 4.5.4 SBA[7:0] (Sideband Address Bus) | 41                         |

|   |                | 4.5.5 SBSTB (Sideband Strobe)         | 42                         |

|   |                | 4.5.6 ST[2:0] (Status)                | 42                         |

|   | 4.6            | Miscellaneous Signals                 | 43                         |

|   |                | 4.6.1 ROM_SCK (SROM Clock)            | 43                         |

|   |                | 4.6.2 ROM_SDA (SROM Data)             | 43                         |

|   |                | 4.6.3 SCAN_EN# (Scan Enable)          | 43                         |

|   |                | 4.6.4 TRISTATE#                       |                            |

| 5 | Functional Ope | eration                               | 45                         |

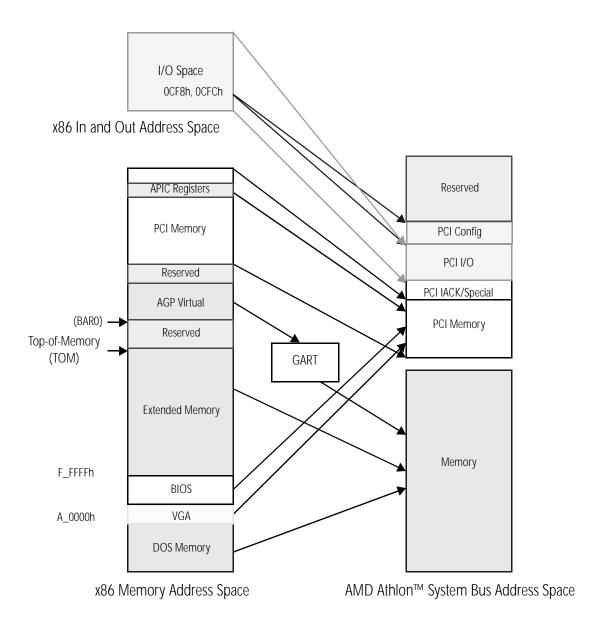

|   | 5.1            | System Addressing                     | 45                         |

|   | 5.2            | Processor Interface                   | <b>53</b>                  |

|   |                | 5.2.1 Bus Interface Unit (BIU)        | 53                         |

|   |                | 5.2.2 BIU Start-Up                    |                            |

|   |                | 5.2.3 Processor Write Posting         |                            |

|   |                | 5.2.4 Read Buffer                     |                            |

|   |                |                                       |                            |

|   | 5.3            | Memory Interface                      | <b>59</b>                  |

|   | 5.3            | ·                                     |                            |

|   | 5.3            | 5.3.1 Memory Request Organizer (MRO)  | 59                         |

|   | 5.3            | 5.3.1 Memory Request Organizer (MRO)  | 59<br>63                   |

|   | 5.3            | 5.3.1 Memory Request Organizer (MRO)  | 59<br>63<br>65             |

|   | 5.3            | 5.3.1 Memory Request Organizer (MRO)  | 59<br>63<br>65<br>67       |

|   | 5.3            | 5.3.1 Memory Request Organizer (MRO)  | 59<br>63<br>65<br>67<br>71 |

Table of Contents

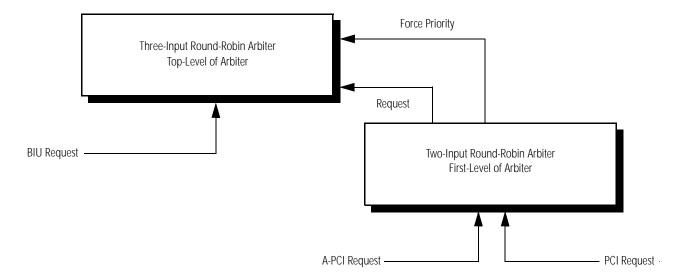

|   | 5.4              | PCI Bus Controller                                                                                                                                                                                                                                                                                                                                                                     | . 78                                 |

|---|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

|   |                  | 5.4.1 Memory Coherency 5.4.2 PCI Arbitration 5.4.3 PCI Configuration 5.4.4 PCI Southbridge Signals 5.4.5 PCI Parity/ECC Errors 5.4.6 PCI-to-Memory/PCI-from-Memory and Other PCI Targets 5.4.7 PCI-to-Processor Bus Read Transactions 5.4.8 Processor-to-PCI Bus Write Transactions 5.4.9 PCI Accesses by An Initiator                                                                 | . 79<br>. 79<br>. 80<br>. 80<br>. 81 |

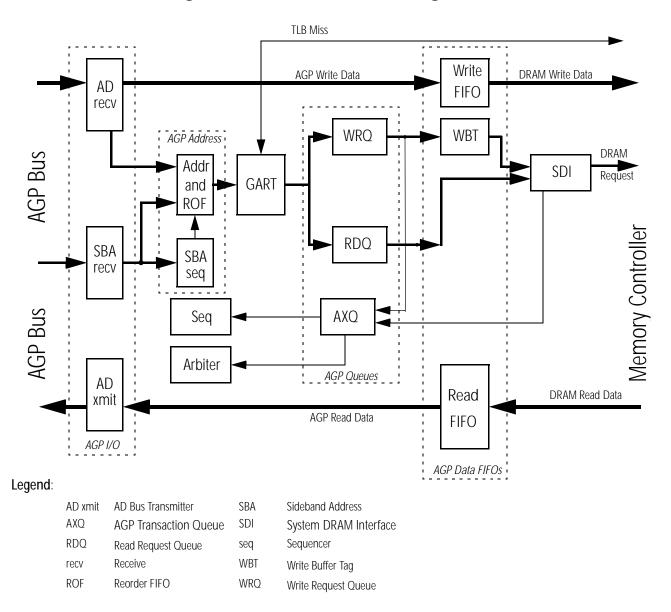

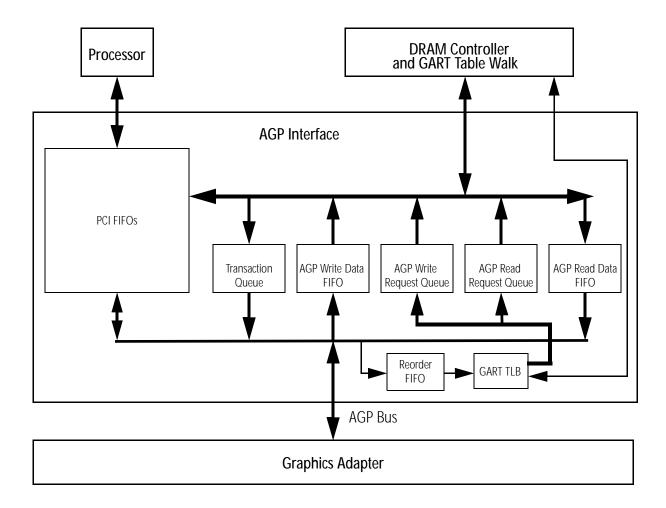

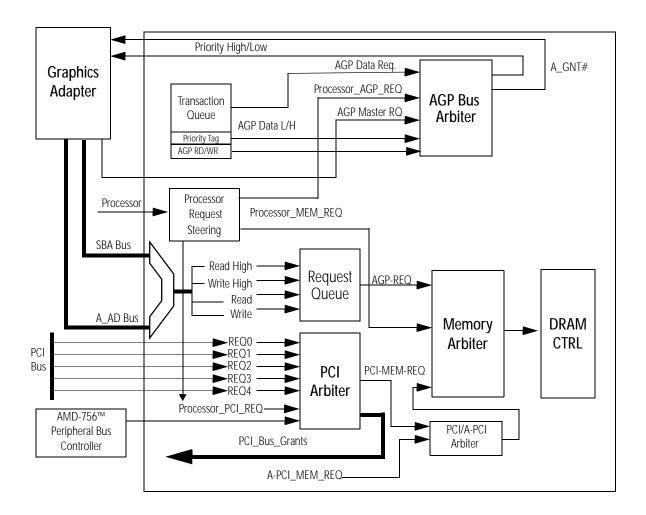

|   | 5.5              | Accelerated Graphics Port (AGP)                                                                                                                                                                                                                                                                                                                                                        | . 83                                 |

|   |                  | <ul> <li>5.5.1 AGP Block Diagram</li> <li>5.5.2 The AGP Queues</li> <li>5.5.3 AGP System DRAM Interface (SDI)</li> <li>5.5.4 AGP Arbitration</li> <li>5.5.5 AGP Data</li> <li>5.5.6 PCI Transactions on the AGP Bus</li> <li>5.5.7 Graphics Adapters and Main Memory</li> <li>5.5.8 AGP Virtual Address Space (Aperture) Range and Size</li> <li>5.5.9 GART Cache Operation</li> </ul> | . 86<br>. 90<br>. 91<br>. 93<br>. 94 |

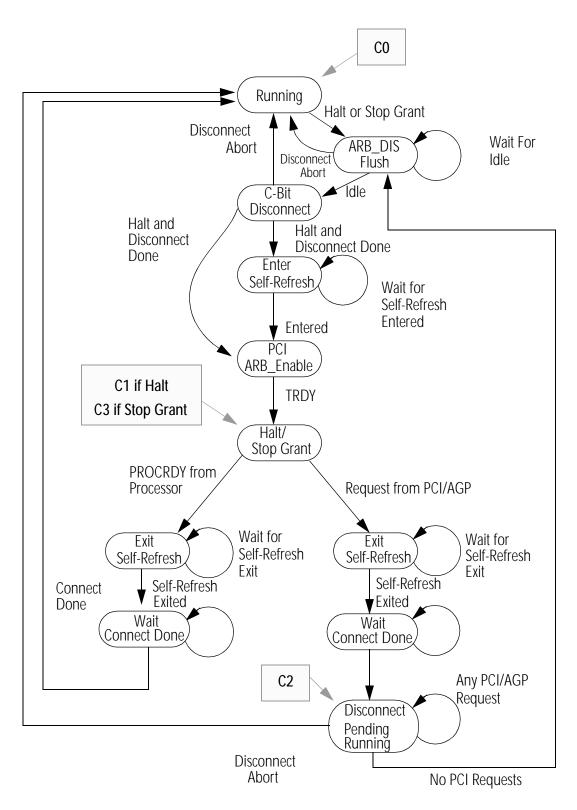

|   | 5.6              | Power Management                                                                                                                                                                                                                                                                                                                                                                       | 106                                  |

|   | 5.7              | Phase Locked Loop (PLL) Features                                                                                                                                                                                                                                                                                                                                                       | 110                                  |

| 5 | Typical Settings |                                                                                                                                                                                                                                                                                                                                                                                        | 111                                  |

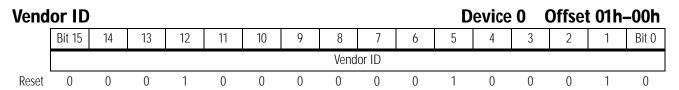

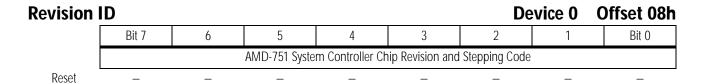

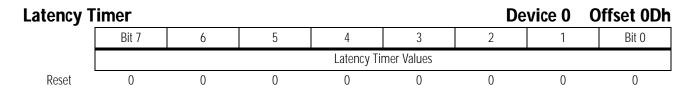

| 7 | Configuration R  | egisters                                                                                                                                                                                                                                                                                                                                                                               | 123                                  |

|   | 7.1              | PCI Configuration Mechanism                                                                                                                                                                                                                                                                                                                                                            | 123                                  |

|   | 7.2              | Register Overview                                                                                                                                                                                                                                                                                                                                                                      | 126                                  |

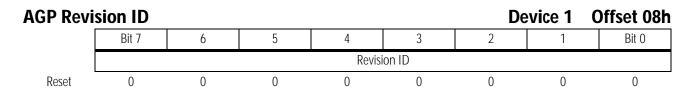

|   |                  | 7.2.1 Revision ID Nomenclature                                                                                                                                                                                                                                                                                                                                                         | 129                                  |

|   | 7.3              | Function 0, Device 0 Registers (Processor-to-PCI Bridge, Memory Controller, etc.)                                                                                                                                                                                                                                                                                                      | 130                                  |

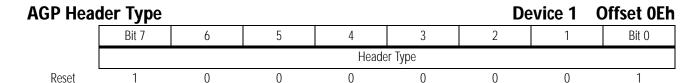

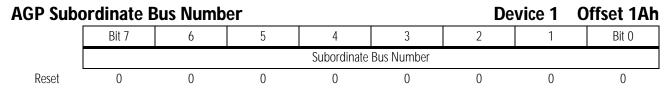

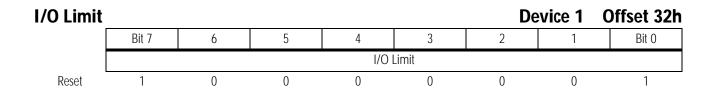

|   | 7.4              | Device 1 Registers (AGP and PCI-to-PCI Bridge)                                                                                                                                                                                                                                                                                                                                         | 161                                  |

|   | 7.5              | Memory-Mapped Control Registers                                                                                                                                                                                                                                                                                                                                                        | 173                                  |

vi Table of Contents

| 8   | <b>Electrical Da</b> | ıta    |                                             | 179 |

|-----|----------------------|--------|---------------------------------------------|-----|

|     | 8.                   | .1     | Absolute Ratings                            | 179 |

|     | 8.                   | .2     | Operating Ranges                            | 180 |

|     | 8.                   | .3     | DC Characteristics                          | 181 |

|     | 8.                   | .4     | Power Dissipation                           | 183 |

|     |                      |        | 8.4.1 Thermal Considerations                | 183 |

| 9   | Switching Ch         | harac  | eteristics                                  | 185 |

|     | 9.                   | .1     | SYSCLK Switching Characteristics            | 186 |

|     | 9.                   | .2     | Valid Delay, Float, Setup, and Hold Timings | 188 |

|     | 9.                   | .3     | PCI Interface Timings                       | 189 |

|     | 9.                   | .4     | SDRAM Interface Timings                     | 190 |

|     | 9.                   | .5     | AGP Interface Timings                       | 191 |

|     | 9.                   | .6     | AMD Athlon System Bus Timings               | 193 |

| 10  | I/O Buffer Cl        | hara   | cteristics                                  | 195 |

|     | 10                   | 0.1    | I/O Buffer Model                            | 195 |

|     | 10                   | 0.2    | I/O Model Application Note                  | 196 |

|     | 10                   | 0.3    | I/O Buffer AC and DC Characteristics        | 196 |

| 11  | Pin Designat         | tions  |                                             | 197 |

| 12  | Package Spe          | cifica | ations                                      | 201 |

| App | endix A Conv         | venti  | ions, Abbreviations, and References         |     |

|     |                      |        | Signals and Bits                            | 205 |

|     |                      |        | Data Terminology                            | 206 |

|     |                      |        | Abbreviations and Acronyms                  | 207 |

|     |                      |        | Related Publications                        | 212 |

|     | Index                |        |                                             | 213 |

Table of Contents

21910E-March 2000

viii Table of Contents

# **List of Figures**

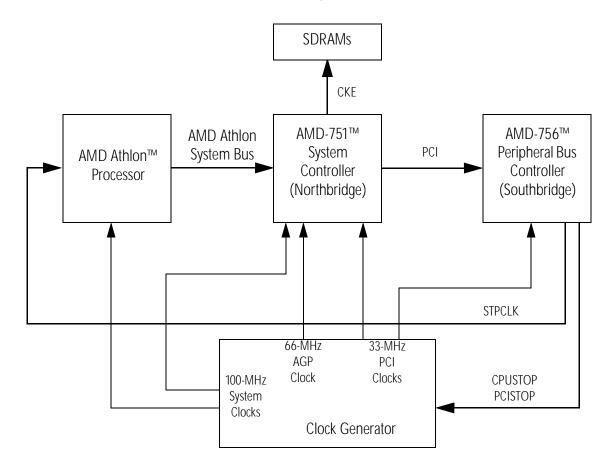

| Figure 1.  | AMD-750™ Chipset System Block Diagram              |

|------------|----------------------------------------------------|

| · ·        | • •                                                |

| Figure 2.  | AMD-751™ System Controller Block Diagram           |

| Figure 3.  | AMD Athlon™ Processor-Based System Clocking        |

| Figure 4.  | Ordering Information Elements                      |

| Figure 5.  | System Memory View                                 |

| Figure 6.  | Address Mapping for x86 Legacy47                   |

| Figure 7.  | Block Diagram of the Bus Interface Unit (BIU) 53   |

| Figure 8.  | SIP Protocol                                       |

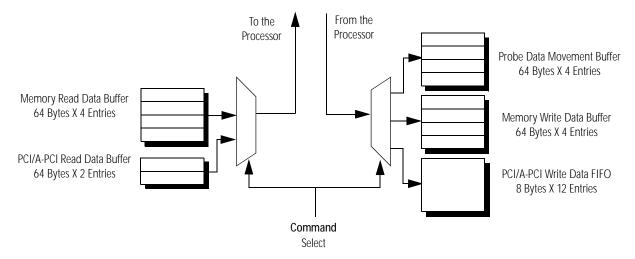

| Figure 9.  | AMD Athlon System Bus Data Buffers (BIU)58         |

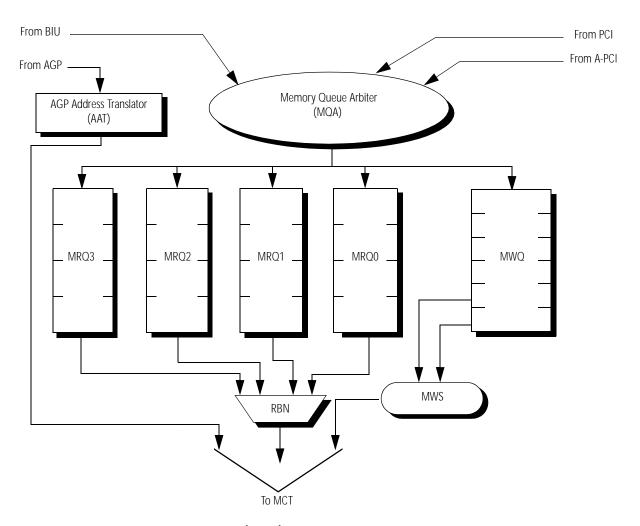

| Figure 10. | Memory Request Organizer (MRO) Block Diagram60     |

| Figure 11. | Memory Queue Arbiter (MQA) Block Diagram 61        |

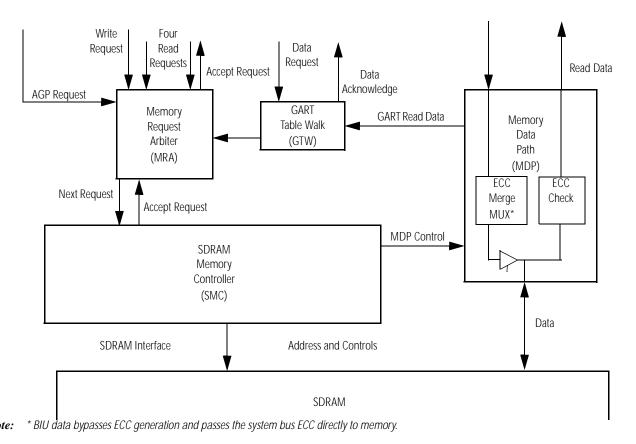

| Figure 12. | Memory Controller (MCT) Block Diagram 63           |

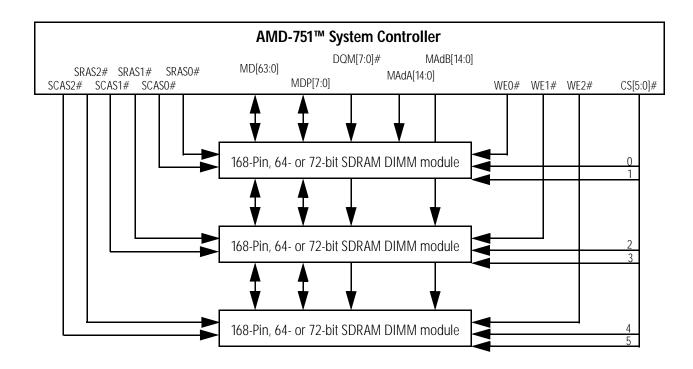

| Figure 13. | SDRAM Interface Example67                          |

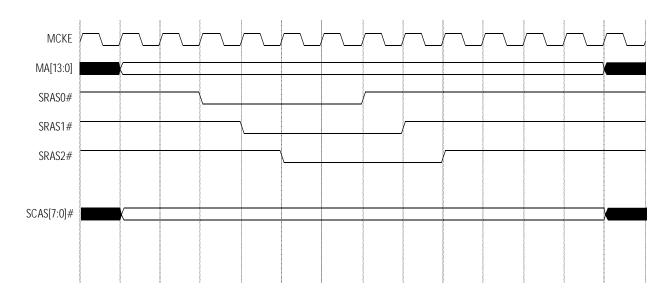

| Figure 14. | DRAM Refresh Timing                                |

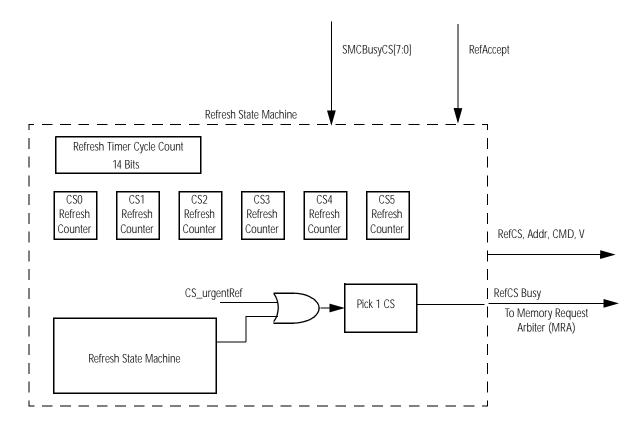

| Figure 15. | Refresh Timer and Counters69                       |

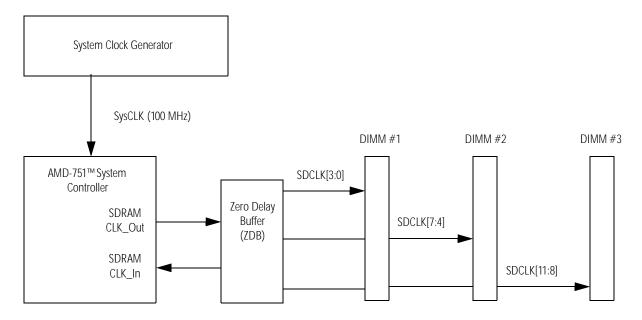

| Figure 16. | AMD-751 System Controller Clocking Scheme          |

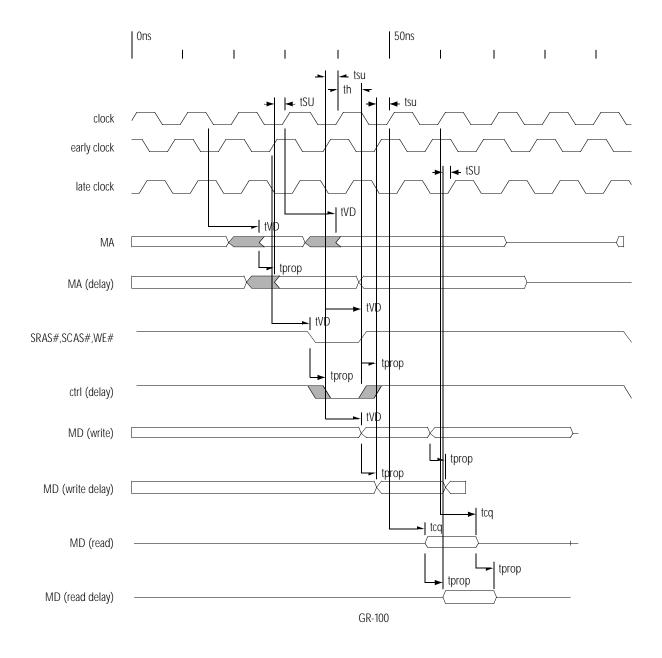

| Figure 17. | 100-MHz SDRAM Detailed Timing                      |

| Figure 18. | AGP Block Diagram85                                |

| Figure 19. | AGP Queues and Buffers                             |

| Figure 20. | AMD-751 System Controller Arbiters                 |

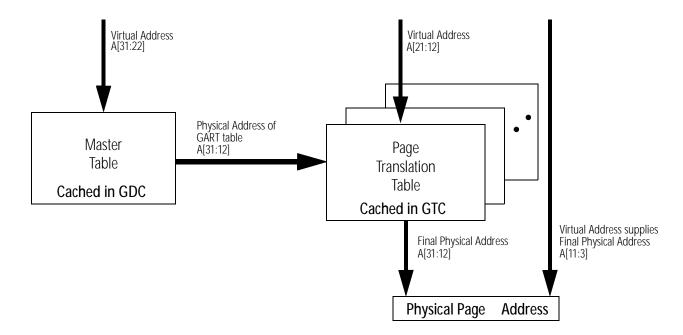

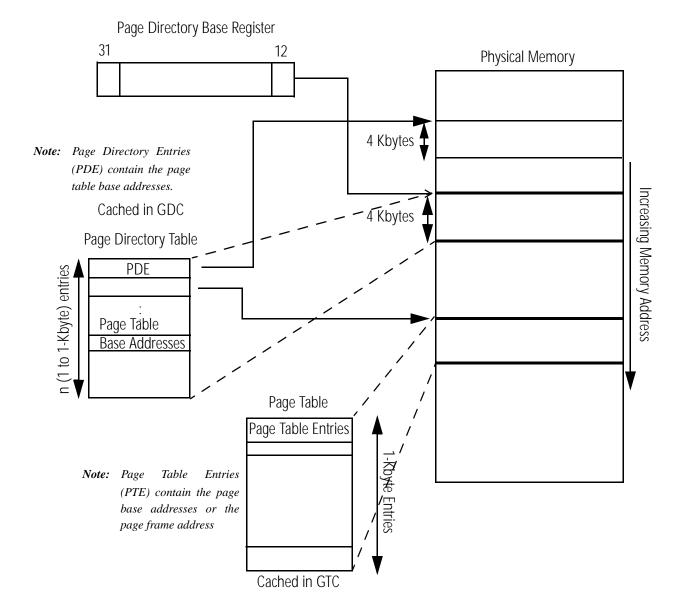

| Figure 21. | Address Remapping94                                |

| Figure 22. | Cache Hierarchy (Conventional Two-Level Scheme) 96 |

| Figure 23. | Conventional GART Scheme—Multiple Tables 96        |

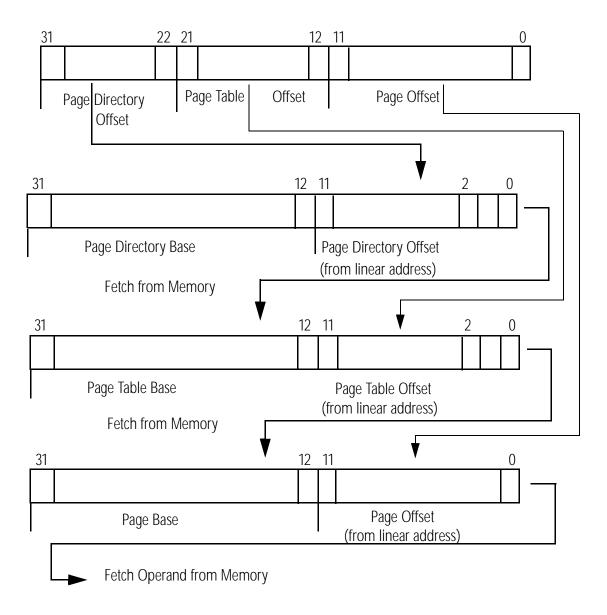

| Figure 24. | Page Translation Structures97                      |

| Figure 25. | Page Directory Entry (PDE) Definition              |

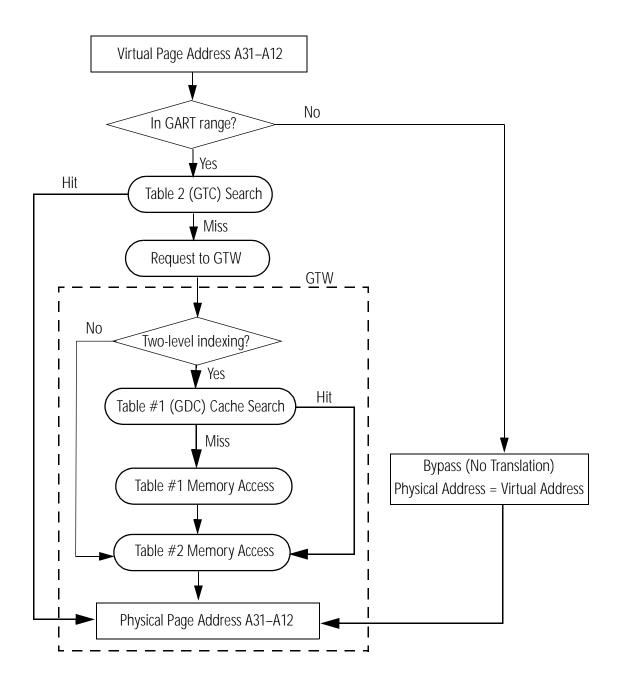

| Figure 26. | Address Translation Flow Chart                     |

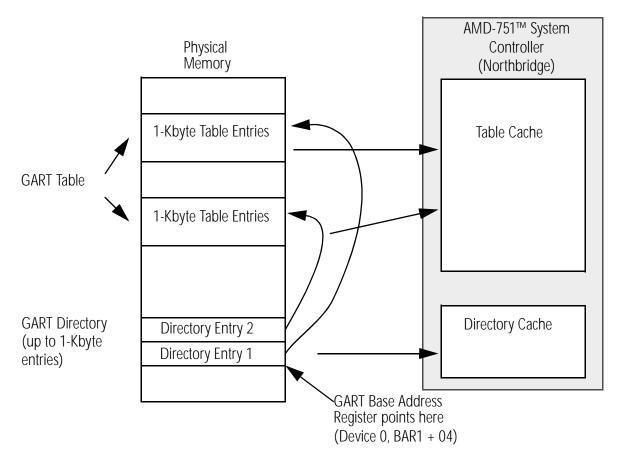

| Figure 27. | Two-Level GART Translation Scheme                  |

| Figure 28. | Another View Of the Two-Level Indexing Scheme 104  |

| Figure 29. | Power Management Signal Connections 106            |

| Figure 30. | ACPI Power States                                  |

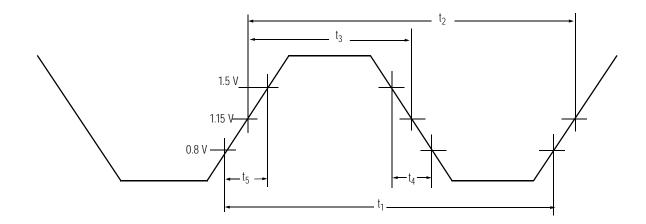

| Figure 31. | SYSCLK Waveform186                                 |

| Figure 32. | CLK Waveform187                                    |

|            |                                                    |

List of Figures ix

## Preliminary Information

AMD-751™ System Controller Data Sheet

21910E-March 2000

| Figure 33. | Setup, Hold, and Valid Delay Timings | 188 |

|------------|--------------------------------------|-----|

| Figure 34. | Test Circuit                         | 194 |

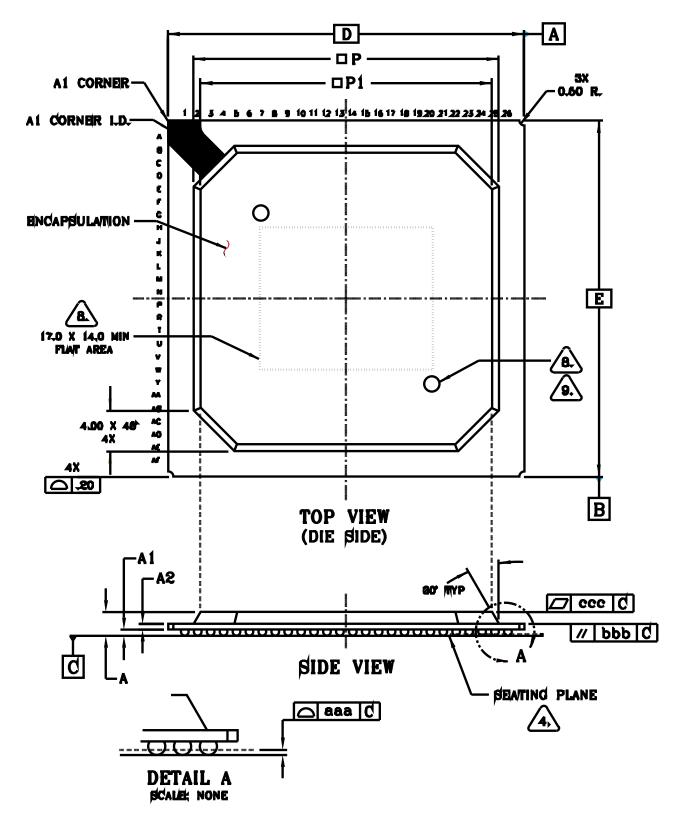

| Figure 35. | Bottom Side View of Package          | 201 |

| Figure 36. | Top and Side Views of Package        | 202 |

X List of Figures

# **List of Tables**

| Table 1.  | SDRAM Organizations Supported9                               |

|-----------|--------------------------------------------------------------|

| Table 2.  | GART Table-Cache Sizes11                                     |

| Table 3.  | AMD-751™ System Controller Interface Voltages                |

| Table 4.  | Valid Combinations for Ordering Parts15                      |

| Table 5.  | AMD-751 System Controller Memory Address Map46               |

| Table 6.  | AMD Athlon <sup>TM</sup> Processor Special Cycle Encoding 48 |

| Table 7.  | SIP Protocol States and Actions                              |

| Table 8.  | SDRAM Memory Organizations                                   |

| Table 9.  | PC-100 REV. 1.0 SDRAM DIMM Part Nomenclature72               |

| Table 10. | SDRAM DIMM Loading Analysis                                  |

| Table 11. | Key SDRAM DIMM Timing Variables                              |

| Table 12. | Summary of GART Terms                                        |

| Table 13. | Mask Bits99                                                  |

| Table 14. | AMD-751 System Controller MSR Settings111                    |

| Table 15. | Configuration Port Register Summary125                       |

| Table 16. | Function 0, Device 0 Configuration Registers126              |

| Table 17. | Function 0, Device 1 Configuration Registers128              |

| Table 18. | Memory Space Configuration Registers (BAR1 + n) 129          |

| Table 19. | Power Management Configuration Registers (BAR2 + n)129       |

| Table 20. | Revision ID Enumeration                                      |

| Table 21. | Size Field versus AGP Memory Allocation                      |

| Table 22. | Mapping Processor Address Lines to Memory Address            |

|           | Lines                                                        |

| Table 23. | Absolute Ratings                                             |

| Table 24. | <b>Operating Ranges180</b>                                   |

| Table 25. | DC Characteristics                                           |

| Table 26. | AMD Athlon System Bus/AMD-751 System Controller DC           |

|           | Specification                                                |

| Table 27. | Typical and Maximum Power Dissipation                        |

| Table 28. | Heatsinks for the AMD-751 System Controller183               |

| Table 29. | Thermal Interface Material for the AMD-751 System            |

|           | Controller                                                   |

List of Tables xi

21910E-March 2000

| Table 30. | SYSCLK Switching Characteristics for 100-MHz Bus           |    |

|-----------|------------------------------------------------------------|----|

|           | Operation                                                  | 86 |

| Table 31. | A_CLK Switching Characteristics for 66-MHz Bus             |    |

|           | Operation                                                  | 87 |

| Table 32. | PCLK Switching Characteristics for 33-MHz PCI Bus 18       | 87 |

| Table 33. | PCI Interface Timings                                      | 89 |

| Table 34. | DRAM Interface Timing                                      | 90 |

| Table 35. | AGP 1x Mode Timings                                        | 91 |

| Table 36. | AGP 2x Mode Timings                                        | 92 |

| Table 37. | AMD Athlon System Bus/AMD-751 System Controller AC         |    |

|           | Specification19                                            | 93 |

| Table 38. | Symbol Notes                                               | 03 |

| Table 39. | 492-Pin PBGA 35.0 mm By 35.0 mm Package Specifications. 20 | 03 |

| Table 40. | Geometric Tolerances                                       | 04 |

| Table 41. | Abbreviations                                              | 07 |

| Table 42. | Acronyms                                                   | 08 |

|           |                                                            |    |

xii List of Tables

# **Revision History**

| Date        | Rev | Description                                                                                                                                                                                        |  |  |

|-------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|             |     | Added cross reference to the <i>AMD-751™ System Controller Memory Settings Application Note</i> , order# 22835 to "SDRAM Initialization" on page 70.                                               |  |  |

|             |     | Added "Revision ID Nomenclature" on page 129.                                                                                                                                                      |  |  |

| March 2000  | E   | Changed note in Table 16, "Function 0, Device 0 Configuration Registers," on page 126 and "Revision ID Device 0 Offset 08h" on page 133 to cross-reference "Revision ID Nomenclature" on page 129. |  |  |

|             |     | Added <i>Queue</i> to name for Bypass Enable bit in "BIU Control and Status Register Device 0 Offset 63h–60h" on page 147.                                                                         |  |  |

|             |     | Moved "Conventions, Abbreviations, and References" from front of book to "Appendix A" on page 205.                                                                                                 |  |  |

| August 1999 | D   | Initial public release                                                                                                                                                                             |  |  |

Revision History xiii

21910E-March 2000

*xiv* Revision History

# 1 Features

The AMD Athlon™ processor powers the next generation in computing platforms, delivering the ultimate performance for cutting-edge applications and an unprecedented computing experience.

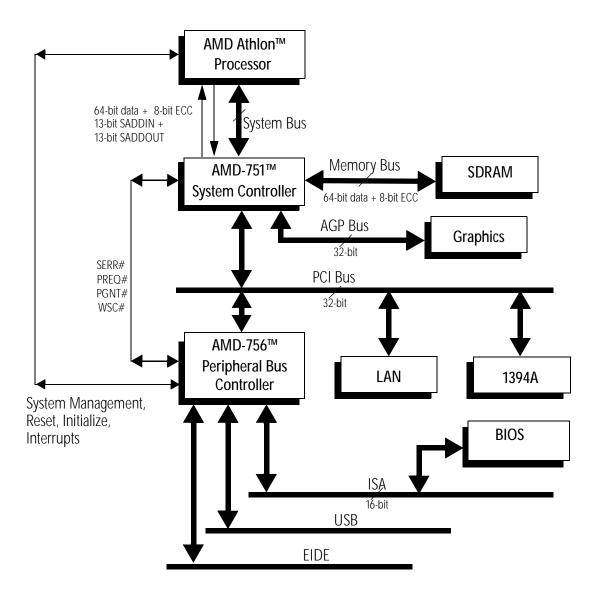

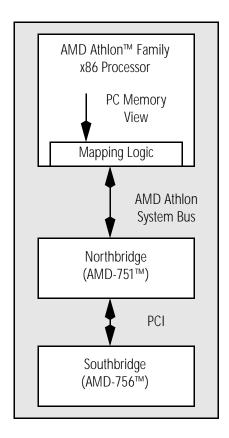

The AMD-750™ chipset is a highly integrated system logic solution that delivers enhanced performance for the AMD Athlon processor and other AMD Athlon system bus-compatible processors. The AMD-750 chipset consists of the AMD-751™ system controller in a 492-pin plastic ball-grid array (PBGA) package and the AMD-756™ peripheral bus controller. The AMD-751 system controller features the AMD Athlon system bus, system memory controller, accelerated graphics port (AGP) controller, and peripheral component interconnect (PCI) bus controller. Figure 1 on page 6 shows a block diagram for the AMD-750 chipset.

The AMD-751 system controller is designed with the following features:

- The AMD Athlon system bus supports three 200-MHz high-speed channels

- The 33-MHz 32-bit PCI 2.2-compliant bus interface supports up to six masters

- The 66-MHz AGP 2.0-compliant interface supports 2x data transfer mode

- High-speed memory—The AMD-751 system controller is designed to support a 100-MHz PC-100 Rev. 1.0 SDRAM DIMMs

This document describes the features and operation of the AMD-751 system controller. For a description of the AMD-756 peripheral bus controller, see the  $AMD-756^{TM}$  Peripheral Bus Controller Data Sheet, order# 21645. Key features of the AMD-751 system controller are provided in this section.

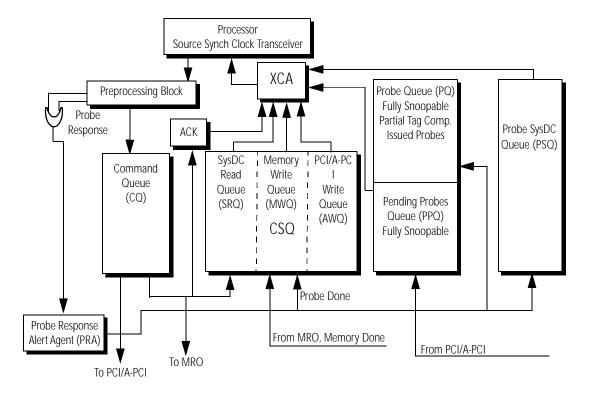

# 1.1 AMD Athlon™ System Bus

The AMD Athlon system bus has the following features:

- High-performance point-to-point system bus topology

- Source-synchronous clocking for high-speed transfers

- HSTL-like low-voltage swing transceiver logic signal levels

- Three 200-MHz independent high-speed channels:

- 13-pin processor request channel

- 13-pin system probe channel

- 72-pint data transfer channel (8-bit ECC)

- 1.6 Gigabyte per second peak data transfer rates at 200 MHz

- Large 64-byte (cache line) data burst transfers

- Data Buffers:

- Memory write FIFO (MWF)

- Memory read FIFO (MRF)

- PCI/APCI (AGP-PCI) write buffer

- PCI/APCI read buffer

- Transaction Queues:

- Command queue (CQ)

- Memory write queue (MWQ)

- Memory read queue (MRQ)

- Probe (snoop) queue (PQ)

# 1.2 Integrated Memory Controller

The integrated memory controller has the following features:

- Memory Request Organizer (MRO)—Serves as a data crossbar, determines request dependencies, and optimizes scheduling of memory requests

- The AMD-751 system controller supports the following concurrences:

- Processor-to-main-memory with PCI-to-main-memory

- Processor-to-main-memory with AGP-to-main-memory

- Processor-to-PCI with PCI-to-main-memory or AGP-to-main-memory

- Memory error correcting code (ECC) support

- Supports the following DRAM:

- Up to three non-buffered PC-100 Rev. 1.0 SDRAM DIMMs using 16-Mbit, 64-Mbit, and 128-Mbit technology (See Table 1 on page 9)

- 64-bit data width, plus 8-bit ECC paths

- Flexible row and column addressing

- Supports up to 768 Mbytes of memory

- Four open pages within one CS (device selected by chip select) for one quadword

- Default two-page leapfrog policy for eight quadword requests

- BIOS-configurable memory-timing parameters and configuration parameters

- 3.3-V memory interface operation with no external buffers

- Four cache lines of processor-to-DRAM posted write buffers with full read-around capability

- Concurrent DRAM writeback and read-around-write

- Burst read and write transactions

- Decoupled and burst DRAM refresh with staggered CS timing

- Provides the following refresh options:

- Programmable refresh rate

- CAS-before-RAS

- · Populated banks only

- Chipset powerdown via SDRAM automatic refresh command

- Automatic refresh of idle slots—improves bus availability for memory access by the processor or system

## 1.3 PCI Bus Controller

The PCI bus controller has the following features:

- Compliance with PCI Local Bus Specification, Revision 2.2

- Supports six PCI masters

- 32-bit interface, compatible with 3.3-V and 5-V PCI I/O

- Synchronous PCI bus operation up to 33 MHz

- PCI-initiator peer concurrence

- Automatic processor-to-PCI burst cycle detection

- Four-entry, 64-bit PCI master (processor or AGP) write FIFO

- Extensive utilization of FIFOs

- Zero wait-state PCI initiator and target burst transfers

- PCI-to-DRAM data streaming up to 132 Mbytes per second

- Enhanced PCI command optimization, such as memory read line (MRL), memory read multiple (MRM), and memory-write-and-invalidate (MWI)

- Timer-enforced fair arbitration between PCI initiators

- Supports advanced concurrency

- Supports retry disconnect for improved bus utilization

- PCI read buffer keeps track of each master

- PCI target request queue

## 1.4 AGP Features

The AGP features include the following:

- Bus Features

- Compliance with AGP 2.0 specification

- Synchronous 66-MHz 1x and 2x data-transfer modes

- Multiplexed and demultiplexed transfers

- Up to four pipelined grants

- Support of sideband address (SBA) bus

- Request Queue Features

- Separate read-request and write-request queues

- Reordering of high-priority requests over low-priority requests in queue

- Simultaneous issuing of requests from both the write queue and read queue

- Selects next request to optimize bus utilization

- Transaction Queues

- Memory-to-AGP and processor-to-AGP transaction queues

- FIFO Features

- 16-entry (64-bit) AGP-to-memory write FIFO

- 64-entry (64-bit) memory-to-AGP read FIFO

- Secondary PCI Bus Features

- Pipelined burst reads and writes

- Extensive utilization of FIFOs

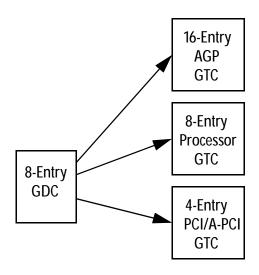

- GART (graphics address remapping table) Features

- · Conventional (two-level) GART scheme

- Eight-entry, fully-associative GART table cache (GTC)

- Three fully-associative GART directory caches (GDC)

- One 4-entry for PCI

- One 8-entry for the processor

- One 16-entry for AGP

# 1.5 Power Management

The power management features include the following:

- Compliance support for both ACPI and Microsoft<sup>®</sup> PC 98 power management

- The AMD-751 system controller supports the following power states:

- · Processor Halt/Stop Grant/Sleep states

- Power-On Suspend

Figure 1. AMD-750™ Chipset System Block Diagram

# 2 Overview

The AMD-751 system controller is designed to optimize the interaction between the processor, DRAM, AGP, and the PCI bus with pipelined burst and concurrent transactions. Each bus interface includes multiple specialized FIFO buffers to enable optimum system concurrency. In the AMD-751, AMD has introduced a memory-request organizer to optimize the bandwidth of the DRAM. The AMD-751 system controller implements the AGP to provide streamlined 3D renderings and reduce graphics memory requirements. The AMD-751 is packaged in a 492-pin PBGA.

# 2.1 System

The AMD-751 system controller is capable of performing I/O transactions, single-access memory transactions, and block-access memory transactions. The AMD Athlon system bus is a split-transaction bus. A split-transaction bus optimizes system throughput by allowing the AMD-751 system controller to schedule tasks and thereby free the bus during resource delays.

The system controller responds only to I/O cycles within its configuration-register space and to memory requests as defined in its configuration registers.

All timing on the system bus is derived from the system clock (SYSCLK).

#### 2.1.1 Processor Interface

The AMD Athlon system bus consists of three independent high-speed channels, including a 72-bit, 200-MHz, point-to-point, non-multiplexed, source-synchronous clocked data transfer channel capable of supporting the AMD Athlon processor with transfer rates of 1.6 Gigabyte per second. To achieve higher speed data transfers, the AMD Athlon system bus uses an open-drain, HSTL-like signaling level. Source-synchronous clocking compensates for PC board propagation delays to enable higher speed transfers.

The AMD-751 processor interface responds to processor commands, issues probes, and controls all data movement into and out of the processor. More details on the processor interface can be found in Chapter 5, "Functional Operation" starting on page 45.

## 2.1.2 Memory Controller

The AMD-751 system controller incorporates a high-performance DRAM controller with a memory-request organizer that provides the DRAM interface for an AMD Athlon processor and can support PC-100 Rev. 1.0 SDRAM DIMMs at 100 MHz. The memory-request organizer serves as a data crossbar and determines request dependencies to provide optimum scheduling of memory requests. Large on-chip FIFOs are used to decouple requests and provide concurrency. These features combine with the split-transaction processor bus to facilitate optimum use of the bus and memory bandwidths. The memory controller can address up to three slots of SDRAM at 100 MHz in various combinations, up to a total of 768 Mbytes.

The AMD-751 system controller supports the following concurrencies:

- Processor-to-main-memory with PCI-to-main-memory

- Processor-to-main-memory with AGP-to-main-memory

- Processor-to-PCI-memory with PCI-to-main-memory or AGP-to-main-memory

PC-100 Rev. 1.0 SDRAMs DIMMs allow fast bursting of data between the DRAM and the internal controller data buffers at 100 MHz. The DRAM controller supports a 72-bit data path to memory and can be configured to support error correcting code (ECC), which can correct single-bit errors and detect double-bit errors for data integrity. The BIOS must determine the type of memory installed and program the configuration registers accordingly.

The AMD-751 supports the SDRAM types shown in Table 1 on page 9. It does not support x32 DRAM configurations in the 16-Mbit technology. The AMD-751 logically supports the x4 configuration, but it is not recommended with unbuffered DIMMs.

| Table 1. SUKAIVI OLYAHIZALIOHS SUPPOLLEU |         |            |  |

|------------------------------------------|---------|------------|--|

| SDRAM Organization                       | Banks   | Addressing |  |

| 16M x 4                                  | 2       | 10 x 11    |  |

| 16M x 8                                  | 2       | 9 x 11     |  |

| 16M x 16                                 | 2       | 8 x 11     |  |

| 16M x 32                                 | Not Sup | ported     |  |

| 64M x 4                                  | 4       | 10 x 12    |  |

| 64M x 4                                  | 2       | 10 x 13    |  |

| 64M x 8                                  | 4       | 9 x 12     |  |

| 64M x 8                                  | 2       | 9 x 13     |  |

| 64M x 16                                 | 4       | 8 x 12     |  |

| 64M x 16                                 | 2       | 8 x 13     |  |

| 64M x 32                                 | 4       | 7 x 12     |  |

| 64M x 32                                 | 2       | 7 x 13     |  |

| 128M x 4                                 | 4       | 11 x 12    |  |

| 128M x 8                                 | 4       | 10 x 12    |  |

| 128M x 16                                | 4       | 9 x 12     |  |

| 40014 00                                 |         | 0 10       |  |

128M x 32

Table 1. SDRAM Organizations Supported

For more details on the memory controller, see Chapter 5, "Functional Operation" starting on page 45.

8 x 12

## 2.1.3 PCI Controller

The AMD-751 system controller is compatible with the *PCI Local Bus Specification, Revision 2.2*. It can operate at either 3.3 V or 5 V, and offers 64-bit to 32-bit data conversion. The AMD-751 supports up to six external PCI masters.

The AMD-751 implements a very high degree of internal concurrency. However, all PCI-to-memory transactions are, by definition, coherent and therefore must be snooped in all processors.

Five separate PCI FIFOs containing over 300 bytes of storage are utilized to facilitate concurrency. In addition, the AMD-751 prefetches eight quadwords (one AMD Athlon processor cache line) when performing memory reads for a PCI master.

Enhanced PCI bus commands, such as memory read line (MRL), memory read multiple (MRM), and memory

write-and-invalidate (MWI), maximize data throughput. The AMD-751 system controller employs a variety of techniques to minimize PCI initiator read latency and DRAM utilization. The combination of these features allows a PCI initiator to achieve the full 133-Mbyte burst transfer rate. In addition, the AMD-751 contains a PCI arbiter. See Chapter 5, "Functional Operation" starting on page 45 for more information.

## 2.1.4 Accelerated Graphics Port (AGP)

The accelerated graphics port (AGP) is an alternate interface bus for a computer system. The AGP provides a point-to-point link between a graphics controller and the memory controller. This additional pathway to memory removes 3D graphics traffic from the PCI bus and provides a special access path to main memory, allowing it to function as part of graphics memory and reducing the amount of memory required on the graphics adapter. Typically, the section of main memory allocated for the AGP adapter would then be used to hold 'textures', improving the realism of 3D images.

The AGP bus is essentially an expansion of the standard PCI local bus containing additional sideband signals and commands. The three primary enhancements to PCI include pipelined memory requests, separate address and data buses, and double-pumped (2x) AC timing mode, in which data is transferred on both edges of the AGP clock. Double-pumping enables effective transfer rates as high as 133 MHz, generating an effective data transfer rate of up to 533 Mbytes/second.

The AGP bus supports PCI as well as AGP transfers. As usual, the A\_FRAME# signal indicates PCI transfers, while a new signal, PIPE#, is used to signify AGP transfers. To avoid confusion in this document, the system-wide PCI bus is referred to as the primary PCI bus, and the PCI implementation on the AGP bus is referred to as the secondary PCI bus or A-PCI.

The AMD-751 implements an AGP 1.0-compliant interface, which provides a 32-bit-wide data path operating at either 66 MHz or 133 MHz. The AMD-751 can queue 16 outstanding AGP transactions. See Chapter 5, "Functional Operation" starting on page 45 for more information.

The AMD-751 system controller functions as a PCI target on the AGP bus. When the AGP bus functions in AGP mode, the graphics controller is the AGP initiator and the AMD-751, which contains the memory controller, functions as the AGP target.

The AMD-751 implements a full-featured graphics-address remapping table (GART). As shown in Table 2, this GART implementation is distributed with individual table caches at each interface and a common directory cache in the table-walk logic that contains four fully associative entries. See Chapter 5, "Functional Operation" starting on page 45 for more details on the GART.

Table 2. GART Table-Cache Sizes

| Interface   | GART Table-Cache Size/Organization |  |

|-------------|------------------------------------|--|

| AGP         | 16 Entries, fully associative      |  |

| PCI & A-PCI | 4 Entries, fully associative       |  |

| Processor   | 8 Entries, fully associative       |  |

21910E – March 2000

## 2.1.5 Block Diagram

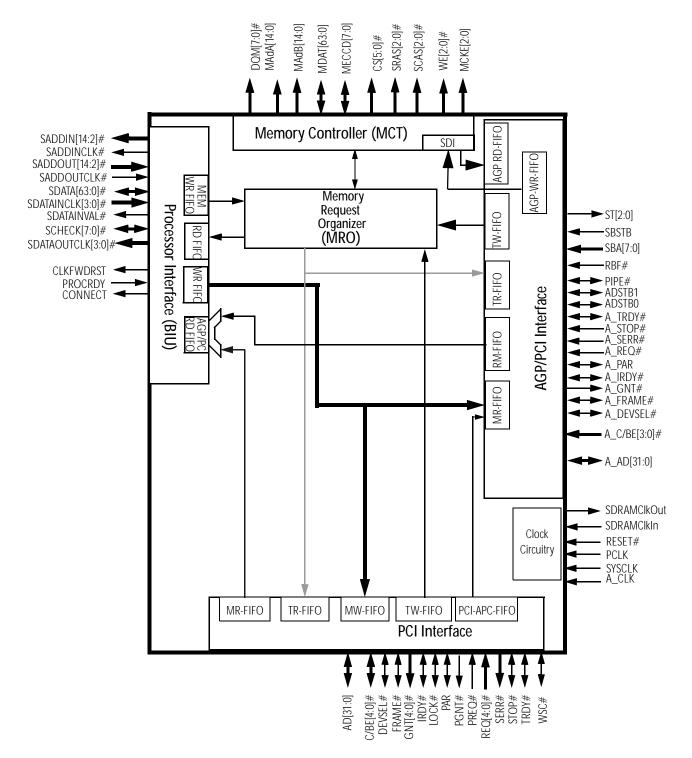

Figure 2 shows the full complement of features and functions built into the AMD-751 system controller system logic.

Figure 2. AMD-751™ System Controller Block Diagram

## 2.1.6 Package

The AMD-751 is packaged in a 492-ball, 35-mm plastic ball grid array (PBGA).

#### **2.1.7** Power

The AMD-751 operates from a 3.3-V  $V_{dd}$  supply and dissipates 4.5 watts (W) operating under worst-case conditions. (Maximum  $V_{dd}$  is with heavy bus traffic.)

The AMD-751 implements the power-on-suspend (POS) power management state. To implement the POS state, the AMD-751 provides two facilities—SDRAM self-refresh and PCI master grant suspend.

SDRAMs are put in a self-refresh mode by the deassertion of the MCKE[2:0] pins. The AMD-751 enters that mode in a Stop Grant state. Careful routing of this signal on the board is important to ensure that it stays clean when it is asserted or deasserted. PCI master grants are disabled via register bit 0 in BAR2 offset 0h (see page 177).

## 2.2 Interface Levels

A complete pinout is shown in Chapter 12, "Package Specifications" on page 201. The rough grouping of signal types is shown in Table 3.

Table 3. AMD-751™ System Controller Interface Voltages

| Interface | Group | Voltages                    |  |

|-----------|-------|-----------------------------|--|

| Processor | OD    | Open drain, pulled to 1.6 V |  |

| SDRAM     | LVTTL | 3.3 V                       |  |

| PCI       | PCI   | 3.3 V, 5 V tolerant         |  |

| AGP       | AGP   | 3.3 V                       |  |

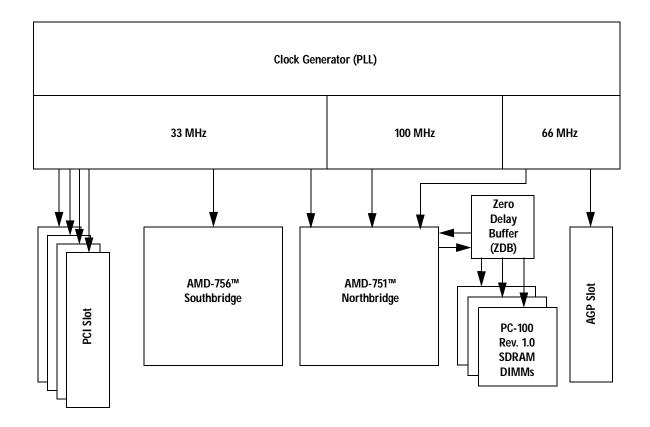

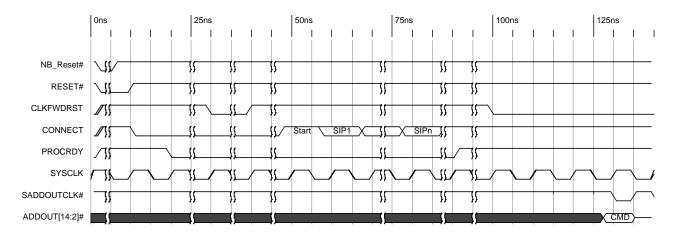

# 2.3 Clocking

The AMD-751 system controller receives a 100-MHz system clock and a 33-MHz PCI clock. The AMD-751 generates and drives the 100-MHz SDRAM clocks through a zero-delay buffer. The 66-MHz AGP clock is provided by the system clock generator as shown in Figure 3. It uses a non-JTAG, partial-scan scheme for silicon and motherboard testability (NAND tree).

Figure 3. AMD Athlon™ Processor-Based System Clocking

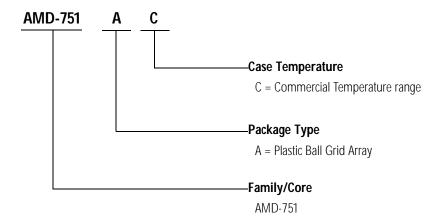

# 3 Ordering Information

AMD standard products are available in several packages and operating ranges. The order number is formed by a combination of the elements shown in Figure 4. Table 4 shows valid combinations of elements. Contact your AMD representative for detailed ordering information.

Figure 4. Ordering Information Elements

Table 4. Valid Combinations for Ordering Parts

to check on newly released combinations.

| OPN                                                                                                                                                                                             | Package Type     | Operating Voltage | Case Temperature |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|------------------|--|--|

| AMD-751AC                                                                                                                                                                                       | 492-pin PBGA ATX | 3.135 V-3.6 V     | 85°C             |  |  |

| Note:                                                                                                                                                                                           |                  |                   |                  |  |  |

| Valid combinations are configurations that are or will be supported in volume for this device.<br>Consult the local AMD sales office to confirm availability of specific valid combinations and |                  |                   |                  |  |  |

21910E-March 2000

# 4.1 Processor Interface Signals

### 4.1.1 CLKFWDRST (Clock Forward Reset)

#### **Output**

Summary CLKFWDRST resets the source-synchronous clock circuitry for

the processor.

Driven This signal is negated by RESET#. It is asserted off the rising

edge of SYSCLK.

## 4.1.2 **CONNECT (Connect)**

#### Output

Summary CONNECT is an output from the AMD-751 system controller

and is used for power management and source-synchronous

clock initialization at reset.

Driven This signal is negated by RESET#. It is asserted off the rising

edge of SYSCLK.

### 4.1.3 PROCRDY (Processor Ready)

#### Input

Summary PROCRDY is an input to the AMD-751 system controller and is

used for power management and source-synchronous clock

initialization at reset.

Sampled This signal is sampled on the rising edge of SYSCLK.

## 4.1.4 SADDIN[14:2]# (Address/Command)

#### **Output**

Summary

The SADDIN[14:2]# bus is the unidirectional system probe channel to the processor. It is used to transfer probes or data movement commands into the processor. All probes and commands on the SADDIN[14:2]# channel are skew-aligned with the source-synchronous clock, SADDINCLK#.

During PCI-to-DRAM cycles, the AMD-751 system controller drives the SADDIN[14:2]# bus to snoop (inquire cycle) the processor cache.

Driven

The AMD-751 system controller drives the SADDIN[14:2]# channel on each edge of SADDINCLK#.

#### 4.1.5 SADDINCLK# (System Address In Clock)

#### Output

**Summary**

SADDINCLK# is the single-ended source-synchronous clock for the SADDIN[14:2]# bus driven by the AMD-751 system controller. Each clock edge is used to transfer probes or data movement commands to the processor.

Driven

This signal is driven inactive (negated) when the CLKFWDRST signal is active (true). When CLKFWDRST is deasserted, SADDINCLK# runs continuously.

## 4.1.6 SADDOUT[14:2]# (System Address Out)

#### Input

Summary

The SADDOUT[14:2]# channel is the unidirectional system address interface from the processor to the AMD-751 system controller. The SADDOUT[14:2]# channel is used to transfer processor requests to the system. All commands on this channel are skew-aligned with the source-synchronous clock, SADDOUTCLK#.

#### Sampled

The SADDOUT[14:2]# channel is sampled by the AMD-751 system controller on each edge of SADDOUTCLK#.

The AMD-751 system controller samples commands driven by the processor on the SADDOUT[14:2]# channel and forwards them to the PCI bus, AGP bus, or DRAM, depending on the address range and AMD-751 configuration.

#### 4.1.7 SADDOUTCLK# (System Address Out Clock)

#### Input

#### Summary

SADDOUTCLK# is the single-ended source-synchronous clock for the SADDOUT[14:2]# channel driven by the processor. Each edge is used to transfer commands.

This signal is driven inactive (negated) when the CLKFWDRST signal is active (true). When CLKFWDRST is deasserted, SADDOUTCLK# runs continuously.

#### 4.1.8 SCHECK[7:0]# (Data Bus Check Byte)

#### **Bidirectional**

Summary

SCHECK[7:0]# contains the ECC check bits for data transferred on the SDATA[63:0]# bus.

Driven, Sampled, and Floated

As Outputs: The AMD-751 system controller drives SCHECK[7:0]# with valid data.

*As Inputs:* During write cycles, the AMD-751 system controller samples SCHECK[7:0]#.

SCHECK[7:0]# is floated out of RESET#. It remains floated except when driven with write data by the processor, by read data (writeback data) from the cache, or by read data from the AMD-751 system controller.

## 4.1.9 SDATA[63:0]# (Processor Data Channel)

#### **Bidirectional**

#### Summary

The SDATA[63:0]# channel is the bidirectional interface to and from the processor and system for data movement. Data is skew-aligned with either SDATAINCLK[3:0]# or SDATAOUTCLK[3:0]#. Each edge is used to transfer data.

**Note:** In/Out is relative to the processor.

The SDATA[63:0]# channel connects to the 64-bit data channel of the processor. Each of the four words of data that comprise this channel is qualified by a corresponding clock (SDATAINCLK[3:0]# or SDATAOUTCLK[3:0]#).

# Driven, Sampled, and Floated

As Outputs: The AMD-751 system controller drives the SDATA[63:0]# channel with valid data on each edge of the system address clocks (SDATAINCLK[3:0]#).

As Inputs: During write cycles, the AMD-751 system controller samples the SDATA[63:0]# channel on each edge of SDATAOUTCLK[3:0]#.

SDATA[63:0]# is floated out of RESET#. It remains floated except when driven with write data by the processor, by read data (writeback data) from the cache, or by read data from the AMD-751 system controller.

## 4.1.10 SDATAINCLK[3:0]# (System Data In Clock)

#### Output

#### Summary

SDATAINCLK[3:0]# is the single-ended source-synchronous clock driven by the AMD-751 system controller to transfer data on SDATA[63:0]#. Each 16-bit data word is skew-aligned with this clock. Each edge is used to transfer data.

#### Driven

This signal is driven inactive (negated) when the CLKFWDRST signal is active (true). When CLKFWDRST is deasserted, SDATAINCLK# runs continuously.

#### 4.1.11 SDATAINVAL# (System Data In Valid)

#### **Output**

SUMMARY SDATAINVAL# is driven by the AMD-751 system controller and

controls the flow of data into the processor. SDATAINVAL# can be used to introduce an arbitrary number of cycles between

octawords (128 bits).

Driven This signal is negated by RESET#. SDATAINVAL# is asserted

off the rising edge of SADDINCLK.

#### 4.1.12 SDATAOUTCLK[3:0]# (System Address Out Clock)

#### Input

SDATAOUTCLK[3:0]# is the single-ended source-synchronous

clock driven by the processor and is used to transfer data on the SDATA[63:0]# channel. Each 16-bit data word is skew-aligned with this clock. Each edge is used to transfer

data.

This signal is driven inactive (negated) when the CLKFWDRST signal is active (true). When CLKFWDRST is deasserted,

SDATAOUTCLK# runs continuously.

## 4.1.13 SYSCLK (System Clock)

#### Input

Sysclk is a single-ended input clock signal provided to the

phase locked loop (PLL) of the AMD-751 system controller from the system-clock generator. It is set at 100 MHz operation.

# 4.2 PCI Interface Signals

## 4.2.1 AD[31:0] (PCI Address/Data Bus)

#### **Bidirectional**

#### Summary

The AD[31:0] bus contains the standard, multiplexed PCI address and data lines. AD[31:0] contains a physical address during the first clock of a PCI transaction, and data during subsequent clocks. The address is driven when FRAME# is asserted, and data is driven or received in subsequent cycles.

When the AMD-751 system controller is the PCI initiator, these lines are outputs during the address and write data phases of a transaction, and inputs during the read data phases.

When the AMD-751 is the PCI target, these lines are inputs during the address and write data phases of a transaction, and outputs during the read data phases.

# Driven, Sampled, and Floated

As Outputs: As an initiator, the AMD-751 system controller drives AD[31:0] with a valid address off the first rising edge of PCLK after it becomes the PCI bus master. During the first clock that FRAME# is asserted, AD[31:0] contains the address. During subsequent clocks, AD[31:0] contains data.

As Inputs: The AMD-751 system controller samples AD[31:0] on the rising edge of PCLK. During the first clock after FRAME# is asserted, the AMD-751 loads the bus contents into its internal address register. On each subsequent clock in which both TRDY# and IRDY# are asserted, AD[31:0] loads data into its data FIFO.

AD[31:0] is floated for one clock in between the address phase and the data phase of a read transfer. AD[31:0] is also floated during RESET# and when there is no initiator driving the bus.

## 4.2.2 C/BE[3:0]# (PCI Command/Byte Enables)

#### **Bidirectional**

Summary

C/BE[3:0]# contain the PCI command during the first clock cycle that FRAME# is asserted. These signals serve as a byte-enable signal for subsequent cycles.

Driven, Sampled, and Floated

As Outputs: The AMD-751 system controller drives C/BE[3:0]# with a valid command or byte enables off the rising edge of PCLK.

As Inputs: When the AMD-751 system controller is a target, it samples C/BE[3:0]# on the rising edge of every PCLK. C/BE[3:0]# are qualified by FRAME# for commands and qualified by IRDY# and TRDY# for data.

C/BE[3:0]# are floated during RESET# and when there is no initiator driving the bus.

## 4.2.3 DEVSEL# (PCI Device Select)

#### **Bidirectional**

Summary

The AMD-751 system controller samples DEVSEL# when it is the initiator in a PCI cycle to determine if the target device has responded. The AMD-751 drives DEVSEL# when it is the targeted device in a PCI cycle.

Driven, Sampled, and Floated

*As an Output:* The AMD-751 system controller drives this signal when it decodes the address and determines it is the target of the transfer.

As an Input: When the AMD-751 system controller is the initiator, it samples this signal on the rising edge of every PCLK to determine that the target is present. The target must respond within eight clocks after FRAME# is asserted.

DEVSEL# is floated during RESET# and when there is no initiator driving the bus.

21910E-March 2000

## 4.2.4 FRAME# (PCI Cycle Frame)

#### **Bidirectional**

#### Summary

The AMD-751 system controller asserts FRAME# at the beginning of a PCI cycle when it is the initiator, and holds it asserted until the beginning of the last data transfer in the cycle.

If the AMD-751 is the targeted PCI device, it samples and latches the C/BE[3:0]# and AD[31:0] signals and asserts DEVSEL# at the first PCLK edge on which it samples FRAME# asserted.

## Driven, Sampled, and Floated

As an Output: The AMD-751 system controller drives FRAME# valid off the rising edge of PCLK. The duration of FRAME# varies with the length of the transfer.

As an Input: When the AMD-751 system controller is a target, it samples this signal on the rising edge of every PCLK. The assertion of FRAME# indicates the start of a cycle. FRAME# remains asserted during burst transfers.

FRAME# is floated during RESET# and when there is no initiator driving the bus.

## 4.2.5 **GNT[4:0]# (PCI Bus Grant)**

#### Output

#### **Summary**

As the PCI bus arbiter, the AMD-751 system controller asserts one of these device-specific bus grant signals off the rising clock edge to indicate to an initiator that it has been granted control of the PCI bus.

#### Driven

GNT[4:0]# signals are never floated. They are negated off the rising edge of the clock, indicating that no device has been granted the bus. One of the GNT[4:0]# signals is asserted off the rising edge of the clock, indicating the particular channel that is granted use of the bus.

## 4.2.6 IRDY# (Initiator Ready)

#### **Bidirectional**

#### Summary

IRDY# indicates that a PCI initiator is ready to complete the current data phase of the transaction. During a read cycle, IRDY# asserted indicates the master is ready to accept the data. During a write cycle, IRDY# asserted indicates that write data is valid on AD[31:0]. Data is transferred on the PCI bus on each PCLK in which both IRDY# and TRDY# are asserted. Wait states are inserted on the bus until both IRDY# and TRDY# are asserted together.

## Driven, Sampled, and Floated

As an Output: When the AMD-751 system controller is the PCI initiator, it drives IRDY# asserted one PCLK after it asserts FRAME# and holds it asserted until one cycle before the end of all transactions. The AMD-751 does not terminate a read or write cycle until it samples both IRDY# and TRDY# asserted.

As an Input: IRDY# is sampled on every rising edge of PCLK, when the AMD-751 system controller is a PCI target. When IRDY# and TRDY# are both asserted, the controller advances the FIFO to the next data. If either signal is negated, the current data is held on the bus.

IRDY# is floated when there is no bus master currently driving the bus.

## 4.2.7 LOCK# (PCI Bus Lock)

#### **Bidirectional**

#### Summary

A PCI initiator asserts LOCK# to prevent other devices from accessing a targeted device during atomic transactions. Using LOCK# is not recommended because it is not supported by the AMD-751 system controller, and the system can hang if the initiator does not unlock the resource.

# Driven, Sampled, and Floated

An 8.2-Kohm pullup resistor is required to keep LOCK# inactive, if it is not implemented on an initiator.

## 4.2.8 PAR (PCI Bus Parity)

#### **Bidirectional**

Summary

PAR indicates even parity. The AMD-751 system controller drives PAR as a PCI initiator one clock after the address phase and each data write phase to generate even parity across A\_AD[31:0] and A\_C/BE[3:0]#. The AMD-751 drives PAR as a PCI target one clock after each data read phase. The AMD-751 does not support parity checking.

Driven, Sampled, and Floated

As an Output: This signal is asserted off the rising edge of every PCLK.

*As an Input*: The AMD-751 system controller does not support parity checking.

PAR is only floated when changing bus ownership from one initiator to another.

## 4.2.9 PCLK (PCI Clock)

#### Input

Summary

PCLK is a 33-MHz clock provided by the system clock generator. It is used by the AMD-751 logic in the PCI clock domain. PCLK to A\_CLK (AGP clock) skew is +/- 500ps maximum.

## **4.2.10 PGNT# (PCI Grant to Peripheral Bus Controller)**

## **Output**

Summary

PGNT# grants control of the PCI bus to the PCI-ISA/IDE bridge functions implemented in the AMD-756 peripheral bus controller.

Driven

PGNT# is driven off the rising edge of PCLK. RESET# forces PGNT# inactive. PGNT# is asserted in response to a PREQ#.

## 4.2.11 PREQ# (PCI Request from Peripheral Bus Controller)

#### Input

Summary The AMD-751 system controller samples PREQ# to determine

if the AMD-756 peripheral bus controller needs PCI bus access.

Sampled This signal is sampled by the rising edge of every PCLK. If

asserted, the arbiter issues a PGNT# when the bus is available.

## 4.2.12 **REQ[4:0]# (PCI Bus Request)**

#### Input

Summary As the PCI bus arbiter, the AMD-751 system controller samples

these device-specific bus request signals to determine if

another agent requires control of the PCI bus.

Sampled These signals are sampled by the rising edge of every PCLK. If

active, the arbiter issues the corresponding GNT[4:0]# when

the bus is available.

## **4.2.13 RESET#** (Reset)

## Input

Summary Asserting RESET# resets the AMD-751 system controller and

sets all register bits to their default values. Bidirectional signals are three-stated and outputs are driven inactive. This signal is driven by the PCIRST# signal from the AMD-756

peripheral bus controller.

Sampled This signal may be asynchronous to SYSCLK and PCLK. It is

synchronized internally, therefore it must be active for a

minimum of four PCLK periods.

## 4.2.14 SERR# (System Error)

#### Output

Summary The AMD-751 system controller, as a PCI agent, asserts SERR#

off the rising edge of PCLK one clock after it detects a system error. SERR# is an input to the AMD-756 peripheral bus controller, which can be programmed to generate a

non-maskable interrupt (NMI).

Driven and Floated SERR# is driven asserted on the rising edge of PCLK to

indicate that a fatal condition has been detected by the AMD-751 system controller. This is an open-drain output—

normally a pullup resistor keeps this signal negated.

## 4.2.15 STOP# (PCI Bus Stop)

#### **Bidirectional**

Summary As a PCI initiator, the AMD-751 system controller samples

STOP# to determine if the target device requires it to abort or

retry a transaction.

STOP# is sampled by the current initiator on the rising edge of

every PCLK to determine if the current transaction should

continue or be stopped.

## 4.2.16 TRDY# (Target Ready)

#### **Bidirectional**

Summary As a PCI initiator, the AMD-751 system controller samples

TRDY# to determine when the target agent is able to complete

the data phase of a transaction.

As a PCI target, the AMD-751 asserts TRDY# to indicate that it has latched the data on AD[31:0] during a write phase or

driven the data on AD[31:0] during a read phase.

Driven, Sampled, and

Floated

As an Output: When the AMD-751 system controller is the PCI target, it asserts TRDY# when valid data is available on the bus (initiator read) or when there is room in its internal FIFO

(initiator write). The AMD-751 does not terminate a read or write cycle until it samples both IRDY# and TRDY# asserted.

As an Input: TRDY# is sampled on every rising edge of PCLK when the AMD-751 system controller is a PCI initiator. When IRDY# and TRDY# are both asserted, the controller advances the FIFO to the next data. If either signal is negated, the current data is held on the bus.

TRDY# is floated when there is no bus master currently driving the bus.

## 4.2.17 WSC# (Write Snoop Complete)

#### **Bidirectional**

Summary

WSC# is asserted to indicate that all of the snoop activity on the processor bus on behalf of the last PCI-to-DRAM write transaction is complete and that an APIC interrupt message can be sent. This signal is used only in configurations where an I/O APIC is installed.

Driven and Floated

WSC# is driven asserted on the rising edge of PCLK to indicate to the AMD-756 peripheral bus controller that all probes due to PCI DMA (direct memory access) are complete.

The AMD-756 peripheral bus controller requests that the AMD-751 system controller issue a Fence command to its buffers by placing a single PCLK pulse on WSC#. The AMD-751 then marks the data currently in its buffers and waits for this data to reach processor-accessible (coherent) space. When this data reaches processor-accessible space, the AMD-751 responds by sending a two-clock pulse back to the AMD-756 peripheral bus controller. After this pulse is received, the AMD-756 peripheral bus controller transmits the interrupt message over the interrupt message bus (IMB).

21910E-March 2000

## 4.3 **DRAM Interface Signals**

## 4.3.1 CS[5:0]# (Chip Selects)

#### Output

Summary CS[5:0]# function as chip select signals for SDRAMs.

Driven These signals are negated by RESET#. The memory controller

asserts or negates these signals off the rising edge of SYSCLK at the appropriate time in the memory access sequence. See Chapter 5, "Functional Operation" starting on page 45 for

more information.

## 4.3.2 DQM[7:0]# (Data Mask)

#### Output

Summary DQM[7:0]# provides data masks for each byte during SDRAM

write cycles.

Driven These control signals are negated by RESET#. The memory

controller asserts or negates these signals off the rising edge of SYSCLK at the appropriate time in the memory access sequence. See Chapter 5, "Functional Operation" starting on

page 45 for more information.

## 4.3.3 MAdA[14:0] and MAdB[14:0] (Memory Address)

## Output

Summary The multiplexed row and column address bits MAdA[14:0] and

MAdB[14:0] connect to the system SDRAMs. They can address any size DRAM from 4 Mbits to 128 Mbits (for example, 16 Mbits x 4 = 64 Mbits, 16 Mbits x 8 = 128 Mbits). Two identical sets of memory addresses are provided to reduce signal loading

for motherboard designs with three DIMM slots.

Driven The memory controller asserts or deasserts these signals off

the rising edge of SYSCLK at the appropriate time in the memory access sequence. See Chapter 5, "Functional

Operation" starting on page 45 for more information.

## 4.3.4 MCKE[2:0] (SDRAM Clock Enable)

#### **Output**

Summary MCKE[2:0] are clock enable signals for the synchronous

DRAM. They operate in parallel to drive greater loads than a single signal can support and are used for power saving modes.

*Driven* These control signals are driven inactive (negated) by RESET#.

See Chapter 5, "Functional Operation" starting on page 45 for

more information.

## 4.3.5 MDAT[63:0] (Memory Data)

#### **Bidirectional**

Summary MDAT[63:0] connect to the DRAM data I/O. They are driven by

the DRAM during reads and are driven by the AMD-751 system

controller during writes.

Driven, Sampled, and

Floated

As Outputs: These signals are driven with the data to be written on the rising edge of SDRAM\_CLKOUT. The data changes at different times based on the type of memory and timing selected. See Chapter 5, "Functional Operation" starting on page 45 for more information.

As Inputs: MDAT[63:0] are sampled on the rising edge of

SDRAM\_CLKIN.

MDAT[63:0] are floated when neither the AMD-751 system

controller or the memory are driving the bus.

## 4.3.6 MECCD[7:0] (Memory ECC)

#### **Bidirectional**

Summary

MECCD[7:0] carry error correction codes for the eight bytes of data on MDAT[63:0]. These signals are inputs to the AMD-751 system controller during DRAM read cycles and outputs during DRAM write cycles.

Driven, Sampled, and Floated

As Outputs: These signals are driven with the parity or ECC data on the rising edge of SYSCLK. They change at different times based on the type of memory and timing selected. See Chapter 5, "Functional Operation" starting on page 45 for more information.

As Inputs: MECCD[7:0] are sampled on the same rising edge of SYSCLK that samples MDAT[63:0].

MECCD[7:0] are floated when neither the AMD-751 system controller or the memory are driving the bus.

## 4.3.7 SCAS[2:0]# (SDRAM Column Address Strobes)

## Output

Summary

SCAS0#, SCAS1#, and SCAS2# are column address strobe signals for the synchronous DRAM. They operate in parallel to drive greater loads than a single signal can support.

Driven

These control signals are driven inactive (negated) by RESET#. The memory controller asserts or negates these signals off the rising edge of SYSCLK at the appropriate time in the memory access sequence. See Chapter 5, "Functional Operation" starting on page 45 for more information.

## 4.3.8 SDRAM Clk\_In

#### Input

Summary

The SDRAM Clk\_In signal is used to clock in the data returned from a SDRAM read operation. Data is clocked in on the rising edge of this signal. This clock is provided by the ZDB and is phase aligned with the SDRAM clocks.

## 4.3.9 SDRAM Clk\_Out

#### Output

SUMMARY SDRAM Clk\_Out is a clock signal for the synchronous DRAM.

Driven This signal is a free-running clock generated by the internal

PLL in the AMD-751 system controller. This signal is used to clock a zero delay buffer (ZDB) external to the AMD-751. The ZDB, in turn, generates the clock for the SDRAMs. The advantage of the ZDB is that the timing of the clocks to the

SDRAM DIMMs can be adjusted.

## 4.3.10 SRAS[2:0]# (SDRAM Row Address Strobes)

#### **Output**

Summary SRAS0#, SRAS1#, and SRAS2# are row address strobe signals

for the synchronous DRAM. They operate in parallel to drive

greater loads than a single signal can support.

*Driven* These control signals are driven inactive (negated) by RESET#.

The memory controller asserts or negates these signals off the rising edge of SYSCLK at the appropriate time in the memory access sequence. See Chapter 5, "Functional Operation"

starting on page 45 for more information.

## 4.3.11 WE[2:0]# (SDRAM Memory Write Enables)

#### **Output**

Summary WE[2:0]# are write enable signals for all DRAM. They operate

in parallel to drive greater loads than a single signal can

support.

*Driven* These control signals are driven inactive (negated) by RESET#.

The memory controller asserts or negates these signals off the rising edge of SYSCLK at the appropriate time in the memory access sequence. See Chapter 5, "Functional Operation"

starting on page 45 for more information.

## 4.4 AGP/PCI Signals

The following signal descriptions apply to AGP bus signals when used for AGP transactions. The AGP bus can also perform PCI transactions, in which case the AGP bus pins function identically to their PCI bus pin equivalents (same pin names without the A\_ prefix), as described in "PCI Interface Signals" on page 22.

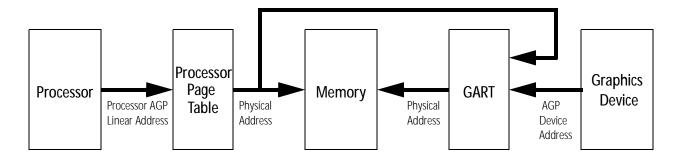

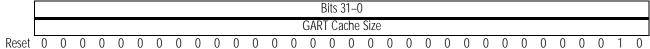

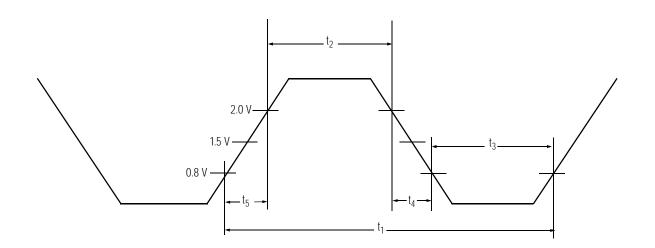

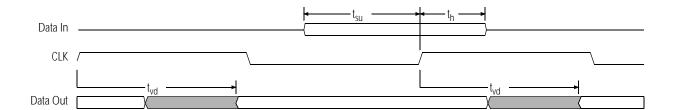

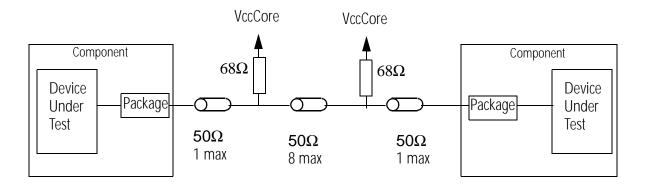

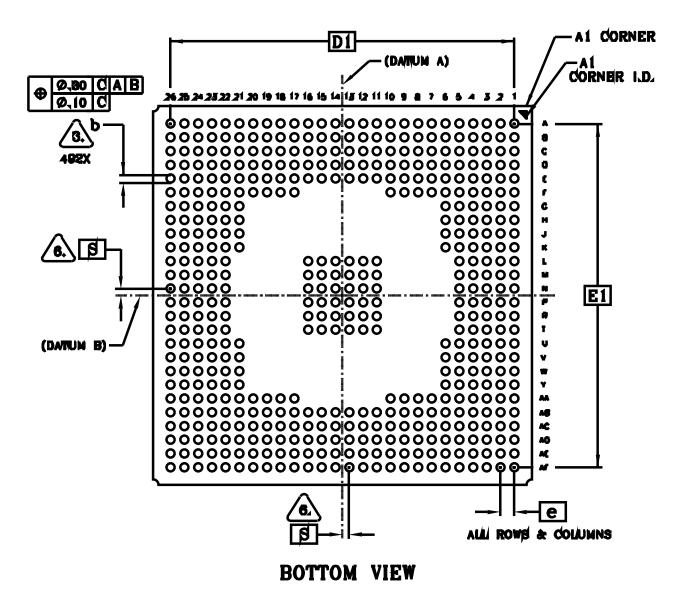

## 4.4.1 A\_AD[31:0] (Address/Data Bus)