### INTEGRATED CIRCUITS

# DATA SHEET

# **TDA4841PS**I<sup>2</sup>C-bus autosync deflection controller for PC monitors

Product specification Supersedes data of 1999 Oct 25 2002 Jun 24

### I<sup>2</sup>C-bus autosync deflection controller for PC monitors

### **TDA4841PS**

#### **FEATURES**

#### **Concept features**

- Full horizontal plus vertical autosync capability

- Extended horizontal frequency range from 15 to 130 kHz

- Comprehensive set of I<sup>2</sup>C-bus driven geometry adjustments and functions, including standby mode

- · Very good vertical linearity

- Moire cancellation

- Start-up and switch-off sequence for safe operation of all power components

- · X-ray protection

- · Power dip recognition

- Flexible switched mode B+ supply function block for feedback and feed forward converter

- Internally stabilized voltage reference

- Drive signal for focus amplifiers with combined horizontal and vertical parabola waveforms

- DC controllable inputs for Extremely High Tension (EHT) compensation

- · SDIP32 package.

#### **Synchronization**

- Can handle all sync signals (horizontal, vertical, composite and sync-on-video)

- Output for video clamping (leading/trailing edge selectable by I<sup>2</sup>C-bus), vertical blanking and protection blanking

- Output for fast unlock status of horizontal synchronization and blanking on grid 1 of picture tube.

### **Horizontal section**

- I<sup>2</sup>C-bus controllable wide range linear picture position, pin unbalance and parallelogram correction via horizontal phase

- Frequency-locked loop for smooth catching of horizontal frequency

- Simple frequency preset of f<sub>min</sub> and f<sub>max</sub> by external resistors

- · Low iitter

- Soft start for horizontal and B+ control drive signals.

#### Vertical section

- I<sup>2</sup>C-bus controllable vertical picture size, picture position, linearity (S-correction) and linearity balance

- Output for I<sup>2</sup>C-bus controllable vertical sawtooth and parabola (for pin unbalance and parallelogram)

- Vertical picture size independent of frequency

- Differential current outputs for DC coupling to vertical booster

- 50 to 160 Hz vertical autosync range.

### East-West (EW) section

- I<sup>2</sup>C-bus controllable output for horizontal pincushion, horizontal size, corner and trapezium correction

- Optional tracking of EW drive waveform with line frequency selectable by I<sup>2</sup>C-bus.

#### **Focus section**

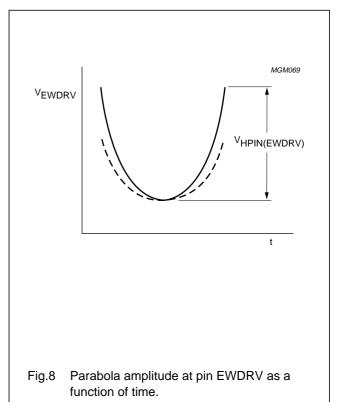

- I<sup>2</sup>C-bus controllable output for horizontal and vertical parabolas

- Vertical parabola is independent of frequency and tracks with vertical adjustments

- · Horizontal parabola independent of frequency

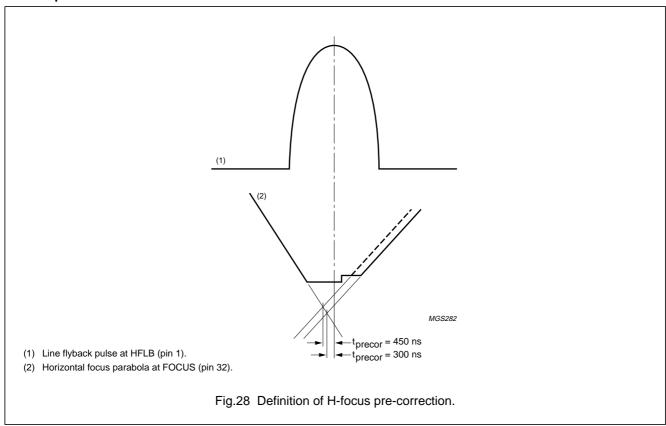

- Adjustable pre-correction of delay in focus output stage.

### I<sup>2</sup>C-bus autosync deflection controller for PC monitors

### **TDA4841PS**

#### **GENERAL DESCRIPTION**

The TDA4841PS is a high performance and efficient solution for autosync monitors. All functions are controllable by the I<sup>2</sup>C-bus.

The TDA4841PS provides synchronization processing, horizontal and vertical synchronization with full autosync capability and very short settling times after mode changes. External power components are given a great deal of protection. The IC generates the drive waveforms for DC-coupled vertical boosters such as TDA486x and TDA835x.

The TDA4841PS provides extended functions e.g. as a flexible B+ control, an extensive set of geometry control facilities, and a combined output for horizontal and vertical focus signals.

Together with the I<sup>2</sup>C-bus driven Philips TDA488x video processor family, a very advanced system solution is offered.

#### **QUICK REFERENCE DATA**

| SYMBOL               | PARAMETER                                         | MIN.  | TYP.  | MAX. | UNIT |

|----------------------|---------------------------------------------------|-------|-------|------|------|

| V <sub>CC</sub>      | supply voltage                                    | 9.2   | _     | 13.2 | ٧    |

| I <sub>CC</sub>      | supply current                                    | _     | 68    | _    | mA   |

| I <sub>CC(stb)</sub> | supply current during standby mode                | _     | 9     | _    | mA   |

| VSIZE                | vertical size                                     | 60    | _     | 100  | %    |

| VGA                  | VGA overscan for vertical size                    | _     | 16.8  | _    | %    |

| VPOS                 | vertical position                                 | _     | ±11.5 | _    | %    |

| VLIN                 | vertical linearity (S-correction)                 | -2    | _     | -46  | %    |

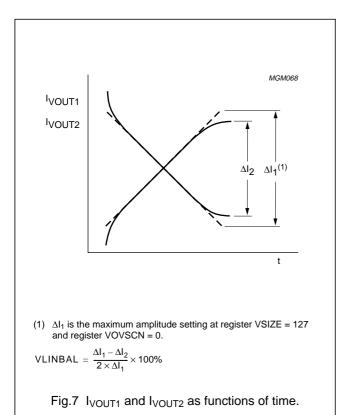

| VLINBAL              | vertical linearity balance                        | _     | ±1.25 | _    | %    |

| V <sub>HSIZE</sub>   | horizontal size voltage                           | 0.13  | _     | 3.6  | V    |

| V <sub>HPIN</sub>    | horizontal pincushion voltage (EW parabola)       | 0.04  | _     | 1.42 | V    |

| V <sub>HEHT</sub>    | horizontal size modulation voltage                | 0.02  | _     | 0.69 | V    |

| V <sub>HTRAP</sub>   | horizontal trapezium correction                   | _     | ±0.5  | _    | V    |

| V <sub>HCORT</sub>   | horizontal corner correction at top of picture    | -0.64 | _     | +0.2 | V    |

| V <sub>HCORB</sub>   | horizontal corner correction at bottom of picture | -0.64 | _     | +0.2 | V    |

| HPOS                 | horizontal position                               | _     | ±13   | _    | %    |

| HPARAL               | horizontal parallelogram                          | _     | ±1.5  | _    | %    |

| HPINBAL              | EW pin unbalance                                  | _     | ±1.5  | _    | %    |

| T <sub>amb</sub>     | ambient temperature                               | -20   | _     | +70  | °C   |

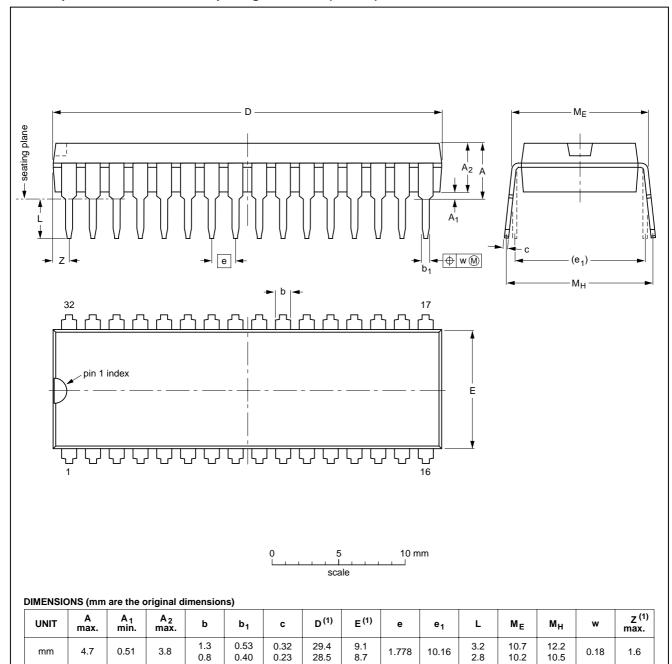

### **ORDERING INFORMATION**

| TYPE      |        | PACKAGE                                                 |          |

|-----------|--------|---------------------------------------------------------|----------|

| NUMBER    | NAME   | AME DESCRIPTION VERSION                                 |          |

| TDA4841PS | SDIP32 | plastic shrink dual in-line package; 32 leads (400 mil) | SOT232-1 |

4

Product specification

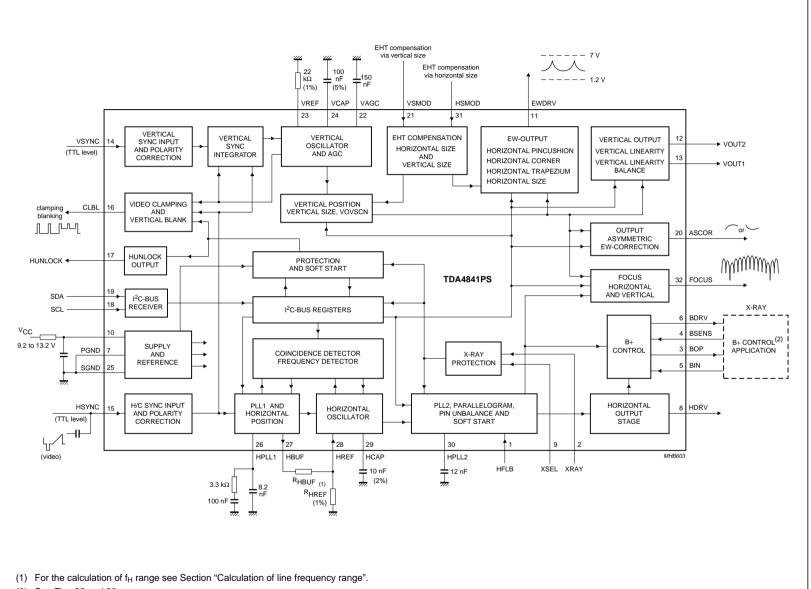

**BLOCK DIAGRAM**

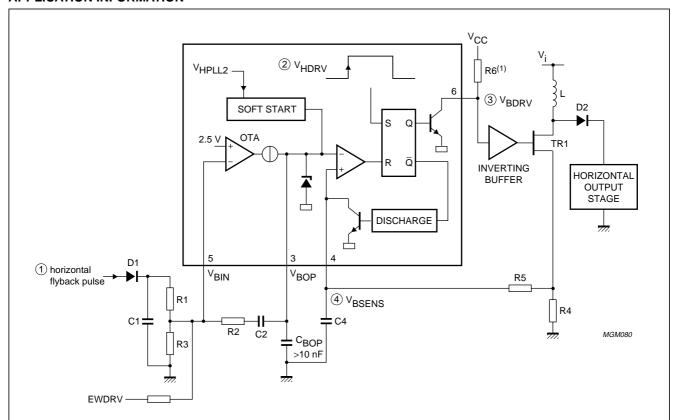

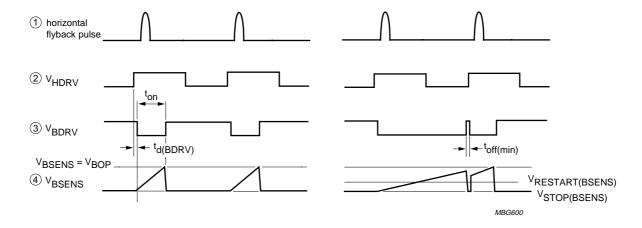

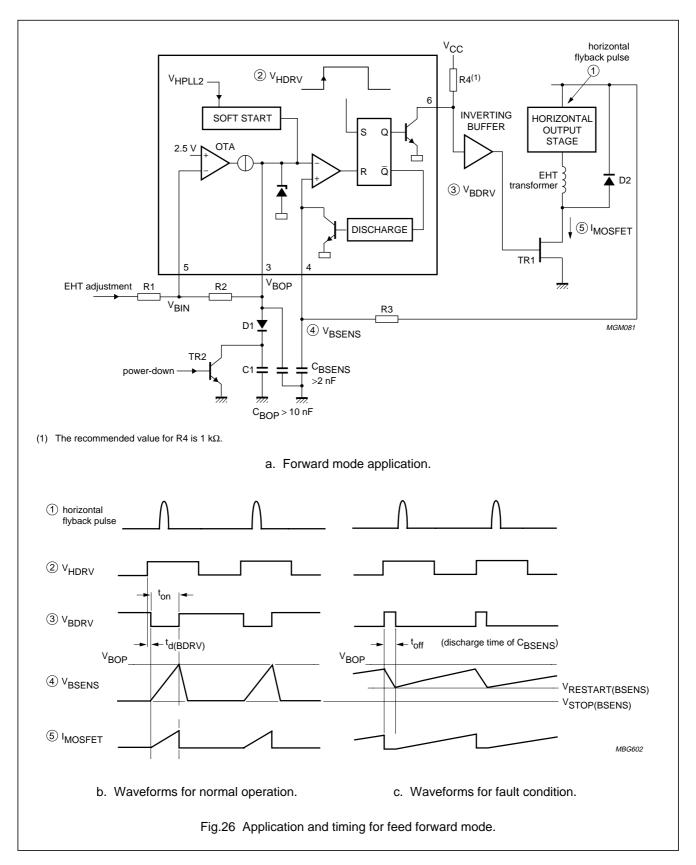

(2) See Figs 25 and 26.

Fig.1 Block diagram and application circuit.

# $\ensuremath{\mathsf{I}}^2\ensuremath{\mathsf{C}}\text{-bus}$ autosync deflection controller for PC monitors

### TDA4841PS

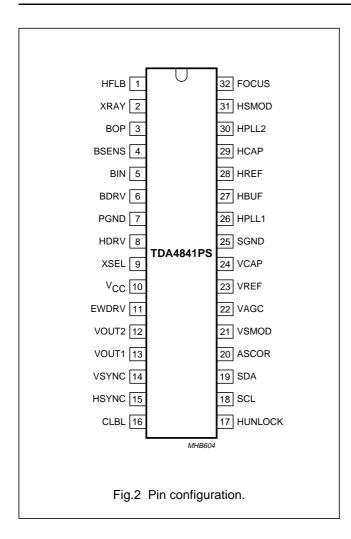

### **PINNING**

| SYMBOL          | PIN | DESCRIPTION                                                           |

|-----------------|-----|-----------------------------------------------------------------------|

| HFLB            | 1   | horizontal flyback input                                              |

| XRAY            | 2   | X-ray protection input                                                |

| ВОР             | 3   | B+ control OTA output                                                 |

| BSENS           | 4   | B+ control comparator input                                           |

| BIN             | 5   | B+ control OTA input                                                  |

| BDRV            | 6   | B+ control driver output                                              |

| PGND            | 7   | power ground                                                          |

| HDRV            | 8   | horizontal driver output                                              |

| XSEL            | 9   | select input for X-ray reset                                          |

| V <sub>CC</sub> | 10  | supply voltage                                                        |

| EWDRV           | 11  | EW waveform output                                                    |

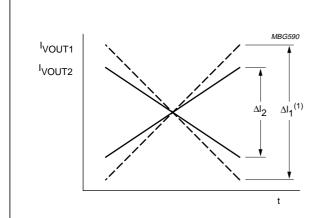

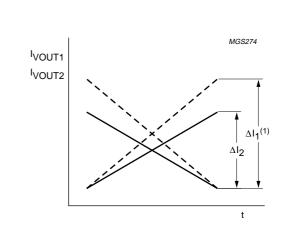

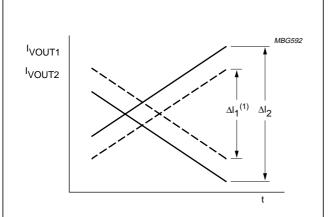

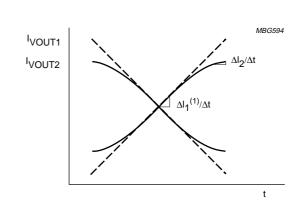

| VOUT2           | 12  | vertical output 2 (ascending sawtooth)                                |

| VOUT1           | 13  | vertical output 1 (descending sawtooth)                               |

| VSYNC           | 14  | vertical synchronization input                                        |

| HSYNC           | 15  | horizontal/composite synchronization input                            |

| CLBL            | 16  | video clamping pulse/vertical blanking output                         |

| HUNLOCK         | 17  | horizontal synchronization unlock/protection/vertical blanking output |

| SCL             | 18  | I <sup>2</sup> C-bus clock input                                      |

| SDA             | 19  | I <sup>2</sup> C-bus data input                                       |

| ASCOR           | 20  | output for asymmetric EW corrections                                  |

| VSMOD           | 21  | input for EHT compensation (via vertical size)                        |

| VAGC            | 22  | external capacitor for vertical amplitude control                     |

| VREF            | 23  | external resistor for vertical oscillator                             |

| VCAP            | 24  | external capacitor for vertical oscillator                            |

| SGND            | 25  | signal ground                                                         |

| HPLL1           | 26  | external filter for PLL1                                              |

| HBUF            | 27  | buffered f/v voltage output                                           |

| HREF            | 28  | reference current input for horizontal oscillator                     |

| HCAP            | 29  | external capacitor for horizontal oscillator                          |

| HPLL2           | 30  | external filter for PLL2/soft start                                   |

| HSMOD           | 31  | input for EHT compensation (via horizontal size)                      |

| FOCUS           | 32  | output for horizontal and vertical focus                              |

### I<sup>2</sup>C-bus autosync deflection controller for PC monitors

### **TDA4841PS**

### **FUNCTIONAL DESCRIPTION**

### Horizontal sync separator and polarity correction

HSYNC (pin 15) is the input for horizontal synchronization signals, which can be DC-coupled TTL signals (horizontal or composite sync) and AC-coupled negative-going video sync signals. Video syncs are clamped to 1.28 V and sliced at 1.4 V. This results in a fixed absolute slicing level of 120 mV related to sync top.

For DC-coupled TTL signals the input clamping current is limited. The slicing level for TTL signals is 1.4 V.

The separated sync signal (either video or TTL) is integrated on an internal capacitor to detect and normalize the sync polarity.

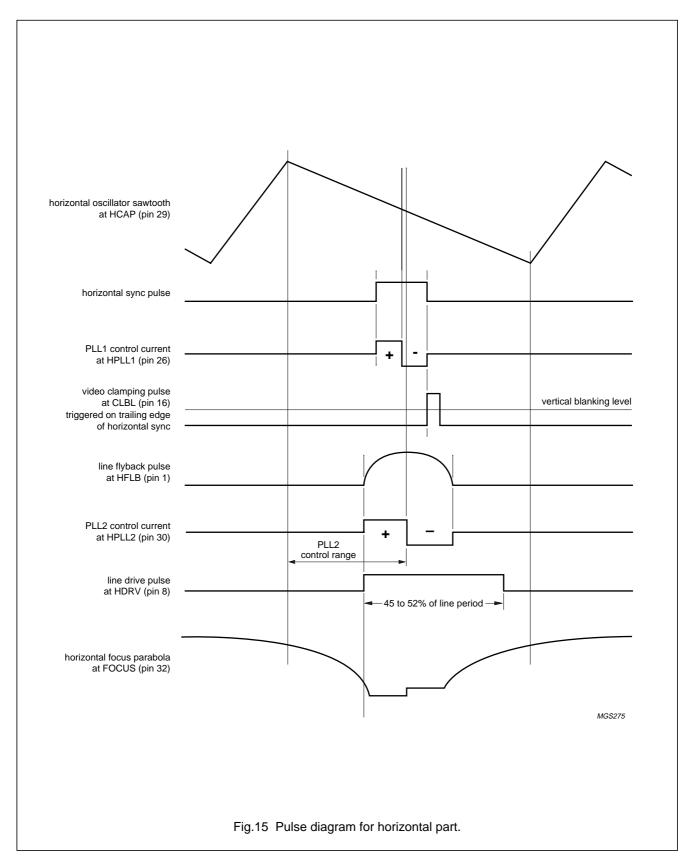

Normalized horizontal sync pulses are used as input signals for the vertical sync integrator, the PLL1 phase detector and the frequency-locked loop.

### Vertical sync integrator

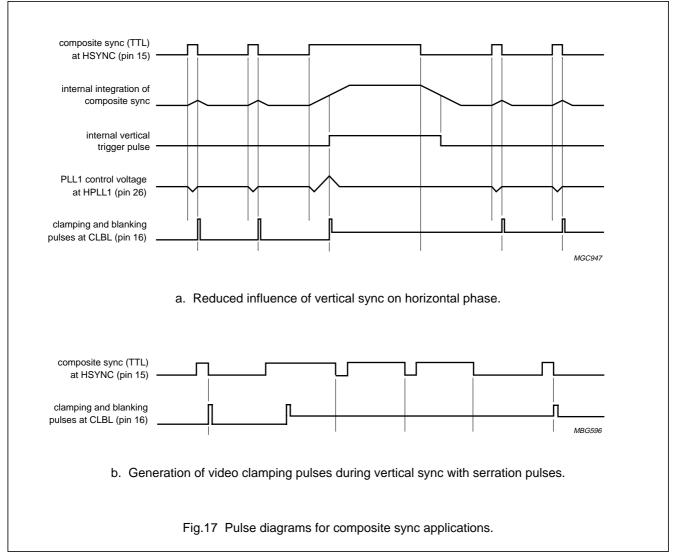

Normalized composite sync signals from HSYNC are integrated on an internal capacitor in order to extract vertical sync pulses. The integration time is dependent on the horizontal oscillator reference current at HREF (pin 28). The integrator output directly triggers the vertical oscillator.

### Vertical sync slicer and polarity correction

Vertical sync signals (TTL) applied to VSYNC (pin 14) are sliced at 1.4 V. The output signal of the sync slicer is integrated on an internal capacitor to detect and normalize the sync polarity. The output signals of vertical sync integrator and sync normalizer are disjuncted before they are fed to the vertical oscillator.

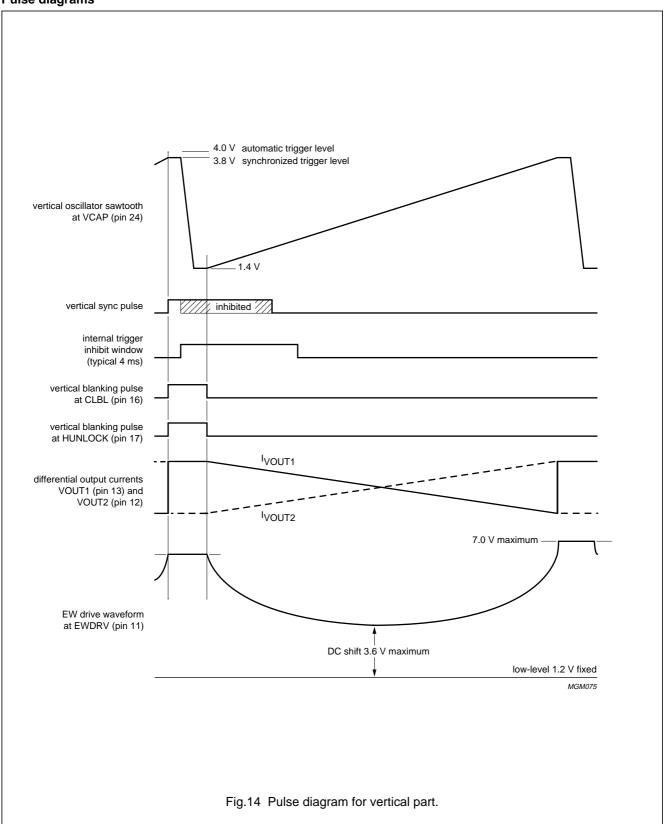

#### Video clamping/vertical blanking generator

The video clamping/vertical blanking signal at CLBL (pin 16) is a two-level sandcastle pulse which is especially suitable for video ICs such as the TDA488x family, but also for direct applications in video output stages.

The upper level is the video clamping pulse, which is triggered by the horizontal sync pulse. Via I<sup>2</sup>C-bus control, either the leading or trailing edge can be selected by setting control bit CLAMP. The width of the video clamping pulse is determined by an internal single-shot multivibrator.

The lower level of the sandcastle pulse is the vertical blanking pulse, which is derived directly from the internal oscillator waveform. It is started by the vertical sync and stopped with the start of the vertical scan. This results in optimum vertical blanking. Via I<sup>2</sup>C-bus control, two different vertical blanking times are accessible by control bit VBLK.

Blanking will be activated continuously, if one of the following conditions is true:

Soft start of horizontal and B+ drive (voltage at HPLL2 (pin 30) pulled down externally or by the I<sup>2</sup>C-bus)

PLL1 is unlocked while frequency-locked loop is in search mode

No horizontal flyback pulses at HFLB (pin 1)

X-ray protection is activated

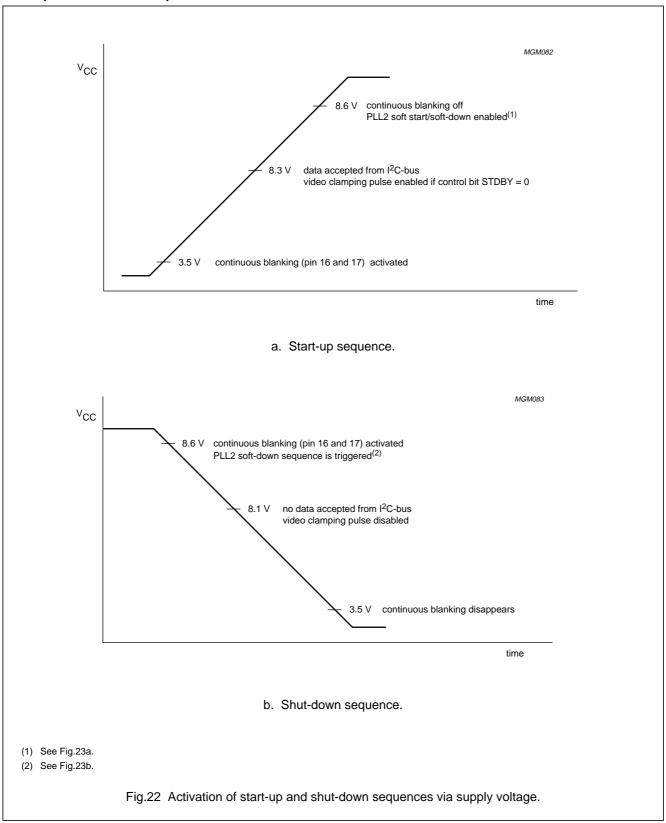

Supply voltage at  $V_{CC}$  (pin 10) is low (see Fig.22).

Via I<sup>2</sup>C-bus control, horizontal unlock blanking can be switched off by control bit BLKDIS while vertical blanking is maintained.

### I<sup>2</sup>C-bus autosync deflection controller for PC monitors

**TDA4841PS**

#### Frequency-locked loop

The frequency-locked loop can lock the horizontal oscillator over a wide frequency range. This is achieved by a combined search and PLL operation. The frequency range is preset by two external resistors and the

recommended maximum ratio is

$$\frac{f_{max}}{f_{min}} = 6.5$$

This can, for instance, be a range from 15.625 to 90 kHz with all tolerances included.

Without a horizontal sync signal the oscillator will be free-running at f<sub>min</sub>. Any change of sync conditions is detected by the internal coincidence detector. A deviation of more than 4% between horizontal sync and oscillator frequency will switch the horizontal section into search mode. This means that PLL1 control currents are switched off immediately. The internal frequency detector then starts tuning the oscillator. Very small DC currents at HPLL1 (pin 26) are used to perform this tuning with a well defined change rate. When coincidence between horizontal sync and oscillator frequency is detected, the search mode is first replaced by a soft-lock mode which lasts for the first part of the next vertical period. The soft-lock mode is then replaced by a normal PLL operation. This operation ensures a smooth tuning and avoids fast changes of horizontal frequency during catching.

In this concept it is not allowed to load HPLL1. The frequency dependent voltage at this pin is fed internally to HBUF (pin 27) via a sample-and-hold and buffer stage. The sample-and-hold stage removes all disturbances caused by horizontal sync or composite vertical sync from the buffered voltage. An external resistor connected between pins HBUF and HREF defines the frequency range.

### Out-of-lock indication (pin HUNLOCK)

Pin HUNLOCK is floating during search mode or if a protection condition is true. All this can be detected by the microcontroller if a pull-up resistor is connected to its own supply voltage.

For an additional fast vertical blanking at grid 1 of the picture tube, a 1 V signal referenced to ground is available at this output. Also the continuous protection blanking (see Section "Video clamping/vertical blanking generator") is available at this pin. Via I<sup>2</sup>C-bus control, the control bit BLKDIS can switch off horizontal unlock blanking while vertical blanking is maintained.

#### Horizontal oscillator

The horizontal oscillator is of the relaxation type and requires a capacitor of 10 nF at HCAP (pin 29). For optimum jitter performance the value of 10 nF must not be changed.

The minimum oscillator frequency is determined by a resistor connected between pin HREF and ground. A resistor connected between pins HREF and HBUF defines the frequency range.

The reference current at pin HREF also defines the integration time constant of the vertical sync integration.

#### Calculation of line frequency range

First the oscillator frequencies  $f_{min}$  and  $f_{max}$  have to be calculated. This is achieved by adding the spread of the relevant components to the highest and lowest sync frequencies  $f_{sync(min)}$  and  $f_{sync(max)}$ . The oscillator is driven by the currents in  $R_{HREF}$  and  $R_{HBUF}$ .

Table 1 describes a 31.45 to 90 kHz application.

Table 1 Calculation of total spread

| spread of               | for f <sub>max</sub> | for f <sub>min</sub> |

|-------------------------|----------------------|----------------------|

| IC                      | ±3%                  | ±5%                  |

| C <sub>HCAP</sub>       | ±2%                  | ±2%                  |

| $R_{HREF}$ , $R_{HBUF}$ | ±2%                  | ±2%                  |

| Total                   | ±7%                  | ±9%                  |

Thus the typical frequency range of the oscillator in this example is:

$$f_{max} = f_{sync(max)} \times 1.07 = 96.3 \text{ kHz}$$

$$f_{min} = \frac{f_{sync(min)}}{1.09} = 28.4 \text{ kHz}$$

The resistors  $R_{\mbox{\scriptsize HREF}}$  and  $R_{\mbox{\scriptsize HBUFpar}}$  can be calculated with the following formulae:

$$R_{HREF} = \frac{78 \times kHz \times k\Omega}{f_{min} + 0.0012 \times f_{min}^{2}[kHz]} = 2.61 k\Omega$$

$$R_{HBUFpar} = \frac{78 \times kHz \times k\Omega}{f_{max} + 0.0012 \times f_{max}^{2}[kHz]} = 726 \Omega$$

The resistor  $R_{\text{HBUFpar}}$  is calculated as the value of  $R_{\text{HREF}}$  and  $R_{\text{HBUF}}$  in parallel.

### I<sup>2</sup>C-bus autosync deflection controller for PC monitors

**TDA4841PS**

The formulae for R<sub>HBUF</sub> additionally takes into account the voltage swing across this resistor:

$$R_{\text{HBUF}} = \frac{R_{\text{HREF}} \times R_{\text{HBUFpar}}}{R_{\text{HREF}} - R_{\text{HBUFpar}}} \times 0.8 \ = \ 805 \ \Omega$$

### PLL1 phase detector

The phase detector is a standard type using switched current sources, which are independent of the horizontal frequency. It compares the middle of horizontal sync with a fixed point on the oscillator sawtooth voltage. The PLL1 loop filter is connected to HPLL1 (pin 26).

See also Section "Horizontal position adjustment and corrections".

#### Horizontal position adjustment and corrections

Via register HPOS the I<sup>2</sup>C-bus allows a linear adjustment of the relative phase between the horizontal sync and oscillator sawtooth (in PLL1 loop). Once adjusted, the relative phase remains constant over the whole frequency range.

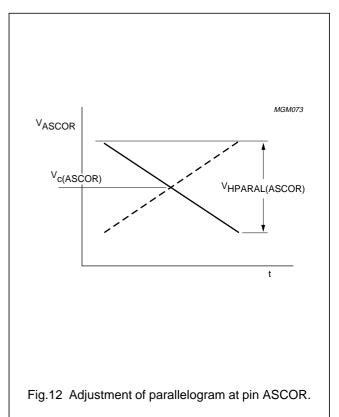

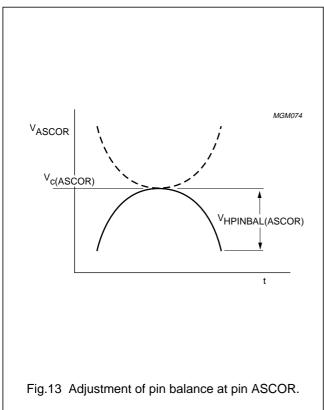

Via registers HPARAL and HPINBAL correction of pin unbalance and parallelogram is achieved by modulating the phase between oscillator sawtooth and horizontal flyback (in loop PLL2). If those asymmetric EW corrections are performed in the deflection stage, both registers can be disconnected from horizontal phase via control bit ACD. This does not change the output at pin ASCOR.

#### Horizontal moire cancellation

To achieve a cancellation of horizontal moire (also known as 'video moire'), the horizontal frequency is divided-by-two for a modulation of the horizontal phase via PLL2. The amplitude is controlled by register HMOIRE. To avoid a visible structure on screen the polarity changes with half the vertical frequency. Control bit MOD disables the moire cancellation function.

#### PLL2 phase detector

The PLL2 phase detector is similar to the PLL1 detector and compares the line flyback pulse at HFLB (pin 1) with the oscillator sawtooth voltage. The control currents are independent of the horizontal frequency. The PLL2 detector thus compensates for the delay in the external horizontal deflection circuit by adjusting the phase of the HDRV (pin 8) output pulse.

An external modulation of the PLL2 phase is not allowed, because this would disturb the pre-correction of the H-focus parabola.

#### Soft start and standby

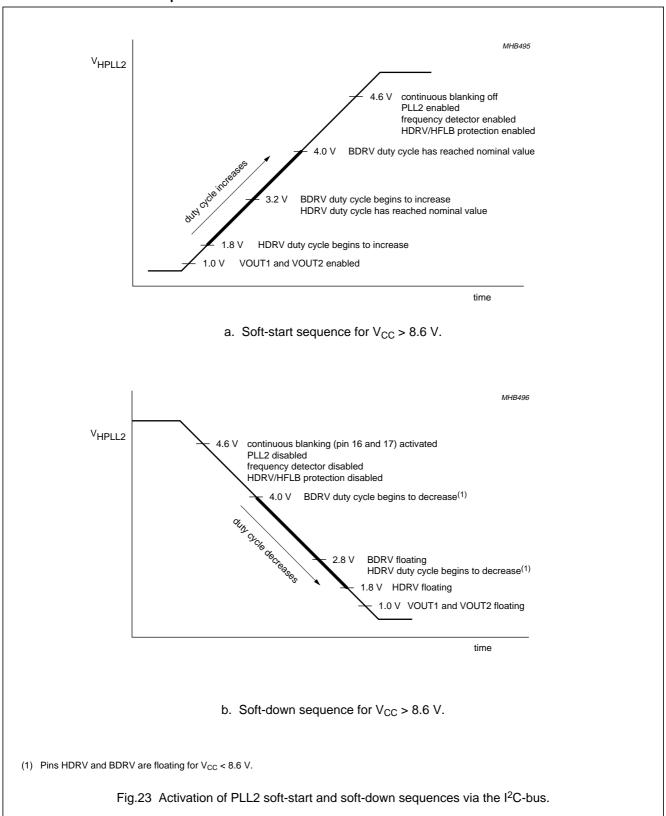

If HPLL2 is pulled to ground, either by an external DC current or by resetting the register SOFTST, horizontal output pulses and B+ control driver pulses are inhibited. This means that HDRV (pin 8), BDRV (pin 6), VOUT1 (pin 13) and VOUT2 (pin 12) are floating in this state. PLL2 and the frequency-locked loop are disabled, CLBL (pin 16) provides a continuous blanking signal and HUNLOCK (pin 17) is floating.

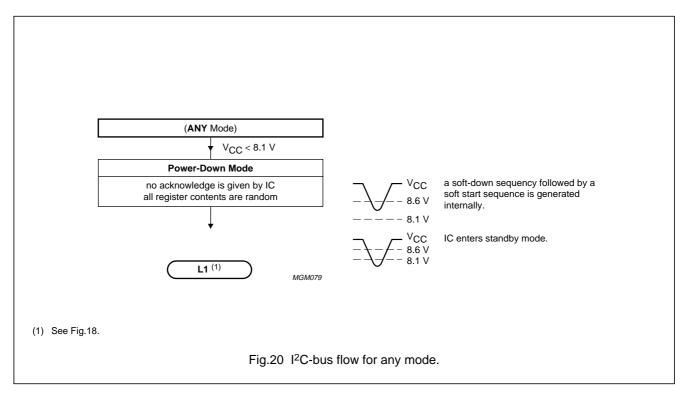

This option can be used for soft start, protection and power-down modes. When the HPLL2 pin is released again, an automatic soft start sequence on the horizontal drive as well as on the B– drive output will be performed (see Fig.22).

A soft start can only be performed if the supply voltage for the IC is 8.6 V at minimum.

The soft start timing is determined by the filter capacitor at HPLL2 (pin 30), which is charged with an constant current during soft start. If the voltage at pin 30 (HPLL2) reaches 1.1 V, the vertical output currents are enabled. At 1.8 V the horizontal driver stage generates very small output pulses. The width of these pulses increases with the voltage at HPLL2 until the final duty cycle is reached. The voltage at HPLL2 increases further and performs a soft start at BDRV (pin 6) as well. After BDRV has reached full duty cycle, the voltage at HPLL2 continues to rise until HPLL2 enters its normal operating range. The internal charge current is now disabled. Finally PLL2 and the frequency-locked loop are activated. If both functions reach normal operation, HUNLOCK (pin 17) switches from the floating status to normal vertical blanking, and continuous blanking at CLBL (pin 16) is removed.

### Output stage for line drive pulses [HDRV (pin 8)]

An open-collector output stage allows direct drive of an inverting driver transistor because of a low saturation voltage of 0.3 V at 20 mA. To protect the line deflection transistor, the output stage is disabled (floating) for low supply voltage at  $V_{CC}$  (see Fig.26).

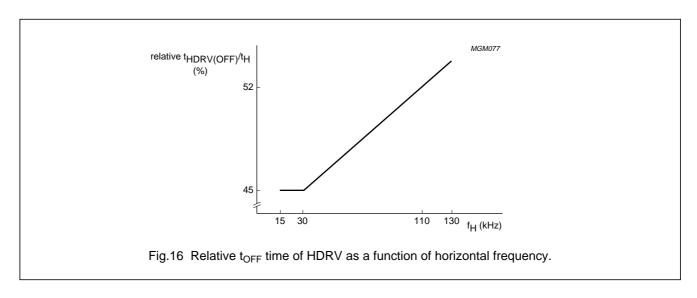

The duty cycle of line drive pulses is slightly dependent on the actual horizontal frequency. This ensures optimum drive conditions over the whole frequency range.

### I<sup>2</sup>C-bus autosync deflection controller for PC monitors

### **TDA4841PS**

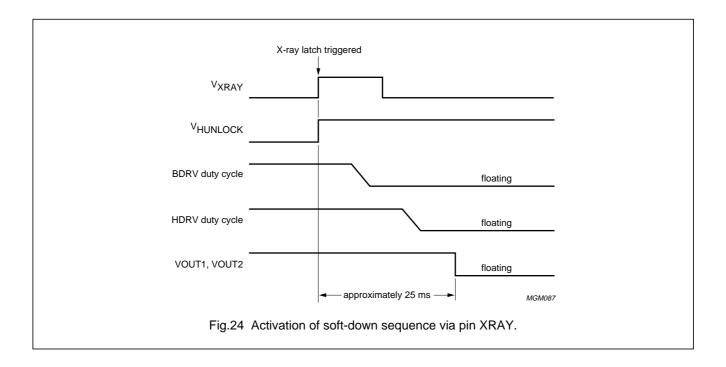

#### X-ray protection

The X-ray protection input XRAY (pin 2) provides a voltage detector with a precise threshold. If the input voltage at XRAY exceeds this threshold for a certain period of time, control bit SOFTST is reset, which switches the IC into protection mode. In this mode several pins are forced into defined states:

HUNLOCK (pin 17) is floating

The capacitor connected to HPLL2 (pin 30) is discharged

Horizontal output stage (HDRV) is floating

B+ control driver stage (BDRV) is floating

Vertical output stages (VOUT1 and VOUT2) are floating

CLBL provides a continuous blanking signal.

There are two different ways to restart the IC:

- XSEL (pin 9) is open-circuit or connected to ground.

The control bit SOFTST must be set to logic 1 via the I<sup>2</sup>C-bus. The IC then returns to normal operation via soft start.

- XSEL is connected to V<sub>CC</sub> via an external resistor.

The supply voltage of the IC must be switched off for a certain time before the IC can be restarted again using the standard power-on procedure.

### Vertical oscillator and amplitude control

This stage is designed for fast stabilization of vertical size after changes in sync frequency conditions. The free-running frequency  $f_{fr(V)}$  is determined by the resistor  $R_{VREF}$  connected to pin 23 and the capacitor  $C_{VCAP}$  connected to pin 24. The value of  $R_{VREF}$  is not only optimized for noise and linearity performance in the whole vertical and EW section, but also influences several internal references. Therefore the value of  $R_{VREF}$  must not be changed. Capacitor  $C_{VCAP}$  should be used to select the free-running frequency of the vertical oscillator in accordance with the following formula:

$$f_{fr(V)} = \frac{1}{10.8 \times R_{VREF} \times C_{VCAP}}$$

To achieve a stabilized amplitude the free-running frequency  $f_{fr(V)}$ , without adjustment, should be at least 10% lower than the minimum trigger frequency. The contributions shown in Table 2 can be assumed.

**Table 2** Calculation of f<sub>fr(V)</sub> total spread

| Contributing elements                                                     |     |

|---------------------------------------------------------------------------|-----|

| Minimum frequency offset between $f_{fr(V)}$ and lowest trigger frequency | 10% |

| Spread of IC                                                              | ±3% |

| Spread of R <sub>VREF</sub>                                               | ±1% |

| Spread of C <sub>VCAP</sub>                                               | ±5% |

| Total                                                                     | 19% |

Result for 50 to 160 Hz application:

$$f_{fr(V)} = \frac{50 \text{ Hz}}{1.19} = 42 \text{ Hz}$$

The AGC of the vertical oscillator can be disabled by setting control bit AGCDIS via the I<sup>2</sup>C-bus. A precise external current has to be injected into VCAP (pin 24) to obtain the correct vertical size. This special application mode can be used when the vertical sync pulses are serrated (shifted); this condition is found in some display modes, e.g. when using a 100 Hz upconverter for video signals.

Application hint: VAGC (pin 22) has a high input impedance during scan. Therefore, the pin must not be loaded externally; otherwise non-linearities in the vertical output currents may occur due to the changing charge current during scan.

### Adjustment of vertical size, VGA overscan and EHT compensation

There are four different ways to adjust the amplitude of the differential output currents at VOUT1 and VOUT2:

- Register VGAIN changes the vertical size without affecting any other output signal of the IC; this adjustment is meant for factory alignments.

- Register VSIZE changes not only the vertical size, but also provides the correct tracking of all other related waveforms (see Section "Tracking of vertical adjustments"); this register should be used for user adjustments.

- 3. For the VGA350 mode the register VOVSCN can activate a +17% step in vertical size.

- 4. VSMOD (pin 21) can be used for a DC controlled EHT compensation of vertical size by correcting the differential output currents at VOUT1 and VOUT2; VSMOD does not affect the EW waveforms, vertical focus, pin unbalance and parallelogram corrections.

### I<sup>2</sup>C-bus autosync deflection controller for PC monitors

### **TDA4841PS**

### Adjustment of vertical position, vertical linearity and vertical linearity balance

Register VOFFS provides a DC shift at the sawtooth output VOUT1 and VOUT2 (pins 13 and 12) without affecting any other output waveform. This adjustment is meant for factory alignments.

Register VPOS provides a DC shift at the sawtooth output VOUT1 and VOUT2 with correct tracking of all other related waveforms (see Section "Tracking of vertical adjustments"). This register should be used for user adjustments. Due to the tracking the whole picture moves vertically while maintaining the correct geometry.

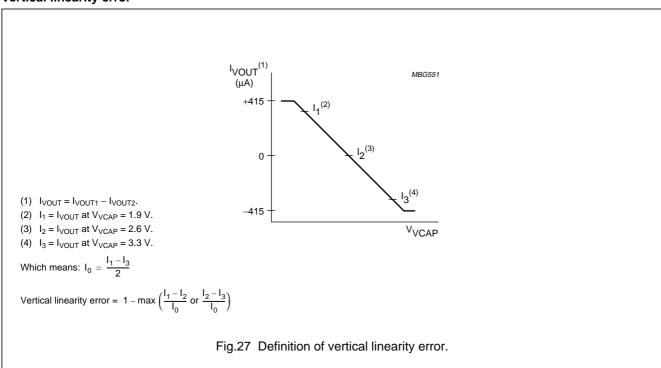

Register VLIN is used to adjust the amount of vertical S-correction in the output signal. This function can be switched off by control bit VSC.

Register VLINBAL is used to correct the unbalance of vertical S-correction in the output signal.

### Tracking of vertical adjustments

The adjustments via registers VSIZE, VOVSCN and VPOS also affect the waveforms of horizontal pincushion, vertical linearity (S-correction), vertical linearity balance, focus parabola, pin unbalance and parallelogram correction. The result of this interaction is that no readjustment of these parameters is necessary after an user adjustment of vertical picture size and vertical picture position.

#### Adjustment of vertical moire cancellation

To achieve a cancellation of vertical moire (also known as 'scan moire') the vertical picture position can be modulated by half the vertical frequency. The amplitude of the modulation is controlled by register VMOIRE and can be switched off via control bit MOD.

### Horizontal pincushion (including horizontal size, corner correction and trapezium correction)

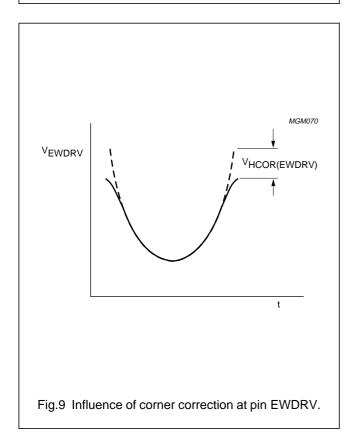

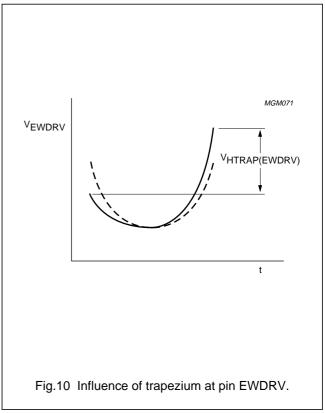

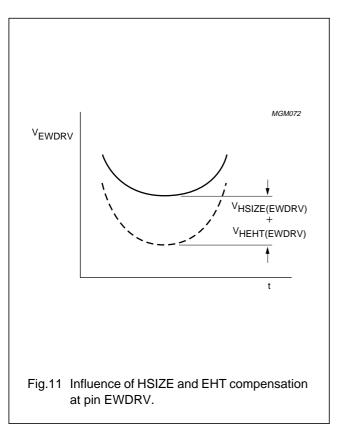

EWDRV (pin 11) provides a complete EW drive waveform. The components horizontal pincushion, horizontal size, corner correction and trapezium correction are controlled by the registers HPIN, HSIZE, HCORT, HCORB and HTRAP.

The corner correction can be adjusted separately for the top (HCORT) and bottom (HCORB) part of the picture.

The pincushion (EW parabola) amplitude, corner and trapezium correction track with vertical picture size (VSIZE) and also with the adjustment for vertical picture

position (VPOS). The corner correction does not track with horizontal pincushion (HPIN).

Further the horizontal pincushion amplitude, corner and trapezium correction track with the horizontal picture size, which is adjusted via register HSIZE and the analog modulation input HSMOD. If the DC component in the EWDRV output signal is increased via HSIZE or I<sub>HSMOD</sub>, the pincushion, corner and trapezium component of the EWDRV output will be reduced by a factor of

$$1 - \frac{V_{HSIZE} + V_{HEHT} \left(1 - \frac{V_{HSIZE}}{14.4 \text{ V}}\right)}{14.4 \text{ V}}$$

The value 14.4 V is a virtual voltage for calculation only. The output pin can not reach this value, but the gain (and DC bias) of the external application should be such that the horizontal deflection is reduced to zero when EWDRV would reach 14.4 V.

HSMOD (pin 31) can be used for a DC controlled EHT compensation by correcting horizontal size, horizontal pincushion, corner and trapezium. The control range at this pin tracks with the actual value of HSIZE. For an increasing DC component  $V_{\mbox{\scriptsize HSIZE}}$  in the EWDRV output signal, the DC component  $V_{\mbox{\scriptsize HEHT}}$  caused by  $I_{\mbox{\scriptsize HSMOD}}$  will be

reduced by a factor of  $1 - \frac{V_{HSIZE}}{14.4 \text{ V}}$  as shown in the equation above.

The whole EWDRV voltage is calculated as follows:

$$\begin{split} &V_{EWDRV,0} = 1.2 \text{ V} + [V_{HSIZE} + V_{HEHT} \times \text{f(HSIZE)} \\ &+ (V_{HPIN} + V_{HCOR} + V_{HTRAP}) \times \text{g(HSIZE,HSMOD)}] \\ &\times \text{h(I}_{HREF}) \end{split}$$

where:

$$V_{HEHT} = \frac{I_{HSMOD}}{120 \mu A} \times 0.69$$

$$f(HSIZE) = 1 - \frac{V_{HSIZE}}{14.4 \text{ V}}$$

$$g(\text{HSIZE},\text{HSMOD}) \ = \ 1 - \frac{V_{\text{HSIZE}} + V_{\text{HEHT}} \bigg( 1 - \frac{V_{\text{HSIZE}}}{14.4 \text{ V}} \bigg)}{14.4 \text{ V}}$$

$$h(I_{HREF}) = \frac{I_{HREF}}{I_{HREF \text{ at } f = 70 \text{ kHz}}}$$

### I<sup>2</sup>C-bus autosync deflection controller for PC monitors

**TDA4841PS**

Via control bit FHMULT two different modes of operation can be chosen for the EW output waveform:

#### 1. Mode 1

Horizontal size is controlled via register HSIZE and causes a DC shift at the EWDRV output. The complete waveform is also multiplied internally by a signal proportional to the line frequency [which is detected via the current at HREF (pin 28)]. This mode is to be used for driving EW diode modulator stages which require a voltage proportional to the line frequency.

#### 2. Mode 2

The EW drive waveform does not track with the line frequency. This mode is to be used for driving EW modulators which require a voltage independent of the line frequency.

### Output stage for asymmetric correction waveforms [ASCOR (pin 20)]

This output is designed as a voltage output for superimposed waveforms of vertical parabola and sawtooth. Via the I<sup>2</sup>C-bus the registers HPARAL and HPINBAL allow to change amplitude and polarity of both signals.

**Application hint:** The TDA4841PS offers two possibilities to control HPINBAL and HPARAL.

### 1. Control bit ACD = 1.

The two registers now control the horizontal phase by means of internal modulation of the PLL2 horizontal phase control. The ASCOR output (pin 20) can be left unused, but it will always provide an output signal because the ASCOR output stage is not influenced by the control bit ACD.

### 2. Control bit ACD = 0.

The internal modulation via PLL2 is disconnected. In order to obtain the required effect on the screen, pin ASCOR must now be fed to the DC amplifier which controls the DC shift of the horizontal deflection. This option is useful for applications which already use a DC shift transformer.

If the tube does not need HPINBAL and HPARAL, then pin ASCOR can be used for other purposes, i.e. for a simple dynamic convergence.

### Dynamic focus section [FOCUS (pin 32)]

This section generates a complete drive signal for dynamic focus applications. The amplitude of the horizontal parabola is internally stabilized, thus it is independent of the horizontal frequency. The amplitude can be adjusted via register HFOCUS. Changing horizontal size may require a correction of HFOCUS. To compensate for the delay in external focus amplifiers a 'pre-correction' for the phase of the horizontal parabola has been implemented (see Fig.28). The amount of this pre-correction can be adjusted via register HFOCAD. The amplitude of the vertical parabola is independent of frequency and tracks with all vertical adjustments. The amplitude can be adjusted via register VFOCUS. FOCUS (pin 32) is designed as a voltage output for the superimposed vertical and horizontal parabolas.

#### **B+ control function block**

The B+ control function block of the TDA4841PS consists of an Operational Transconductance Amplifier (OTA), a voltage comparator, a flip-flop and a discharge circuit (see Fig.25). This configuration allows easy applications for different B+ control concepts. See also Application Note AN96052: "B+ converter Topologies for Horizontal Deflection and EHT with TDA4855/58".

#### GENERAL DESCRIPTION

The non-inverting input of the OTA is connected internally to a high precision reference voltage. The inverting input is connected to BIN (pin 5). An internal clamping circuit limits the maximum positive output voltage of the OTA. The output itself is connected to BOP (pin 3) and to the inverting input of the voltage comparator. The non-inverting input of the voltage comparator can be accessed via BSENS (pin 4).

B+ drive pulses are generated by an internal flip-flop and fed to BDRV (pin 6) via an open-collector output stage. This flip-flop will be set at the rising edge of the signal at HDRV (pin 8). The falling edge of the output signal at BDRV has a defined delay of  $t_{d(BDRV)}$  to the rising edge of the HDRV pulse. When the voltage at BSENS exceeds the voltage at BOP, the voltage comparator output resets the flip-flop and, therefore, the open-collector stage at BDRV is floating again.

2002 Jun 24

### I<sup>2</sup>C-bus autosync deflection controller for PC monitors

**TDA4841PS**

An internal discharge circuit allows a well defined discharge of capacitors at BSENS. BDRV is active at a LOW-level output voltage (see Figs 25 and 26), thus it requires an external inverting driver stage.

The B+ function block can be used for B+ deflection modulators in many different ways. Two popular application combinations are:

- Boost converter in feedback mode (see Fig.25)

In this application the OTA is used as an error amplifier with a limited output voltage range. The flip-flop will be set at the rising edge of the signal at HDRV. A reset will be generated when the voltage at BSENS, taken from the current sense resistor, exceeds the voltage at BOP.

If no reset is generated within a line period, the rising edge of the next HDRV pulse forces the flip-flop to reset. The flip-flop is set immediately after the voltage at BSENS has dropped below the threshold voltage

VRESTART(BSENS).

- Buck converter in feed forward mode (see Fig.26)

This application uses an external RC combination at BSENS to provide a pulse width which is independent from the horizontal frequency. The capacitor is charged via an external resistor and discharged by the internal discharge circuit. For normal operation the discharge circuit is activated when the flip-flop is reset by the internal voltage comparator. The capacitor will now be discharged with a constant current until the internally controlled stop level V<sub>STOP(BSENS)</sub> is reached. This level will be maintained until the rising edge of the next HDRV pulse sets the flip-flop again and disables the discharge circuit.

If no reset is generated within a line period, the rising edge of the next HDRV pulse automatically starts the discharge sequence and resets the flip-flop. When the voltage at BSENS reaches the threshold voltage  $V_{RESTART(BSENS)}$ , the discharge circuit will be disabled automatically and the flip-flop will be set immediately. This behaviour allows a definition of the maximum duty cycle of the B+ control drive pulse by the relationship of charge current to discharge current.

### Supply voltage stabilizer, references, start-up procedures and protection functions

The TDA4841PS provides an internal supply voltage stabilizer for excellent stabilization of all internal references. An internal gap reference, especially designed for low-noise, is the reference for the internal horizontal and vertical supply voltages. All internal reference currents and drive current for the vertical output stage are derived from this voltage via external resistors.

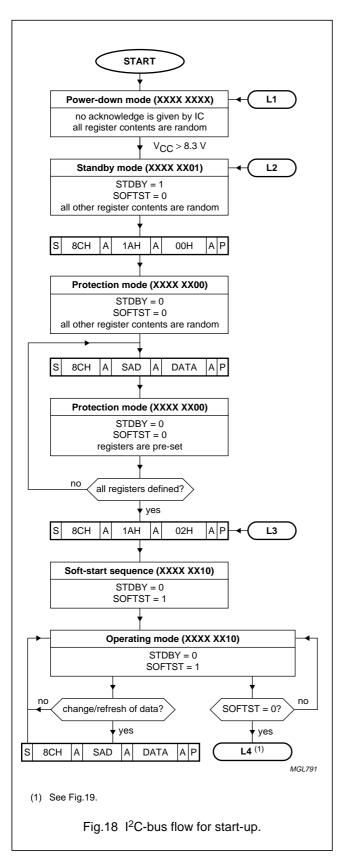

If either the supply voltage is below 8.3 V or no data from the I<sup>2</sup>C-bus has been received after power-up, the internal soft start and protection functions do not allow any of those outputs [HDRV, BDRV, VOUT1, VOUT2 and HUNLOCK (see Fig.22)] to be active.

For supply voltages below 8.3 V the internal I<sup>2</sup>C-bus will not generate an acknowledge and the IC is in standby mode. This is because the internal protection circuit has generated a reset signal for the soft start register SOFTST. Above 8.3 V data is accepted and all registers can be loaded. If the SOFTST register has received a set from the I<sup>2</sup>C-bus, the internal soft start procedure is released, which activates all outputs which are mentioned above.

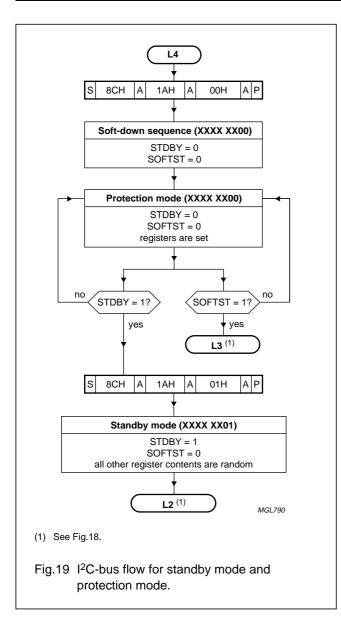

If during normal operation the supply voltage has dropped below 8.1 V, the protection mode is activated and HUNLOCK (pin 17) changes to the protection status and is floating. This can be detected by the microprocessor.

This protection mode has been implemented in order to protect the deflection stages and the picture tube during start-up, shut-down and fault conditions. This protection mode can be activated as shown in Table 3.

### I<sup>2</sup>C-bus autosync deflection controller for PC monitors

### **TDA4841PS**

Table 3 Activation of protection mode

| ACTIVATION                                 | RESET                                                                             |

|--------------------------------------------|-----------------------------------------------------------------------------------|

| Low supply voltage at pin 10               | increase supply voltage, reload registers, soft start via I <sup>2</sup> C-bus    |

| Power dip, below 8.1 V                     | reload registers,<br>soft start via I <sup>2</sup> C-bus or via<br>supply voltage |

| X-ray protection XRAY (pin 2) triggered    | reload registers,<br>soft start via I <sup>2</sup> C-bus                          |

| HPLL2 (pin 30) externally pulled to ground | release pin 30                                                                    |

When the protection mode is active, several pins of the TDA4841PS are forced into a defined state:

HDRV (horizontal driver output) is floating

BDRV (B+ control driver output) is floating

(see Figs 22 and 23).

HUNLOCK (indicates, that the frequency-to-voltage converter is out of lock) is floating (HIGH via external pull-up resistor)

CLBL provides a continuous blanking signal VOUT1 and VOUT2 (vertical outputs) are floating The capacitor at HPLL2 is discharged.

If the soft start procedure is activated via the  $I^2C$ -bus, all of these actions will be performed in a well defined sequence

### Power dip recognition

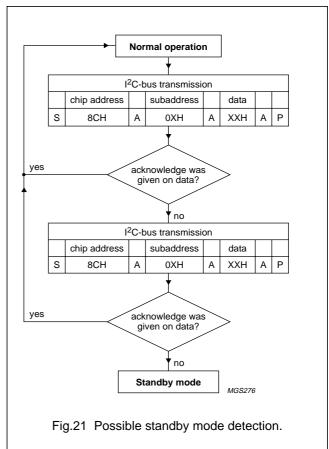

In standby mode the I<sup>2</sup>C-bus will only answer with an acknowledge when data is sent to the control register 1AH. This register contains the standby and soft start control bit.

If the I<sup>2</sup>C-bus master transmits data to another register, an acknowledge is given after the chip address and the subaddress; an acknowledge is not given after the data. This indicates that data can be stored into normal registers only in soft start mode.

If the supply voltage drops below 8.1 V the deflection controller leaves normal operation and changes to standby mode. The microcontroller can check this state by sending data into a register with the subaddress 0XH.

The acknowledge will only be given on the data if the IC is active.

Due to this behaviour the start-up of the TDA4841PS is defined as follows: the first data that is transferred to the deflection controller must be sent to the control register with subaddress 1AH. Any other subaddress will not lead to an acknowledge. This is a limitation in checking the I<sup>2</sup>C-busses of the monitor during start-up.

### I<sup>2</sup>C-bus autosync deflection controller for PC monitors

**TDA4841PS**

#### **LIMITING VALUES**

In accordance with the Absolute Maximum Rating System (IEC 60134); all voltages measured with respect to ground.

| SYMBOL                | PARAMETER                                             | CONDITIONS | MIN.  | MAX.            | UNIT |

|-----------------------|-------------------------------------------------------|------------|-------|-----------------|------|

| V <sub>CC</sub>       | supply voltage                                        |            | -0.5  | +13.2           | V    |

| V <sub>i(n)</sub>     | input voltage                                         |            |       |                 |      |

|                       | pin BIN                                               |            | -0.5  | +6.0            | V    |

|                       | pins HSYNC, VSYNC, VREF, HREF, VSMOD and HSMOD        |            | -0.5  | +6.5            | V    |

|                       | pins SDA, SCL and XRAY                                |            | -0.5  | +8.0            | V    |

| V <sub>o(n)</sub>     | output voltage                                        |            |       |                 |      |

|                       | pins VOUT2, VOUT1 and HUNLOCK                         |            | -0.5  | +6.5            | V    |

|                       | pins BDRV and HDRV                                    |            | -0.5  | +13.2           | V    |

| V <sub>I/O(n)</sub>   | input/output voltages at pins BOP and BSENS           |            | -0.5  | +6.0            | V    |

| I <sub>o(HDRV)</sub>  | horizontal driver output current                      |            | _     | 100             | mA   |

| I <sub>i(HFLB)</sub>  | horizontal flyback input current                      |            | -10   | +10             | mA   |

| I <sub>o(CLBL)</sub>  | video clamping pulse/vertical blanking output current |            | _     | -10             | mA   |

| I <sub>o(BOP)</sub>   | B+ control OTA output current                         |            | _     | 1               | mA   |

| I <sub>o(BDRV)</sub>  | B+ control driver output current                      |            | _     | 50              | mA   |

| I <sub>o(EWDRV)</sub> | EW driver output current                              |            | _     | -5              | mA   |

| V <sub>o(EWDRV)</sub> | maximum EW driver output voltage                      |            | -0.5  | V <sub>CC</sub> | V    |

| I <sub>o(FOCUS)</sub> | focus driver output current                           |            | _     | <b>-</b> 5      | mA   |

| T <sub>amb</sub>      | ambient temperature                                   |            | -20   | +70             | °C   |

| Tj                    | junction temperature                                  |            | _     | 150             | °C   |

| T <sub>stg</sub>      | storage temperature                                   |            | -55   | +150            | °C   |

| V <sub>esd</sub>      | electrostatic discharge voltage for all pins          | note 1     | -150  | +150            | V    |

|                       |                                                       | note 2     | -2000 | +2000           | V    |

### **Notes**

1. Machine model: 200 pF; 0.75  $\mu H;$  10  $\Omega.$

2. Human body model: 100 pF; 7.5  $\mu$ H; 1500  $\Omega$ .

### THERMAL CHARACTERISTICS

| SYMBOL               | PARAMETER                                   | CONDITIONS  | VALUE | UNIT |

|----------------------|---------------------------------------------|-------------|-------|------|

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | in free air | 55    | K/W  |

### **QUALITY SPECIFICATION**

In accordance with "URF-4-2-59/601"; EMC emission/immunity test in accordance with "DIS 1000 4.6" (IEC 801.6).

| SYMBOL           | PARAMETER     | CONDITIONS | MIN. | TYP. | MAX. | UNIT |

|------------------|---------------|------------|------|------|------|------|

| V <sub>EMC</sub> | emission test | note 1     | _    | 1.5  | _    | mV   |

|                  | immunity test | note 1     | _    | 2.0  | _    | V    |

#### Note

1. Tests are performed with application reference board. Tests with other boards will have different results.

# I<sup>2</sup>C-bus autosync deflection controller for PC monitors

**TDA4841PS**

### **CHARACTERISTICS**

$V_{CC}$  = 12 V;  $T_{amb}$  = 25 °C; peripheral components in accordance with Fig.1; unless otherwise specified.

| SYMBOL                      | PARAMETER                                                   | CONDITIONS                                                  | MIN.       | TYP.      | MAX. | UNIT |

|-----------------------------|-------------------------------------------------------------|-------------------------------------------------------------|------------|-----------|------|------|

| Horizontal synd             | separator                                                   |                                                             | · ·        |           | -1   | -1   |

| INPUT CHARACTE              | RISTICS FOR DC-COUPLED TTL SIGNA                            | ALS: PIN HSYNC                                              |            |           |      |      |

| V <sub>i(HSYNC)</sub>       | sync input signal voltage                                   |                                                             | 1.7        | _         | _    | V    |

| V <sub>HSYNC(sl)</sub>      | slicing voltage level                                       |                                                             | 1.2        | 1.4       | 1.6  | V    |

| t <sub>r(HSYNC)</sub>       | rise time of sync pulse                                     |                                                             | 10         | _         | 500  | ns   |

| t <sub>f(HSYNC)</sub>       | fall time of sync pulse                                     |                                                             | 10         | _         | 500  | ns   |

| t <sub>W(HSYNC)(min)</sub>  | minimum width of sync pulse                                 |                                                             | 0.7        | _         | _    | μs   |

| I <sub>i(HSYNC)</sub>       | input current                                               | $V_{i(HSYNC)} = 0.8 \text{ V}$                              | _          | _         | -200 | μΑ   |

|                             |                                                             | $V_{i(HSYNC)} = 5.5 \text{ V}$                              | _          | _         | 10   | μΑ   |

| INPUT CHARACTE              | RISTICS FOR AC-COUPLED VIDEO SIGI                           | NALS (SYNC-ON-VIDEO, NEGAT                                  | IVE SYNC I | POLARITY) | '    | '    |

| V <sub>HSYNC</sub>          | sync amplitude of video input signal voltage                | $R_{\text{source}} = 50 \ \Omega$                           | _          | 300       | _    | mV   |

| V <sub>HSYNC(AC,sl)</sub>   | slicing voltage level (measured from top sync)              | $R_{\text{source}} = 50 \ \Omega$                           | 90         | 120       | 150  | mV   |

| V <sub>clamp(HSYNC)</sub>   | top sync clamping voltage level                             | $R_{\text{source}} = 50 \Omega$                             | 1.1        | 1.28      | 1.5  | V    |

| I <sub>ch(HSYNC)</sub>      | charge current for coupling capacitor                       | $V_{i(HSYNC)} > V_{clamp(HSYNC)}$                           | 1.7        | 2.4       | 3.4  | μΑ   |

| t <sub>W(HSYNC)(min)</sub>  | minimum width of sync pulse                                 |                                                             | 0.7        | _         | _    | μs   |

| R <sub>source(max)</sub>    | maximum source resistance                                   | duty cycle = 7%                                             | _          | _         | 1500 | Ω    |

| R <sub>i(diff)(HSYNC)</sub> | differential input resistance                               | during sync                                                 | _          | 80        | _    | Ω    |

| Automatic pola              | rity correction for horizontal syn                          | C                                                           | '          | '         | •    |      |

| $\frac{t_{P(H)}}{t_{H}}$    | horizontal sync pulse width related to t <sub>H</sub>       |                                                             | _          | _         | 25   | %    |

| t <sub>d(HPOL)</sub>        | delay time for changing polarity                            |                                                             | 0.3        | _         | 1.8  | ms   |

| Vertical sync in            |                                                             |                                                             |            |           | 1    |      |

| $t_{int(V)}$                | integration time for generation of a vertical trigger pulse | f <sub>H</sub> = 15.625 kHz;<br>I <sub>HREF</sub> = 0.52 mA | 14         | 20        | 26   | μs   |

|                             |                                                             | f <sub>H</sub> = 31.45 kHz;<br>I <sub>HREF</sub> = 1.052 mA | 7          | 10        | 13   | μs   |

|                             |                                                             | f <sub>H</sub> = 64 kHz;<br>I <sub>HREF</sub> = 2.141 mA    | 3.9        | 5.7       | 6.5  | μs   |

|                             |                                                             | f <sub>H</sub> = 100 kHz;<br>I <sub>HREF</sub> = 3.345 mA   | 2.5        | 3.8       | 4.5  | μs   |

| Vertical sync sl            | licer (DC-coupled, TTL compatibl                            | e): pin VSYNC                                               |            |           |      |      |

| V <sub>i(VSYNC)</sub>       | sync input signal voltage                                   |                                                             | 1.7        | _         | _    | ٧    |

| V <sub>VSYNC(sl)</sub>      | slicing voltage level                                       |                                                             | 1.2        | 1.4       | 1.6  | ٧    |

| I <sub>i(VSYNC)</sub>       | input current                                               | 0 V < V <sub>i(VSYNC)</sub> < 5.5 V                         | _          | _         | ±10  | μΑ   |

# $\ensuremath{\mathsf{I}}^2\ensuremath{\mathsf{C}}\text{-bus}$ autosync deflection controller for PC monitors

### TDA4841PS

| SYMBOL                       | PARAMETER                                                                              | CONDITIONS                                                          | MIN. | TYP. | MAX. | UNIT |

|------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------|------|------|------|------|

| Automatic pola               | rity correction for vertical sync                                                      |                                                                     |      |      | - 1  |      |

| t <sub>VSYNC(max)</sub>      | maximum width of vertical sync pulse                                                   |                                                                     | _    | _    | 400  | μs   |

| t <sub>d(VPOL)</sub>         | delay time for changing polarity                                                       |                                                                     | 0.45 | _    | 1.8  | ms   |

| Video clamping               | g/vertical blanking output: pin CL                                                     | BL                                                                  |      |      |      |      |

| t <sub>clamp(CLBL)</sub>     | width of video clamping pulse                                                          | measured at V <sub>CLBL</sub> = 3 V                                 | 0.6  | 0.7  | 0.8  | μs   |

| V <sub>clamp(CLBL)</sub>     | top voltage level of video clamping pulse                                              |                                                                     | 4.32 | 4.75 | 5.23 | V    |

| TC <sub>clamp</sub>          | temperature coefficient of V <sub>clamp(CLBL)</sub>                                    |                                                                     | _    | 4    | _    | mV/K |

| STPS <sub>clamp</sub>        | steepness of slopes for clamping pulse                                                 | $R_L = 1 \text{ M}\Omega; C_L = 20 \text{ pF}$                      | _    | 50   | _    | ns/V |

| t <sub>d</sub> (HSYNCt-CLBL) | delay between trailing edge of<br>horizontal sync and start of<br>video clamping pulse | clamping pulse triggered<br>on trailing edge of<br>horizontal sync; | _    | 130  | _    | ns   |

| t <sub>clamp(max)</sub>      | maximum duration of video clamping pulse referenced to end of horizontal sync          | control bit CLAMP = 0;<br>measured at V <sub>CLBL</sub> = 3 V       | _    | _    | 1.0  | μs   |

| t <sub>d(HSYNCI-CLBL)</sub>  | delay between leading edge of<br>horizontal sync and start of<br>video clamping pulse  | clamping pulse triggered on leading edge of horizontal sync;        | _    | 300  | _    | ns   |

| t <sub>clamp(max)</sub>      | maximum duration of video clamping pulse referenced to end of horizontal sync          | control bit CLAMP = 1;<br>measured at V <sub>CLBL</sub> = 3 V       | _    | _    | 0.15 | μs   |

| V <sub>blank(CLBL)</sub>     | top voltage level of vertical blanking pulse                                           | notes 1 and 2                                                       | 1.7  | 1.9  | 2.1  | V    |

| t <sub>blank(CLBL)</sub>     | width of vertical blanking pulse                                                       | control bit VBLK = 0                                                | 220  | 260  | 300  | μs   |

|                              | at pins CLBL and HUNLOCK                                                               | control bit VBLK = 1                                                | 305  | 350  | 395  | μs   |

| TC <sub>blank</sub>          | temperature coefficient of $V_{blank(CLBL)}$                                           |                                                                     | _    | 2    | _    | mV/K |

| V <sub>scan(CLBL)</sub>      | output voltage during vertical scan                                                    | I <sub>CLBL</sub> = 0                                               | 0.59 | 0.63 | 0.67 | V    |

| TC <sub>scan</sub>           | temperature coefficient of V <sub>scan(CLBL)</sub>                                     |                                                                     | -    | -2   | _    | mV/K |

| I <sub>sink(CLBL)</sub>      | internal sink current                                                                  |                                                                     | 2.4  | _    | _    | mA   |

| I <sub>L(CLBL)</sub>         | external load current                                                                  |                                                                     | _    | _    | -3.0 | mA   |

# $\ensuremath{\mathsf{I}}^2\ensuremath{\mathsf{C}}\text{-bus}$ autosync deflection controller for PC monitors

### TDA4841PS

| SYMBOL                      | PARAMETER                                                                        | CONDITIONS                                                                                               | MIN.  | TYP.  | MAX.  | UNIT                |

|-----------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------|-------|-------|---------------------|

| Horizontal oscil            | lator: pins HCAP and HREF                                                        |                                                                                                          |       |       | 1     |                     |

| f <sub>fr(H)</sub>          | free-running frequency without PLL1 action (for testing only)                    | $R_{HBUF} = \infty;$<br>$R_{HREF} = 2.4 \text{ k}\Omega;$<br>$C_{HCAP} = 10 \text{ nF}; \text{ note } 3$ | 30.53 | 31.45 | 32.39 | kHz                 |

| $\Delta f_{fr(H)}$          | spread of free-running<br>frequency (excluding spread of<br>external components) |                                                                                                          | _     | _     | ±3.0  | %                   |

| TC <sub>fr</sub>            | temperature coefficient of free-running frequency                                |                                                                                                          | -100  | 0     | +100  | 10 <sup>-6</sup> /K |

| f <sub>H(max)</sub>         | maximum oscillator frequency                                                     |                                                                                                          | _     | _     | 130   | kHz                 |

| V <sub>HREF</sub>           | voltage at input for reference current                                           |                                                                                                          | 2.43  | 2.55  | 2.68  | V                   |

| Unlock blanking             | g detection: pin HUNLOCK                                                         |                                                                                                          | •     |       |       | •                   |

| V <sub>scan(HUNLOCK)</sub>  | low-level voltage of HUNLOCK                                                     | saturation voltage in case<br>of locked PLL1; internal<br>sink current = 1 mA                            | _     | _     | 250   | mV                  |

| V <sub>blank(HUNLOCK)</sub> | blanking level of HUNLOCK                                                        | I <sub>L</sub> = 0                                                                                       | 0.9   | 1     | 1.1   | V                   |

| TC <sub>blank</sub>         | temperature coefficient of V <sub>blank</sub> (HUNLOCK)                          |                                                                                                          | _     | -0.9  | _     | mV/K                |

| TC <sub>sink</sub>          | temperature coefficient of Isink(HUNLOCK)                                        |                                                                                                          | _     | 0.15  | _     | %/K                 |

| I <sub>sink(int)</sub>      | internal sink current                                                            | for blanking pulses;<br>PLL1 locked                                                                      | 1.4   | 2.0   | 2.6   | mA                  |

| I <sub>L(max)</sub>         | maximum external load current                                                    | V <sub>HUNLOCK</sub> = 1 V                                                                               | _     | _     | -2    | mA                  |

| I <sub>LI</sub>             | leakage current                                                                  | V <sub>HUNLOCK</sub> = 5 V in case of<br>unlocked PLL1 and/or<br>protection active                       | _     | -     | ±5    | μА                  |

| PLL1 phase cor              | mparator and frequency-locked l                                                  | oop: pins HPLL1 and HBUF                                                                                 | •     | •     |       |                     |

| t <sub>W(HSYNC)(max)</sub>  | maximum width of horizontal sync pulse (referenced to line period)               |                                                                                                          | _     | _     | 25    | %                   |

| t <sub>lock(HPLL1)</sub>    | total lock-in time of PLL1                                                       |                                                                                                          | _     | 40    | 80    | ms                  |

| I <sub>ctrl(HPLL1)</sub>    | control currents                                                                 | notes 4 and 5                                                                                            |       |       |       |                     |

|                             |                                                                                  | locked mode; level 1                                                                                     | _     | 15    | _     | μΑ                  |

|                             |                                                                                  | locked mode; level 2                                                                                     | _     | 145   | _     | μΑ                  |

| V <sub>HBUF</sub>           | buffered f/v voltage at HBUF (pin 27)                                            | minimum horizontal frequency                                                                             | _     | 2.55  | _     | V                   |

|                             |                                                                                  | maximum horizontal frequency                                                                             | -     | 0.5   | _     | V                   |

# $\ensuremath{\mathsf{I}}^2\ensuremath{\mathsf{C}}\text{-bus}$ autosync deflection controller for PC monitors

### TDA4841PS

| SYMBOL                        | PARAMETER                                                                                       | CONDITIONS                                                         | MIN. | TYP. | MAX. | UNIT |

|-------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------|------|------|------|

| Phase adjustmer               | nts and corrections via PLL1 an                                                                 | d PLL2                                                             | '    |      |      | '    |

| HPOS                          | horizontal position (referenced                                                                 | register HPOS = 0                                                  | _    | -13  | _    | %    |

|                               | to horizontal period)                                                                           | register HPOS = 127                                                | _    | 0    | _    | %    |

|                               |                                                                                                 | register HPOS = 255                                                | _    | 13   | -    | %    |

| HPINBAL                       | horizontal pin unbalance correction via HPLL2                                                   | register HPINBAL = 0;<br>note 6                                    | _    | -1.2 | _    | %    |

|                               | (referenced to horizontal period)                                                               | register HPINBAL = 63;<br>note 6                                   | _    | 1.2  | _    | %    |

|                               |                                                                                                 | register HPINBAL = 32;<br>note 6                                   | _    | 0.02 | _    | %    |

| HPARAL                        | horizontal parallelogram correction (referenced to                                              | register HPARAL = 0;<br>note 6                                     | _    | -1.2 | _    | %    |

|                               | horizontal period)                                                                              | register HPARAL = 63;<br>note 6                                    | _    | 1.2  | _    | %    |

|                               |                                                                                                 | register HPARAL = 32;<br>note 6                                    | _    | 0.02 | _    | %    |

| HMOIRE                        | relative modulation of horizontal position by                                                   | register HMOIRE = 0;<br>control bit MOD = 0                        | _    | 0    | _    | %    |

|                               | $1\frac{1}{2}$ horizontal frequency;<br>phase alternates with $1\frac{1}{2}$ vertical frequency | register HMOIRE = 63;<br>control bit MOD = 0                       | _    | 0.02 | -    | %    |

|                               | moire cancellation off                                                                          | control bit MOD = 1                                                | -    | 0    | 1-   | %    |

| PLL2 phase dete               | ctor: pins HFLB and HPLL2                                                                       |                                                                    |      | •    | •    | •    |

| ФРLL2                         | PLL2 control (advance of horizontal drive with respect to middle of horizontal flyback)         | maximum advance;<br>register HPINBAL = 32;<br>register HPARAL = 32 | 36   | _    | -    | %    |

|                               |                                                                                                 | minimum advance; register<br>HPINBAL = 32; register<br>HPARAL = 32 | _    | 7    | -    | %    |

| I <sub>ctrl(PLL2)</sub>       | PLL2 control current                                                                            |                                                                    | -    | 75   | -    | μΑ   |

| $\Phi_{PLL2}$                 | relative sensitivity of PLL2<br>phase shift related to horizontal<br>period                     |                                                                    | _    | 28   | _    | mV/% |

| V <sub>PROT(HPLL2)(max)</sub> | maximum voltage for PLL2 protection mode/soft start                                             |                                                                    | _    | 4.6  | _    | V    |

| I <sub>ch(PLL2)</sub>         | charge current for external capacitor during soft start                                         | V <sub>HPLL2</sub> < 3.7 V                                         | _    | 1    | _    | μΑ   |

| I <sub>dch(PLL2)</sub>        | discharge current for external capacitor during soft down                                       | V <sub>HPLL2</sub> < 3.7 V                                         | _    | -1   | -    | μΑ   |

# $\ensuremath{\mathsf{I}}^2\ensuremath{\mathsf{C}}\text{-bus}$ autosync deflection controller for PC monitors

### TDA4841PS

| SYMBOL                                 | PARAMETER                                                             | CONDITIONS                                                                      | MIN.     | TYP.                     | MAX.      | UNIT                 |  |

|----------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------|----------|--------------------------|-----------|----------------------|--|

| HORIZONTAL FLYB                        | ACK INPUT: PIN HFLB                                                   | -                                                                               |          | -                        | -         |                      |  |

| V <sub>pos(HFLB)</sub>                 | positive clamping level                                               | I <sub>i(HFLB)</sub> = 5 mA                                                     | _        | 5.5                      | _         | V                    |  |

| V <sub>neg(HFLB)</sub>                 | negative clamping level                                               | $I_{i(HFLB)} = -1 \text{ mA}$                                                   | _        | -0.75                    | _         | V                    |  |

| I <sub>pos(HFLB)</sub>                 | positive clamping current                                             |                                                                                 | _        | _                        | 6         | mA                   |  |

| I <sub>neg(HFLB)</sub>                 | negative clamping current                                             |                                                                                 | _        | _                        | -2        | mA                   |  |

| V <sub>sl(HFLB)</sub>                  | slicing level                                                         |                                                                                 | _        | 2.8                      | _         | V                    |  |

| Output stage fo                        | r line driver pulses: pin HDRV                                        |                                                                                 |          |                          |           |                      |  |

| OPEN-COLLECTOR                         | R OUTPUT STAGE                                                        |                                                                                 |          |                          |           |                      |  |

| V <sub>sat(HDRV)</sub>                 | saturation voltage                                                    | $I_{o(HDRV)} = 20 \text{ mA}$                                                   | _        | _                        | 0.3       | V                    |  |

|                                        | $I_{o(HDRV)} = 60 \text{ mA}$                                         |                                                                                 | _        | _                        | 0.8       | V                    |  |

| ,                                      |                                                                       | V <sub>HDRV</sub> = 16 V                                                        | _        | _                        | 10        | μΑ                   |  |

| AUTOMATIC VARIATION OF DUTY CYCLE      |                                                                       |                                                                                 |          | •                        | •         | •                    |  |

| t <sub>HDRV(OFF)</sub> /t <sub>H</sub> | relative t <sub>OFF</sub> time of HDRV output; measured at            | $I_{o(HDRV)} = 20 \text{ mA};$<br>$f_H = 31.45 \text{ kHz}; \text{ see Fig.16}$ | 42       | 45                       | 48        | %                    |  |

|                                        | V <sub>HDRV</sub> = 3 V; HDRV duty cycle is modulated by the relation | $I_{o(HDRV)} = 20 \text{ mA};$<br>$f_H = 58 \text{ kHz}; \text{ see Fig.16}$    | 45.5     | 48.5                     | 51.5      | %                    |  |

|                                        | I <sub>HREF</sub> /I <sub>VREF</sub>                                  | $I_{o(HDRV)} = 20 \text{ mA};$<br>$f_H = 110 \text{ kHz}; \text{ see Fig.16}$   | 49       | 52                       | 55        | %                    |  |

| X-ray protection                       | n: pin XRAY                                                           | -                                                                               |          | 1                        | 1         |                      |  |

| V <sub>XRAY(sl)</sub>                  | slicing voltage level for latch                                       |                                                                                 | 6.22     | 6.39                     | 6.56      | V                    |  |

| t <sub>W(XRAY)(min)</sub>              | minimum width of trigger pulse                                        |                                                                                 | _        | 1-                       | 30        | μs                   |  |

| R <sub>i(XRAY)</sub>                   | input resistance at XRAY                                              | $V_{XRAY} < 6.38 \text{ V} + V_{BE}$                                            | 500      | -                        | -         | kΩ                   |  |

|                                        | (pin 2)                                                               | V <sub>XRAY</sub> > 6.38 V + V <sub>BE</sub>                                    | _        | 5                        | _         | kΩ                   |  |

|                                        |                                                                       | standby mode                                                                    | _        | 5                        | _         | kΩ                   |  |

| XRAY <sub>rst</sub>                    | reset of X-ray latch                                                  | pin 9 open-circuit or connected to GND                                          | set con  | trol bit SC              | FTST via  | I <sup>2</sup> C-bus |  |

|                                        |                                                                       | pin 9 connected to V <sub>CC</sub> via R <sub>XSEL</sub>                        | switch o | off V <sub>CC</sub> , th | en re-app | oly V <sub>CC</sub>  |  |

| V <sub>CC(XRAY)(min)</sub>             | minimum supply voltage for correct function of the X-ray latch        | pin 9 connected to V <sub>CC</sub> via R <sub>XSEL</sub>                        | _        | _                        | 4         | V                    |  |

| V <sub>CC(XRAY)(max)</sub>             | maximum supply voltage for reset of the X-ray latch                   | pin 9 connected to V <sub>CC</sub> via R <sub>XSEL</sub>                        | 2        | _                        | _         | V                    |  |

| R <sub>XSEL</sub>                      | external resistor at pin 9                                            | no reset via I <sup>2</sup> C-bus 56 – 130                                      |          |                          |           |                      |  |

# $\ensuremath{\mathsf{I}}^2\ensuremath{\mathsf{C}}\text{-bus}$ autosync deflection controller for PC monitors

### TDA4841PS

| SYMBOL                  | PARAMETER                                                                   | CONDITIONS                                                              | MIN.      | TYP.      | MAX.       | UNIT  |

|-------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------|-----------|------------|-------|

| Vertical oscillat       | or (oscillator frequency in applic                                          | ation without adjustment o                                              | f free-ru | nning fre | quency f   | fr(V) |

| $f_{fr(V)}$             | free-running frequency                                                      | $R_{VREF}$ = 22 k $\Omega$ ;<br>$C_{VCAP}$ = 100 nF                     | 40        | 42        | 43.3       | Hz    |