# Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note: Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp. Customer Support Dept. April 1, 2003

### 8-BIT 12CH D-A CONVERTER WITH BUFFER AMPLIFIERS

#### DESCRIPTION

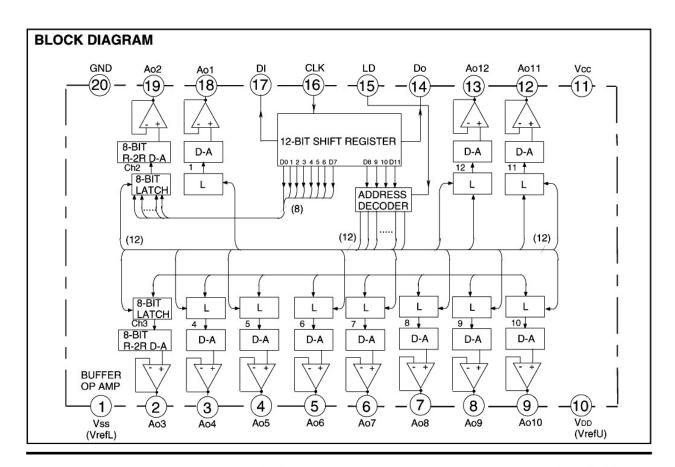

The M62352 is an integrated circuit semiconductor of CMOS structure with 12 channels of built-in D-A converters with output buffer operational amplifiers.

The 3-wire serial interface method is used for the transfer format mum wiring.

It is able to cascading serial use with Do terminal.

The output buffer operational amplifier operates in the whole voltage range from power supply to ground for both

#### **FEATURES**

- 12bit serial data input(3-wire serial data transfer method)

- •Highly stable output buffer operational amplifier allow operation in the all voltage range from power supply to ground.

#### **APPLICATION**

Adjustment/control of industrial or home-use electronic equipment, such as VTR camera, VTR set, TV, and CRT

# 8-BIT 12CH D-A CONVERTER WITH BUFFER AMPLIFIERS

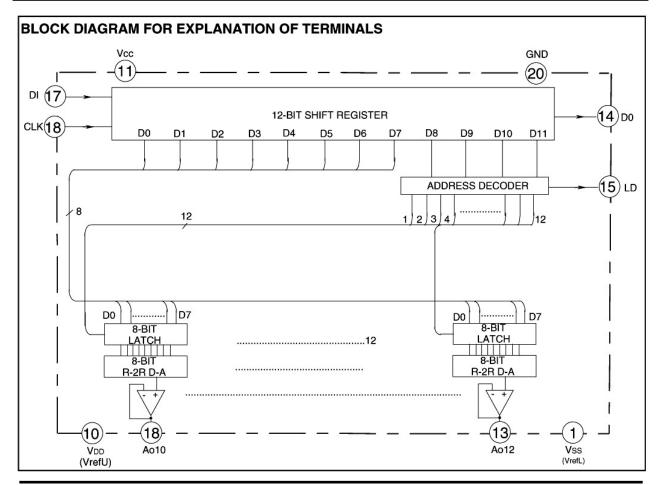

#### **EXPLANATION OF TERMINALS**

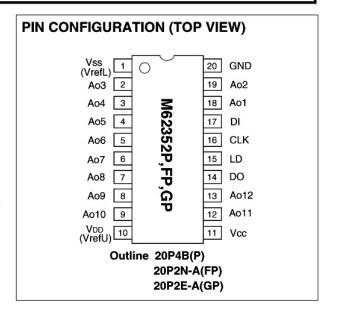

| Pin No.   | Symbol | Function                                                  |

|-----------|--------|-----------------------------------------------------------|

| 17        | DI     | Serial data input terminal                                |

| 14        | DO     | Serial data output terminal                               |

| 16        | CLK    | Serial clock input terminal                               |

| 15        | LD     | LD terminal input high level than latch circuit data load |

|           | Ao1    |                                                           |

| 19        | Ao2    |                                                           |

| 2         | Ao3    |                                                           |

| ②<br>③    | Ao4    |                                                           |

| 4         | Ao5    |                                                           |

| <b>5</b>  | Ao6    | 8-bit D-A converter output terminal                       |

|           | Ao7    | 8-bit b-A converter output terminal                       |

| 7         | Ao8    |                                                           |

| 8         | Ao9    |                                                           |

| 9         | Ao10   |                                                           |

| 12        | Ao11   |                                                           |

|           | Ao12   |                                                           |

| ①<br>①    | Vcc    | Power supply terminal                                     |

| <b>29</b> | GND    | Digital and analog common GND                             |

| 10        | VDD    | D-A converter upper reference voltage input terminal      |

| 1         | Vss    | D-A converter lower reference voltage input terminal      |

# 8-BIT 12CH D-A CONVERTER WITH BUFFER AMPLIFIERS

#### **DIGITAL DATA FORMAT**

| LAST<br>LSB |    |    |       |      |    |    |    |       |           |          | → FIRST<br>MSB |

|-------------|----|----|-------|------|----|----|----|-------|-----------|----------|----------------|

| D0          | D1 | D2 | D3    | D4   | D5 | D6 | D7 | D8    | D9        | D10      | D11            |

| -           |    |    | DAC D | ATA- |    | >  | 4  | DAC : | SELECT DA | ATA——ATA | -              |

| D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | D-A output                  |

|----|----|----|----|----|----|----|----|-----------------------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | (VrefU-VrefL)/256X1+VrefL   |

| 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | (VrefU-VrefL)/256X2+VrefL   |

| 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | (VrefU-VrefL)/256X3+VrefL   |

| 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | (VrefU-VrefL)/256X4+VrefL   |

|    |    |    | :  |    |    |    |    | :                           |

| 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | (VrefU-VrefL)/256X255+VrefL |

| 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | VrefU                       |

| D8 | D9 | D10 | D11 | DAC selection |

|----|----|-----|-----|---------------|

| 0  | 0  | 0   | 0   | Don t care    |

| 0  | 0  | 0   | 1   | Ao1 selection |

| 0  | 0  | 1   | 0   | Ao2           |

| 0  | 0  | 1   | 1   | Ao3           |

| 0  | 1  | 0   | 0   | Ao4           |

| 0  | 1  | 0   | 1   | Ao5           |

| 0  | 1  | 1   | 0   | Ao6           |

| 0  | 1  | 1   | 1   | Ao7           |

| 11 | 0  | 0   | 0   | Ao8           |

| 11 | 0  | 0   | 11  | Ao9           |

| 1  | 0  | 1   | 0   | Ao10          |

| 1  | 0  | 1   | 1   | Ao11          |

| 1  | 1  | 0   | 0   | Ao12          |

| 1  | 1  | 0   | 1   | Don t care    |

| 1  | 1  | 1   | 0   | Don t care    |

| 1  | 1  | 1   | 1   | Don t care    |

\*VrefU=VDD VrefL=Vss

# 8-BIT 12CH D-A CONVERTER WITH BUFFER AMPLIFIERS

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol | Parameter                             | Conditions | Ratings                | Unit |

|--------|---------------------------------------|------------|------------------------|------|

| Vcc    | Supply voltage                        |            | -0.3~7.0               | V    |

| VDD    | D-A converter upper reference voltage |            | -0.3~7.0               | ٧    |

| VIN    | Input voltage                         |            | -0.3~Vcc+0.3           | ٧    |

| Vo     | Output voltage                        |            | -0.3~Vcc+0.3           | ٧    |

| Pd     | Power dissipation                     |            | 350(P)/350(FP)/150(GP) | mV   |

| Topr   | Operating temperature                 |            | -20~+85                | °C   |

| Tstg   | Storage temperature                   |            | -55~+125               | °C   |

#### **ELECTRICAL CHARACTERISTICS**

Digital part(Vcc,VrefU=+5V±10%,Vcc≥VrefU,GND,VrefL=0V,Ta=-20°C~+85°C, unless otherwise noted)

| Symbol      | Parameter           | Test conditions               |        | Unit    |        |       |

|-------------|---------------------|-------------------------------|--------|---------|--------|-------|

|             |                     | rest conditions               | Min.   | Тур.    | Max.   | Offic |

| Vcc         | Supply voltage      |                               | 4.5    | 5.0     | 5.5    | ٧     |

| Icc         | Circuit current     | CLK=1MHz operation<br>Ioa=0µA |        | 1.6     | 3.2    | mA    |

| lilk        | Input leak current  | Vin=0~Vcc                     | -10    |         | 10     | μΑ    |

| VIL         | Input low voltage   |                               |        |         | 0.2Vcc | V     |

| VIH         | Input high voltage  |                               | 0.8Vcc |         |        | V     |

| <b>V</b> OL | Output low voltage  | IoL=2.5mA                     |        |         | 0.4    | ٧     |

| Vон         | Output high voltage | IOH=-400µA                    |        | Vcc-0.4 |        | V     |

#### Analog part(Vcc,VrefU=+5V±10%,Vcc≥VrefU,Ta=-20°C~+85°C, unless otherwise noted)

| Symbol | Parameter                                   | Test conditions                                                                                                                       |      | Unit |         |       |

|--------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------|------|---------|-------|

| Cymbol | Parameter                                   | Test conditions                                                                                                                       | Min. | Тур. | Max.    | Offic |

| IDD    | Current dissipation                         | VrefU=5V,VrefL=0V<br>Data condition;at maximum current                                                                                |      | 1.4  | 2.5     | mA    |

| VDD    | D-A converter upper reference voltage range | The output dose not necessarily be the value within the reference voltage setting range. The output value is determined by the buffer | 3.5  |      | Vcc     | ٧     |

| Vss    | D-A converter lower reference voltage range | amplifier output voltage range(VAO)                                                                                                   | GND  |      | Vcc-3.5 | V     |

| VAO    | Buffer amplifier                            | Ioa=±100μA                                                                                                                            | 0.1  |      | Vcc-0.1 | V     |

| VAO    | output voltage range                        | Ioa=±500μA                                                                                                                            | 0.2  |      | Vcc-0.2 | V     |

| IAO    | Buffer amplifier output drive range         | Upper side saturation voltage=0.3V<br>Lower side saturation voltage=0.2V                                                              | -1   |      | 1       | mA    |

| SDL    | Differential nonlinearity error             | VrefU=4.79V                                                                                                                           | -1.0 |      | 1.0     | LSB   |

| SL     | Nonlinearity error                          | VrefL=0.95V                                                                                                                           | -1.5 |      | 1.5     | LSB   |

| Szero  | Zero code error                             | Vcc=5.5V(15mV/LSB) Without load(IoA=±0)                                                                                               | -2   |      | 2       | LSB   |

| SFULL  | Full scale error                            | ,                                                                                                                                     | -2   |      | 2       | LSB   |

| Co     | Output capacitive load                      |                                                                                                                                       |      |      | 0.1     | μF    |

| Ro     | Buffer amplifier output impedance           |                                                                                                                                       |      | 5    |         | Ω     |

# 8-BIT 12CH D-A CONVERTER WITH BUFFER AMPLIFIERS

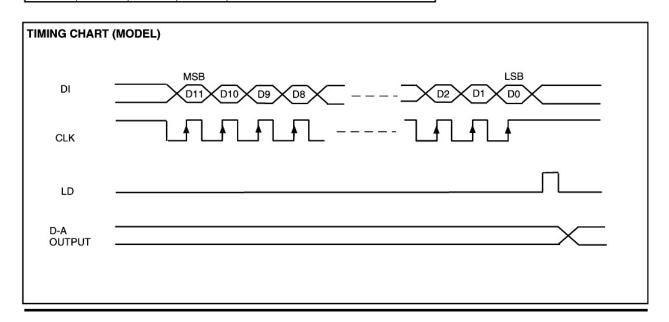

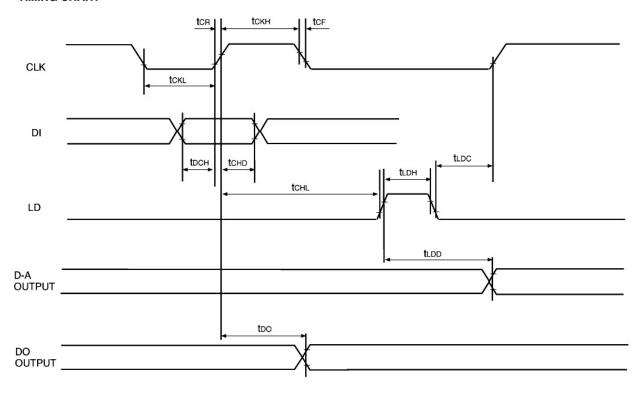

### AC CHARACTERISTICS(Vcc,VrefU=+5V±10%,Vcc≥VrefU,GND,VrefL=0V,Ta=-20~+85°C, unless otherwise noted)

|        | Parameter               | T 400            |     |       |     |      |

|--------|-------------------------|------------------|-----|-------|-----|------|

| Symbol |                         | Test conditions  | Min | Тур   | Max | Unit |

| tclk   | Clock "L"pulse width    |                  | 200 | 40.00 |     | ns   |

| tckH   | Clock "H"pulse width    |                  | 200 |       |     | ns   |

| tcr    | Clock rise time         |                  |     |       | 200 | ns   |

| tcF    | Clock fall time         |                  |     |       | 200 | ns   |

| toch   | Data setup time         |                  | 30  |       |     | ns   |

| tCHD   | Data hold time          |                  | 60  |       |     | ns   |

| tCHL   | LD setup time           |                  | 200 |       |     | ns   |

| tldc   | LD hold time            |                  | 100 |       |     | ns   |

| tldh   | LD "H" pulse width      |                  | 100 |       |     | ns   |

| too    | Data output delay time  | CL≤100pF         | 70  |       | 350 | ns   |

| tLDD   | D-A output setting time | CL≤100pF VAQ:0.5 |     |       | 300 | μs   |

### **TIMING CHART**

# 8-BIT 12CH D-A CONVERTER WITH BUFFER AMPLIFIERS

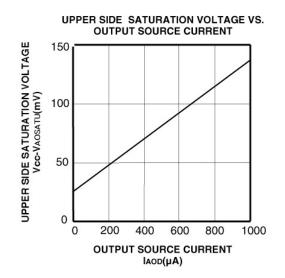

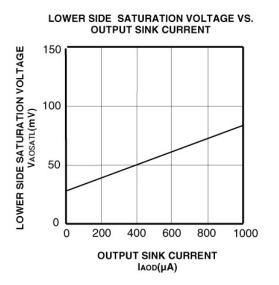

#### TYPICAL CHARACTERISTICS

SATURATION VOLTAGE VS.OUTPUT CURRENT