PWM Switching Regulator for High-performance Voltage Mode Control

# HITACHI

# Description

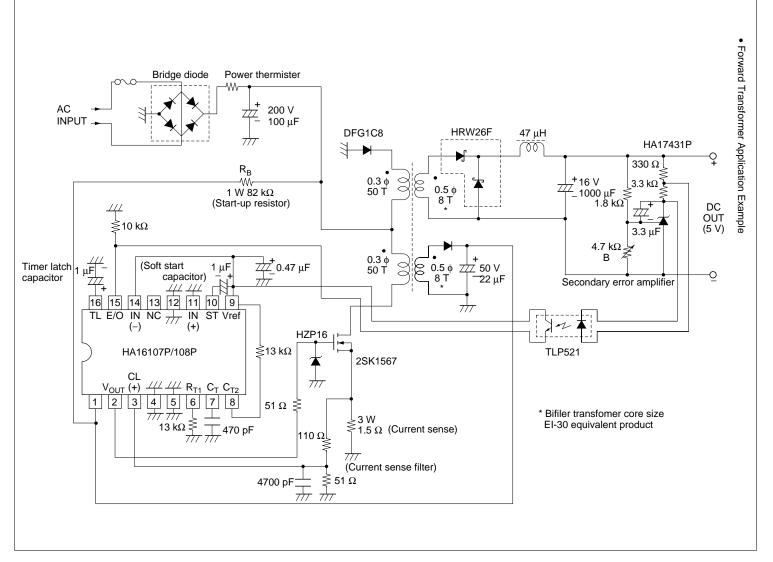

The IC products in this series are primary control switching regulator control IC's appropriate for obtaining stabilized DC voltages from commercial AC power.

These IC's can directly drive power MOS FET's, they have a timer function built in to the secondary overcurrent protection, and they can perform intermittent operation or delayed latched shutdown as protection operations in unusual conditions. They can be used to implement switching power supplies with a high level of safety due to the wide range of built-in functionality.

# Functions

- 6.45 V reference voltage

- Triangle wave generator

- Error amplifier

- Under voltage lockout protector

- PWM comparator

- Pulse-by-pulse current limitting

- Timer-latch current limitting (HA16107)

- ON/OFF timer function (HA16108)

- Soft start and quick shutdown

- Output circuit for power MOS FET driving

### Features

- Operating frequencies up to a high 600 kHz

- Built-in pre-driver circuit for driving power MOS FET

- Built-in timer latch over-current protection function (HA16107)

- The OCL enables intermittent operation by an ON/OFF timer for prevention of secondary overcurrent. (HA16108)

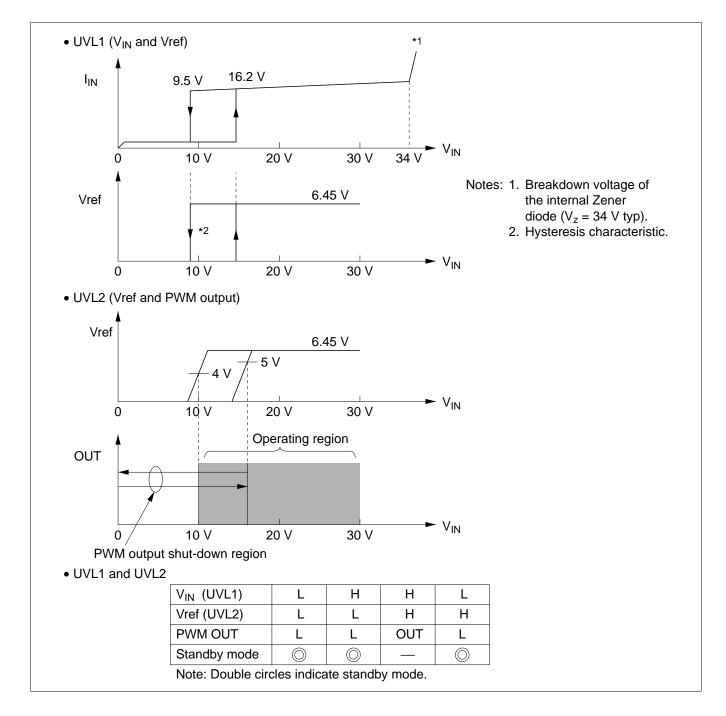

- The UVL function (under voltage lockout) is applied to both Vin and Vref.

- ON/OFF reset: an auto-reset function which is based on the time constant of an external capacitor and observation of drops in Vin.

- Since the over-voltage protection function OVP (the TL pin) only observes voltage drops in Vin, it is possible to use the OVP and ON/OFF pin for independent purposes.

- Built-in 34 V Zener diode between Vin and ground.

# **Ordering Information**

|           | Typical Thres | nold voltage |                                   |         |  |  |

|-----------|---------------|--------------|-----------------------------------|---------|--|--|

| Product   | UVL1          | OVP          | Notes                             | Package |  |  |

| HA16107P  | Hi: 16.2 V    | 7.0 V        | Timer latch protection            | DP-16   |  |  |

| HA16107FP | Lo: 9.5 V     |              |                                   | FP-16DA |  |  |

| HA16108P  | Hi: 16.2 V    | Hi: 7.0 V    | On-off timer protection           | DP-16   |  |  |

| HA16108FP | Lo: 9.5 V     | Lo: 1.3 V    | (intermittent operation possible) | FP-16DA |  |  |

### Typical Threshold Voltage

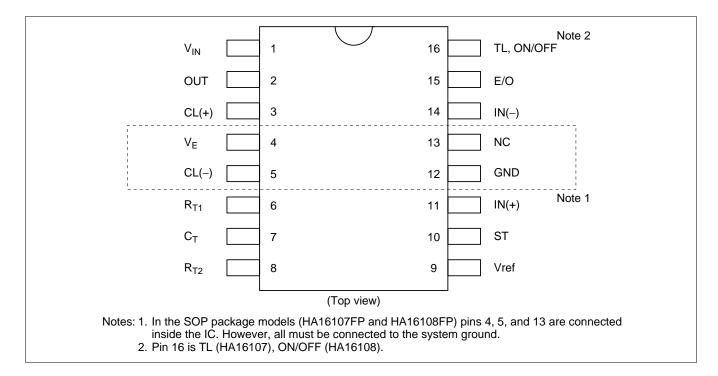

### **Pin Arrangement**

# **Pin Functions**

• HA16107P, HA16108P

| Pin No. | Symbol          | Pin Functions                           |

|---------|-----------------|-----------------------------------------|

| 1       | V <sub>IN</sub> | Input voltage                           |

| 2       | OUT             | Pulse output                            |

| 3       | CL (+)          | Current limiter                         |

| 4       | V <sub>E</sub>  | Output ground                           |

| 5       | CL (–)          | Current limiter                         |

| 6       | R <sub>T1</sub> | Timing resistor (rising time)           |

| 7       | C <sub>T</sub>  | Timing capacitor                        |

| 8       | R <sub>T2</sub> | Timing resistor (falling time)          |

| 9       | Vref            | Reference voltage output                |

| 10      | ST              | Soft start                              |

| 11      | IN (+)          | Error amp (+) input                     |

| 12      | GND             | Ground                                  |

| 13      | NC              | NC                                      |

| 14      | IN (–)          | Error amp (-) input                     |

| 15      | E/O             | Error output                            |

| 16      | TL, ON/OFF      | Timer latch (HA16107), ON/OFF (HA16108) |

| • HA16107FP, HA16108FP |                 |                                         |  |  |  |  |  |

|------------------------|-----------------|-----------------------------------------|--|--|--|--|--|

| Pin No.                | Symbol          | Pin Functions                           |  |  |  |  |  |

| 1                      | V <sub>IN</sub> | Input voltage                           |  |  |  |  |  |

| 2                      | OUT             | Pulse output                            |  |  |  |  |  |

| 3                      | CL (+)          | Current limiter                         |  |  |  |  |  |

| 4                      | GND             | Ground                                  |  |  |  |  |  |

| 5                      | GND             | Ground                                  |  |  |  |  |  |

| 6                      | R <sub>T1</sub> | Timing resistor (rising time)           |  |  |  |  |  |

| 7                      | C <sub>T</sub>  | Timing capacitor                        |  |  |  |  |  |

| 8                      | R <sub>T2</sub> | Timing resistor (falling time)          |  |  |  |  |  |

| 9                      | Vref            | Reference voltage output                |  |  |  |  |  |

| 10                     | ST              | Soft start                              |  |  |  |  |  |

| 11                     | IN (+)          | Error amp (+) input                     |  |  |  |  |  |

| 12                     | GND             | Ground                                  |  |  |  |  |  |

| 13                     | GND             | Ground                                  |  |  |  |  |  |

| 14                     | IN (–)          | Error amp (–) input                     |  |  |  |  |  |

| 15                     | E/O             | Error output                            |  |  |  |  |  |

| 16                     | TL, ON/OFF      | Timer latch (HA16107), ON/OFF (HA16108) |  |  |  |  |  |

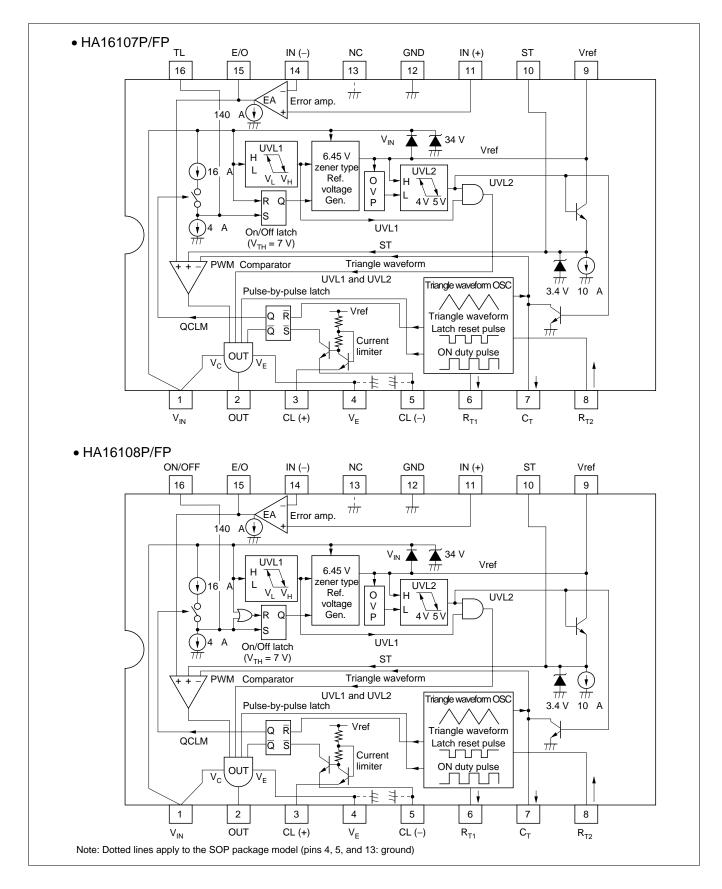

### **Block Diagram**

### **Function and Timing Chart**

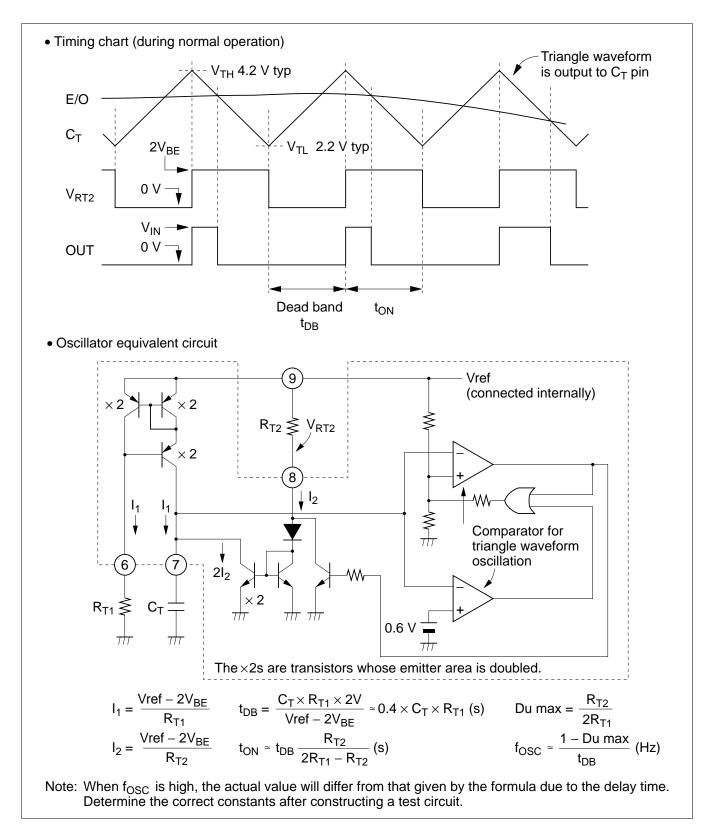

### **Triangle Waveform and PWM Output**

### 1. Timing in Normal Operation

Timing in these ICs is based on a triangular voltage waveform. The rising edge (leading edge) defines the deadband time  $t_{DB}$ . The falling edge (trailing edge) defines the ON-duty control band  $t_{ON}$ . PWM output is on in the area within  $t_{ON}$  that is bounded above by the triangle wave  $V_{CT}$  and error output  $V_{E/O}$ . The following pin outputs are related to PWM control:

- $C_T$  (pin 7): triangle-wave voltage output

- E/O (pin 15): error output voltage

- R<sub>T2</sub> (pin 8): ON-duty pulse output voltage

- OUT (pin 2): PWM pulse output (for driving the gate of a power MOS FET)

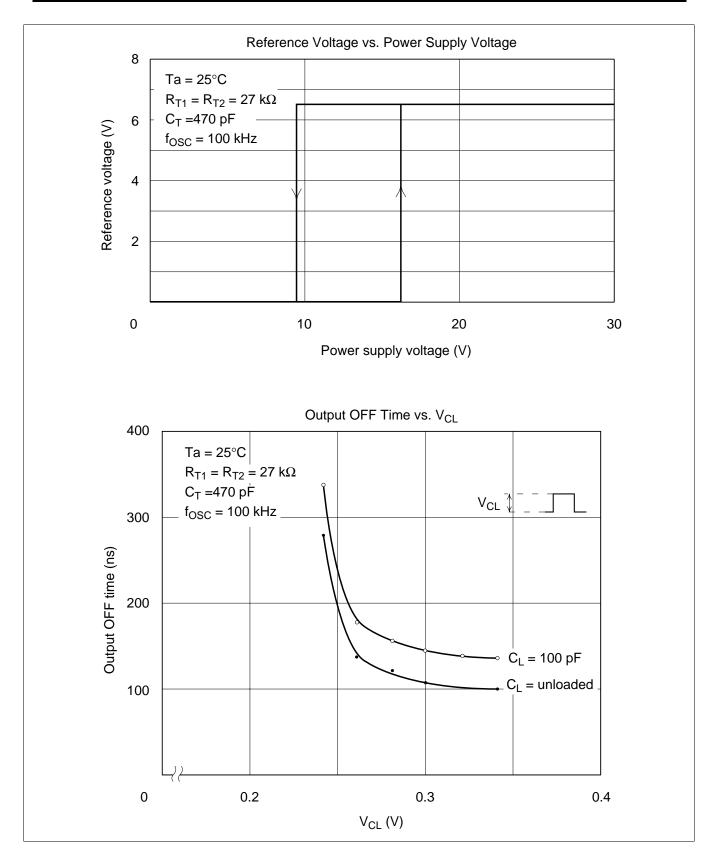

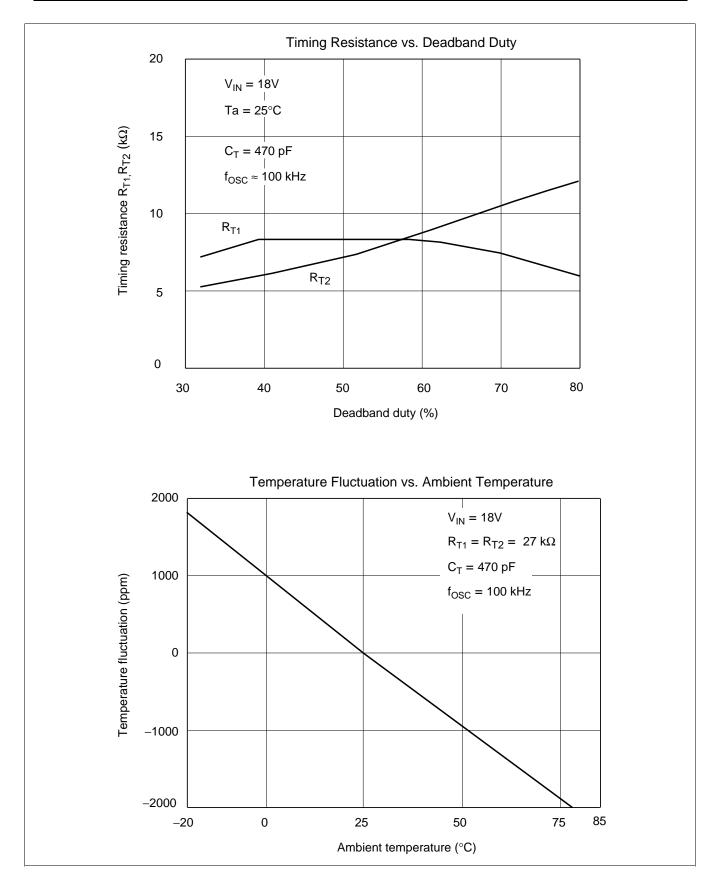

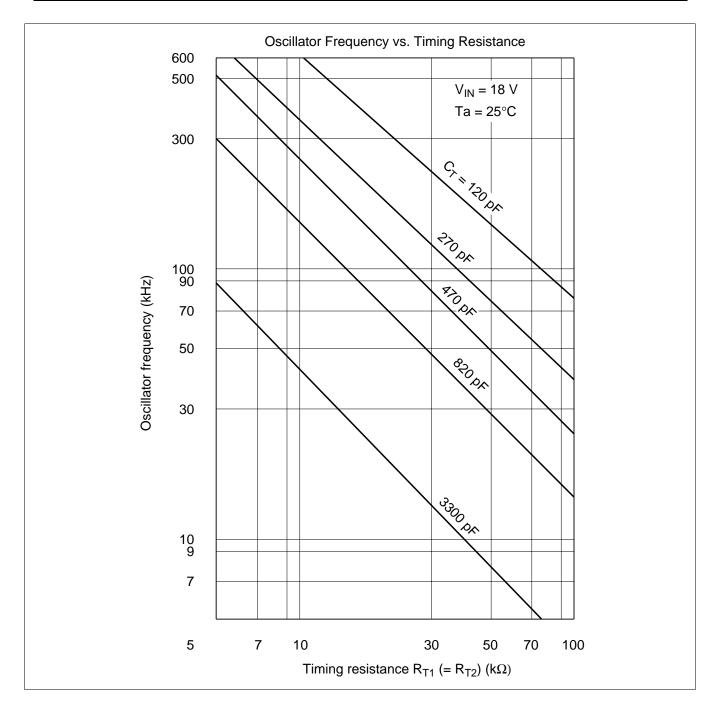

### 2. Triangle Oscillator, Waveform and Frequency

The triangle oscillator in these ICs generates a triangular waveform by charging and discharging timing capacitor  $C_T$  with a constant current, as shown in the equivalent circuit. The  $C_T$  charge current is:

$$I(C_{Tchg}) = I_1 = \frac{V_{REF} - 2V_{BE}}{R_{T1}}$$

The discharge current is:

$$I(C_{Tdischg}) = 2I_2 - I_1, \text{ where } I_2 = \frac{V_{REF} - 2V_{BE}}{R_{T2}}$$

In these equations Vref (reference voltage) is typically 6.45 V, and  $V_{BE}$  (base-emitter voltage of internal transistors) is about 0.7 V.

The deadband time is:

$$t_{\text{DB}} = \frac{C_{\text{T}} \times R_{\text{T1}} \times 2V}{V_{\text{REF}} - 2V_{\text{BE}}} + 0.8 \,\mu\text{s}$$

$$\approx 0.4 \times C_{\text{T}} \times R_{\text{T1}} + 0.8 \,\mu\text{s}$$

The ON-duty time is:

$$t_{\text{ON}} = t_{\text{DB}} \times \frac{R_{\text{T2}}}{2R_{\text{T1}} - R_{\text{T2}}}$$

The 0.8 µs in these equations is a correction term for internal circuit delays.

The maximum ON-duty is

Du max =

$$\frac{R_{T2}}{2R_{T1}}$$

The oscillating frequency is:

$$f_{OSC} = \frac{1}{\frac{t_{DB}}{1 - Du \max} + 0.8 \,\mu s}}$$

$$= \frac{1}{\frac{0.8 \times C_T \times R_{T1}^2}{2R_{T1} - R_{T2}} + 0.8 \,\mu s}}$$

(Hz)

When  $R_{T1} = R_{T2}$ , the maximum ON-duty is 50%, and:

$$f_{OSC} \approx \frac{1}{0.8 C_T R_{T1} + 0.8 \,\mu s}$$

(Hz)

This approximation is fairly close, but it should be checked in-circuit.

3. Programming of Maximum ON-Duty (Du Max)

The preceding equations should be used to program the deadband or maximum ON-duty. The following table gives a summary.

| Condition            | $R_{T1} > R_{T2}$ | $\mathbf{R}_{T1} = \mathbf{R}_{T2}$ | $R_{T1} < R_{T2}$ |

|----------------------|-------------------|-------------------------------------|-------------------|

| Triangle<br>waveform |                   |                                     |                   |

| Du max               | Less than 50%     | 50%                                 | Greater than 50%* |

Note: In a primary-control switching regulator, Du Max > 50% is dangerous because the transformer will saturate.

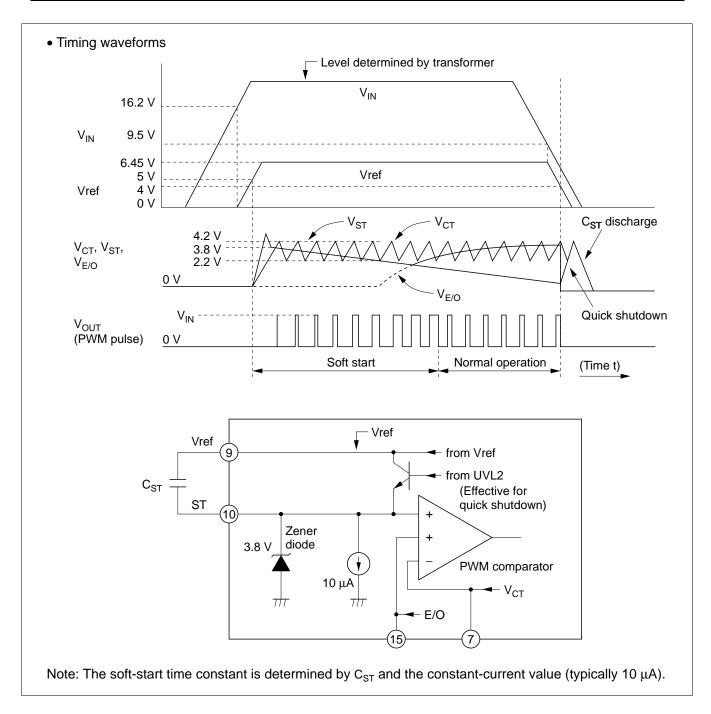

### Soft Start and Quick Shutdown

One purpose of the soft-start function is to protect the switching controller and power MOSFET from surges at power-up. Another purpose is to let the secondary-side DC voltage rise smoothly.

When power goes off, the quick-shutdown function rapidly discharges the capacitor in the soft-start circuit (and at the same time switches the PWM output off) to prepare for the next power-on.

The soft-start function in these ICs lets the PWM output develop smoothly from zero to the designated pulse width at power-up. The soft-start voltage is the 3.8 V voltage value of an internal Zener diode, so the PWM output is able to start widening gradually as soon as the soft-start function starts operating. The soft-start function will start promptly even if  $C_{sT}$  is large.

The soft-start and quick-shutdown modes are selected automatically in the IC, under control of the UVL signal.

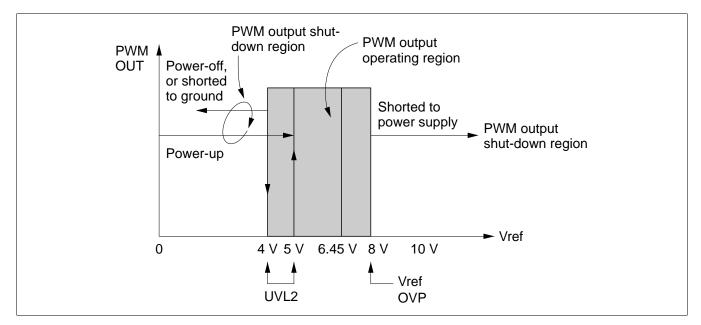

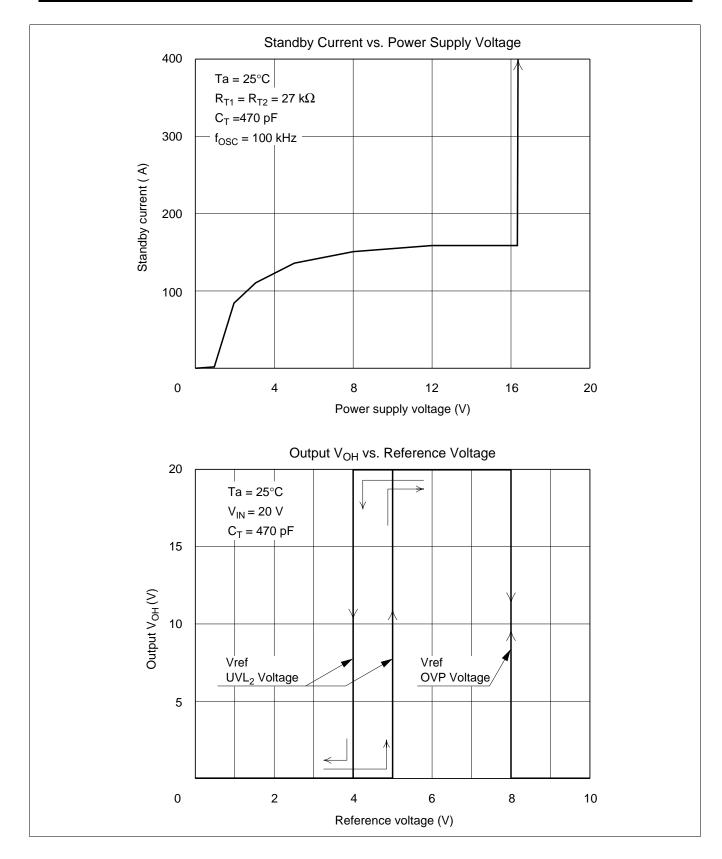

### Vref Protection Functions: Overvoltage and Undervoltage

Vref overvoltage and undervoltage conditions are detected by the overvoltage detection circuit and UVL2 circuit. PWM output shuts down when Vref  $\geq 8$  V. UVL2 detects undervoltage with hysteresis between approximately 4 V and 5 V. PWM output also shuts down below these voltages. It follows that PWM output will shut off whenever the Vref pin is shorted to the power supply (V<sub>IN</sub>) or ground (GND). PWM output also shuts off when V<sub>IN</sub> is turned on or off.

The following diagram shows how these protection functions operate when power comes on and goes off (Vref < 6.45 V), and when a high external voltage is applied to the Vref pin (Vref > 6.45 V).

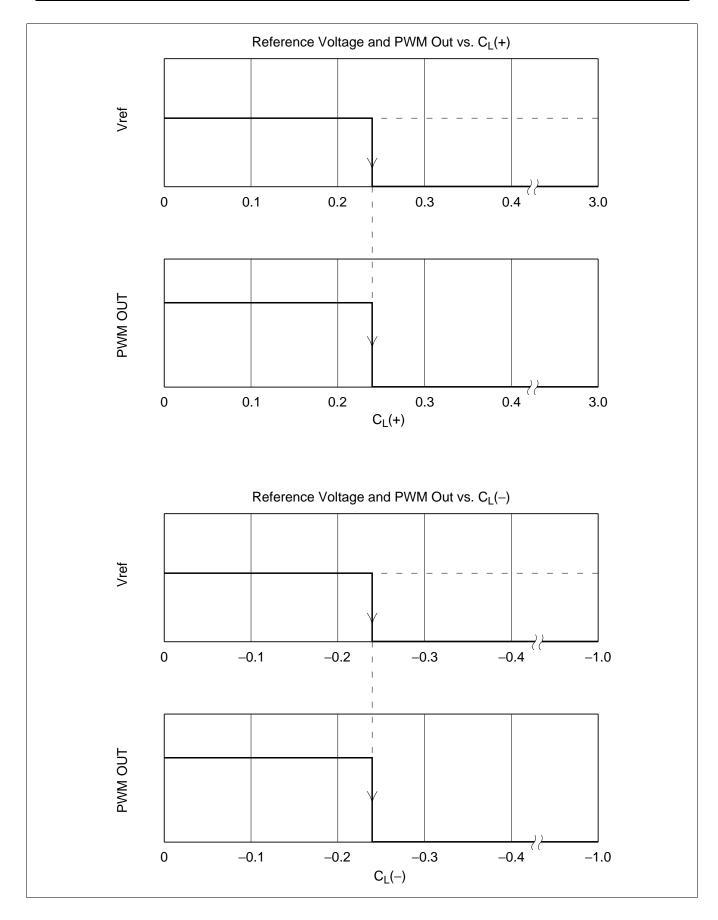

### 1. Current-Limiter Circuit

The current limiter pin (CL) is connected to the emitter of an npn transistor, as shown in the block diagram. The threshold voltage is 240 mV typ. The switching speed of this circuit is approximately 100 ns from detection of overcurrent to shut-down of PWM output. Switching speed increases with the strength of the signal input to the CL pin.

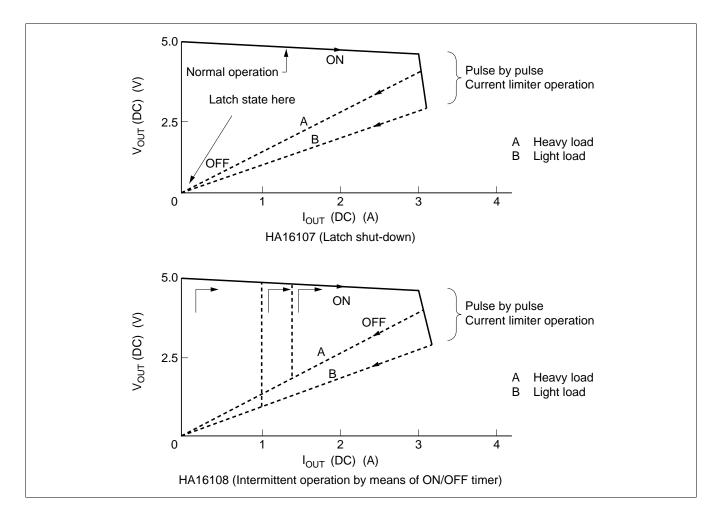

Instead of simple pulse-by-pulse current limiting, in these ICs the current limiting circuit is linked to the timer-and-latch or ON/OFF timer circuit, and also detects the degree of overcurrent. The overcurrent value is determined from the point at which current limiting is triggered in the ON-duty cycle. With a large overcurrent (causing current limiting to operate even at a small ON-duty), the IC automatically shortens the timer time.

### **Undervoltage Lockout and PWM Output**

The undervoltage lockout function turns off the PWM pulse output when the controller's supply voltage goes below a designated value. These ICs have two undervoltage lockout circuits. The UVL1 circuit senses the supply voltage  $V_{IN}$ . The UVL2 circuit senses the Vref voltage. A feature of these ICs is that PWM output is turned on only when both voltages are above designated values. Otherwise, the IC operates in standby mode.

The two built-in undervoltage lockout circuits make it possible to configure an extremely safe power supply system. PWM output will shut down under a variety of abnormal conditions, such as if Vref is shorted to ground while  $V_{IN}$  is applied.

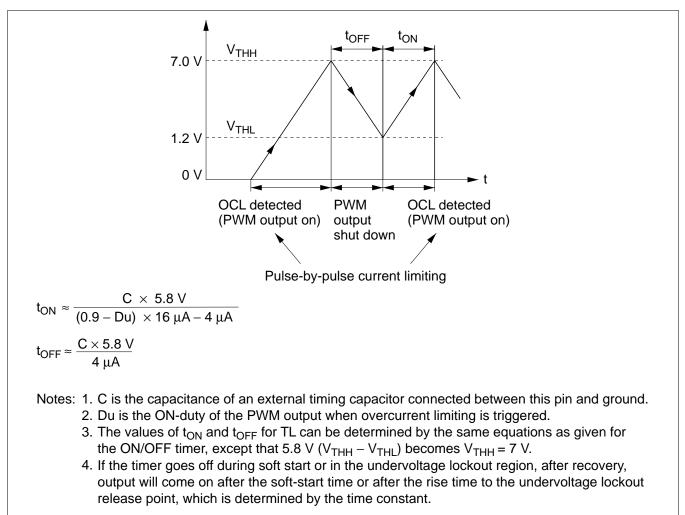

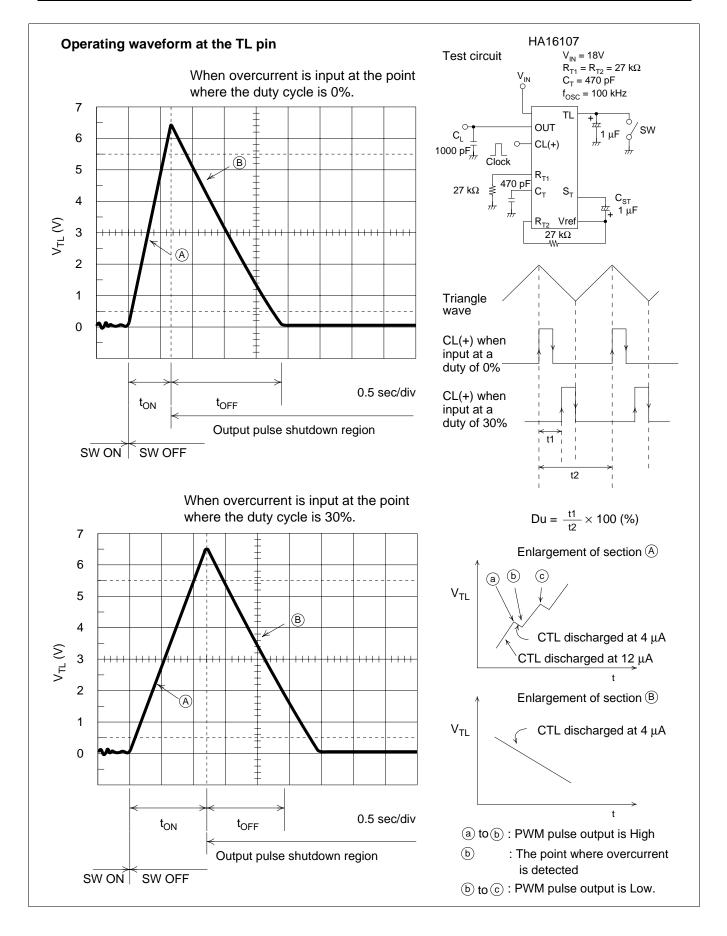

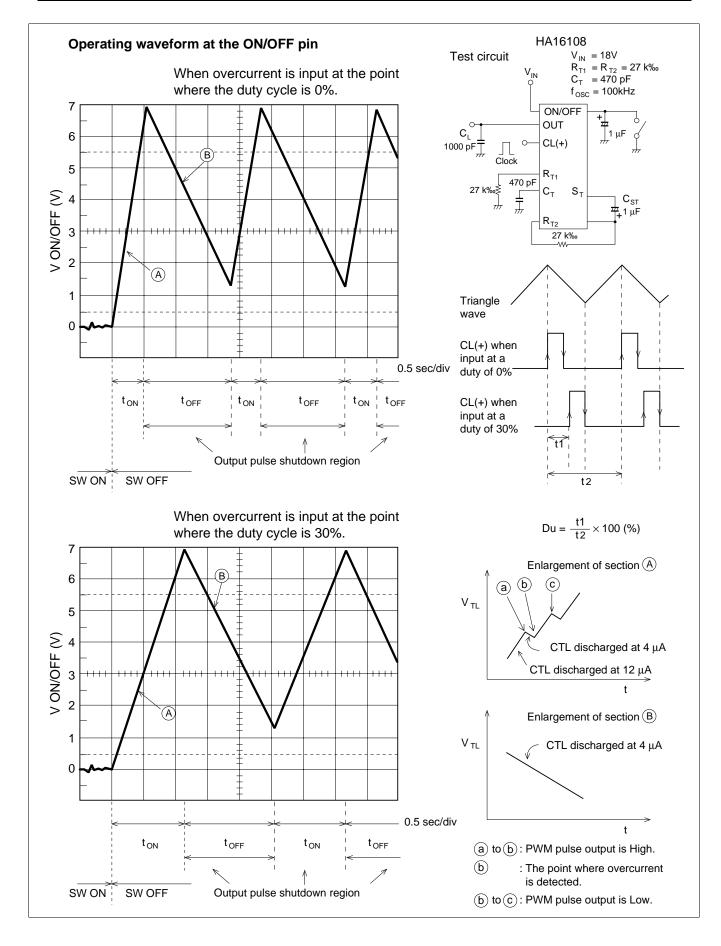

### **Timer Latch and ON/OFF Timer**

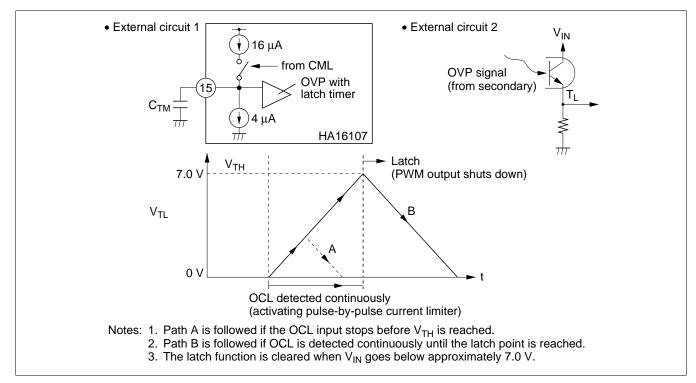

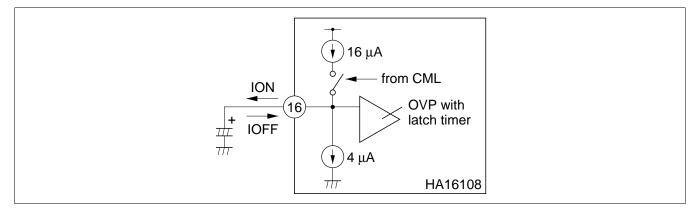

The HA16107 has a built-in timer-latch function. The HA16108 has a built-in ON/OFF timer function.

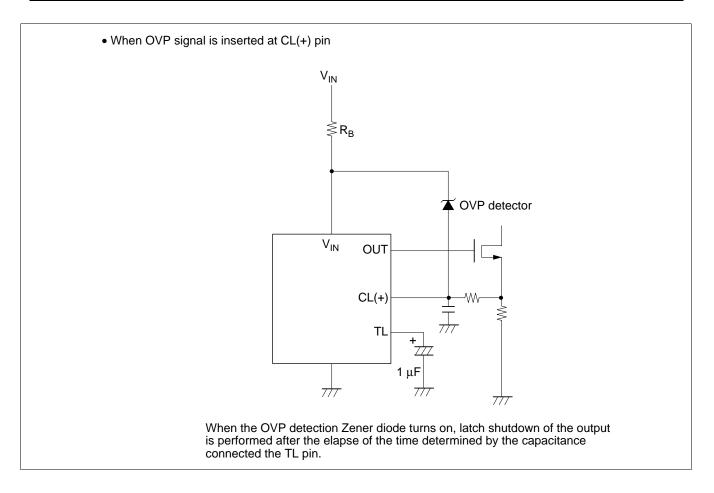

The timer-latch function is an overvoltage protection function that combines latched shutdown of PWM output with a timer function to vary the time until latched shutdown occurs according to the overcurrent value. A dedicated voltage detection pin is provided in addition to Vref overvoltage protection.

The ON/OFF timer function is equivalent to the above timer-latch function without the latch. If overcurrent is detected continuously, PWM output shuts down temporarily, then normal operation resumes. This process repeats, temporary shutdown alternating with normal operation.

Both the timer-latch function in the HA16107 and the ON/OFF function in the HA16108 wait for an interval after overcurrent detection before shutting down PWM output. The interval is determined by capacitor  $C_{TM}$  and the value of the charge/discharge current supplied internally from the IC. Normal operation therefore continues if a single overcurrent spike is detected, while if continuous overcurrent is detected, the current and voltage droop curves for the secondary-side output have sharp characteristics.

- 1. Use of Timer-Latch Pin (HA16107)

- Timer-Latch Usage

See external circuit 1 in the following diagram. Under continuous overcurrent, the CML switch turns on, charging  $C_{TM}$  with 12  $\mu$ A. PWM output shuts down when the voltage at pin 15 exceeds 7 V.

Overvoltage Protection Usage

See external circuit 2 in the diagram. This configuration is suitable when overvoltage is detected by an OVP signal received through an optocoupler from the DC output on the secondary side of an AC/DC converter. PWM output shuts down when the OVP signal allows the voltage at the TL pin to exceed 7 V. The shutdown is latched.  $V_{IN}$  must go below approximately 6.5 V ( $V_{INR2}$ ) to release the latched state.

- 2. Use of ON/OFF Timer Pin (HA16108)

- External Circuit

• ON/OFF Timer Operation

| Item                        | Symbol            | Rating Value | Units | Notes |

|-----------------------------|-------------------|--------------|-------|-------|

| Supply voltage              | V <sub>IN</sub>   | 30           | V     |       |

| Output current (DC)         | I <sub>o</sub>    | ±0.2         | А     |       |

| Output current (peak)       | lopeak            | ±2           | А     |       |

| Current limiter voltage     | V <sub>CL</sub>   | +4, -1       | V     |       |

| Error amp input voltage     | V <sub>IEA</sub>  | Vref         | V     |       |

| E/O output voltage          | V <sub>IE/O</sub> | Vref         | V     |       |

| $R_{T1}$ pin current        | I <sub>RT1</sub>  | 500          | μA    |       |

| R <sub>T2</sub> pin current | I <sub>RT2</sub>  | 5            | mA    |       |

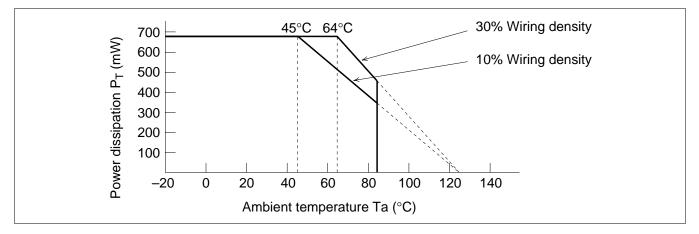

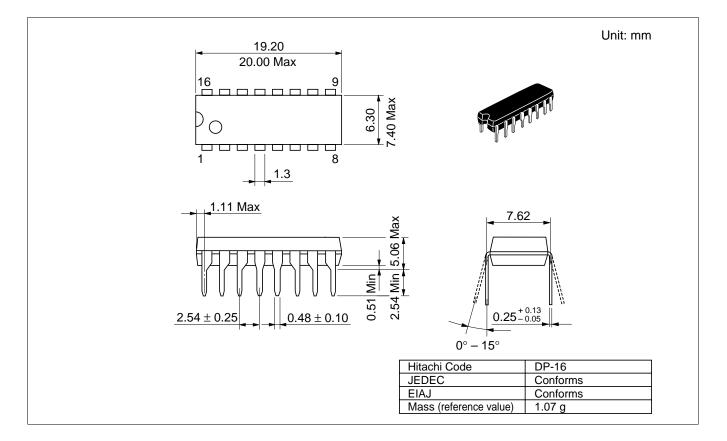

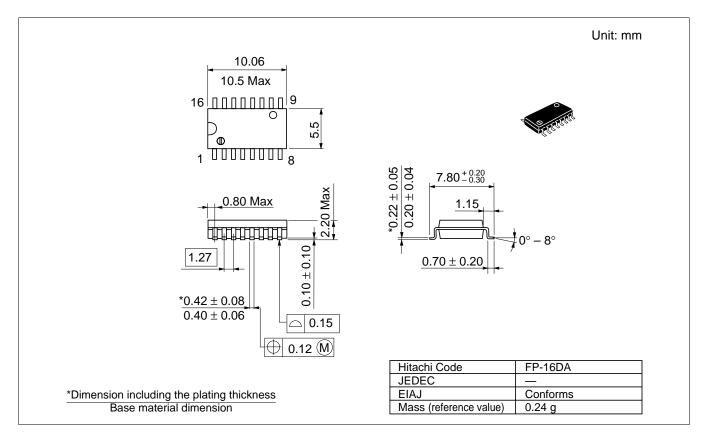

| Power dissipation           | P <sub>T</sub>    | 680          | mW    | 1, 2  |

| Operating temperature range | Topr              | -20 to +85   | °C    |       |

| Storage temperature range   | Tstg              | –55 to +125  | °C    |       |

### **Absolute Maximum Ratings** ( $Ta = 25^{\circ}C$ )

Notes: 1. For the "FP" products (SOP package), this value is when mounted on a 40 by 40 by 1.6 mm glass epoxy substrate. However, this value must be derated by 8.3 mW/°C from Ta = 45°C. When the wiring density is 10%, and 11.1 mW/°C from Ta = 64°C when the wiring density is 30%.

- 2. For the "P" products (DIP package), this value is valid up to 45°C, and must be derated by 8.3 mW/°C above 45°C.

- 3. In the case of SOP, use center 4 pins, (4), (5), (12), (13) for solder-mounting and connect the wide ground pattern, because these pins are available for heat sink of this IC.

# **Electrical Characteristics** (Ta = $25^{\circ}$ C, V<sub>IN</sub> = 18 V, f<sub>OSC</sub> = 100 kHz)

| Section           | Item                                               | Symbol                   | Min  | Тур  | Max  | Unit       | Test Conditions                                                                                        | Note |

|-------------------|----------------------------------------------------|--------------------------|------|------|------|------------|--------------------------------------------------------------------------------------------------------|------|

| Reference         | Output voltage                                     | Vref                     | 6.10 | 6.45 | 6.80 | V          |                                                                                                        |      |

| voltage           | Line regulation                                    | Line                     | _    | 30   | 60   | mV         | $12~V \leq V_{\rm IN} \leq 30~V$                                                                       |      |

|                   | Load regulation                                    | Load                     | _    | 30   | 60   | mV         | $0 \text{ mA} \le I_{o} \le 10 \text{ mA}$                                                             |      |

|                   | Temperature<br>stability                           | $\Delta Vref/ \Delta Ta$ | —    | 40   | —    | ppm/<br>°C |                                                                                                        |      |

|                   | Short circuit current                              | I <sub>os</sub>          | 30   | 50   | —    | mA         | Vref = 0 V                                                                                             |      |

|                   | Over voltage protec-<br>tion (Vref OVP<br>voltage) | Vrovp                    | 7.4  | 8.0  | 9.0  | V          |                                                                                                        |      |

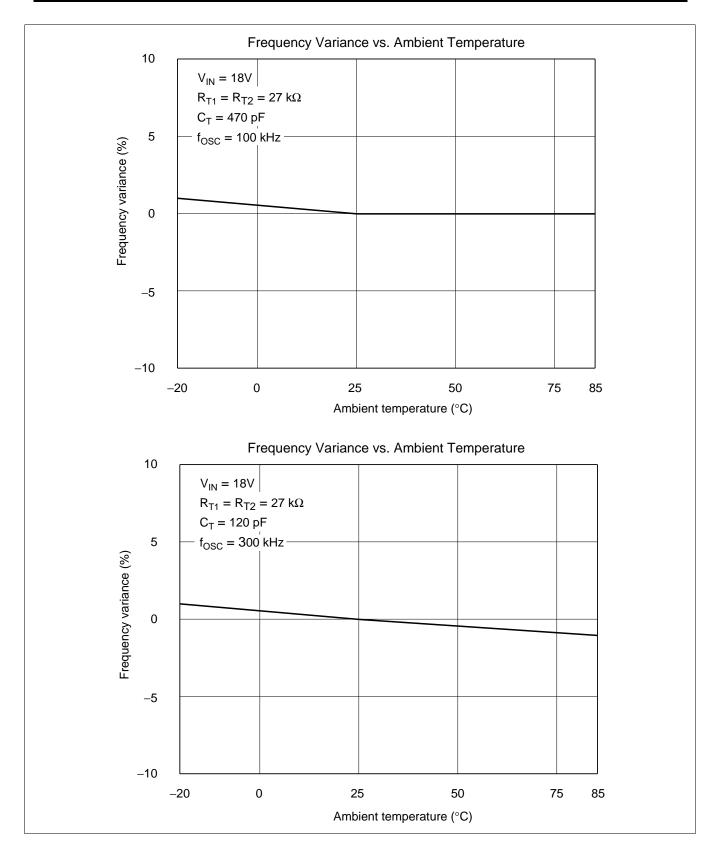

| Triangle          | Maximum frequency                                  | fmax                     | 600  | _    | —    | kHz        |                                                                                                        |      |

| wave              | Minimum frequency                                  | fmin                     | —    | —    | 1    | kHz        |                                                                                                        |      |

| generator         | Voltage stability                                  | $\Delta f/fo_1$          | —    | ±1   | ±3   | %          | $12 \text{ V} \le \text{V}_{\text{IN}} \le 30 \text{ V}$ $\text{fo}_1 = (\text{fmax} + \text{fmin})/2$ |      |

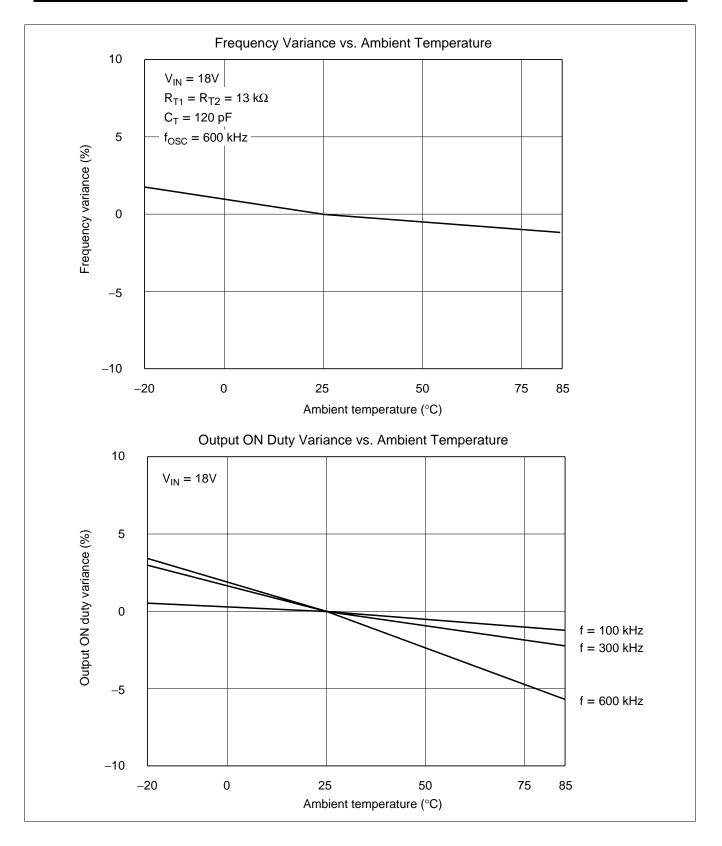

|                   | Temperature stability                              | $\Delta f/fo_2$          | —    | ±1   | —    | %          | $-20^{\circ}C \le Ta \le +85^{\circ}C$<br>fo <sub>2</sub> = (fmax + fmin)/2                            |      |

|                   | Frequency accuracy                                 | f <sub>osc</sub>         | 270  | 300  | 330  | kHz        | $R_{T1} = R_{T2} = 27 \text{ k}\Omega$<br>$C_T = 120 \text{ pF}$                                       |      |

| PWM<br>comparator | Minimum deadband pulse width                       | t <sub>DB</sub>          | —    | _    | 1.0  | μs         |                                                                                                        |      |

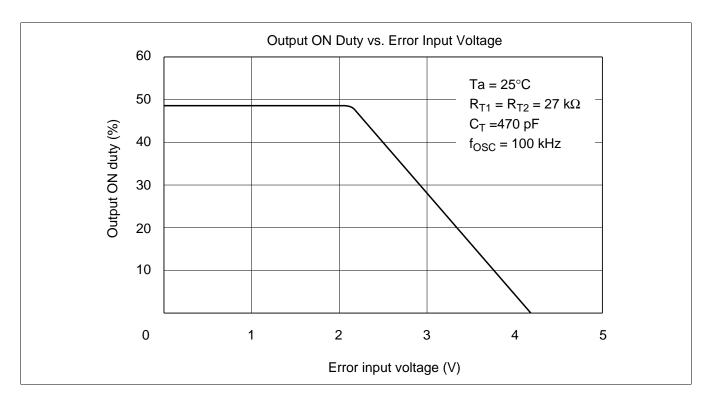

|                   | Low level threshold voltage                        | $V_{TL}$                 | 1.9  | 2.2  | 2.5  | V          |                                                                                                        |      |

|                   | High level threshold                               | V <sub>TH</sub>          | 3.8  | 4.2  | 4.6  | V          |                                                                                                        |      |

|                   | Differential threshold                             | $\Delta V_{\rm TH}$      | 1.7  | 2.0  | 2.3  | V          |                                                                                                        |      |

|                   | Deadband width initial accuracy                    | ∆DB1                     | _    | ±1   | ±3   | %          | $R_{T1} = R_{T2} = 27 \text{ k}\Omega$<br>$C_T = 470 \text{ pF}$                                       |      |

|                   | Deadband width voltage stability                   | $\Delta DB2$             | _    | ±0.2 | ±2.0 | %          | $12 \text{ V} \le \text{V}_{IN} \le 30 \text{ V}$<br>(Dmax - Dmin)/2                                   |      |

|                   | Deadband width temperature stability               | $\Delta DB3$             | _    | ±1   | _    | %          | $-20^{\circ}C \le Ta \le +85^{\circ}C$<br>(Dmax - Dmin)/2                                              |      |

| Error amp         | Input offset voltage                               | V <sub>IO</sub>          | —    | 2    | 10   | mV         |                                                                                                        |      |

|                   | Input bias current                                 | I <sub>IB</sub>          | _    | 0.8  | 2.0  | μA         |                                                                                                        |      |

|                   | Input sink current                                 | losink                   | 80   | 140  | _    | μΑ         | $V_0 = 2 V$                                                                                            |      |

|                   | Output source current                              | losource                 | 80   | 140  | _    | μΑ         | $V_o = 5 V$                                                                                            |      |

| Section              | Item                                              | Symbol              | Min           | Тур    | Max           | Unit | Test Conditions                       | Note |

|----------------------|---------------------------------------------------|---------------------|---------------|--------|---------------|------|---------------------------------------|------|

| Error amp<br>(cont.) | High level output voltage                         | V <sub>OH</sub>     | Vref –<br>1.5 | _      | _             | V    | I <sub>o</sub> = 10 μA                |      |

|                      | Low level output voltage                          | V <sub>ol</sub>     | _             | _      | 0.5           | V    | l <sub>o</sub> = 10 μA                |      |

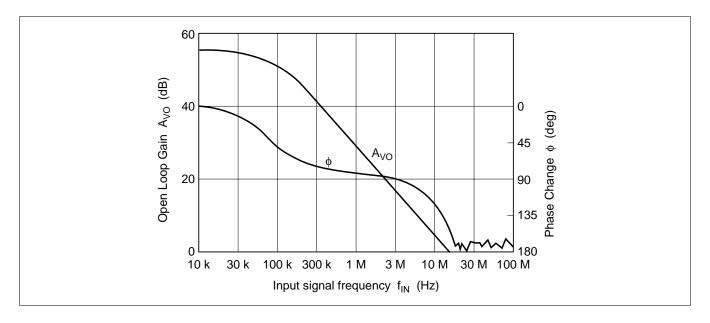

|                      | Voltage gain                                      | G <sub>v</sub>      | _             | 55     |               | dB   | f = 10 kHz                            |      |

|                      | Band width                                        | BW                  | —             | 15     | —             | MHz  |                                       |      |

|                      | (–) Common mode<br>voltage                        | V <sub>cm</sub> -   | 1.2           | _      | _             | V    |                                       |      |

|                      | (+) Common mode<br>voltage                        | V <sub>CM</sub> +   | —             | —      | Vref –<br>1.5 | V    |                                       |      |

| Over-                | (+) Threshold voltage                             | V <sub>TH</sub> +   | 0.216         | 0.240  | 0.264         | V    |                                       |      |

| current              | (+) Bias current                                  | I <sub>B</sub> +    | _             | 180    | 250           | μΑ   | $V_{cL}$ + = 0 V                      |      |

| detector             | (-) Threshold voltage                             | V <sub>TH</sub> -   | -0.264        | -0.240 | -0.216        | V    |                                       | 1, 2 |

|                      | (–) Bias current                                  | I <sub>в</sub> —    | _             | 950    | 1350          | μΑ   | $V_{cL} = -0.3 V$                     | 1, 2 |

|                      | Response time                                     | t <sub>off</sub>    | _             | 100    | _             | ns   | CL; open<br>V <sub>CL</sub> = +0.35 V |      |

| Soft start           | High level voltage                                | $V_{\rm STH}$       | 3.2           | 3.8    | 4.4           | V    | lsink = 1 mA                          |      |

|                      | Sink current                                      | lsink               | 7             | 10     | 13            | μA   | V <sub>ST</sub> = 2.0 V               |      |

| Under<br>voltage     | V <sub>IN</sub> high level thre-<br>shold voltage | $V_{\text{INTH}}$   | 14.7          | 16.2   | 17.7          | V    |                                       |      |

| lockout 1            | V <sub>IN</sub> low level thre-<br>shold voltage  | $V_{\text{INTL}}$   | 8.5           | 9.5    | 10.5          | V    |                                       |      |

|                      | Threshold differential voltage                    | $\Delta V_{\rm TH}$ | 5.2           | 6.2    | 7.2           | V    | $(V_{INTH} - V_{INTL})$               |      |

| Under<br>voltage     | Vref high level thre-<br>shold voltage            | $V_{\rm rTH}$       | 4.5           | 5.0    | 5.5           | V    |                                       |      |

| lockout 2            | Vref low level thre-<br>shold voltage             | $V_{\rm rTL}$       | 3.5           | 4.0    | 4.5           | V    |                                       |      |

# Electrical Characteristics (Ta = $25^{\circ}$ C, V<sub>IN</sub> = 18 V, f<sub>OSC</sub> = 100 kHz) (cont.)

Notes: 1. Only applies to the HA16107P, HA16108P

2. The terminal should not be applied under -1.0 V.

| Section                | Item                                      | Symbol            | Min                      | Тур | Max | Unit | <b>Test Conditions</b>                                         | Note |

|------------------------|-------------------------------------------|-------------------|--------------------------|-----|-----|------|----------------------------------------------------------------|------|

| Timer latch,<br>ON/OFF | Latch threshold voltage                   | $V_{\text{THH}}$  | 6.5                      | 7.0 | 7.5 | V    |                                                                |      |

| timer*2                | V <sub>IN</sub> reset voltage             | V <sub>INR2</sub> | 6.0                      | 6.5 | 7.0 | V    |                                                                |      |

|                        | Reset voltage                             | $V_{\text{THL2}}$ | 1.0                      | 1.3 | 1.6 | V    |                                                                | 1    |

|                        | Differential threshold to UVL low voltage | $\Delta V$        | 2.0                      | 3.0 | _   | V    | $(V_{intl} - V_{inr2})$                                        |      |

|                        | Source current<br>(OCL mode)              | Isource           | 8                        | 12  | 16  | μΑ   | Over current detection mode                                    |      |

|                        | Sink current<br>(latch mode)              | lsink             | 2.5                      | 4   | 5.5 | μΑ   | TL(ON/OFF)<br>terminal = 4 V                                   |      |

| Output                 | Low voltage                               | $V_{\text{OL1}}$  | _                        | 1.7 | 2.2 | V    | losink = 0.2 A                                                 |      |

|                        | High voltage                              | V <sub>OH</sub>   | V <sub>IN</sub> –<br>2.2 | —   | —   | V    | losource = 0.2 A                                               |      |

|                        | Low voltage<br>(standby mode)             | $V_{OL2}$         | _                        | _   | 0.5 | V    | losink = 1 mA                                                  |      |

|                        | Rising time                               | t,                | _                        | 40  | _   | ns   | C <sub>L</sub> = 1000 pF                                       |      |

|                        | Falling time                              | t <sub>f</sub>    | _                        | 60  | _   | ns   | C <sub>L</sub> = 1000 pF                                       |      |

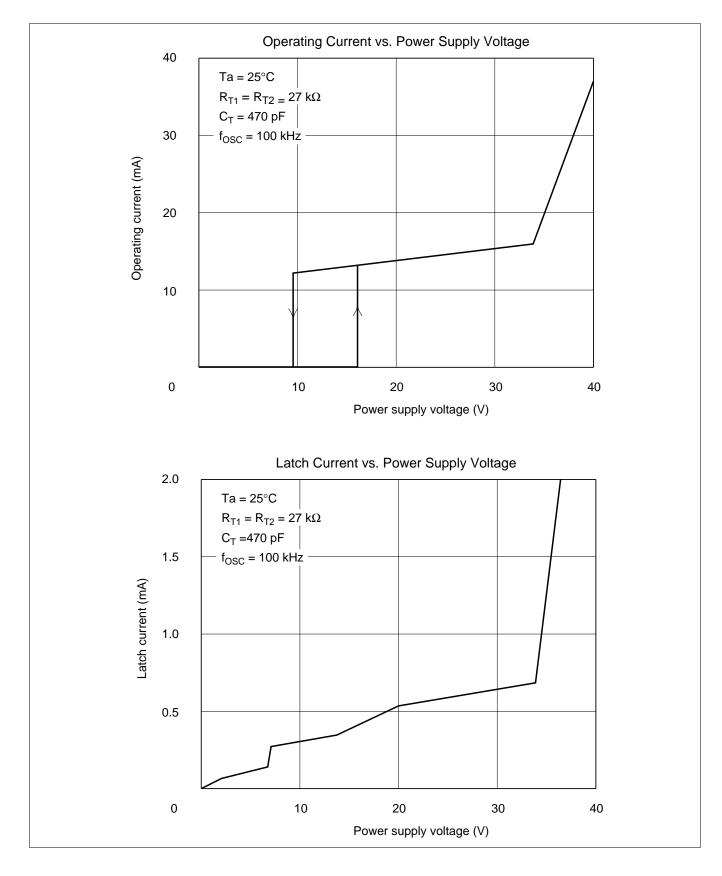

| Total                  | Standby current                           | lst               | —                        | 160 | 250 | μΑ   | V <sub>IN</sub> = 14 V                                         |      |

|                        | Operation current                         | I <sub>IN1</sub>  | _                        | 16  | 20  | mA   | $V_{IN} = 30 V,$<br>$C_{L} = 1000 \text{ pF},$<br>f = 100  kHz |      |

|                        | Operation current                         | I <sub>IN2</sub>  | _                        | 12  | 16  | mA   | $V_{IN} = 30 V,$<br>f = 100 kHz,<br>Output open                |      |

|                        | ON/OFF latch current                      | I <sub>IN3</sub>  | _                        | 350 | 460 | μA   | V <sub>IN</sub> = 14 V                                         |      |

|                        | $V_{IN}$ – GND Zener voltage              | Vz                | 30                       | 34  | —   | V    |                                                                |      |

# Electrical Characteristics (Ta = $25^{\circ}$ C, V<sub>IN</sub> = 18 V, f<sub>OSC</sub> = 100 kHz) (cont.)

Notes: 1. Only applies to the HA16108P/FP.

2. Timer latch: HA16107P/FP. ON/OFF timer: HA16108P/FP.

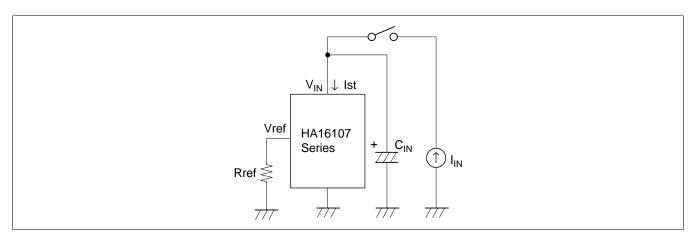

### Note on Standby Current

In the test circuit shown in figure 1, the operating current at the start of PWM pulse output is the standby current.

If the resistance connected externally to the Vref pin (including  $R_{T2}$ ) is smaller than that of the test circuit, the apparent standby current will increase.

Figure 1 Standby Current Test Circuit

### **Application Note**

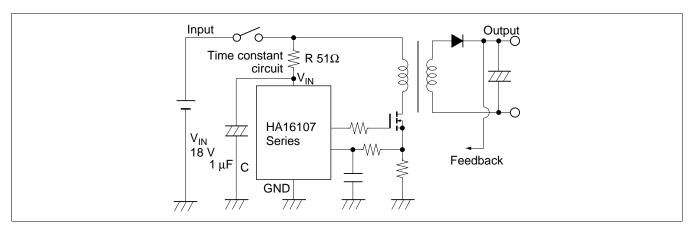

• Case:

When DC power is applied directly as the power supply of the HA16107/HA16108, without using the transformer backup coil.

• Phenomenon:

The IC may not be activated in the case of a circuit in which  $V_{IN}$  rises quickly (10 V/100 µs or faster), such as that shown in figure 2.

• Reason:

Because of the IC circuit configuration, the timer latch block operates first.

• Remedy (counter measure):

Take remedial action such as configuring a time constant circuit as shown in figure 3, to keep the  $V_{IN}$  rise speed below 10 V/100  $\mu$ s.

If the IC power supply consists of an activation resistance and backup coil, as in an AC/DC converter, The  $V_{IN}$  rise speed is usually around 1 V/100  $\mu$ s, and there is no risk of this phenomenon occurring.

Figure 2 Example of Circuit with Fast V<sub>IN</sub> Rise Time

Figure 3 Sample Remedial Circuit

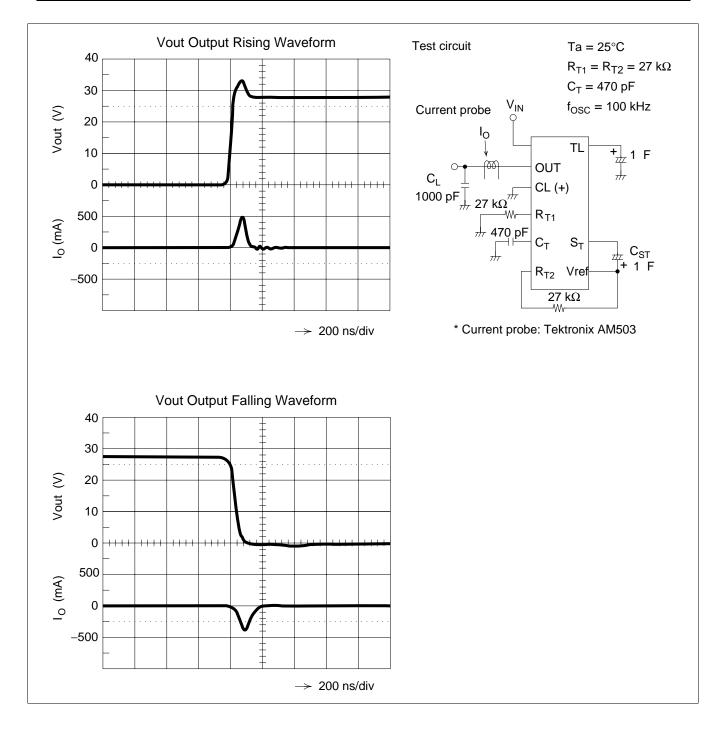

### **Characteristic Curves**

### **Error Amplifier Characteristic**

**Examples of Drooping Characteristics of Power Supplies Using these ICs**

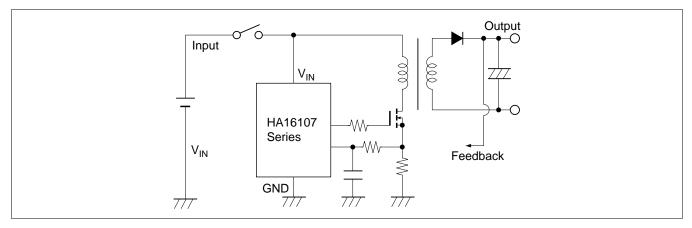

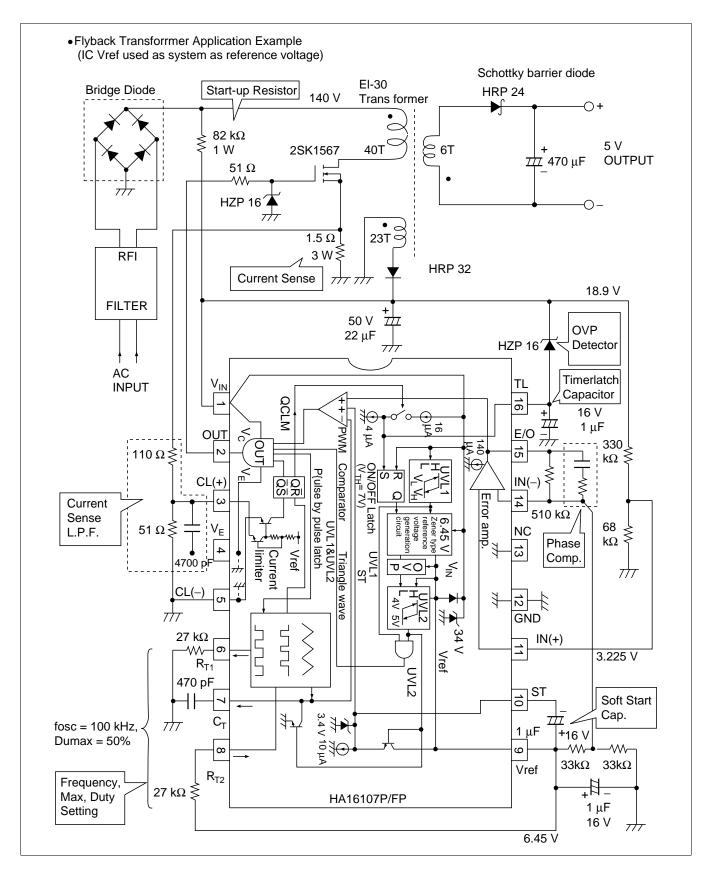

# **Operating Circuit Example**

### **Package Dimensions**

### Cautions

- 1. Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

# HITACHI

### Hitachi, Ltd.

Semiconductor & Integrated Circuits. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109 URL NorthAmerica : http:semiconductor.hitachi.com/

Europe Asia (Singapore) Asia (Taiwan) Asia (HongKong) Japan

http://www.hitachi-eu.com/hel/ecg http://www.has.hitachi.com.sg/grp3/sicd/index.htm http://www.hitachi.com.tw/E/Product/SICD\_Frame.htm http://www.hitachi.com.hk/eng/bo/grp3/index.htm http://www.hitachi.co.jp/Sicd/indx.htm

### For further information write to: Hitachi Semiconductor Hitachi Europe GmbH

Hitachi Semiconductor (America) Inc. 179 East Tasman Drive, San Jose, CA 95134 Tel: <1> (408) 433-1990 Fax: <1>(408) 433-0223

Electronic components Group Dornacher Straße 3 D-85622 Feldkirchen, Munich Germany Tel: <49> (89) 9 9180-0 Fax: <49> (89) 9 29 30 00 Hitachi Europe Ltd. Electronic Components Group. Whitebrook Park Lower Cookham Road Maidenhead Berkshire SL6 8YA, United Kingdom Tel: <44> (1628) 585000 Fax: <44> (1628) 778322 Hitachi Asia Pte. Ltd. 16 Collyer Quay #20-00 Hitachi Tower Singapore 049318 Tel: 535-2100 Fax: 535-1533

Hitachi Asia Ltd. Taipei Branch Office 3F, Hung Kuo Building. No.167, Tun-Hwa North Road, Taipei (105) Tel: <886> (2) 2718-3666 Fax: <886> (2) 2718-8180 Hitachi Asia (Hong Kong) Ltd. Group III (Electronic Components) 7/F., North Tower, World Finance Centre, Harbour City, Canton Road, Tsim Sha Tsui, Kowloon, Hong Kong Tel: <852> (2) 735 9218 Fax: <852> (2) 730 0281 Telex: 40815 HITEC HX

Copyright ' Hitachi, Ltd., 1998. All rights reserved. Printed in Japan.

### **Revision Record**

| Rev. | Date          | Contents of Modification | Drawn by   | Approved by |

|------|---------------|--------------------------|------------|-------------|

| 0.0  | Oct. 11, 1994 | Initial issue            | A. Koizumi | M. Yamamura |

| 0.1  | Oct. 11, 1994 | Initial issue            | A. Koizumi | M. Yamamura |

| 0.2  | Nov. 12, 1994 | Initial issue            | A. Koizumi | M. Yamamura |