## 4096-word x 1-bit High Speed CMOS Static RAM

#### **FEATURES**

- High Speed: Fast Access Time 35ns/45ns/55ns (max.)

- Low Power Standby and Low Power Operation, Standby: 100µW (typ.)/5µW (typ.) (L-version),

Operation: 150mW typ.

- Single 5V Supply and High Density 18 Pin Package

- Completely Static Memory No Clock nor Timing Strobe Required

- No Peak Power—On Current

- No Change of t<sub>ACS</sub> with Short Chip Deselect Time

- Equal Access and Cycle Time

- Directly TTL Compatible All Input and Output

- Separate Data Input and Output: Three State Output

- Plug-In Replacement with Intel 2147H NMOS STATIC RAM

- Capability of Battery Back Up Operation (L-version)

## **BORDERING INFORMATION**

| Type No.                                     | Access Time          | Package      |

|----------------------------------------------|----------------------|--------------|

| HM6147HP-35<br>HM6147HP-45<br>HM6147HP-55    | 35ns<br>45ns<br>55ns | 300mil 18pin |

| HM6147HLP-35<br>HM6147HLP-45<br>HM6147HLP-55 | 35ns<br>45ns<br>55ns | Plastic DÎP  |

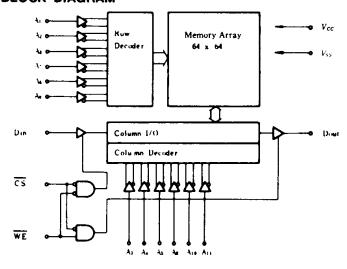

## **BBLOCK DIAGRAM**

#### **BABSOLUTE MAXIMUM RATINGS**

| Item                               | Symbol     | Rating              | Unit |

|------------------------------------|------------|---------------------|------|

| Voltage on Any Pin relative to Vss | V r        | $-0.5^{*1}$ to +7.0 | V    |

| DC Output Current                  | 1.         | 20                  | m A  |

| Power Dissipation                  | $P_{\tau}$ | 1.0                 | W    |

| Operating Temperature              | T.,.       | 0 to +70            | .c   |

| Storage Temperature under bias     | Talgitas;  | -10 to +85          | ·c   |

| Storage Temperature                | Tere       | 55 to +125          | •c   |

Note) #1 =3.5V for pulse width ≤20ns

#### **PIN ARRANGEMENT**

# **TRECOMMENDED DC OPERATING CONDITIONS** $(0^{\circ}C \le Ta \le 70^{\circ}C)$

| Parameter                    | Symbol           | min         | typ | max | Unit |

|------------------------------|------------------|-------------|-----|-----|------|

| Supply Voltage               | Vcc              | 4.5         | 5.0 | 5.5 | V    |

|                              | $V_{\rm SS}$     | 0           | 0   | 0   | V    |

| Input High (logic 1) Voltage | V <sub>I H</sub> | 2.0         | 3.0 | 6.0 | V    |

| Input Low (logic 0) Voltage  | V <sub>1</sub> L | $-0.5^{*1}$ | _   | 0.8 | V    |

Note) +1. -3.0V for pulse width≤20ns

# **EDC** AND OPERATING CHARACTERISTICS (0°C $\leq Ta \leq 70$ °C, $V_{cc} = 5V \pm 10\%$ , $V_{SS} = 0V$ )

| Parameter                            | Symbol    | Test Condition                                                                          | min | typ*2 | max   | Unit |

|--------------------------------------|-----------|-----------------------------------------------------------------------------------------|-----|-------|-------|------|

| Input Leakage Current                | ILI       | Vcc-5.5V, Vss to Vcc                                                                    |     |       | 10    | μΑ   |

| Output Leakage Current               | ILO       | $\overline{CS} - V_{IH}$ , $V_{out} - V_{SS}$ to $V_{CC}$                               | _   | _     | 10    | μĀ   |

| Operating Power Supply Current(1)    | Icc       | CS-Vil., Output open                                                                    | _   | 30    | 80    | mA   |

| Operating Power Supply Current(2)    | Icci      | CS-V14. Minimum Cycle                                                                   | _   | 40    | 80    | mA   |

| Standby Power Supply Current (1)     |           | $\overline{\mathrm{CS}} = V_{IH}, \ V_{CC} = \mathrm{Min} \ \mathrm{to} \ \mathrm{Max}$ | _   | 8     | 20    | mA   |

|                                      | $I_{SB}$  |                                                                                         | _   | 5*3   | 15*3  |      |

|                                      | _         | $\overline{\text{CS}} \ge Vcc - 0.2\text{V},$                                           |     | 20    | 800   |      |

| Standby Power Supply Current (2)  Is | $I_{SB1}$ | $V_{IN} \ge 0.2 \text{V}$ or $V_{IN} \ge V_{CC} - 0.2 \text{V}$                         | _   | 1*3   | 100*3 | μA   |

| Output Low Voltage                   | VoL       | Io1 - 8mA                                                                               |     | _     | 0.40  | V    |

| Output High Voltage                  | Von       | I <sub>OH</sub> — — 4 m A                                                               | 2.4 | -     | _     | V    |

Notes) \* 1. The operating ambient temperature range is guaranteed with transverse air flow exceeding 400 linear feet minute. \* 2. Typical limits are at Vcc = 5.0V. Ta = 25°C and Specified loading.

\*3. This characteristics are guaranteed only for L-version.

## **ECAPACITANCE** ( $Ta-25^{\circ}C$ , f-1.0 MHz)

| ltem               | Symbol | Conditions          | max | Unit |

|--------------------|--------|---------------------|-----|------|

| Input Capacitance  | c.,    | V.,-0V              | 5   | pF   |

| Output Capacitance | Cmr    | V <sub>m1</sub> -0V | 6   | рF   |

Note) This parameter is sampled and not 100% tested.

**a** AC CHARACTERISTICS (Ta = 0 to  $+70^{\circ}$ C,  $V_{CC} = 5$ V ± 10%)

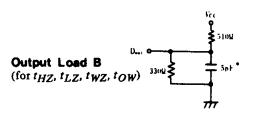

## • AC TEST CONDITIONS

Input pulse levels: V<sub>SS</sub> to 3.0V Input rise and fall times: 5 ns Input timing reference levels: 1.5V

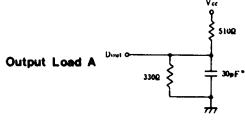

Output load: See Figure

Output timing reference levels: 1.5V (HM6147H-35) 0.8 to 2.0V (HM6147H-45/55)

\* Including scope & jig capacitance

#### • READ CYCLE

| Parameter                            |                 | HM6147H-35 |     | HM6147H-45 |     | HM6147H-55 |     | ] <u>.,</u> |               |

|--------------------------------------|-----------------|------------|-----|------------|-----|------------|-----|-------------|---------------|

|                                      | Symbol          | min        | max | min        | max | min        | max | Unit        | Notes         |

| Read Cycle Time                      | tac             | 35         | _   | 45         | _   | 55         |     | กร          | (1)           |

| Address Access Time                  | t <sub>AA</sub> | -          | 35  |            | 45  | _          | 55  | n <b>s</b>  |               |

| Chip Select Access Time              | tacs            | _          | 35  | _          | 45  |            | 55  | ns          |               |

| Output Hold from Address Change      | t on            | 5          |     | 5          | _   | 5          | ] - | ns.         |               |

| Chip Selection to Output in Low Z    | tız             | 5          | -   | 5          |     | 5          | I   | n\$         | (2), (3), (7) |

| Chip Deselection to Output in High Z | ŧ HZ            | 0          | 30  | 0          | 30  | 0          | 30  | n\$         | (2), (3), (7) |

| Chip Selection to Power Up Time      | t pu            | 0          | -   | 0          | _   | 0          |     | ns          |               |

| Chip Deselection to Power Down Time  | t PD            | _          | 20  |            | 20  | ] –        | 20  | ns          |               |

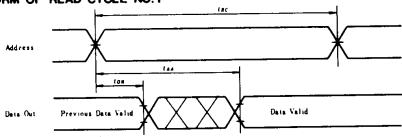

# TIMING WAVEFORM OF READ CYCLE NO.1(4)(5)

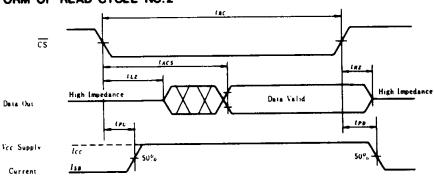

# TIMING WAVEFORM OF READ CYCLE NO.2 (4) (4)

- Notes: 1. All Read Cycle timings are referenced from last valid address to the first transitioning address.

- 2. At any given temperature and voltage condition, IHZ max. is less than  $t_{LZ}$  min. both for a given device and from device to device.

- 3. Transition is measured ±500mV from steady state voltage with specified loading in Load B.

4. WE is high for READ Cycle.

- 5. Device is continuously selected,  $\overline{CS} = V_{IL}$ .

- 6. Addresses valid prior to or coincident with CS transition low.

- 7. This parameter is sampled and not 100% tested.

## • WRITE CYCLE

|                                   |        | HM61 | 47H-35 | HM61 | 47H-45 | HM61 | 47H-55 | 1,,_:, | Notes    |

|-----------------------------------|--------|------|--------|------|--------|------|--------|--------|----------|

| Parameter                         | Symbol | min  | max    | min  | max    | min  | max    | Unit   | Notes    |

| Write Cycle Time                  | lwc    | 35   | _      | 45   | _      | 55   | _      | ns     | (2)      |

| Chip Selection to End of Write    | tew    | 35   | _      | 45   | _      | 45   | I -    | ns     |          |

| Address Valid to End of Write     | taw    | 35   | _      | 45   | _      | 45   |        | ns     |          |

| Address Setup Time                | tas    | 0    | _      | 0    |        | 0    |        | ns     |          |

| Write Pulse Width                 | lwp    | 20   | T -    | 25   |        | 30   |        | ns     |          |

| Write Recovery Time               | twa    | 0    | _      | 0    | _      | 0    |        | ns     |          |

| Data Valid to End of Write        | t pw   | 20   | -      | 25   | _      | 25   | _      | ns     |          |

| Data Hold Time                    | t DH   | 10   | _      | 10   | _      | 10   | _      | ns     |          |

| Write Enabled to Output in High Z | twz    | 0    | 20     | 0    | 25     | 0    | 30     | ns     | (3), (4) |

| Output Active from End of Write   | tow    | 0    | -      | 0    | _      | 0    | -      | ns     | (3), (4) |

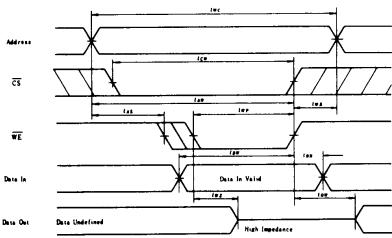

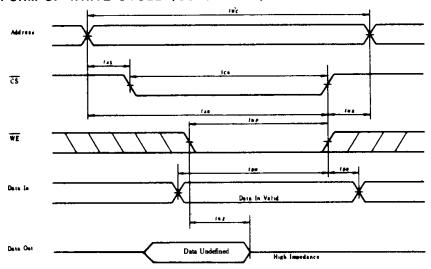

# TIMING WAVEFORM OF WRITE CYCLE (WE Controlled)

## TIMING WAVEFORM OF WRITE CYCLE (CS Controlled)

- Notes: 1. If CS goes high simultaneously with WE high, the output remains in a high impedance states.

- 2. All Write Cycle timings are referenced from the last valid address to the first transitioning address.

- 3. Transition is measured ±500mV from steady state voltage with specified loading in Load B.

- 4. This parameter is sampled and not 100% tested.

- 5. CS or WE is high for address transition.

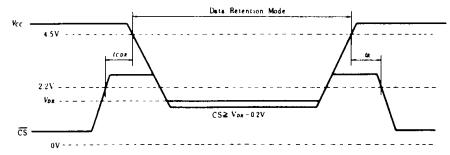

# **■LOW Vcc DATA RETENTION CHARACTERISTICS** (Ta-0℃ to +70℃)

This characteristics are guaranteed only for L-version.

| ltem .                               | Symbol         | Test Condition                                                                                                                    | min   | typ | max | Unit |

|--------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------|-------|-----|-----|------|

| Vcc for Data Retention               | Von            | $\overline{CS} \ge V_{CC} - 0.2V$ $V_{IN} \ge V_{CC} - 0.2V \text{ or } V_{IN} \le 0.2V$                                          | 2.0   | -   | _   | ν    |

| Data Retention Current               | Iccor          | $V_{cc} = 3.0 \text{V}, \ \overline{\text{CS}} \ge 2.8 \text{V}$<br>$V_{iN} \ge 2.8 \text{V} \text{ or } V_{iN} \le 0.2 \text{V}$ | _     | -   | 50  | μΑ   |

| Chip Deselect to Data Retention Time | lcon           | C D W (                                                                                                                           | 0     | -   |     | ns   |

| Operation Recovery Time              | l <sub>R</sub> | See Retention Waveform                                                                                                            | tac*1 | _   | _   | ns   |

Note) \*1.  $t_{RC}$  = Red Cycle Time.

## **●LOW V** CC DATA RETENTION WAVEFORM

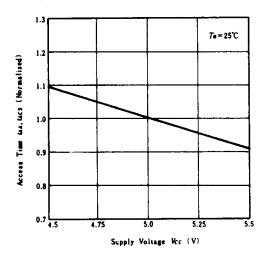

## ACCESS TIME VS. SUPPLY VOLTAGE

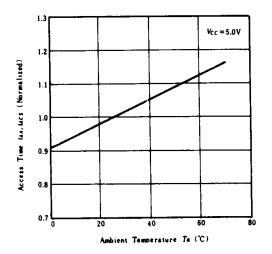

#### ACCESS TIME VS. AMBIENT TEMPERATURE

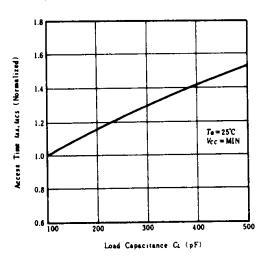

## ACCESS TIME VS. LOAD CAPACITANCE

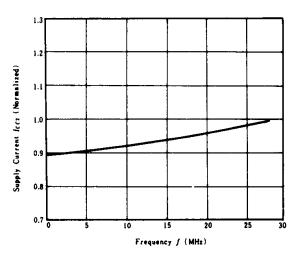

#### SUPPLY CURRENT VS. FREQUENCY

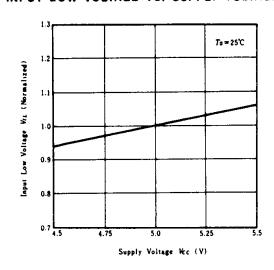

#### INPUT LOW VOLTAGE VS. SUPPLY VOLTAGE

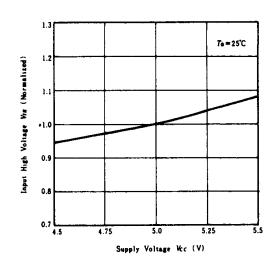

## INPUT HIGH VOLTAGE VS. SUPPLY VOLTAGE

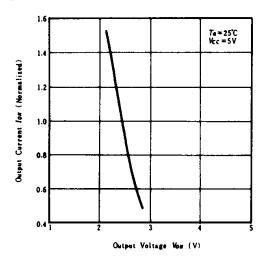

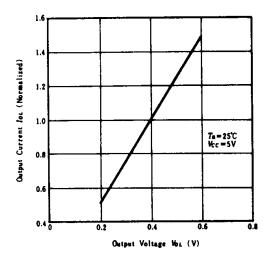

## OUTPUT CURRENT VS. OUTPUT VOLTAGE

## OUTPUT CURRENT VS. OUTPUT VOLTAGE

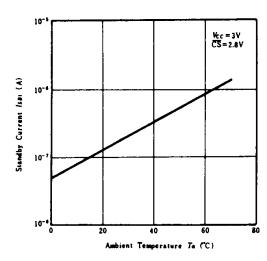

## STANDBY CURRENT VS. AMBIENT TEMPERATURE

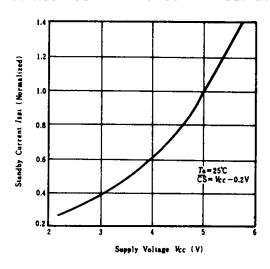

## STANDBY CURRENT VS. SUPPLY VOLTAGE

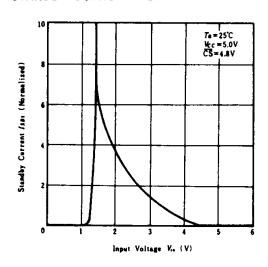

#### STANDBY CURRENT VS. INPUT VOLTAGE