# HM53461 Series

# 65,536-word x 4-bit Multiport CMOS Video RAM

#### **■ DESCRIPTION**

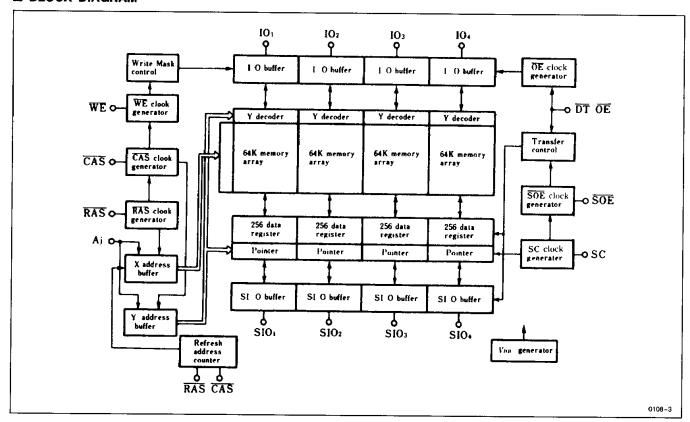

The HM53461 is a 262,144-bit multiport memory equipped with a 64k-word x 4-bit Dynamic RAM port and a 256-word x 4-bit Serial Access Memory (SAM) port. The SAM port is connected to an internal 1,024-bit data register through a 256-word x 4-bit serial read or write access control. In the read transfer cycle, the memory cell data is transferred from a selected word line of the RAM port to the data register. The RAM port has a write mask capability in addition to the conventional operation mode. Write bit selection out of 4 data bit can be achieved.

Utilizing the Hitachi 2  $\mu m$  CMOS process, fast serial access operation and low power dissipation are realized. All inputs and outputs, including clocks, are TTL compatible.

#### **■ FEATURES**

- Multiport Organization (RAM; 64k-word x 4-bit and SAM; 256 word x 4-bit) • Double Layer Polysilicon/Polyicide n-Well CMOS Process Single 5V (±10%) Low Power Active RAM .......380 mW (max) SAM ......220 mW (max) Standby ......40 mW (max) Access Time SAM ......40 ns/40 ns/60 ns

- Cycle Time Random Read or Write Cycle Time (RAM) .....190 ns/220 ns/260 ns Serial Read or Write Cycle Time (SAM) ......40 ns/40 ns/60 ns TTL Compatible

- · Refresh Function

RAS Only Refresh CAS Before RAS Refresh

Hidden Refresh

- Data Transfer Operation (RAM ←→ SAM)

- Fast Serial Access Operation Asynchronized with RAM Port Except Data Transfer Cycle

- Real Time Read Transfer Capability

- Write Mask Mode Capability

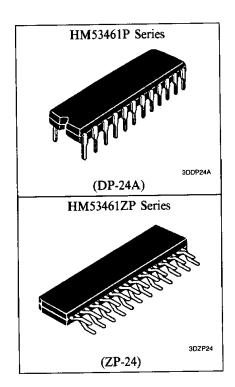

#### **■ ORDERING INFORMATION**

| Part No.     | Access Time | Package        |

|--------------|-------------|----------------|

| HM53461P-10  | 100 ns      | 400 mil 24-pin |

| HM53461P-12  | 120 ns      | Plastic DIP    |

| HM53461P-15  | 150 ns      | (DP-24A)       |

| HM53461ZP-10 | 100 ns      | 24-pin         |

| HM53461ZP-12 | 120 ns      | Plastic ZIP    |

| HM53461ZP-15 | 150 ns      | (ZP-24)        |

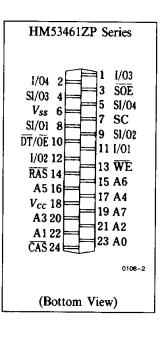

#### **■ PIN OUT**

## **■ PIN DESCRIPTION**

| Pin Name                             | Function                    |

|--------------------------------------|-----------------------------|

| A <sub>0</sub> -A <sub>7</sub>       | Address Inputs              |

| I/O <sub>1</sub> -I/O <sub>4</sub>   | RAM Port Data Input/Output  |

| SI/O <sub>1</sub> -SI/O <sub>4</sub> | SAM Port Data Input/Output  |

| RAS                                  | Row Address Strobe          |

| CAS                                  | Column Address Strobe       |

| SC                                   | Serial Clock                |

| WE                                   | Write Enable                |

| DT/OE                                | Data Transfer/Output Enable |

| SOE                                  | SAM Port Enable             |

| $v_{cc}$                             | Power Supply                |

| V <sub>SS</sub>                      | Ground                      |

## **BLOCK DIAGRAM**

## ■ ABSOLUTE MAXIMUM RATINGS

| Parameter                                        | Symbol           | Value          | Unit |  |

|--------------------------------------------------|------------------|----------------|------|--|

| Voltage on Any Pin Relative to VSS               | $v_{T}$          | -1.0  to  +7.0 | v    |  |

| Power Supply Voltage Relative to V <sub>SS</sub> | v <sub>cc</sub>  | -0.5 to $+7.0$ | v    |  |

| Operating Temperature, T <sub>A</sub> (Ambient)  | Topr             | 0 to + 70      | °C   |  |

| Storage Temperature                              | T <sub>stg</sub> | - 55 to + 125  | °C   |  |

| Short Circuit Output Current                     | I <sub>out</sub> | 50             | mA   |  |

| Power Dissipation                                | P <sub>T</sub>   | 1.0            | w    |  |

## ■ ELECTRICAL CHARACTERISTICS

# ullet Recommended DC Operating Conditions (T<sub>A</sub> = 0 to $\pm 70^{\circ}$ C)

| Parameter          | Symbol          | Min   | Тур | Max | Unit | Note |

|--------------------|-----------------|-------|-----|-----|------|------|

| Supply Voltage     | v <sub>CC</sub> | 4.5   | 5.0 | 5.5 | V    |      |

| Input High Voltage | V <sub>IH</sub> | 2.4   | _   | 6.5 | v    |      |

| Input Low Voltage  | V <sub>IL</sub> | - 0.5 | _   | 0.8 | V    | 2    |

Notes: 1. All voltages referenced to  $V_{SS}$ .

2. -3.0V for pulse width  $\leq 10$  ns.

# • DC Electrical Characteristics ( $T_A = 0$ to $+70^{\circ}$ C, $V_{CC} = 5V \pm 10\%$ , $V_{SS} = 0V$ )

|                          |                   | SAM I   | PORT |     |                              | HM53461-15 | 17-34                                                                                    | RAM PORT                                 | Note |

|--------------------------|-------------------|---------|------|-----|------------------------------|------------|------------------------------------------------------------------------------------------|------------------------------------------|------|

| Parameter                | Symbol            | Standby |      |     | HM53461-10   HM53461-12   H1 |            | Unit                                                                                     | Test Conditions                          | Note |

| Operating Current        | I <sub>CC1</sub>  | _       | ×    | 70  | 60                           | 50         | mA                                                                                       | RAS, CAS Cycling                         |      |

|                          | I <sub>CC7</sub>  | ×       |      | 110 | 100                          | 80         | mA                                                                                       | t <sub>RC</sub> = Min                    |      |

|                          | I <sub>CC2</sub>  | _       | ×    | 7   | 7                            | 7          | $\overline{\text{MA}}$ $\overline{\text{RAS}}$ , $\overline{\text{CAS}} = V_{\text{IH}}$ |                                          |      |

| Standby Current          | I <sub>CC8</sub>  | ×       |      | 40  | 40                           | 30         | mA                                                                                       | KAS, CAS — VIH                           |      |

| RAS Only Refresh Current | I <sub>CC3</sub>  |         | ×    | 60  | 50                           | 40         | mA                                                                                       | $\overline{\text{CAS}} = V_{\text{IH}},$ |      |

|                          | I <sub>CC9</sub>  | ×       | -    | 100 | 90                           | 70         | mA                                                                                       | RAS Cycling t <sub>RC</sub> = Min        |      |

|                          | I <sub>CC4</sub>  | _       | ×    | 50  | 40                           | 35         | mA                                                                                       | $\overline{RAS} = V_{IL},$               |      |

| Page Mode Current        | I <sub>CC10</sub> | ×       | _    | 90  | 80                           | 65         | mA                                                                                       | CAS Cycling t <sub>PC</sub> = Min        |      |

|                          | I <sub>CC5</sub>  | _       | ×    | 60  | 50                           | 40         | mA                                                                                       | RAS Cycling                              |      |

| CBR Refresh Current      | I <sub>CC11</sub> | ×       | _    | 100 | 90                           | 70         | mA                                                                                       | $t_{RC} = Min$                           | ļ    |

| Data Transfer Current    | I <sub>CC6</sub>  | _       | ×    | 75  | 65                           | 55         | mA                                                                                       | RAS, CAS Cycling                         |      |

|                          | I <sub>CC12</sub> | ×       |      | 115 | 105                          | 85         | mA                                                                                       | $t_{RC} = Min$                           |      |

| Parameter           | Symbol          | Min             | Max | Unit | Test Conditions           | Note |

|---------------------|-----------------|-----------------|-----|------|---------------------------|------|

| Input Leakage       | I <sub>LI</sub> | <del>-</del> 10 | 10  | μA   |                           |      |

| Output Leakage      | I <sub>LO</sub> | <del>-</del> 10 | 10  | μА   |                           |      |

| Output High Voltage | v <sub>oh</sub> | 2.4             |     | v    | $I_{OH} = -2 \text{ mA}$  |      |

| Output Low Voltage  | $v_{OL}$        |                 | 0.4 | V    | $I_{OL} = 4.2 \text{ mA}$ |      |

# ■ INPUT/OUTPUT CAPACITANCE

| Parameter | Symbol           | Тур          | Max | Unit | Note |

|-----------|------------------|--------------|-----|------|------|

| Address   | CII              | _            | 5   | pF   |      |

| Clocks    | C <sub>12</sub>  | <del>-</del> | 5   | pF   |      |

| I/O, SI/O | C <sub>I/O</sub> |              | 7   | pF   |      |

## ■ ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS

$(T_A = 0 \text{ to } +70^{\circ}\text{C}, V_{CC} = 5\text{V} \pm 10\%, V_{SS} = 0\text{V})^{1, 10, 11}$

| Parameter                                      | Symbol            |          | 461-10      | HM53461-12 |              | HM53461-15 |                                                  | Unit | Note        |

|------------------------------------------------|-------------------|----------|-------------|------------|--------------|------------|--------------------------------------------------|------|-------------|

| T drameter                                     | by incor          | Min      | Max         | Min        | Max          | Min        | Max                                              | Cint | 11010       |

| Random Read or Write Cycle Time                | t <sub>RC</sub>   | 190      | _           | 220        | _            | 260        | _                                                | ns   |             |

| Read-Modify-Write Cycle Time                   | t <sub>RWC</sub>  | 260      | _           | 300        |              | 355        | -                                                | ns   |             |

| Page Mode Cycle Time                           | t <sub>PC</sub>   | 70       | _           | 85         |              | 105        | _                                                | ns   |             |

| Access Time from RAS                           | t <sub>RAC</sub>  | _        | 100         | _          | 120          |            | 150                                              | ns   | 2, 3        |

| Access Time from CAS                           | t <sub>CAC</sub>  | _        | 50          | _          | 60           |            | 75                                               | ns   | 3, 4        |

| Output Buffer Turn-off Delay Referenced to CAS | t <sub>OFF1</sub> | 0        | 25          | 0          | 30           | 0          | 40                                               | ns   | 5           |

| Transition Time (Rise and Fall)                | t <sub>T</sub>    | 3        | 50          | 3          | 50           | 3          | 50                                               | ns   | 6           |

| RAS Precharge Time                             | t <sub>RP</sub>   | 80       |             | 90         | _            | 100        |                                                  | ns   |             |

| RAS Pulse Width                                | tRAS              | 100      | 10000       | 120        | 10000        | 150        | 10000                                            | ns   |             |

| CAS Pulse Width                                | t <sub>CAS</sub>  | 50       | 10000       | 60         | 10000        | 75         | 10000                                            | ns   | <del></del> |

| RAS to CAS Delay Time                          | t <sub>RCD</sub>  | 25       | 50          | 25         | 60           | 30         | 75                                               | ns   | 7           |

| RAS Hold Time                                  | tRSH              | 50       | _           | 60         | _            | 75         | l _                                              | ns   |             |

| CAS Hold Time                                  | tCSH              | 100      | _           | 120        |              | 150        | <u> </u>                                         | ns   |             |

| CAS to RAS Precharge Time                      | tCRP              | 10       | _           | 10         | _            | 10         | <u> </u>                                         | ns   | <u> </u>    |

| Row Address Setup Time                         | tASR              | 0        |             | 0          | _            | 0          |                                                  | ns   |             |

| Row Address Hold Time                          |                   | 15       | _           | 15         |              | 20         | _                                                | ns   |             |

| Column Address Setup Time                      | tage.             | 0        |             | 0          |              | 0          |                                                  | ns   |             |

| Column Address Hold Time                       | tasc              | 20       | _           | 20         |              | 25         |                                                  | ns   | <del></del> |

| Write Command Setup Time                       | t-can             | 0        |             | 0          |              | 0          | <del>                                     </del> | ns   | 8           |

| Write Command Hold Time                        | twcs              | 25       |             | 25         |              | 30         |                                                  |      | ⊢ °         |

| Write Command Pulse Width                      | twch              | 15       | _           | 20         |              | 25         |                                                  | ns   |             |

| Write Command to RAS Lead Time                 | twp               | 35       | _           |            | _            |            | <u> </u>                                         | ns   |             |

|                                                | tRWL              |          | _           | 40         |              | 45         | _                                                | ns   | -           |

| Write Command to CAS Lead Time                 | t <sub>CWL</sub>  | 35       |             | 40         |              | 45         | -                                                | ns   |             |

| Data-in Setup Time                             | t <sub>DS</sub>   | 0        | _           | 0          |              | 0          | <del>-</del>                                     | ns   | 9           |

| Data-in Hold Time                              | t <sub>DH</sub>   | 25       | _           | 25         |              | 30         | <u> </u>                                         | ns   | 8, 9        |

| Read Command Setup Time                        | tRCS              | 0        |             | 0          |              | 0          | _                                                | ns   | ļ <u>.</u>  |

| Read Command Hold Time                         | t <sub>RCH</sub>  | 0        | <del></del> | 0          |              | 0          | ļ. <del>-</del>                                  | ns   |             |

| Read Command Hold Time Referenced to RAS       | trrh              | 10       |             | 10         | <del>-</del> | 10         | _                                                | ns   |             |

| Refresh Period                                 | tREF              | <u> </u> | 4           |            | 4            | _          | 4                                                | ms   |             |

| RAS Pulse Width (Read-Modify-Write Cycle)      | t <sub>RWS</sub>  | 170      | 10000       | 200        | 10000        | 245        | 10000                                            | ns   |             |

| CAS to WE Delay                                | tCWD              | 85       |             | 100        |              | 125        | <del>  -</del>                                   | ns   | 8           |

| CAS Setup Time (CAS Before RAS Refresh)        | tCSR              | 10       | _           | 10         |              | 10         | _                                                | ns   |             |

| CAS Hold Time (CAS Before RAS Refresh)         | <sup>t</sup> CHR  | 20       | _           | 25         |              | 30         |                                                  | ns   |             |

| RAS Precharge to CAS Hold Time                 | tRPC              | 10       | _           | 10         |              | 10         |                                                  | ns   |             |

| CAS Precharge Time                             | t <sub>CP</sub>   | 10       |             | 15         | _            | 20         |                                                  | ns   |             |

| Access Time from OE                            | toac              |          | 30          |            | 35           | -          | 40                                               | ns   |             |

| Output Buffer Turn-off Delay referenced to OE  | t <sub>OFF2</sub> | 0        | 25          | 0          | 30           | 0          | 40                                               | ns   |             |

| OE to Data-in Delay Time                       | t <sub>ODD</sub>  | 25       | _           | 30         |              | 40         |                                                  | ns   | <u> </u>    |

| OE Hold Time referenced to WE                  | t <sub>OEH</sub>  | 10       |             | 15         |              | 20         |                                                  | ns   |             |

| Data-in to CAS Delay Time                      | t <sub>DZC</sub>  | 0        | _           | 0          | _            | 0          | _                                                | ns   |             |

| Data-in to OE Delay Time                       | t <sub>DZO</sub>  | 0        |             | 0          |              | 0          |                                                  | ns   |             |

| OE to RAS Delay Time                           | tord              | 35       |             | 40         |              | 45         |                                                  | ns   |             |

| Serial Clock Cycle Time                        | t <sub>SCC</sub>  | 40       | _           | 40         |              | 60         | <u> </u>                                         | ns   |             |

| Access Time from SC                            | t <sub>SCA</sub>  | _        | 40          | _          | 40           | _          | 60                                               | ns   | 10          |

| Access Time from SOE                           | t <sub>SEA</sub>  | _        | 25          | _          | 30           | _          | 40                                               | ns   | 10          |

# ■ ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS

$(T_A = 0 \text{ to } +70^{\circ}\text{C}, V_{CC} = 5\text{V} \pm 10\%, V_{SS} = 0\text{V})1, 10, 11 \text{ (continued)}$

| Parameter                                    | Symbol            | HM5 | 3461-10      | HM: | 3461-12                                          | HM  | 53461-15       |                                                  |             |

|----------------------------------------------|-------------------|-----|--------------|-----|--------------------------------------------------|-----|----------------|--------------------------------------------------|-------------|

|                                              | Symoon            | Min | Max          | Min | Max                                              | Min | Max            | Unit                                             | Note        |

| SC Pulse Width                               | t <sub>SC</sub>   | 10  | _            | 10  | _                                                | 10  |                | ns                                               | <u> </u>    |

| SC Precharge Width                           | tSCP              | 10  | _            | 10  | <b>†</b>                                         | 10  |                | ns                                               |             |

| Serial Data-out Hold Time after SC High      | tsoh              | 10  | _            | 10  |                                                  | 10  | <del> </del>   | пs                                               |             |

| Serial Output Buffer Turn-off Delay from SOE | t <sub>SEZ</sub>  | 0   | 25           | 0   | 25                                               | 0   | 30             | ns                                               |             |

| Serial Data-in Setup TIme                    | tSIS              | 0   | T            | 0   | <b>—</b>                                         | 0   |                | ns                                               | <del></del> |

| Serial Data-in Hold Time                     | tSIH              | 15  | _            | 20  | <b>1</b>                                         | 25  | <u> </u>       | ns                                               |             |

| DT to RAS Setup Time                         | t <sub>DTS</sub>  | 0   |              | 0   | <u> </u>                                         | 0   | <del> </del>   | ns                                               |             |

| DT to RAS Hold Time (Read Transfer Cycle)    | tRDH              | 80  |              | 90  |                                                  | 110 |                | ns                                               | <del></del> |

| DT to RAS Hold Time                          | tDTH              | 15  |              | 15  | <del>                                     </del> | 20  | <del></del>    | <del>                                     </del> |             |

| DT to CAS Hold Time                          | t <sub>CDH</sub>  | 20  | <del> </del> | 30  | <u> </u>                                         | 45  | <del>  -</del> | ns                                               |             |

| Last SC to DT Delay Time                     | tSDD              | 5   |              | 5   |                                                  | 10  | <del>  _</del> | ns                                               |             |

| First SC to DT Hold Time                     | tSDH              | 25  |              | 25  | <del> </del> -                                   | 30  |                | ns                                               |             |

| DT to RAS Delay Time                         | tDTR              | 10  |              | 10  | <u> </u>                                         | 10  |                | ns                                               |             |

| WE to RAS Setup Time                         | tws               | 0   |              | 0   |                                                  | 0   |                | ns                                               |             |

| WE to RAS Hold Time                          | twH               | 15  |              | 15  |                                                  |     |                | ns                                               |             |

| I/O to RAS Setup Time                        | t <sub>MS</sub>   | 0   |              | 0   |                                                  | 20  |                | ms                                               |             |

| I/O to RAS Hold Time                         | t <sub>MH</sub>   | 15  |              | 15  |                                                  | 0   |                | ns                                               |             |

| Serial Output Buffer Turn-off Delay from RAS | tSRZ              | 10  | 50           | 10  | 60                                               | 20  |                | ns                                               |             |

| SC to RAS Setup Time                         | tSRS              | 30  |              | 40  |                                                  | 10  | 75             | 115                                              |             |

| RAS to SC Delay Time                         | tSRD              | 25  |              | 30  |                                                  | 45  |                | ns                                               |             |

| Serial Data Input Delay Time from RAS        | tSID              | 50  |              |     |                                                  | 35  |                | ns                                               |             |

| Serial Data Input to DT Delay Time           | tSZD              | 0   |              | 60  |                                                  | 75  |                | ns                                               |             |

| SOE to RAS Setup Time                        | tES               | 0   |              | 0   |                                                  | 0   |                | ns                                               |             |

| SOE to RAS Hold Time                         |                   | 15  |              |     |                                                  | 0   |                | ns                                               |             |

| Serial Write Enable Setup Time               | terre             | 0   |              | 15  |                                                  | 20  |                | ns                                               |             |

| Serial Write Enable Hold Time                | tsws              | 35  |              | 0   |                                                  | 0   |                | ns                                               |             |

| Serial Write Disable Setup Time              | tswH              | 0   |              | 35  |                                                  | 55  |                | ns                                               |             |

| Serial Write Disable Hold Time               | tswis             | -   |              | 0   |                                                  | 0   |                | ns                                               |             |

| DT to Sout in Low-Z Delay Time               | t <sub>SWIH</sub> | 35  |              | 35  |                                                  | 55  |                | ns                                               |             |

| Notes: 1 AC measurements assume t = 5        | <sup>t</sup> DLZ  | 5   |              | 10  |                                                  | 10  |                | ns                                               |             |

Notes: 1. AC measurements assume  $t_T = 5$  ns.

- 2. Assumes that t<sub>RCD</sub> ≤ t<sub>RCD</sub> (max). If t<sub>RCD</sub> is greater than the maximum recommended value shown in this table, t<sub>RAC</sub> exceeds the value shown.

- 3. Measured with a load circuit equivalent to 2 TTL loads and 100 pF.

- 4. Assumes that  $t_{RCD} \ge t_{RCD}$  (max).

- 5. t<sub>OFF</sub> (max) defines the time at which the output achieves the open circuit condition and is not referenced to output voltage levels.

- 6. V<sub>IH</sub> (min) and V<sub>IL</sub> (max) are reference levels for measuring timing of input signals. Also, transition times are measured between V<sub>IH</sub> and V<sub>IL</sub>.

- 7. Operation with the t<sub>RCD</sub> (max) limit insures that t<sub>RAC</sub> (max) can be met, t<sub>RCD</sub> (max) is specified as a reference point only, if t<sub>RCD</sub> is greater than the specified t<sub>RCD</sub> (max) limit, then access time is controlled exclusively by t<sub>CAC</sub>.

- 8. twcs and tcwd are not restrictive operating parameters. They are included in the data sheet as electrical characteristics only: if twcs ≥ twcs (min), the cycle is an early write cycle and the data out pin will remain open circuit (high impedance) throughout the entire cycle; if tcwd ≥ tcwd (min), the cycle is a read/write and the data output will contain data read from the selected cell; if neither of the above sets of conditions is satisfied, the condition of the data out (at access time) is indeterminate.

- These parameters are referenced to CAS leading edge in an early write cycle and to WE leading edge in a delayed write or a read-modify-write cycle.

- 10. Measured with a load circuit equivalent to 2 TTL and 50 pF.

- 11. An initial pause of 100 µs is required after power-up. Then execute at least 8 initialization cycles.

## **III** TIMING WAVEFORMS

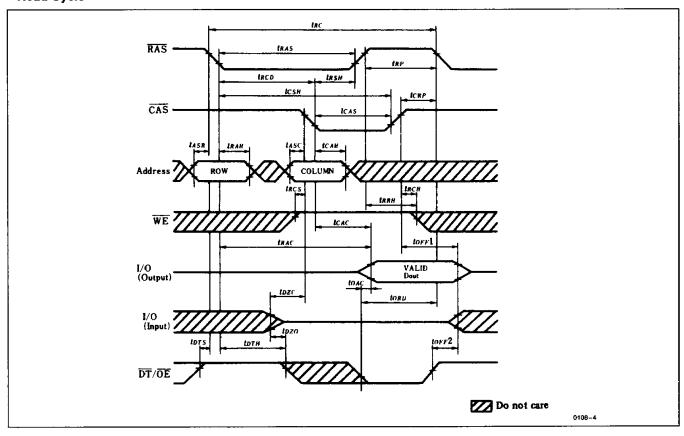

## • Read Cycle

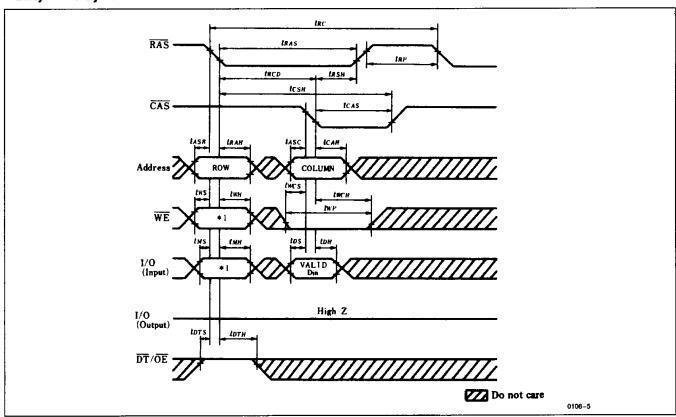

# • Early Write Cycle

Note: \*1. When  $\overline{WE}$  is "H" level, all the data on the I/O can be written into the cell. When  $\overline{WE}$  is "L" level, the data on the I/O are not written except for when I/O is "high" at the falling edge of  $\overline{RAS}$ .

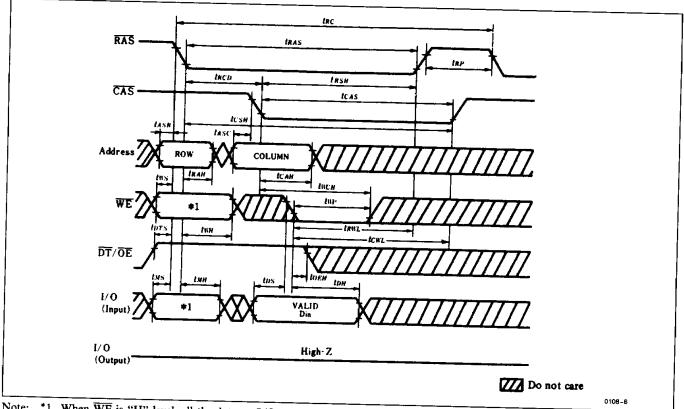

# Delayed Write Cycle

Note: \*1. When  $\overline{WE}$  is "H" level, all the data on  $I/O_1-I/O_4$  can be written into the memory cell. When  $\overline{WE}$  is "L" level, the data on I/Os are not written except for when I/O = "H" at the falling edge of  $\overline{RAS}$ .

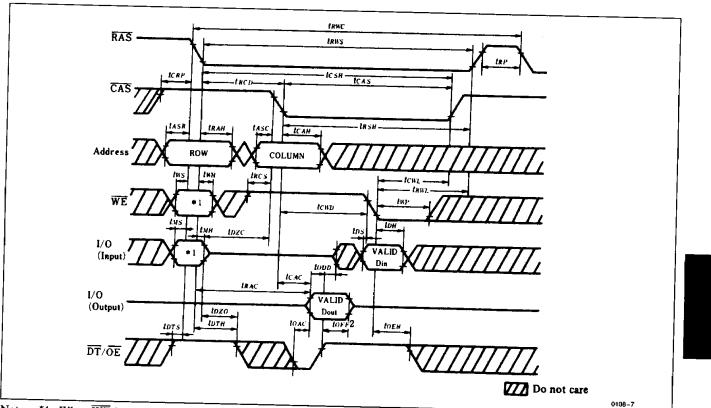

# Read-Modify-Write Cycle

Note: \*1. When WE is "H" level, all the data on I/O<sub>1</sub>-I/O<sub>4</sub> can be written into the memory cell.

When WE is "L" level, the data on I/Os are not written except for when I/O = "H" at the falling edge of RAS.

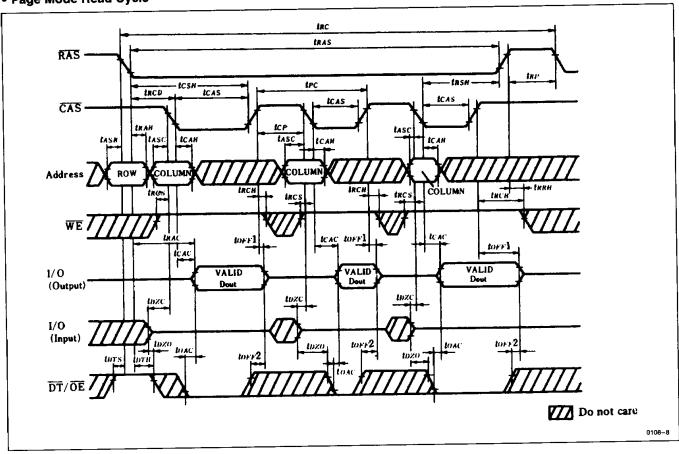

# Page Mode Read Cycle

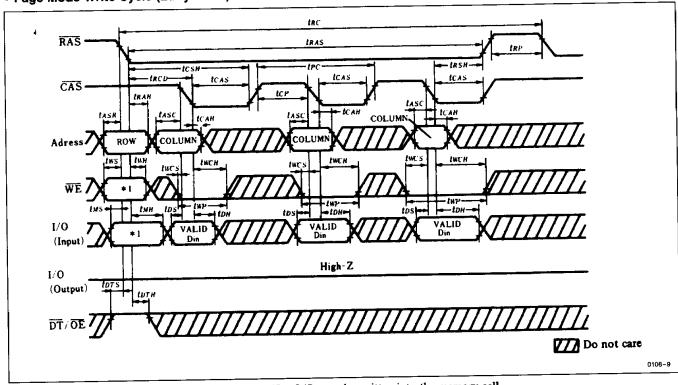

## • Page Mode Write Cycle (Early Write)

Note: \*1. When  $\overline{WE}$  is "H" level, all the data on I/O<sub>1</sub>-I/O<sub>4</sub> can be written into the memory cell.

When  $\overline{WE}$  is "L" level, the data on I/Os are not written except for when I/O = "H" at the falling edge of  $\overline{RAS}$ .

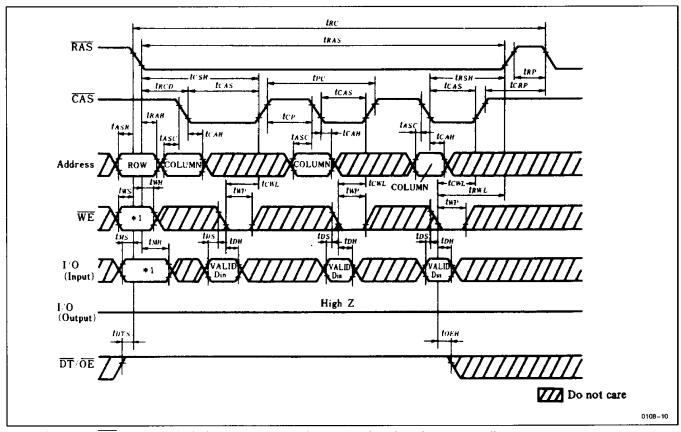

## • Page Mode Write Cycle (Delayed Write)

Note: \*1. When  $\overline{WE}$  is "H" level, all the data on  $I/O_1-I/O_4$  can be written into the memory cell. When  $\overline{WE}$  is "L" level, the data on  $I/O_5$  are not written except for when I/O = "H" at the falling edge of  $\overline{RAS}$ .

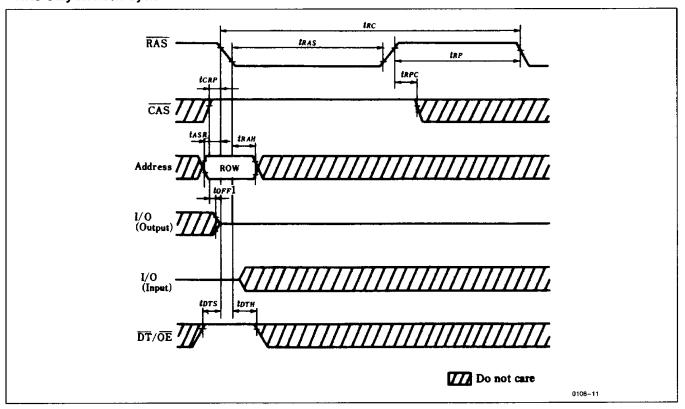

## • RAS Only Refresh Cycle

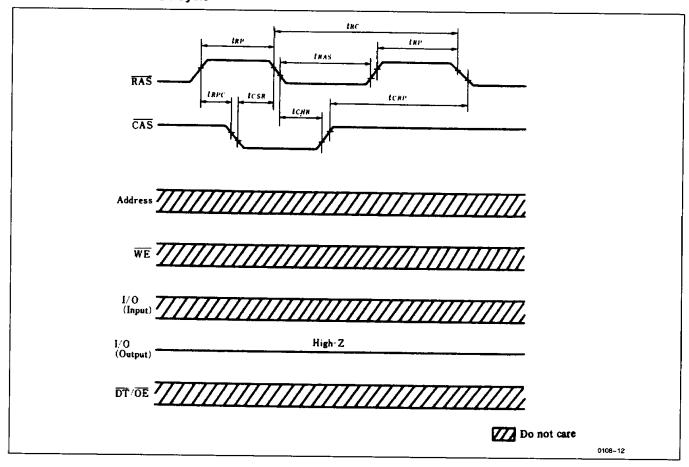

# • CAS Before RAS Refresh Cycle

## • Hidden Refresh Cycle

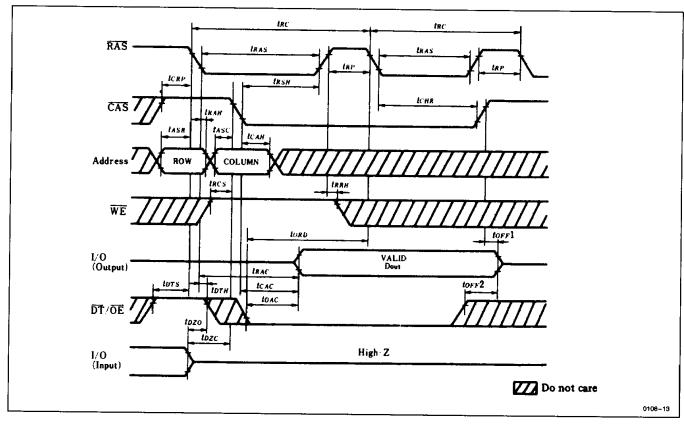

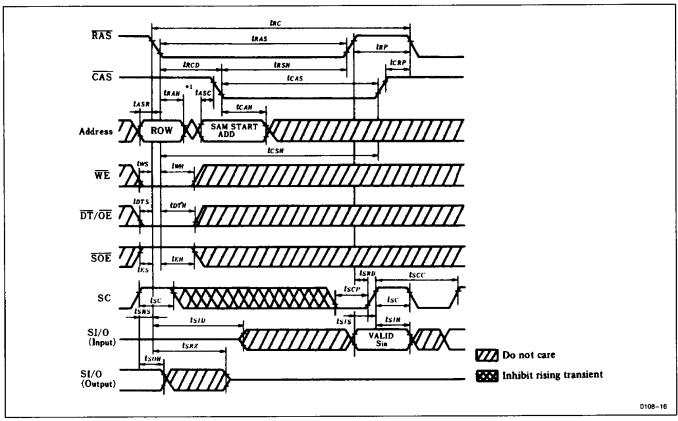

# • Read Transfer Cycle (1)\*1,\*2

Notes: \*1. In the case that the previous data transfer cycle was read transfer.

\*2. Assume that SOE is "L" level.

\*3. CAS and SAM start address need not be supplied every cycle, only when it is desired to change to a new SAM start address.

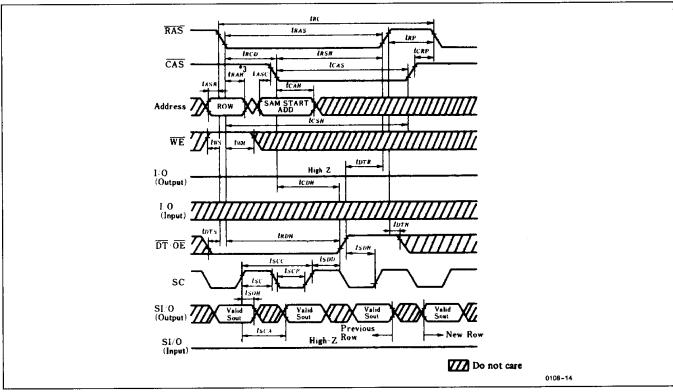

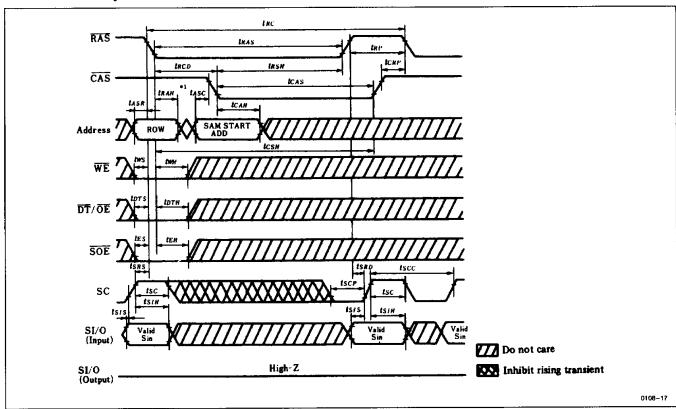

## • Read Transfer Cycle (2)\*1, \*2

otes: \*1. In the case that the previous data transfer cycle was write transfer or pseudo transfer.

\*2. Assume that  $\overline{SOE}$  is "L" level.

\*3. CAS and SAM start address need not be supplied every cycle, only when it is desired to change to a new SAM start address.

## • Pseudo Transfer Cycle

Note: \*1. CAS and SAM start address need not be supplied every cycle, only when it is desired to change to a new SAM start address.

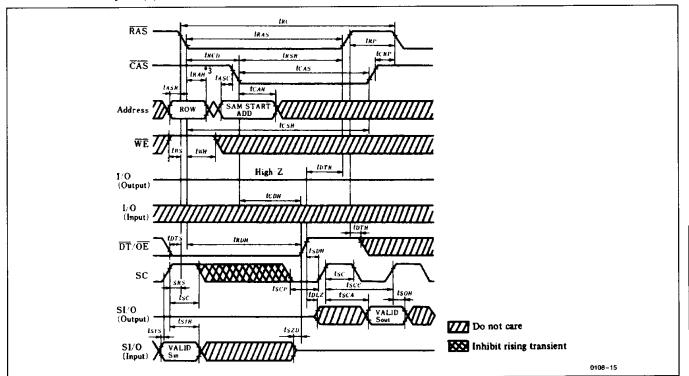

## • Write Transfer Cycle

Note: \*1. CAS and SAM start address need not be supplied every cycle, only when it is desired to change to a new SAM start address.

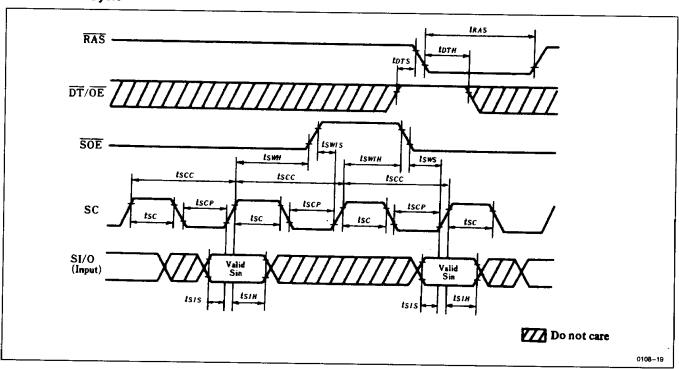

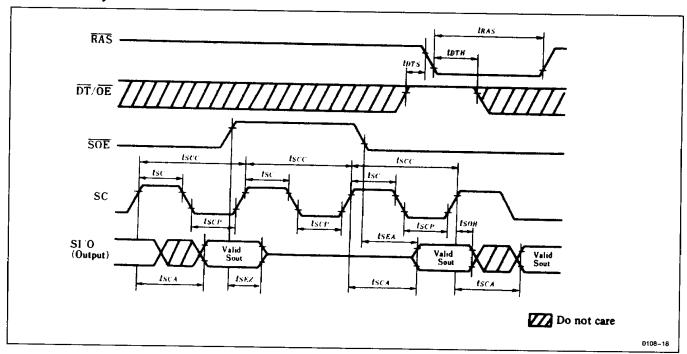

# • Serial Read Cycle

# Serial Write Cycle