# HM53051 Series

## 262,144-Word x 4-Bit Frame Memory

#### **■ DESCRIPTION**

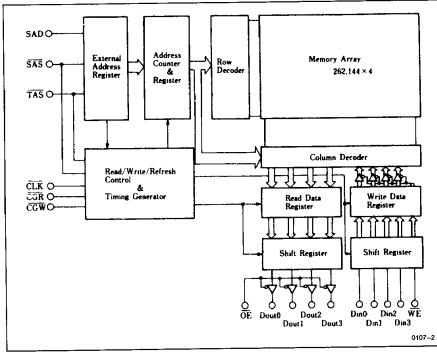

HM53051P is a 262,144-word x 4-bit frame memory, using the most advanced 1.3  $\mu m$  CMOS processes. It performs serial access by an internal address generator

It offers a high-speed cycle time of 45 ns or 60 ns (min). As input data and output data can be written or read in any cycle, synchronized with a system clock, and the delay between data read/write operations is freely settable. Y/C separation and frozen pictures can be realized easily in 4 fsc NTSC digital TV or VCR systems. Also, it enables random access in 32-word x 4-bit data block. With this function, picture in picture or a multiplexed picture can be displayed with ease.

# FEATURES

- 262,144-Word x 4-Bit Serial Access Memory

- Organized with Dual Ports

Serial Input ... x 4-Bit

Serial Output ... x 4-Bit

High Speed

Read/Write Cycle Time ... 45 ns/60 ns (min)

Access Time ... 35 ns/40 ns (max)

- · Semi-Synchronous Read/Write Cycle

- Low Power

Active: 200 mW (typ)

- Random Access in 32-Word x 4-Bit Blocks

- External Refresh Control is Unnecessary

#### **■ ORDERING INFORMATION**

| Part No.                   | Access Time    | Package                                   |

|----------------------------|----------------|-------------------------------------------|

| HM53051P-45<br>HM53051P-60 | 45 ns<br>60 ns | 300 mil 18-pin<br>Plastic DIP<br>(DP-18B) |

## **BLOCK DIAGRAM**

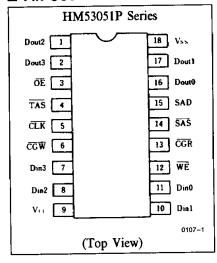

#### **■ PIN OUT**

#### **■ PIN DESCRIPTION**

| Pin Name         | Function                |

|------------------|-------------------------|

| D <sub>in</sub>  | Data Input              |

| D <sub>out</sub> | Data Output             |

| ŌĒ               | Output Enable           |

| TAS              | Transfer Address Strobe |

| CLK              | System Clock            |

| CGW              | Clock Gate (Write)      |

| CGR              | Clock Gate (Read)       |

| SAD              | Serial Address          |

| SAS              | Serial Address Strobe   |

| WE               | Read/Write Enable       |

#### **■ FUNCTIONAL DESCRIPTION**

#### Serial Access Memory with I/O Separated

Read cycle and write cycle of HM53051 can be operated independently synchronized with a system clock. It realizes time compression or expansion for picture in picture in digital TV, for example.

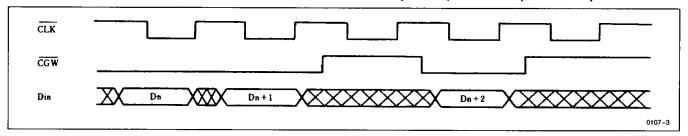

#### Write Cycle by CGW

Write data are taken in at the falling edge of the system clock  $\overline{CLK}$  when  $\overline{CGW}$  is low. If  $\overline{CGW}$  is high, HM53051 does not enter write cycle (cycle time is defined by system clock cycle time). Time is compressed easily with  $\overline{CGW}$ .

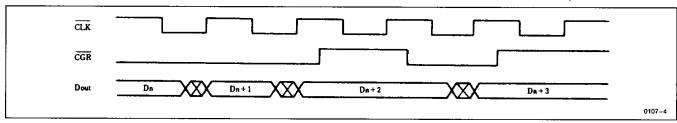

# • Read Cycle by CGR

Read data is output at the falling edge of the system clock  $\overline{\text{CLK}}$  when  $\overline{\text{CGR}}$  is low. If  $\overline{\text{CGR}}$  is high, HM53051 does

not enter read cycle (cycle time is defined by system clock time). Time is expanded is realized easily with  $\overline{\text{CGR}}$ .

#### RANDOM ACCESS

The HM53051 is also capable of random access by serial address input, SAD. Random access by the unit of 32-word x 4-bit is performed, when TAS is low after read address (AR0-AR12), write address (AW0-AW12) and mode setting

flags,  $\overline{\text{RF}}$  (Read Flag),  $\overline{\text{WF}}$  (Write Flag) and  $\overline{\text{MF}}$  (Mode Flag) are read into by  $\overline{\text{SAD}}$  with synchronous  $\overline{\text{SAS}}$ . In order to output data continuously, the address specified by  $\overline{\text{SAD}}$  increments automatically.

## **■ MODE PROGRAMMING**

Operation mode in HM53051 is programmed by the combination of SAD 5-bit.

| MF | WF | RF | AW0 | AR0 | Mode                                     |  |  |

|----|----|----|-----|-----|------------------------------------------|--|--|

| 0  | 0  | 0  | х   | х   | Write/Read Address Asynchronous Transfer |  |  |

| 0  | 0  | 1  | х   | х   | Write Address Asynchronous Transfer      |  |  |

| 0  | 1  | 0  | х   | х   | Read Address Asynchronous Transfer       |  |  |

| 0  | 1  | 1  | х   | х   |                                          |  |  |

| 1  | 0  | 0  | х   | х   | Write/Read Address Synchronous Transfer  |  |  |

| 1  | 0  | 1  | х   | х   | Write Address Synchronous Transfer       |  |  |

| 1  | 1  | 0  | х   | х   | Read Address Synchronous Transfer        |  |  |

| 1  | 1  | 1  | 1   | 1   | System Reset                             |  |  |

| 1  | 1  | 1  | 0   | 0   |                                          |  |  |

| 1  | 1  | 1  | 0   | 1   | Inhibit                                  |  |  |

| 1  | 1  | 1  | 1   | 0   |                                          |  |  |

Note: x means Don't Care.

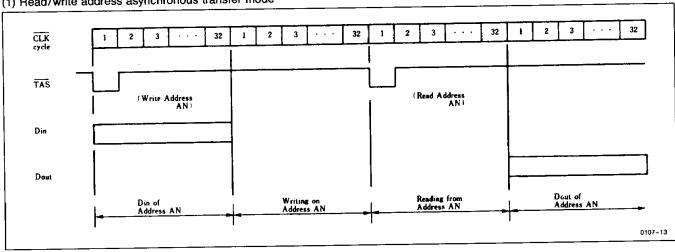

# ■ READ/WRITE ADDRESS ASYNCHRONOUS TRANSFER MODE

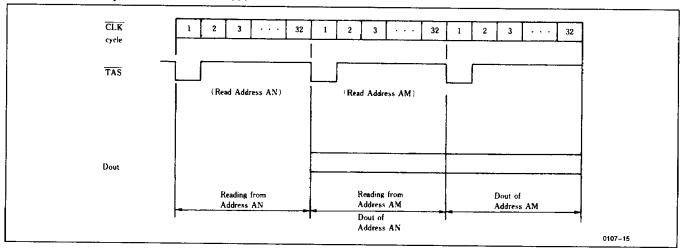

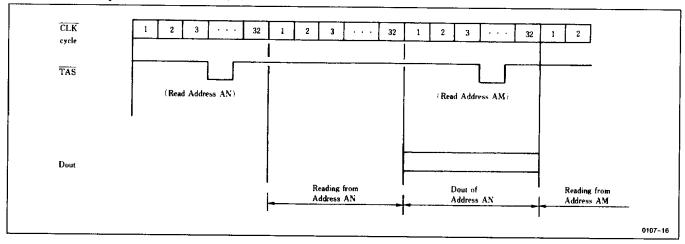

# Read Address Asynchronous Transfer Mode

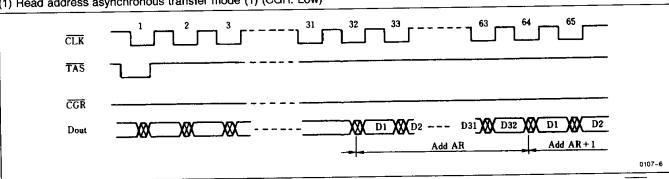

(1) Read address asynchronous transfer mode (1) (CGR: Low)

Note: The data block at read address AR, specified by SAD, is output starting from the 32nd system clock after the falling of TAS.

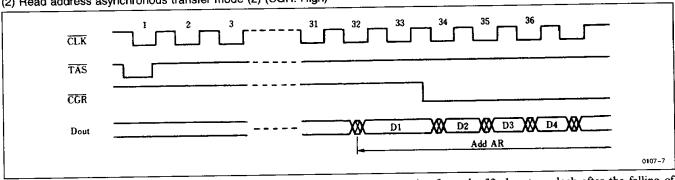

(2) Read address asynchronous transfer mode (2) (CGR: High)

1. The data block at read address AR, specified by SAD, is output starting from the 32nd system clock after the falling of Notes:

2. If  $\overline{\text{CGR}}$  is turned to low after 33rd clock from falling edge of  $\overline{\text{TAS}}$ , the data at read address AR( D2, D3, D4 ...) is output with synchronous  $\overline{CLK}$  while  $\overline{CGR}$  is low.

# Write Address Asynchronous Transfer Mode

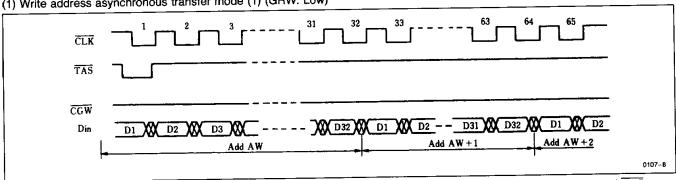

(1) Write address asynchronous transfer mode (1) (GRW: Low)

Note: The data block at write address AW, specified by SAD, is taken in starting from the 1st clock after the falling edge of TAS.

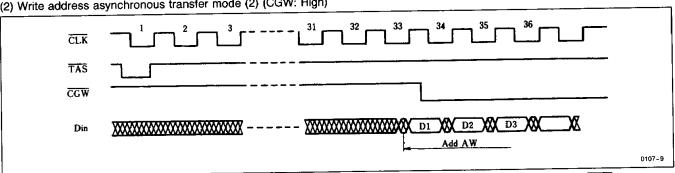

(2) Write address asynchronous transfer mode (2) (CGW: High)

Note: If  $\overline{CGW}$  is turned to low after falling of  $\overline{TAS}$ , the data block at write address AW is taken in with synchronous  $\overline{CLK}$ .

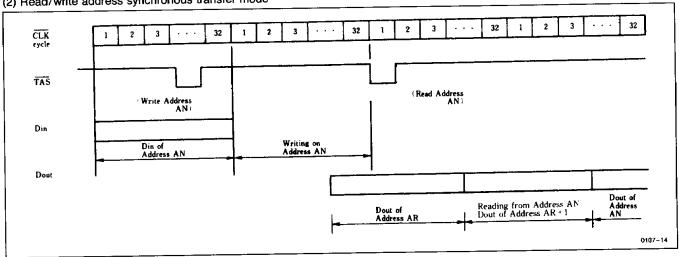

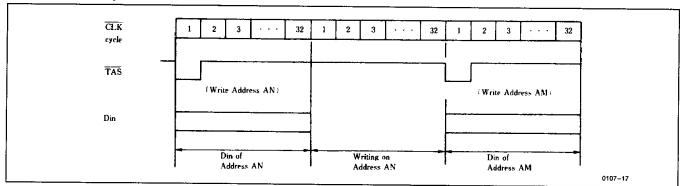

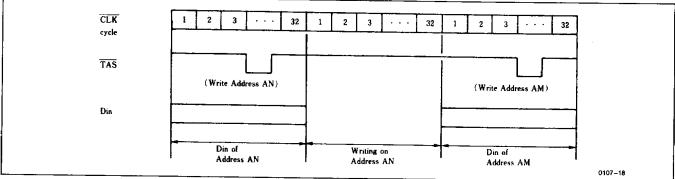

## ■ READ/WRITE ADDRESS SYNCHRONOUS TRANSFER MODE

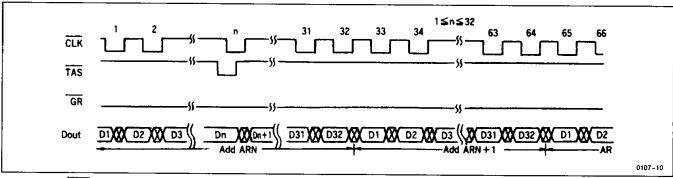

#### Read Address Synchronous Transfer Mode

Note: When TAS turns to low, the data block at read address AR, specified by SAD, is output after the data block at the present read address ARN, and the next address ARN + 1 is put out.

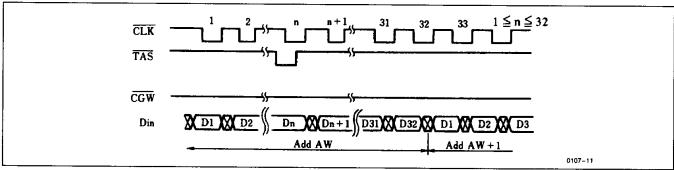

## Write Address Synchronous Transfer Mode

Note: When  $\overline{TAS}$  turns to low, the data block being written is taken into write address AW.

#### ■ SYSTEM RESET MODE

System reset mode is the same as read/write address asynchronous transfer mode except that read/write address are reset to 0.

System Reset by SAD

Note: System reset mode starts when MF, WF, RF, AWO, and ARO are all high.

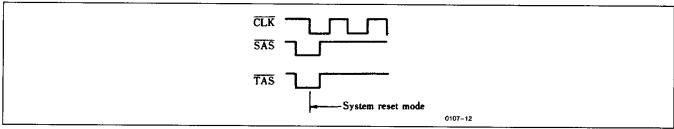

System Reset by SAS and TAS

Note: System reset mode starts when both  $\overline{SAS}$  and  $\overline{TAS}$  are low at the falling edge of the  $\overline{CLK}$ .

#### • 1 Field Delay

Note: Field-delayed data is output, when  $\overline{CGR}$  and  $\overline{CGW}$  turn to high before the system reset at the beginning of every field, and turn to low simultaneously after the 33rd clock from the system reset.

# ■ NOTES ON USING HM53051

- Input/Output data of 32 words is not written or read in read/write address asynchronous transfer mode or during system reset. The data is written or read out in blocks of 32-word x 4-bit. Input data of less than 32 words is not written in write address asynchronous transfer mode or during system reset. When asynchronous read address transfer mode or system reset mode is activated, output from the current data block will continue. When output data from the current data block is finished, the next data block is not read out if it has less than 32 words.

- Input data is not read out immediately. The data (32 word x 4-bit) is written into the memory array in the next 32 cycles after it is taken in.

The data can be read out only after writing to the memory array is completed. If read address transfer mode is programmed after the 33 word clock from on input data block, new data can be read out. If this mode is programmed before the 33 word clock, new data or old data is output.

(1) Read/write address asynchronous transfer mode

(2) Read/write address synchronous transfer mode

## Mode Programming

Do not reprogram read address transfer mode before a read operation of the previous read address transfer mode or system reset mode is completed. If it is reprogrammed during a read operation, address becomes invalid, and the device may malfunction.

Do not reprogram write address transfer mode or system reset mode before a write operation of the previous write address transfer mode or system reset mode is completed. If it is reprogrammed during a write operation, address becomes invalid, and the device may malfunction.

# (1) Read address asynchronous transfer mode

#### (2) Read address synchronous transfer mode

## (3) Write address asynchronous transfer mode

# (4) Write address synchronous transfer mode

Before an address can be set, 32  $\overline{\text{CLK}}$  initialization cycles or more are required.

#### ■ ABSOLUTE MAXIMUM RATINGS

| Parameter                                      | Symbol            | Rating         | Unit |

|------------------------------------------------|-------------------|----------------|------|

| Voltage on Any Pin Relative to V <sub>SS</sub> | $v_{\mathrm{T}}$  | - 1.0 to + 7.0 | v    |

| Power Dissipation                              | $P_{T}$           | 1.0            | w    |

| Operating Temperature                          | Торг              | 0 to +70       | °C   |

| Storage Temperature                            | T <sub>stg</sub>  | -35  to  + 125 | °C   |

| Storage Temperature (under Bias)               | T <sub>bias</sub> | - 10 to + 85   | °C   |

# **■ ELECTRICAL CHARACTERISTICS**

# • Recommended DC Operating Conditions ( $T_A = 0 \text{ to } +70^{\circ}\text{C}$ )

| Parameter       | Symbol          | Min   | Тур | Max | Unit | Note |

|-----------------|-----------------|-------|-----|-----|------|------|

| Supply Voltage  | V <sub>CC</sub> | 4.5   | 5.0 | 5.5 | V    |      |

| V <sub>SS</sub> | 0               | 0     | 0   | v   |      |      |

| Input Voltage   | V <sub>IH</sub> | 2.7   | _   | 6.5 | v    |      |

|                 | $v_{IL}$        | - 0.5 |     | 0.8 | v    | 1    |

Note: 1. - 3.0V for pulse width  $\leq 10$  ns.

# $\bullet$ DC and Operating Characteristics (T<sub>A</sub> = 0 to +70°C, V<sub>CC</sub> = 5V $\pm$ 10%, V<sub>SS</sub> = 0V)

| Parameter                      | Symbol          | Min  | Тур | Max | Unit | Test Conditions                                                | Note |

|--------------------------------|-----------------|------|-----|-----|------|----------------------------------------------------------------|------|

| Operating Power Supply Current | I <sub>CC</sub> | _    | 40  | 60  | mA   | Min. Cycle,<br>I <sub>out</sub> = 0 mA                         |      |

| Input Leakage Current          | I <sub>LI</sub> | - 10 |     | 10  | μΑ   | $V_{CC} = 5.5V$<br>$V_{in} = V_{SS}$ to $V_{CC}$               | _    |

| Output Leakage Current         | I <sub>LO</sub> | - 10 |     | 10  | μΑ   | $\overline{OE} = V_{IH}$ $V_{out} = V_{SS} \text{ to } V_{CC}$ |      |

| Output Voltage                 | V <sub>OL</sub> |      |     | 0.4 | v    | $I_{OL} = 4.2 \mathrm{mA}$                                     |      |

|                                | v <sub>oh</sub> | 2.4  |     |     | v    | $I_{OH} = -2 \text{ mA}$                                       |      |

# • Capacitance ( $T_A = 25$ °C, f = 1.0 MHz)

| Parameter          | Symbol          | Min | Тур | Max | Unit | Test Conditions | Note |

|--------------------|-----------------|-----|-----|-----|------|-----------------|------|

| Input Capacitance  | C <sub>in</sub> | _   | _   | 5   | pF   | $V_{in} = 0V$   |      |

| Output Capacitance | Cout            |     | _   | 7   | pF   | $V_{out} = 0V$  |      |

Note: This parameter is sampled and not 100% tested.

# HM53051 Series

$\bullet$  AC Characteristics (V $_{CC}=5V~\pm10\%,\,T_{A}=0~to~+70^{\circ}C)$

# **AC Test Conditions**

Input and Output Timing Reference Levels:

1.5V

Input Pulse Levels:

V<sub>SS</sub> to 3V

Input Rise and Fall Times: Output Load: 5 ns 2 TTL + 50 pF

(Including scope and jig)

|                                               |                  | HM53051-45 |     | HM53 | HM53051-60 |      |  |

|-----------------------------------------------|------------------|------------|-----|------|------------|------|--|

| Parameter                                     | Symbol           | Min        | Max | Min  | Max        | Unit |  |

| System Clock Cycle Time                       | t <sub>CC</sub>  | 45         | 300 | 60   | 300        | ns   |  |

|                                               | t <sub>CL</sub>  | 15         | _   | 15   | _          | ns   |  |

| CLK Pulse Width                               | t <sub>CH</sub>  | 15         | _   | 15   |            | ns   |  |

| Access Time from CLK                          | †AC              | _          | 35  |      | 40         | ns   |  |

| Output Hold Time                              | t <sub>OH</sub>  | 5          | _   | 8    |            | ns   |  |

| Output Enable Access Time                     | t <sub>OEA</sub> |            | 25  |      | 30         | ns   |  |

| Output Enable to Output in Low Z              | tolz             | 5          | _   | 5    |            | ns   |  |

| Output Disable to Output in High Z            | tonz             | 0          | 20  | 0    | 20         | ns   |  |

| CGR Setup Time                                | tGRS             | 15         |     | 15   |            | ns   |  |

| CGR Hold Time                                 | tGRH             | 5          |     | 5    |            | ns   |  |

| CGW Setup Time                                | t <sub>GWS</sub> | 15         |     | 15   |            | ns   |  |

| CGW Hold Time                                 | t <sub>GWH</sub> | 5          |     | 5    | <u></u>    | ns   |  |

| Write Command Setup Time                      | twcs             | 15         |     | 15   |            | ns   |  |

| Write Command Hold Time                       | twcH             | 5          |     | 5    |            | ns   |  |

| Data Input Setup Time                         | t <sub>DS</sub>  | 15         |     | 15   | _          | ns   |  |

| Data Input Hold Time                          | t <sub>DH</sub>  | 5          |     | 5    |            | ns   |  |

| SAS Cycle Time                                | t <sub>SC</sub>  | 45         |     | 60   |            | ns   |  |

|                                               | t <sub>SL</sub>  | 15         |     | 15   |            | ns   |  |

| SAS Pulse Width                               | t <sub>SH</sub>  | 15         |     | 15   | -          | ns   |  |

| Serial Address Setup Time                     | t <sub>SAS</sub> | 15         |     | 15   |            | ns   |  |

| Serial Address Hold Time                      | t <sub>SAH</sub> | 5          |     | 5    |            | ns   |  |

| SAS Setup Time during Mode Programming        | t <sub>SSH</sub> | 15         |     | 15   |            | ns   |  |

| SAS Hold Time during Mode Programming         | tSHH             | 5          | _   | 5    |            | ns   |  |

| TAS Setup Time                                | t <sub>TS</sub>  | 15         |     | 15   |            | ns   |  |

| TAS Hold Time                                 | t <sub>TH</sub>  | 5          |     | 5    |            | ns   |  |

| SAS Setup Time during System Reset by SAS/TAS | tssl             | 15         | _   | 15   | _          | ns   |  |

| SAS Hold Time during System Reset by SAS/TAS  | t <sub>SHL</sub> | 5          | _   | 5    |            | ns   |  |

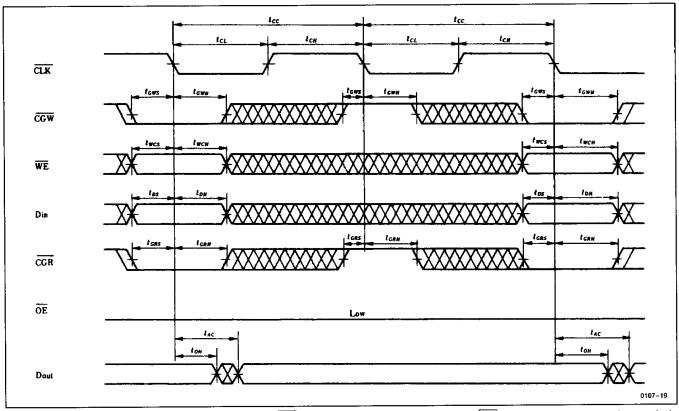

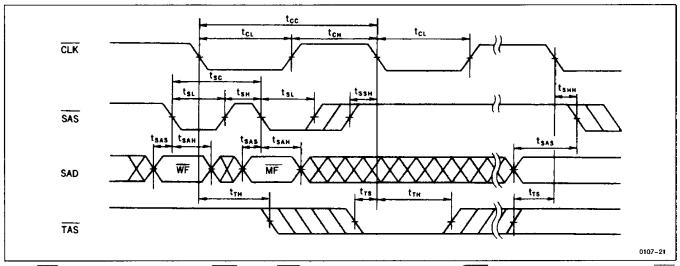

# **■ TIMING WAVEFORMS**

## • Read/Write Cycle

Notes: 1. Write cycle starts when  $\overline{CGW}$  is low and  $\overline{WE}$  is low. Data are not written when  $\overline{WE}$  is high. Time-compression mode is realized by controlling  $\overline{CGW}$ .

2. Read cycle starts when  $\overline{CGR}$  is low. Time-expansion mode is realized by controlling  $\overline{CGR}$ .

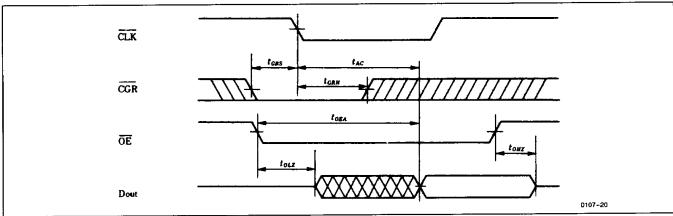

# • Read Cycle (OE Control)

Notes: 1. t<sub>OHZ</sub> is defined by the time at which the output achieves the open circuit condition.

2.  $t_{\mbox{\scriptsize OLZ}}$  and  $t_{\mbox{\scriptsize OHZ}}$  are sampled and not 100% tested.

#### • Mode Selection

Note: SAS operates asynchronously with CLK. When TAS is low at the falling edge of the CLK, the address transfer cycle starts. SAS should be high during the address transfer cycle.

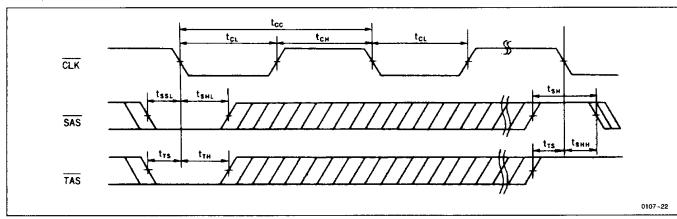

# • SAS, TAS Reset Mode

Note: The mode which was selected by SAD before  $\overline{SAS}$  and  $\overline{TAS}$  reset, if  $\overline{SAS}$  and  $\overline{TAS}$  are reset, should be changed because SAD is newly taken into by SAS. The mode should be reselected by SAD after  $\overline{SAS}$  and  $\overline{TAS}$  reset.