# SONY

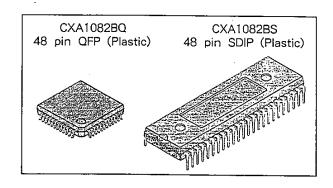

# CXA1082BQ/BS

# Servo Signal Processor for CD Player

# Description

CXA1082BQ/BS is a bipolar IC designed for the servo control of the compact disc player. The only difference from CXA1082AQ/AS is the FZC threshold.

#### **Features**

- Single power supply, 5 V

- Dual power supply, ±5 V

- Low power consumption (165 mW Typ.: ±5 V, 100 mW, 5 V)

- Servo functions same as the CX20108 (focus, tracking, and sled servo)

- Built-in auto sequencer

- · Built-in LPF for spindle servo

- Built-in loop filter and VCO for EFM clock reproduction PLL

- · Fewer external parts

- Built-in circuit for preventing sled runaway

- · Built-in circuit for disc defects

- Built-in anti-shock circuit

- High-speed access using a linear motor

- Sharing of the serial data bus of the microcomputer with the CX23035 or CXD1135Q

- Compatible in the upword with the CX20108 for microcomputer software

- The peaks of focus search, track jump, and sled kick pulse can be set with external resistors.

#### **Functions**

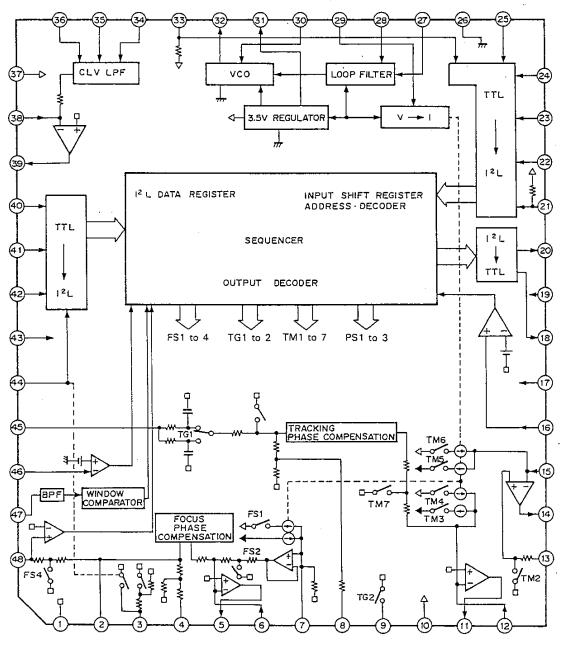

- · Focus servo control

- Tracking servo control

- Sled servo control

- Spindle servo

LPF, drive amplifier

- EFM clock reproduction PLL Loop filter, 8.64 MHz VCO

- Auto sequencer Built-in RAM

#### Structure

Bipolar silicon monolithic IC

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

# Absolute Maximum Ratings (Ta = 25°C)

| <ul> <li>Supply voltage</li> </ul>              | Vcc - VEE   | 12            | V  |

|-------------------------------------------------|-------------|---------------|----|

| <ul> <li>Operating temperature</li> </ul>       | Topr        | -20  to  +75  | °C |

| <ul> <li>Storage temperature</li> </ul>         | Tstg        | -55 to $+150$ | °C |

| <ul> <li>Allowable power dissipation</li> </ul> | PD CXA1082E | 3Q 833        | mW |

|                                                 | CXA1082E    | 3S 1330       | mW |

# **Recommended Operating Conditions**

| • Sup | pply voltage |  |

|-------|--------------|--|

|-------|--------------|--|

Vcc — VEE

4 to 11

\

Vcc — DGND

4 to 5.5

\

# **Block Diagram**

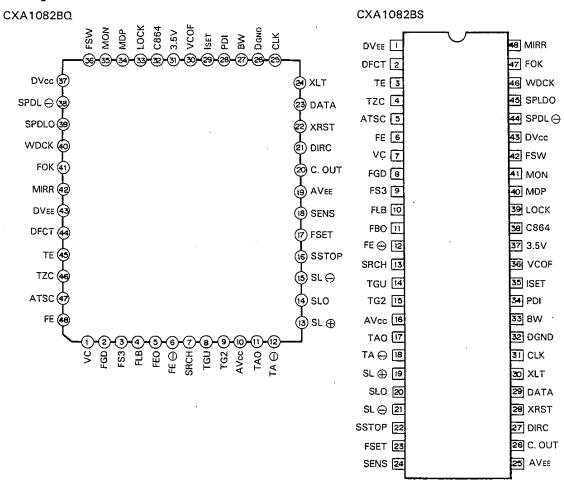

# Pin Configuration

# Pin Description

Numbers in ( ) show CXA1082BS

| No.   | Symbol | Equivalent Circuit | Description                                                                           |

|-------|--------|--------------------|---------------------------------------------------------------------------------------|

| 2 (8) | FGD    | 20 N               | Connect a capacitor between this pin and pin 3 (9) to reduce the high-frequency gain. |

| 3 (9) | FS3    | 3 180 46K W        | The high-frequency gain of the focus servo can be changed by switching FS3 ON or OFF. |

| No.                                     | Symbol            | Equivalent Circuit                | Description                                                                        |

|-----------------------------------------|-------------------|-----------------------------------|------------------------------------------------------------------------------------|

| 4 (10)                                  | FLB               | 40K W W W                         | Time constant external pin for rising low bandwidth of the focus servo.            |

| 5 (11)<br>11 (19)<br>14 (20)<br>39 (45) | FEO TAO SLO SPDLO | 9 Vcc 11 W 100 µА VEE             | Focus drive output  Tracking drive output  Sled drive output  Spindle drive output |

| 6 (12)                                  | FE —              | 6 ¥90К 2,5µА VEE                  | Inverse input pin for the focus amplifier.                                         |

| 7 (13)                                  | SRCH              | 7 180<br>50K ₹3.5µA 1 11µA<br>VEE | Pin for providing a time constant to generate the focus search waveform.           |

| 8 (14)                                  | TGU               | Vcc<br>20 K<br>W W W<br>8 82 K    | Pin for providing a time constant to switch the tracking gain of high-frequency.   |

| 9 (15)                                  | TG2               | 9 180<br>W 470К 2µA VEE           | Pin for providing a time constant to change the high-frequency tracking gain.      |

| No.     | Symbol | Equivalent Circuit                  | Description                                                                                         |

|---------|--------|-------------------------------------|-----------------------------------------------------------------------------------------------------|

| 12 (18) | TA —   | Vcc<br>180 ≥90K<br>180 111µA<br>VEE | Inverse input pin for the tracking amplifier.                                                       |

| 13 (19) | SL +   | 10K<br>10K<br>W                     | Non-inverse input pin for the sled amplifier.                                                       |

| 15 (21) | SL     | 180<br>15<br>3 µА 122 µА<br>VEE     | Inverse input pin for the sled amplifier.                                                           |

| 16 (22) | SSTOP  | 180 Vcc<br>180 VEE                  | Pin for detecting a signal for the ON/OFF limit switch of the innermost part of the disc.           |

| 17 (23) | FSET   | Vcc<br>17<br>180<br>15K ₹15K<br>VEE | Pin for setting the peak frequency of the focus, tracking phase compensation and f0 of the CLV LPF. |

| 18 (24) | SENS   | 180 ¥20K Vcc                        | Pin to output FZC, AS, TZC, SSTOP and BUSY by command from CPU.                                     |

| 20 (26) | C. OUT | (2) 100K                            | Track number count signal output                                                                    |

| No.                                                  | Symbol                           | Equivalent Circuit                   | Description                                                                                                                                                                                                                                                                              |

|------------------------------------------------------|----------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21 (27)  22 (28)  23 (29)  24 (30)  25 (31)  33 (39) | DIRC  XRST  DATA  XLT  CLK  LOCK | 21 Vcc<br>23 47 К<br>23 M<br>180 Vee | Pin for one-track jump Contains a 47 kΩ pull-up resistor. Reset input pin, reset at "L" Serial data input from CPU Latch input from CPU Serial data transfer clock input from CPU Pin for the operation of the sled runaway prevention circuit at "L" Contains a 47 kΩ pull-up resistor. |

| 27 (33)                                              | BW                               | 2.7 K<br>4.7 K ₹ VEE                 | Pin for providing a time constant for the loop filter.                                                                                                                                                                                                                                   |

| 28 (34)                                              | PDI                              | 4.7 K<br>M<br>100 P                  | Input pin for the CX23035/CXD1135 phase comparator output PDO.                                                                                                                                                                                                                           |

| 29 (35)                                              | ISET                             | 180 10K W VEE                        | Current is input, determining the peaks of focus search, track jump, and sled kick.                                                                                                                                                                                                      |

| 30 (36)                                              | VCOF                             | 39 TOK                               | The free-running frequency of VCO is almost proportional to the resistance value between this pin and pin 31 (37).                                                                                                                                                                       |

| 32 (38)                                              | C864                             | ₹DVcc<br>₹ 180                       | Output pin of 8.64 MHz VCO.                                                                                                                                                                                                                                                              |

| No.                                     | Symbol                      | Equivalent Circuit                   | Description                                                                                                                                                                                 |

|-----------------------------------------|-----------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 34 (40)                                 | MDP                         | 180 W 20K 14.5K                      | Pin for connecting the CX23035/CXD1135 MDP pin.                                                                                                                                             |

| 35 (41)                                 | MON                         | Vcc<br>180<br>35<br>W 20.5K<br>VEE   | Pin for connecting the CX23035/CXD1135 MON pin.                                                                                                                                             |

| 36 (42)                                 | FSW                         | Vcc<br>180<br>36<br>W<br>220K<br>VEE | Pin for providing an external LPF time constant of the CLV servo error signal.                                                                                                              |

| 38 (44)                                 | SPDL —                      | 180 VEE                              | Inverse input pin for the spindle drive amplifier.                                                                                                                                          |

| 40 (46)<br>41 (47)<br>42 (48)<br>44 (2) | WDCK<br>FOK<br>MIRR<br>DFCT | 180<br>41<br>42<br>44<br>VEE         | Clock input for auto sequence, usually 88.2 kHz is input FOK signal input pin Mirror signal input pin Defect signal input pin for the operation of the defect countermeasure circuit at "H" |

| 45 (3)                                  | ΤE                          | 680K<br>680K<br>W                    | Input pin for tracking error signals.                                                                                                                                                       |

| No.    | Symbol | Equivalent Circuit                   | Description                                            |

|--------|--------|--------------------------------------|--------------------------------------------------------|

| 46 (4) | TZC    | Vcc<br>√7 ji A<br>180<br>√75 K ₹     | Input pin for the zero-cross tracking comparator.      |

| 47 (5) | ATSC   | Vcc 470K<br>470K<br>W 47P<br>VEE 47P | Input pin of the window comparator for ATSC detection. |

| 48 (6) | FE     | Vcc<br>7μ<br>180<br>¥20K<br>VEE      | Input pin for focus error signals.                     |

### **Electrical Characteristics**

|             |             |                            | T       |    |    |    |    | sw | condi | tions |    |    |     |     |     |          | Bias o  |               |         |    |                | 1             | = 2.5V AV <sub>εε</sub> , DV <sub>εε</sub> Description of output  |        |        | GND=   |      |

|-------------|-------------|----------------------------|---------|----|----|----|----|----|-------|-------|----|----|-----|-----|-----|----------|---------|---------------|---------|----|----------------|---------------|-------------------------------------------------------------------|--------|--------|--------|------|

| Test<br>No. |             | Test items                 | Symbol  | Sì | S2 | S3 | S4 | S5 | S6    | S7    | S8 | S9 | S10 | Sii | SD  | E1       | E       | $\overline{}$ | E3      | E4 | Input<br>point | Test<br>point | waveform                                                          | Min.   | Тур.   | Max.   | Unit |

| ł           | Sup         | oply current 1             | VICC    |    |    |    |    |    |       |       |    |    |     |     | 00  | 0        | 0       | T             | 0       | 0  |                | 10            | Measure after resetting                                           | 2, 8   | 5, 5   | 8, 2   | · mA |

| 2           | Sup         | oply current 2             | Dicc    |    |    |    |    |    |       |       |    |    |     |     |     | П        | П       | 1             | П       |    |                | 37            |                                                                   | 10.8   | . 15.0 | 19.2   | mА   |

| 3           | Sup         | oply current 3             | A, DIEE |    |    |    |    |    |       |       |    |    |     |     |     | $\top$   | Ħ       | $\top$        | $\Box$  | 1  |                | 19<br>43      |                                                                   | 9.8    | 13, 0  | 16, 2  | mА   |

| 4           | Sup         | oply current 4             | IDGND   |    |    |    |    |    |       |       |    |    |     |     |     | Ħ        | П       |               | T       |    |                | 26            |                                                                   | 4.8    | 7.5    | 10, 2  | mΑ   |

| 5           |             | DC voltage gain            | Grao    |    |    |    |    |    |       |       |    |    |     |     | 08  | П        | П       |               |         |    | 48             | 5             | SG == 10 Hz, 200mVp-p                                             | 18.0   | 21.0   | 24.0   | dB   |

| 6           |             | Feedthrough                | VEROF   | 0  | 0  |    |    |    |       |       |    |    |     |     |     |          |         |               | $\prod$ | Τ  | П              |               | SG = 10kHz, 40mVp-p, Gain differ-<br>ence between 08 and 00 of SD |        |        | -35    | dB   |

| 7           | Į,          | Max. output<br>voltage I   | VFEOI   |    |    |    |    |    |       |       |    |    | 0   |     | 08  | П        | П       |               |         |    | П              |               | SG = 0.5VDC                                                       | 1, 98  |        |        | ٧    |

| 8           | Focus servo | Max. output<br>voltage 2   | VFEO2   |    |    |    |    |    |       |       |    |    | 0   |     | 08  |          | П       |               |         |    |                | l i           | SG = -0.5VDC                                                      |        |        | -1. 98 | ٧    |

| 9           | OV          | Max. output<br>voltage 3   | VFE03   |    |    | 0  |    |    |       |       |    |    | 0   |     | 08- |          | П       |               |         |    |                | П             | SG = 0.5VDC                                                       | 1, 18  |        |        | ٧    |

| 10          |             | Max. output<br>voltage 4   | VITEO4  |    |    | 0  |    |    |       |       |    |    | 0   |     | 08  |          |         |               | П       |    |                |               | SG = -0.5VDC                                                      |        |        | -i.18  | ٧    |

| n           |             | Search output<br>voltage 1 | VSRCIII |    |    |    |    |    |       |       |    |    |     |     | 02  |          | П       | T             | П       |    |                |               |                                                                   | -0. 64 | -0, 55 | -0, 36 | ٧    |

| 12          |             | Search output<br>voltage 2 | VSRC112 |    |    |    |    |    |       |       |    |    |     |     | 03  |          | П       |               | П       |    |                |               |                                                                   | 0.36   | 0, 55  | 0, 64  | ٧    |

| 13          |             | DC voltage gain            | GTEO    |    |    |    | 0  |    |       |       |    |    |     |     | 25  |          | П       |               |         |    | 45             | 11            | SG = 10 Hz, 500mVp-p                                              | 11.6   | 14.6   | 17, 6  | dB   |

| 14          |             | Feedthrough                | VTEOF   |    |    |    | 0  |    |       |       |    |    |     |     | 13  |          | П       |               | П       |    | П              |               | SG=10kHz,100mVp-p,Gain differ-<br>ence between 25 and 20 of SD    |        |        | ~39    | dB   |

| 15          | -3          | Max, output<br>voltage i   | VTEPI   |    |    |    |    |    |       |       |    |    |     | 0   | 25  |          |         |               |         |    |                |               | SG = -1.5VDC                                                      | 1. 98  |        |        | ٧    |

| 16          | Tracking    | Max. output<br>voltage 2   | VTEP2   |    |    |    |    |    |       |       |    |    |     | 0   | 25  |          |         |               | П       |    | Т              |               | SG = 1.5VDC                                                       |        |        | ~1.98  | v    |

| 17          | g servo     | Max. output<br>voltage 3   | VTEP3   |    |    |    |    |    |       |       | 0  |    |     | 0   | 25  |          |         |               |         |    |                |               | SG = -1.5VDC                                                      | 1, 18  |        |        | ٧    |

| 18          | •           | Max. output<br>voltage 4   | VTEP4   |    |    |    |    |    |       |       | 0  |    |     | 0   | 25  | П        |         |               |         |    |                |               | SG = 1.5VDC                                                       |        |        | -l, 18 | ٧    |

| 19          |             | Jump output<br>voltage I   | VJUMPI  |    |    |    |    |    |       |       |    |    |     |     | 2C  | П        | П       |               | П       |    |                |               |                                                                   | -0, 64 | -0, 55 | -0, 36 | ٧    |

| 20          |             | Jump output<br>voltage 2   | VJUMP2  |    |    |    |    |    |       |       |    |    |     |     | 28  |          | П       |               | П       |    |                |               |                                                                   | 0, 36  | 0,55   | 0, 64  | ٧    |

| 21          |             | DC voltage gain            | GSLO    |    |    |    |    |    |       |       |    |    |     |     | 25  |          | П       |               | П       |    | 13             | 14            | SG = 101fz<br>Openloop gain                                       | 50     | 56     | 62     | dB   |

| 22          | Sled        | Max. output<br>voltage 1   | VSLPI   |    |    |    |    |    |       |       |    |    |     |     | 25  |          | П       |               | П       |    |                |               | SG = 0.4VDC                                                       | 1, 98  |        |        | ٧    |

| 23          | ed servo    | Max. output<br>voltage 2   | VSLP2   |    |    |    |    |    |       |       |    |    |     |     | 25  |          | П       | T             | П       |    |                |               | SG = -0.4VDC                                                      |        |        | -1, 98 | V    |

| 24          | ò           | Max. output<br>voltage 3   | VSLP3   |    |    |    |    |    |       |       |    | 0  |     |     | 25  | $\sqcap$ | $\prod$ | T             | $\prod$ |    |                | П             | SG = 0.4VDC                                                       | i, 18  |        |        | ٧    |

\*Serial data (hex)

| Test |               | Test items                 | Symbol   |    |    |    |    | sw | cond | itions |        |    |     |     | . * | В      | ias co | nditi | ons                                               | lnou     | Test     | Description of output                                     |        |       |        |      |

|------|---------------|----------------------------|----------|----|----|----|----|----|------|--------|--------|----|-----|-----|-----|--------|--------|-------|---------------------------------------------------|----------|----------|-----------------------------------------------------------|--------|-------|--------|------|

| No.  |               | rest tterns                | 3,111001 | Sı | S2 | S3 | S4 | S5 | S6   | S7     | S8     | S9 | S10 | Sil | SD  | E1     | E2     | E3    | Ε4                                                | point    | poin     | waveform<br>and test method                               | Min.   | Тур.  | Max.   | Unit |

| 25   |               | Max. output<br>voltage 4   | VSLP4    |    |    |    |    |    |      |        |        | 0  |     |     | 25  | 0      | 0      | 0     | 0                                                 | 13       | 14       | SG = -0.4VDC                                              |        | l —   | -1.18  | v    |

| 26   | Sled s        | Feed through               | VSLOF    |    |    |    |    |    |      |        |        |    |     |     |     |        |        | Т     |                                                   | $\top$   | П        | SG=10kHz,200mVp-p,Gain difference between 25 and 20 of SD |        |       | -34    | dB   |

| 27   | Servo         | Kick output<br>voltage l   | VKICKI   |    |    |    |    |    |      |        |        |    |     |     | 22  |        |        | П     |                                                   |          |          | 7.7.                                                      | -0, 75 | -0, 6 | -0, 45 | V    |

| 28   |               | Kick output<br>voltage 2   | VKICK2   |    |    |    |    |    |      |        |        |    |     |     | 23  |        |        | П     | 11                                                |          | Ħ        | <u></u>                                                   | 0, 45  | 0, 6  | 0.75   | V    |

| 29   | ļ             | Spindle servo<br>gain      | GSPO     |    |    |    |    |    | 0    |        |        |    |     |     |     |        |        |       |                                                   | 34       | 39       | SG = 10Hz, 200mVp-p                                       | 14     | 16,5  | 19     | dВ   |

| 30   | Spi           | Max. output<br>voltage'1   | VSPP1    |    |    |    |    |    | 0    |        |        |    |     |     |     | $\top$ |        |       | $\top$                                            | П        | П        | SG = 1.0VDC                                               | 1.78   |       |        | v    |

| 31   | Spindle so    | Max. output<br>voltage 2   | VSPP2    |    |    |    |    |    | 0    |        |        |    |     |     |     |        |        | П     | <del>                                      </del> | $\sqcap$ | $\sqcap$ | SG = 1.0VDC                                               |        |       | -1.78  | V    |

| 32   | Servo         | Max, output<br>voltage 3   | VSPP3    |    |    | -  |    |    | 0    | 0      |        |    |     |     |     |        |        |       | 11                                                | П        |          | SG = 1.0VDC                                               | 1, 13  |       |        | v    |

| 33   |               | Max. output<br>voltage 4   | VSPP4    |    |    |    |    |    | 0    | 0      |        |    |     |     |     | T      |        | T     | 11                                                | $\prod$  | Ħ        | SG = ~1.0VDC                                              |        |       | -1, 13 | v    |

| 34   |               | PLL Reg. output<br>voltage | Vreg     |    |    |    |    |    |      |        |        |    |     |     |     | $\top$ |        |       | 11                                                | Ė        | 31       | DC voltage                                                | 3, 3   | 3, 5  | 3, 85  | v    |

| 35   | PLL           | Self-running<br>frequency  | Fvco     |    |    |    |    |    |      |        |        |    |     |     |     |        | 0      | T     |                                                   |          | 32       | $V_1 = 0 \text{mV}$                                       | 7.4    | 8.6   | 9.7    | MHz  |

| 36   | į.            | Frequency<br>deviation !   | ΔFı      |    |    |    |    |    |      |        |        |    |     |     |     |        |        |       | 11                                                |          |          | Frequency deviation from FVCO, V <sub>1</sub> =148mV      | 7      | 11    | 15     | %    |

| 37   |               | Frequency<br>deviation 2   | ΔFz      |    |    |    |    |    |      |        |        |    |     |     |     |        |        |       |                                                   |          |          | V <sub>1</sub> =-148mV                                    | -15    | -11   | -7     | %    |

| 38   | SENS          | low level                  | VSENS    |    |    |    |    |    |      |        |        |    |     |     |     |        |        |       | П                                                 |          | 18       |                                                           |        |       | -1, 98 | v    |

| 39   | COUT          | low level                  | VCOUT    |    |    |    |    |    |      |        |        |    |     |     |     |        |        | 1     | П                                                 |          | 20       |                                                           |        |       | -1, 98 | v    |

| 40   | FZC value     | threshold                  | VTZC     |    |    |    |    |    |      |        |        |    |     |     | 00  |        | •      | T     | $\prod$                                           | 48       | 18       |                                                           | 39     | 50    | 61     | mV   |

| 41   | ATSC<br>value | threshold                  | Vatsci   |    |    |    |    |    |      |        |        |    |     |     | 10  |        | 0      | T     |                                                   | 47       |          | * Value of E when SENS                                    | -45    | -26   | -7     | mV   |

| 42   | ATSC          | threshold                  | VATSC2   |    |    |    |    |    |      |        |        |    |     |     | 10  |        | $\top$ | Ť     |                                                   | 47       |          | becomes High (=1.1V) by<br>E1 to E4 varying               | 7      | 26    | 45     | мV   |

| 43   | TZC i         | threshold                  | VTZC     |    |    |    |    |    | İ    |        |        |    |     |     | 20  | П      | $\Box$ | •     | 0                                                 | 46       |          | SG = 0V                                                   | -20    | 0     | 20     | mV   |

| 44   | SSTO<br>value | P threshold                | VSSTOP   |    |    |    |    |    |      |        | $\neg$ |    |     |     | 30  | -      | $\top$ | 0     | $\top \top$                                       | 16       |          | - WT                                                      | -65    | -50   | -35    | mV   |

# **Electrical Characteristics Test Circuit**

(See the Pin Configuration for CXA1082BS)

#### **Description of Functions**

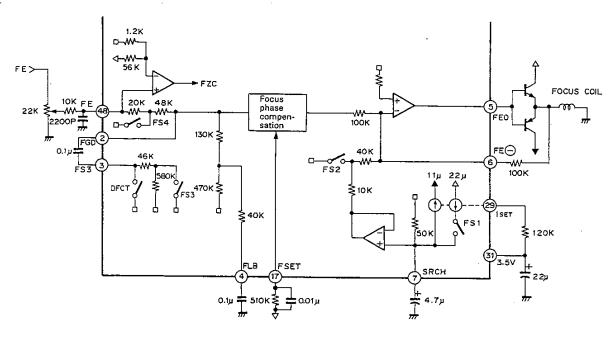

#### Focus servo system

(See the Pin Configuration for CXA1082BS)

The above is a block diagram of the focus servo system.

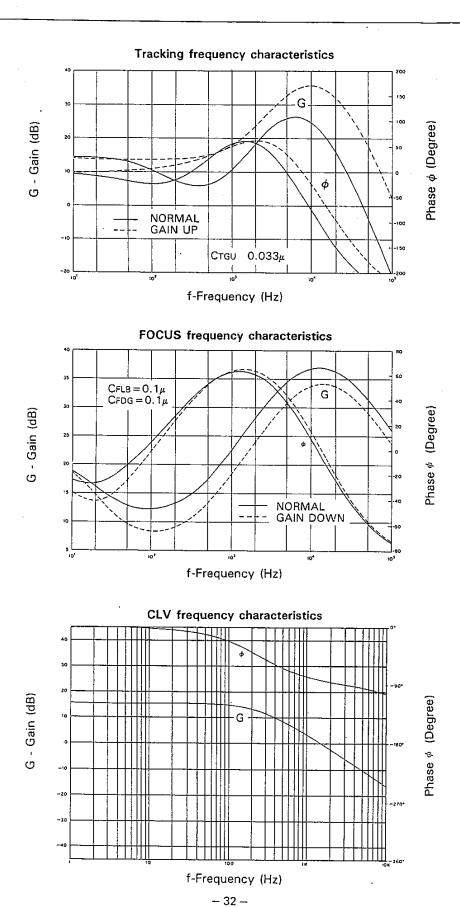

When FS3 is switched on, the high frequency gain can be reduced by forming a low frequency time constant through a capacitor connected across pins 2 and 3 and the internal resistor.

The capacitor across the pin 4 and GND has a time constant to raise the low frequency usually playback condition.

The peak frequency of the focus phase compensation is inversely proportional to the resistor connected to pin 17 (about 1.2 kHz when the resistor is 510 k $\Omega$ ).

The focus search peak becomes about  $\pm 1.1$  Vp-p with the above constant. The peak is inversely proportional to the resistor connected across the pins 29 and 30. However, when this resistor is varied, the peaks of track jump and sled kick also vary.

The FZC comparator invert input is set to 2% of the difference between the reference voltage VCC and VC (pin 1):  $2\% \times (VCC - VC)$ .

**Note**) A resistor of 510 k $\Omega$  is recommended for pin 17.

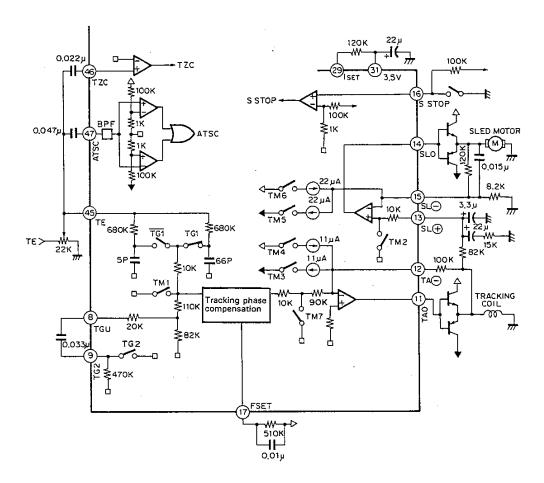

#### Tracking sled servo system

The above is a block diagram of the tracking sled servo system.

The capacitor across pins 8 and 9 has a time constant to lower the high frequency when TG2 is switched off. The tracking phase compensation peak frequency is inversely proportional to the resistor connected to pin 17 (about 1.2 kHz when the resistor is 510 k $\Omega$ ).

For a tracking jump in the FWD or REV direction, TM3 or TM4 are set to ON. At this time, the peak voltage fed to the tracking coil is determined by the TM3 and TM4 current values and the feedback resistor from pin 12. That is:

Track jump peak voltage = TM3 (TM4) current value x feedback resistor value

The FWD or REV sled kick is done by setting TM5 or TM6 to ON. At this time, the peak voltage added

to the sled motor is determined by the TM5 or TM6 current value and the feedback resistor from pin 15.

Sled jump peak voltage = TM5 (TM6) current value x feedback resistor value Each SW current value is determined by the resistor connected to pins 29 and 31. When the resistor is at about 120  $k\Omega$ ,

TM3 or TM4 is  $\pm$  11  $\mu$ A and TM5 or TM6 is  $\pm$  22  $\mu$ A.

This current value is almost inversely proportional to the resistor, variable within a range of about 5 to 40  $\mu$ A for TM3.

S STOP is the ON/OFF detection signal for the limit SW of the sled motor's innermost circumference.

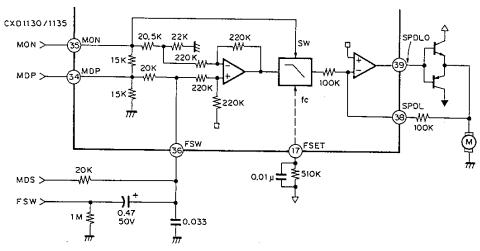

#### Spindle servo and LPF

The 200 Hz LPF is formed with 0.033  $\mu$ F and 20 k $\Omega$  connected to pin 36 and the secondary LPF is formed with the built-in LPF (fc up to 200 Hz with 510 k $\Omega$  for pin 17), and the carrier component of the CLV servo error signals MDS and MDP is eliminated.

In the CLV-S mode, FSW becomes L and the pin 36 LPF fc lowers, strengthening the filter further. With the pin 17 resistor connected to Vcc, fc does not vary with power supply voltage fluctuations. **Note**) Use the phase compensation instead of MDS when the CX23035 is used.

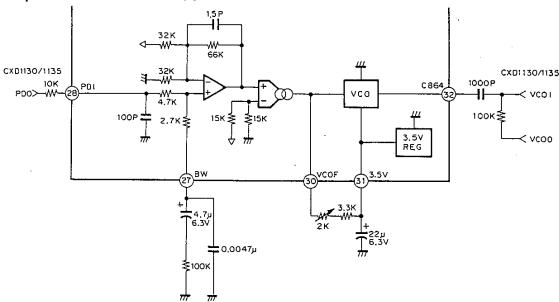

#### VCO loop filter and 8.64 MHz VCO

The phase compensation output PDO input from pin 28 has its PWM carrier component removed in the loop filter. Then, the V-I conversion is made and the free-running frequency setting current from pin 30 is added to control the VCO frequency. The VCO self-running frequency is almost inversely proportional to the resistor across pins 30 and 31. This resistor is set so that the PLL capture range center matches the 4.3218 MHz at pin 70 of the CXD1135/1130.

#### Commands

The input data to activate this IC consists of 8-bits. It shall be represented as \$XX in two hexadecimal digits. (X denotes 0 to F). Instructions for the CXA1082BQ are classified into 8 types — \$0X to 7X.

1. \$0X [SENSE Pin 18 is "FZC"]

This instruction is related to the focus servo control.

The bit configuration is as follows:

| D7 | D6 | D5 | D4 | D3  | D2  | D1  | DO  |

|----|----|----|----|-----|-----|-----|-----|

| 0  | 0  | 0  | 0  | FS4 | FS3 | FS2 | FS1 |

The four switches FS1 to FS4 are related to focusing, and correspond to D0 to D3.

\$00 At FS1 = 0, Pin 7 is charged to  $(22\mu A - 11\mu A) \times 50 \text{ k}\Omega = 0.55 \text{ V}$ ). If FS2 = 0, this voltage is not output and the output of Pin 5 remains 0 V.

\$02 From the above state, FS2 only becomes 1 and a negative output is output to Pin 5. This voltage level is stipulated as follows:

(22 μA

$$-$$

11 μA) x 50 kΩ x Resistance value between Pin 5 and Pin 6 ..... (1)

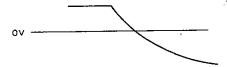

\$03 From the above state, FS1 becomes 1 and the current supply of  $+22 \,\mu\text{A}$  is separated. Then, the CR charge/discharge circuit is formed and Pin 7 voltage decreases as time passes, as shown in Fig. 1.

Fig. 1 Voltage of pin 7 as FS1 changes from 0 to 1

The time constant is formed by 50  $k\Omega$  and an external capacitor.

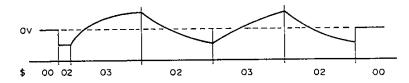

By giving instructions \$02 and \$03 alternately, the focus search voltage is produced (Fig. 2).

Fig. 2 Production of search voltage by \$02 and \$03 (Voltage of Pin 5)

#### 1) Description of FS4

This switch is placed between the focus error input 48 and the focus phase compensation, serving to switch on and off the focus servo.

$$$00 \rightarrow $08$$

Focus off  $\leftarrow$  Focus on

#### 2) Focusing procedure

Assume the polarity as follows:

- a) The lens moves away or toward the disc in searching.

- b) At this time, the output voltage of Pin 5 varies from negative to positive.

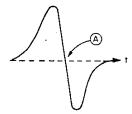

- c) Further, the focus S-curve changes as follows:

Fig. 3 S-curve

The focus servo is activated at the operating point of (A) as shown in Fig. 3. Generally, a logical product (AND) with the Focus-OK signal is used to switch on the focus servo in focus searching and to prevent a malfunction while passing the (A) point in Fig. 3.

This IC is designed so FZC (Focus Zero Cross) is output from the Sense Pin 18 as the A point passing signal.

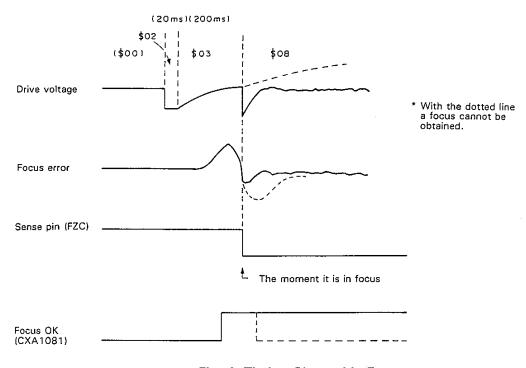

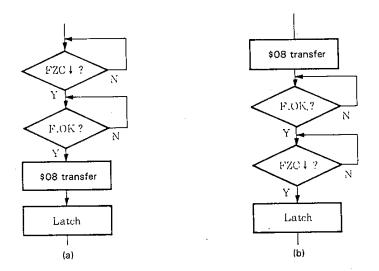

The Focus-OK indicates a signal is in focus (focus is enabled in this case). In summary, the following time chart shows how to obtain the focus.

Fig. 4 Timing Chart of In-Focus

Care should be taken here that \$08 is instructed in the shortest time after FZC changes from H to L.

For this purpose, the (b) sequence required for software is better than (a).

Fig. 5 Bad Sequence and Good Sequence

#### 3) On the Sense Pin 18

What is output to the Sense Pin depends on input data as follows:

FZC is output with \$0X.

AS is output with \$1X.

TZC is output with \$2X.

SSTOP is output with \$3X.

BUSY is output with \$4X.

HIGH-Z is output with \$5X to 7X.

Higher instructions than \$7X are codes for the CXD1135 and several outputs are obtained by connecting to the CXD1135 "SENS" pin.

#### 2. \$1X (SENS Pin 18 is "AS")

This instruction refers to ON/OFF of TG1, TG2 and the break circuit. The bit configuration is as follows:

| D7 | D6 | D5 | D4 | .D3    | D2      | D1  | DO  |

|----|----|----|----|--------|---------|-----|-----|

| 0  | 0  | 0  | 1  | ANTI   | Break   | TG2 | TG1 |

|    |    |    |    | SHOCK  | Circuit |     |     |

|    |    |    |    | ON/OFF | ON/OFF  |     |     |

# TG1, TG2

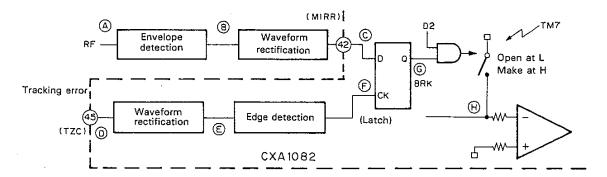

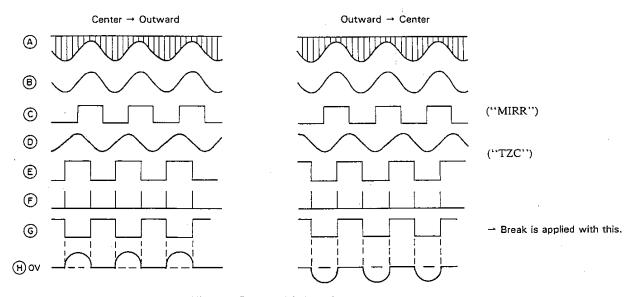

The purpose of these switches is to switch on or off Up/Normal of the tracking servo gain. The break circuit refers to a mechanism which prevents a volatile actuator servo circuit. After jumps of 100 tracks or 10 tracks, the servo circuit is out of the linear range and the actuator often sets tracks wrong. Using a feature that the RF envelope and the tracking error are out of phase by 180° when the actuator crosses the tracks outwardly and vice versa, unwanted tracking errors are cut to break this undesirable jumping.

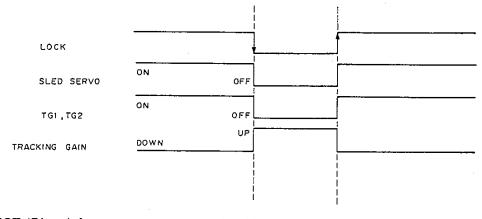

Fig. 6 TM7 Movement (Break Circuit)

Fig. 7 External Waveform

# 3. \$2X (SENS Pin 18 is "TZC")

This instruction refers to ON/OFF of the tracking servo and thread servo as well as generation of the jump pulse and speed feeding pulse in accessing.

| D7 . | D6 | D5 | D4 | D3 D2            | D1 D0           |

|------|----|----|----|------------------|-----------------|

| 0    | 0  | 1  | 0  | Tracking control | Sled control    |

| -    | _  | ·  | •  | 00 off           | 00 off          |

|      |    |    |    | 01 Servo ON      | 01 Servo ON     |

|      |    |    |    | 10 F-JUMP        | 10 F-speed feed |

|      |    |    |    | 11 R-JUMP<br>↓   | 11 R-speed feed |

|      |    |    |    | TM1,TM3,TM4      | TM2,TM5,TM6     |

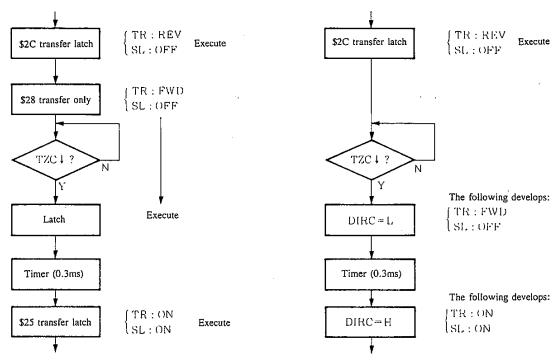

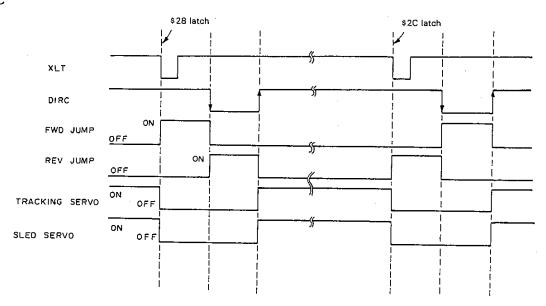

#### DIRC Pin 21 and 1 Track Jump

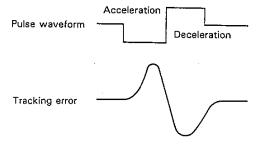

Generally, for a 1-track jump, an acceleration pulse is added and a deceleration pulse is given for a specified time from the moment a tracking error passes the 0 point; then the tracking servo is switched on again. For the 100-track jump to be explained in the next item, as long as the number of tracks is about 100 there is no problem, but the 1-track jump must be exactly, requiring the above complicated procedure. For a 1-track jump of a CD player, both the acceleration and deceleration take about 300 to 400  $\mu$ s. When software is used to execute this operation, it will be as in the flow chart of Fig. 9, but practically it takes time to transfer data.

Fig. 8 Pulse Waveform and Tracking Error of 1-Track Jump

Fig. 9 1-Track Jump without DIRC 21

Fig. 10 1-Track Jump with DIRC 21

For this IC, the "DIRC" (Direct Control) Pin is provided for simple 1-track jumping. For 1-track jump using DIRC, the following is undertaken (DIRC = normal H).

- (a) Acceleration pulse is output. (\$2C for REV or \$28 for FWD).

- (b) With TZC ↓ (or TZC ↑), set DIRC to L. (SENS Pin 18 is "TZC"). As the jump pulse polarity is inverted, deceleration is applied.

- (c) Set DIRC to H for a specific time. Both the tracking servo and sled servo are switched on automatically. As a result, the track jump will be as shown in the flow chart of Fig. 10 and two serial data transfers are saved.

#### 4. \$3X

This command is for switching the Focus search and Sled kick peak value.

DO, D1 ..... Sled, NORMAL feed, high-speed feed

D2, D3 ..... Focus search peak switching

|    | D6 *D5 D4 D3 (PS3)  0 1 1 1 1 1 1 | earch peak | Sled |       |       |       |       |                   |

|----|-----------------------------------|------------|------|-------|-------|-------|-------|-------------------|

| D7 | D6                                | •D5        | D4   | D3    | D2    | D1    | D0    | Relative<br>value |

|    |                                   |            |      | (PS3) | (PS2) | (PSI) | (PS0) | 14140             |

|    |                                   |            |      | 0     | 0     | 0     | 0     | ·± 1              |

| 0  | Λ                                 | 1          | 1    | 0     | 1     | 0     | 1     | ± 2               |

| "  | U                                 | 1          | 1    | 1     | 0     | 1     | 0     | ± 3               |

|    |                                   |            |      | 1     | 1     | 1     | 1     | ± 4               |

#### 5. \$4X to \$7X

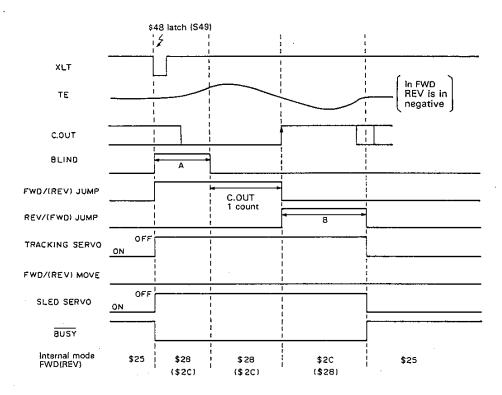

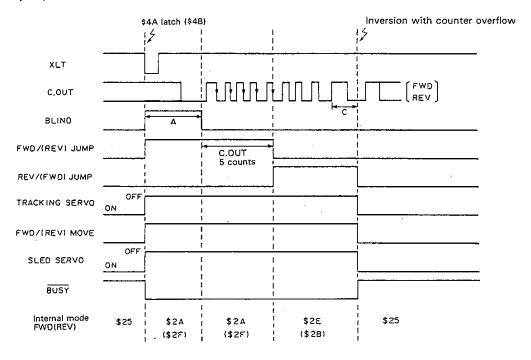

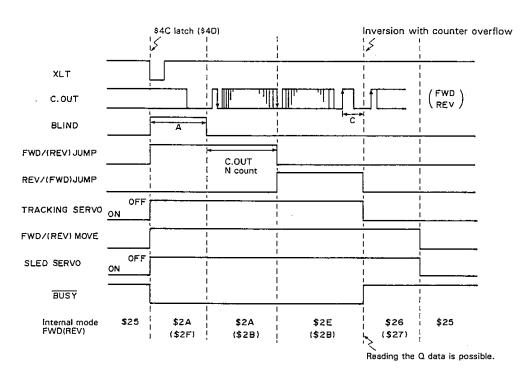

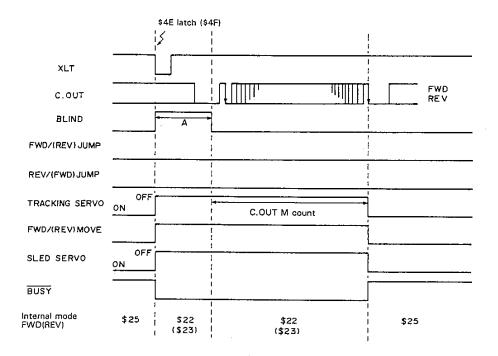

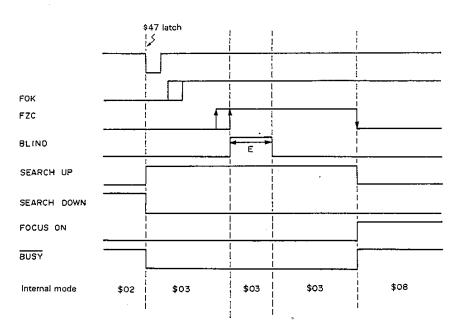

\$4X to \$7X are for the auto sequencer commands. Refer to the table and timing chart for the auto sequencer.

The auto sequencer automates the troublesome routines of focus pull-in and track jump, eliminating any timing control of the microcomputer that is less than 10 ms and combining with the Q register of the CXD1135, CXD1125, CXD1130 and CX23035.

Auto focus

When a focus is pull-in during the  $\overline{BUSY}$  shifts  $H \to L \to H$ , the \$08 is automatically set in the register. Even when it is out of focus, no auto pull-in is done requiring FOK to be monitored.

Track jump

When the  $\overline{BUSY}$  shifts  $H \to L \to H$  and the track jump is completed, the \$25 is automatically set in the register.

Sequencer malfunctions can be relieved with the \$40 anytime.

#### Others

# 1. Connection of the power supply pin

|                            | Vcc  | VEE | VC  |

|----------------------------|------|-----|-----|

| ±5 V dual power supply     | +5V  | -5V | 0V  |

| 5 V single power<br>supply | + 5V | 0V  | VC* |

#### \* CXA1081

#### 2. FSET pin

The FSET pin determines the characteristic of the high frequency phase compensation of Focus, Tracking servo, and cut-off frequency (fc) of CLV LPF.

#### 3. ISET pin

ISET current = 1.27 V/R

= Focus search current (\$30)

= Tracking kick current

= 1/2 sled kick current (\$30)

- 4. In the tracking amplifier, input is clamped at 1 VBE to prevent over input.

- 5. How to change the FE and TE gains

- (1) To increase: Pins 5 and 6, pins 11 and 12 to more than 100 k $\Omega$ .

- (2) To decrease: Divide the FE and TE resistor of input.

- 6. Tracking servo phase

From TE to TAO the phase is negative. (CXA20108 has a positive phase.)

# **Auto Sequencer Timing Chart**

#### 1. 1 track jump

# 2. 10 track jump

# 3. 2N track jump

# 4. M track movement

#### 5. Auto focus

- 6. Notes on use of the auto sequence

- 1) The horizontal axis of the timing chart is not always proportional to the actual time.

- Use the auto focus only while the search is down.

Use the track jump while the focus, tracking, and sled servo are switched on.

- 3) The auto sequencer does not cover tracking gain up, brake, anti-shock, and focus gain down. Separate commands are required.

- 4) BUSY does not tell the full status of the player. Monitor FOK and GFS, etc. using the microcomputer.

- 5) When the sequencer hangs up, detect BUSY's max, excess time using the microcomputer and send \$40 (CANCEL) to reset to the preceding status.

- 6) In all modes the auto sequence starts from the first WDCK falling edge right after XLT falls.

# Parallel Direct Interface

# 1. DIRC

# 2. LOCK (Sled runaway prevention circuit)

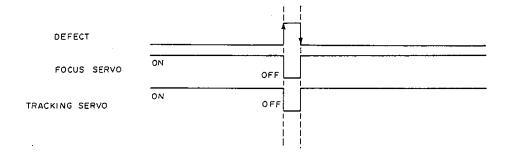

# 3. DEFECT (Disc defect countermeasure circuit)

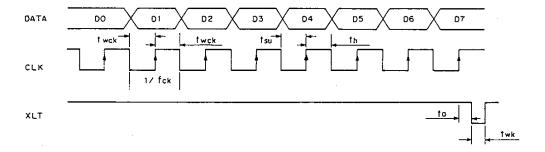

# **CPU Serial Interface Timing Chart**

DVcc - DGND = 4.5 to 5.5V

| Item              | Symbol         | Min. | Тур. | Max. | Unit |

|-------------------|----------------|------|------|------|------|

| Clock frequency   | fck            |      |      | 1    | MHz  |

| Clock pulse width | fwck           | 500  |      |      | ns   |

| Hold time         | tsu            | 500  |      |      | ns   |

| Setup time        | th             | 500  | -    |      | ns   |

| Delay time        | ŧ <sub>D</sub> | 500  |      |      | ns   |

| Latch pulse width | twL            | 1000 |      |      | ns   |

# System Control

|              | Τ,                        | ADDRESS  |            | DA         | TA              |         | SENS   |  |

|--------------|---------------------------|----------|------------|------------|-----------------|---------|--------|--|

|              | Item                      | D7D6D5D4 | D3         | D2         | D1              | D0      | Output |  |

|              |                           |          | FS4        | FS3        | FS2             | FS1     |        |  |

| Focus Co     | ontrol                    | 0000     | Focus      | Gain       | Search          | Search  | FZC    |  |

|              |                           |          | ОИ         | Down       | ON              | Up      |        |  |

| Trooking     | Control                   | 0 0 0 1  | Anti       | Brake      | TG2             | TG1     | A.S    |  |

| Tracking     | Tracking Control          |          | Shock      | ON         | Gain Set *.     | 1       | A.S    |  |

| Tracking     | Mode                      | 0 0 1 0  | Tracking N | lode *2    | Sled Mode       | TZC     |        |  |

|              |                           |          | PS4        | PS3        | PS2             | PS1     |        |  |

| Select       |                           | 0 0 1 1  | Focus      | Focus      | Sled            | Sled    | SSTOP  |  |

|              |                           |          | Search+2   | Search + 1 | Kick+2          | Kick+1  |        |  |

| Auto Seq     | uence *4                  | 0 1 0 0  | AS3        | AS2        | AS1             | AS0     | BUSY   |  |

|              | Blind (A, E)/Overflow (C) | 0 1 0 1  | 0.18ms     | 0.09ms     | 0.045ms 0.022ms |         |        |  |

| *5 Brake (B) |                           | 0 1 0 1  | 0.36ms     | 0.18ms     | 0.09ms          | 0.045ms |        |  |

| RAM          | Kick (D)                  | 0 1 1 0  | 11.6ms     | 5.8ms      | 2.9ms           | 1.45ms  | Hi-2   |  |

| SEI          | Track Jump (N)            | 0 1 1 1  | 64         | 32         | 16              | 8       | ].     |  |

|              | Track Move (M)            | 0 1 1 1  | 128        | 64         | 32              | 16      |        |  |

Note)\*1. GAIN SET

It is possible to set TG1 and TG2 independently.

When the anti-shock is 1 (00011xxx), invert both TG1 and TG2 when the internal anti-shock is H.

#### \* 2 TRACKING MODE

|          | D3 | D2 |

|----------|----|----|

| OFF      | 0  | 0  |

| ON       | 0  | 1  |

| FWD JUMP | 1  | 0  |

| REV JUMP | 1  | 1  |

#### \* 3 SLED MODE

|          | D1 | D0 |

|----------|----|----|

| OFF      | 0  | 0  |

| ОИ       | 0  | 1  |

| FWD MOVE | 1  | 0  |

| REV MOVE | 1  | 1  |

#### \* 4 AUTO SEQUENCE

|               | AS3 | AS2 | ASI | AS0 |

|---------------|-----|-----|-----|-----|

| CANCEL        | 0   | 0   | 0   | 0   |

| FOCUS ON      | 0   | 1   | 1   | 1.  |

| 1 TRACK JUMP  | 1   | 0   | 0   | X   |

| 10 TRACK JUMP | 1   | 0   | 1   | X   |

| 2N TRACK JUMP | 1   | 1   | 0   | X   |

| M TRACK MOVE  | 1   | 1   | I   | X   |

X = 0 FORWARD X = 1 REVERSE

- When CANCEL \$40 is sent, the status immediately preceding the auto sequence mode (just before \$4X is sent) is reset.

- The auto sequence mode starts with the first falling of the pin 40 input pulse (WDCK) after the \$4X transfer and the falling of latch pulse.

# \*5 RAM·SET

- Values \$1 to \$E (not \$0, \$F) can be set.

- The above set values are ones when WDCK (88.2 kHz) is input to pin 40.

- The RAM is preset when the power is switched on and the internal initial set values are as follows:

| ADDRESS | DATA    |

|---------|---------|

| 0 1 0 1 | 0 1 0 1 |

| 0 1 1 0 | 0 1 1 1 |

| 0 1 1 1 | 1110    |

• The actual count values are slightly different from the set values.

A set value + 4 to 5 WDCK

B, D, E set value + 3 WDCK

C set value + 5 WDCK

N, M set value + 3 Count out

SONY CXA1082BQ/BS

# Serial Data Truth Table

| Serial data      | Hexa. | Function        |

|------------------|-------|-----------------|

| FOCUS CONTROL    |       | FS = 4321       |

| 00000000         | \$00  | 0000            |

| 10000000         | \$01  | 0001            |

| 00000010         | \$02  | 0 0 1 0         |

| 00000011         | \$03  | 0011            |

| 00000100         | \$04  | 0100            |

| 0.0000101        | \$05  | 0101            |

| 00000110         | \$06  | 0 1 1 0         |

| 00000111         | \$07  | 0 1 1 1         |

| 00001000         | \$08  | 1000            |

| 00001001         | \$09  | 1 0 0 1         |

| 0 0 0 0 1 0 1 0  | \$0A  | 1010            |

| 0 0 0 0 1 0 1 1  | \$0B  | 1011            |

| 00001100         | \$0C  | 1100            |

| 00001101         | \$0D  | 1 1 0 1         |

| 0 0 0 0 1 1 1 0  | \$0E  | 1 1 1 0         |

| 00001111         | \$0F  | 1 1 1 1         |

| TRACKING CONTROL |       | AS= 0 AS= 1     |

|                  |       | TG= 2 1 TG= 2 1 |

| 00010000         | \$10  | 0 0 0 0         |

| 00010001         | \$11  | 0 1 0 1         |

| 00010010         | \$12  | 1 0 1 0         |

| 00010011         | \$13  | 1 1 1 1         |

| 00010100         | \$14  | 0 0 0 0         |

| 00010101         | \$15  | 0 1 0 1         |

| 00010110         | \$16  | 1 0 1 0         |

| 0 0 0 1 0 1 1 1  | \$17  | 1 1 1 1         |

| 00011000         | \$18  | 0 0 1 1         |

| 00011001         | \$19  | 0 1 1 0         |

| 0 0 0 1 1 0 1 0  | \$1A  | 1 0 0 1         |

| 0 0 0 1 1 0 1 1  | \$1B  | 1 1 0 0         |

| 0 0 0 1 1 1 0 0  | \$1C  | 0 0 1 1         |

| 0 0 0 1 1 1 0 1  | \$ID  | 0 1 1 0         |

| 0 0 0 1 1 1 1 0  | \$1E  | 1 0 0 1         |

| 00011111         | \$1F  | 1 1 0 0         |

| Serial data                | Hexa. | Fun         | ction  |        |

|----------------------------|-------|-------------|--------|--------|

| TRACKING MODE              |       | DIRC=1      | DIRC=0 | DIRC=1 |

| 11010101110111011101110111 | _     | TM = 654321 | 654321 | 654321 |

| 00100000                   | \$20  | 000000      | 001000 | 000011 |

| 00100001                   | \$21  | 000010      | 001010 | 000011 |

| 00100010                   | \$22  | 010000      | 011000 | 100001 |

| 00100011                   | \$23  | 100000      | 101000 | 100001 |

| 00100100                   | \$24  | 000001      | 000100 | 000011 |

| 00100101                   | \$25  | 000011      | 000110 | 000011 |

| 00100110                   | \$26  | 010001      | 010100 | 100001 |

| 00100111                   | \$27  | 100001      | 100100 | 100001 |

| 00101000                   | \$28  | 001000      | 001000 | 000011 |

| 00101001                   | \$29  | 000110      | 001010 | 000011 |

| 00101010                   | \$2A  | 010100      | 011000 | 100001 |

| 00101011                   | \$2B  | 100100      | 101000 | 100001 |

| 00101100                   | \$2C  | 001000      | 000100 | 110000 |

| 00101101                   | \$2D  | 001010      | 000110 | 000011 |

| 00101110                   | \$2E  | 011000      | 010100 | 100001 |

| 00101111                   | \$2F  | 101000      | 100100 | 100001 |

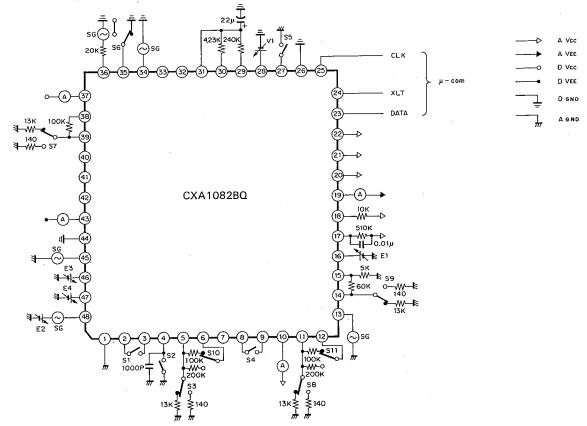

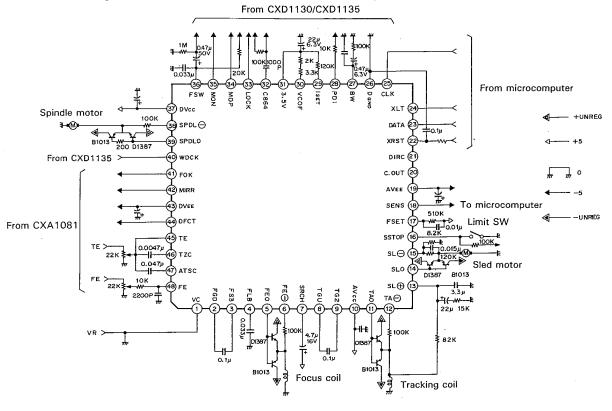

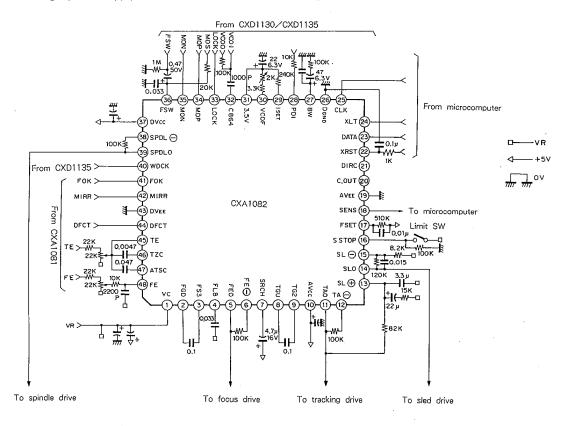

#### **Application Circuit**

1.  $\pm 5$  V dual power supply for CXA1082BQ (48 pin QFP) (See the Pin Configuration for CXA1082BS)

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

# 2. $\pm$ 5 V single power supply for CXA1082BQ (See the Pin Configuration for CXA1082BS)

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

# Internal Phase Compensation Standard Circuit Design Data

|          |                |        |    |    |    | SW 6 | condi | itions | 6  |    |    |     | Bia | s co | ndition | ıs | 2 5 | 모      | Output waveform and description | N4:  | T     |      | Unit |

|----------|----------------|--------|----|----|----|------|-------|--------|----|----|----|-----|-----|------|---------|----|-----|--------|---------------------------------|------|-------|------|------|

| Mode     | Item           | Symbol | SI | S2 | S3 | S4   | S5    | S6     | S7 | S8 | S9 | SD  |     |      |         |    | Ë   | Test   | of test methods                 | Min. | Тур.  | Max. | Onit |

|          | 1. 2 kHz gain  |        | 0  | 0  |    |      |       |        |    |    |    | 08  |     |      |         | 1  | 48  | 5      |                                 |      | 21, 5 |      | dB   |

| Focus    | 1. 2 kHz phase |        | 0  | 0  |    |      |       |        |    |    |    | 08  |     |      |         |    |     |        |                                 |      | . 63  |      | deg  |

| Sus      | 1. 2 kHz gain  |        | 0  | 0  |    |      |       |        |    |    |    | 0C  |     |      |         |    | П   |        |                                 |      | 16    |      | dB   |

|          | 1. 2 kHz phase |        | 0  | 0  |    |      |       |        |    |    |    | 00. |     |      |         |    | П   |        |                                 |      | 63    |      | deg  |

|          | 1. 2 kHz gain  |        |    |    |    | 0    |       |        |    |    |    | 25  |     |      |         |    | 45  | П      |                                 |      | 13    |      | dB   |

| Tracking | 1. 2 kHz phase |        |    |    |    | 0    |       |        |    |    |    | 25  |     |      |         |    | П   |        |                                 |      | -125  |      | deg  |

| king     | 2. 7 kHz gain  |        |    |    |    | 0    |       |        |    |    |    | 25  |     |      |         |    |     |        |                                 |      | 26, 5 |      | dB   |

|          | 2. 7 kHz phase |        |    |    |    | 0    |       |        |    |    |    | 25  |     |      |         |    | Ţ   | $\Box$ |                                 |      | ~130  |      | deg  |

| "        | 100 Hz phase   |        |    |    |    |      |       |        |    |    |    |     |     |      |         |    | 34  | 39     |                                 |      | -30   |      | deg  |

| Spindle  | 2 kHz gain     |        |    |    |    |      |       |        |    |    |    |     |     |      |         |    | П   |        |                                 |      | -3, 5 |      | dB   |

| ē        |                |        |    |    |    |      |       |        |    |    |    |     |     |      |         |    |     | $\Box$ |                                 |      |       |      |      |

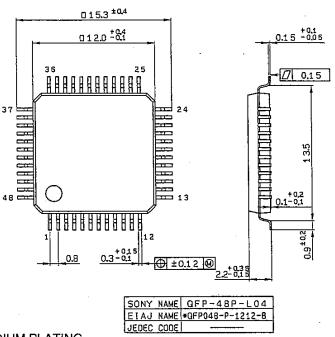

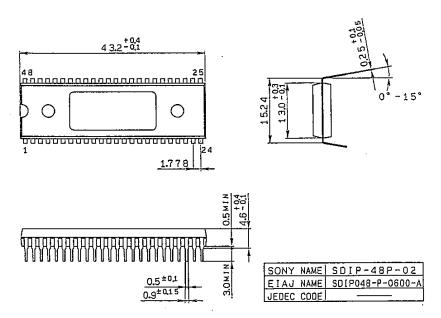

Package Outline

Unit: mm

CXA1082BQ

48pin QFP (Plastic) 0.7g

**NOTE: PALLADIUM PLATING**

This product uses S-PdPPF (Sony Spec.-Palladium Pre-Plated Lead Frame).

**CXA1082BS**

48pin SDIP (Plastic) 600mil 5.1g

**NOTE: PALLADIUM PLATING**

This product uses S-PdPPF (Sony Spec.-Palladium Pre-Plated Lead Frame).