## **CMOS** μP-Compatible 10-Bit Plus Sign ADC

AD7571

#### **FEATURES**

10-Bit Plus Sign Resolution No Missed Codes Over Full Temperature Range Conversion Time 80µs Differential Analog Voltage Inputs, ±10V Range Serial and Parallel Data Outputs Easy Interface to Most Microprocessors Internal Clock Oscillator Single Supply Operation for Positive-Only Signals **Monolithic Construction**

#### GENERAL DESCRIPTION

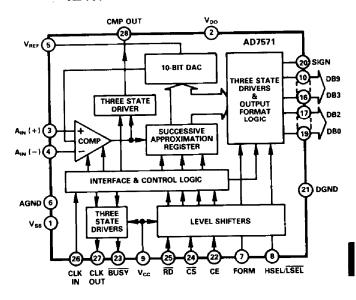

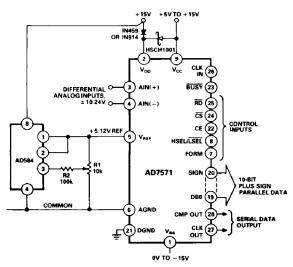

The AD7571 is a high speed, low cost 10-bit plus sign CMOS A/D converter which uses the successive approximation technique to provide a conversion time of 80 µs. The device is designed for easy microprocessor interface allowing full parallel or double byte reading over three-state outputs. Conversion results are also available in serial form allowing opto-isolated operation using as few as two wires for the interconnect.

A new differential analog input configuration is used in the AD7571, increasing the common-mode rejection performance and allowing the analog zero input voltage to be offset from true analog ground. Analog input voltage range is ±10V using a single positive reference. With positive-only input signals the AD7571 can be operated from a single positive power supply.

#### PRODUCT HIGHLIGHTS

- 1. Pin Programmable Data Output Formats The output format for the 10-bits plus sign data is pin programmable allowing full parallel, two byte (left justified) and serial output formats.

- 2. Proven Control Logic The AD7571 control logic is similar to that used in the highly successful AD7574. This allows the AD7571 to be operated as a memory mapped input device interfacing to the  $\mu P$  via the control lines  $\overline{CS}$  (chip select) and  $\overline{RD}$  ( $\overline{READ}/WRITE$ ).

#### AD7571 FUNCTIONAL BLOCK DIAGRAM

3. All Active Components on Chip

The addition of a few passive support components makes the AD7571 a complete 10-bit plus sign converter requiring only a reference voltage and power supply(ies). An on chip clock is also provided but the device can run from an external clock if required.

4. Differential Analog Inputs

The analog input voltage can be unipolar or bipolar with an input range of  $\pm 10V$ . The differential input allows asymmetric input voltage ranges to be easily accommodated.

5. Single Supply Operation

The AD7571 may be operated with a single positive supply if the input signal range is always positive with respect to AGND.

#### PACKAGE IDENTIFICATION

Suffix "N" - Plastic DIP (N28A) Suffix "Q"-Cerdip (Q28A)

Suffix "D" - Ceramic DIP (D28B)

##

| Parameter                                                                                                               | AD7571JN <sup>1</sup>                          | AD7571KN                              | AD7571AQ     | AD7571BQ                                | AD7571SD                                | AD7571 TD       | Units                                | Conditions/Comments                                                   |

|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------------|--------------|-----------------------------------------|-----------------------------------------|-----------------|--------------------------------------|-----------------------------------------------------------------------|

| ACCURACY <sup>2</sup>                                                                                                   |                                                |                                       |              |                                         |                                         |                 |                                      | Conditions/Comments                                                   |

| Resolution                                                                                                              | 10 bits plus sign                              | *                                     |              |                                         |                                         |                 |                                      |                                                                       |

| Relative Accuracy                                                                                                       | ±1                                             | ± 3/4                                 |              | **                                      | *                                       | *               |                                      |                                                                       |

| Zero Input Reading                                                                                                      | ± 000H                                         | *                                     |              | •                                       | *                                       | **              | LSB max                              |                                                                       |

|                                                                                                                         | 2 00011                                        |                                       |              | -                                       | -                                       | •               | Hex                                  | Full Scale Reading is                                                 |

| Roll-Over Error                                                                                                         | ± 2                                            | ± 1                                   | •            | **                                      |                                         | **              |                                      | ± 3FFH                                                                |

|                                                                                                                         |                                                | -1                                    |              |                                         | •                                       | •               | LSB max                              | Difference in reading for equal<br>positive and negative inputs nea   |

| Minimum Resolution for which no                                                                                         |                                                |                                       |              |                                         |                                         |                 |                                      | full scale                                                            |

| Missing Codes are Guaranteed,                                                                                           | 10 bits plus sign                              | *                                     | *            | *                                       |                                         |                 |                                      |                                                                       |

| Full Scale Error (Gain Error)                                                                                           |                                                |                                       |              |                                         |                                         |                 |                                      |                                                                       |

| + 25℃                                                                                                                   | ± 4                                            | ±3                                    | •            | **                                      | •                                       | **              | LSB max                              |                                                                       |

| T <sub>min</sub> to T <sub>max</sub>                                                                                    | ± 5                                            | ±4                                    | *            | **                                      | *                                       | **              | LSB max                              |                                                                       |

| Offset Errors                                                                                                           |                                                |                                       |              |                                         |                                         |                 | Lon mar                              |                                                                       |

| Positive Differential Input                                                                                             | - 3/4; + 2                                     | -3/4; +1                              | •            | **                                      | *                                       | **              | LSB max                              |                                                                       |

| Negative Differential Input                                                                                             | - 3/4; + 2                                     | -3/4; +1                              | *            | **                                      | *                                       | **              | LSB max                              |                                                                       |

| Sign Bit Offset Error<br>+ 25°C                                                                                         |                                                |                                       |              |                                         |                                         |                 |                                      |                                                                       |

| T <sub>min</sub> to T <sub>max</sub>                                                                                    | ±1                                             | ± 1/2                                 | *            | **                                      | *                                       | **              | LSB max                              |                                                                       |

| Offset Error TC                                                                                                         | ±1                                             | ± 1                                   | *            | **                                      | *                                       | **              | LSB max                              |                                                                       |

| Sign Bit Offset TC                                                                                                      | ±5                                             | *                                     | *            | *                                       | *                                       | *               | ppm/°C typ                           |                                                                       |

| Full Scale Error TC                                                                                                     | ±5                                             | *                                     | *            | •                                       | *                                       | *               | ppm/°C typ                           |                                                                       |

|                                                                                                                         |                                                |                                       |              |                                         |                                         |                 | ••                                   |                                                                       |

| (Gain Error TC)                                                                                                         | ±5                                             | *                                     | *            | *                                       | *                                       | *               | ppm/°C typ                           |                                                                       |

| POWER SUPPLY REJECTION                                                                                                  |                                                |                                       |              |                                         |                                         |                 |                                      |                                                                       |

| V <sub>DD</sub> Only                                                                                                    | 1                                              | *                                     | *            | •                                       | *                                       | *               | LSB max                              | 14 35-11 2001                                                         |

| V <sub>SS</sub> Only                                                                                                    | 0.1                                            | •                                     | *            | •                                       | *                                       |                 | LSB max                              | 14.25≤V <sub>DD</sub> ≤15.75V                                         |

| V <sub>DD</sub> and V <sub>SS</sub> Together                                                                            | 1                                              | •                                     | *            |                                         |                                         | *               | LSB max                              | - 15.75≤V <sub>SS</sub> ≤ - 14.25V                                    |

|                                                                                                                         |                                                |                                       |              |                                         |                                         |                 | L36 max                              | Same Limits as Above.  Worst Case Combination.                        |

| ANALOGINPUTS                                                                                                            |                                                |                                       | <del> </del> |                                         |                                         | <del></del>     |                                      | worst Case Combination.                                               |

| Analog Input Range                                                                                                      | ± 10.24                                        | *                                     |              |                                         |                                         |                 |                                      |                                                                       |

| Analog de Input Impedance,                                                                                              |                                                |                                       |              | -                                       |                                         | <del>7</del>    | v                                    | Full Scale with $V_{REF} = +5.12V$                                    |

| $\Lambda_{\text{IN}}(+), \Lambda_{\text{IN}}(-)$                                                                        | 10                                             | *                                     |              |                                         |                                         |                 |                                      |                                                                       |

| Input Common Mode Voltage                                                                                               | ± 10                                           |                                       |              |                                         |                                         | •               | MΩmin                                |                                                                       |

| Common Mode Rejection                                                                                                   | 0.1                                            | *                                     |              |                                         |                                         | *               | V                                    |                                                                       |

| REFERENCE INPUT                                                                                                         |                                                |                                       |              |                                         |                                         |                 | LSB/V typ                            |                                                                       |

| V <sub>REF</sub> (for specified performance)                                                                            | + 5.12                                         |                                       |              |                                         |                                         |                 |                                      |                                                                       |

| V <sub>REF</sub> Range <sup>3</sup>                                                                                     |                                                | *                                     | •            | *                                       | *                                       | *               | V                                    | ±5%                                                                   |

| IREF, Input Reference Current                                                                                           | +1 to +6<br>1.5                                | *                                     | *            | *                                       | *                                       | •               | v                                    | Degraded transfer accuracy                                            |

| LOGICINPUTS                                                                                                             | 1.3                                            | •                                     | *            | *                                       | •                                       | •               | mA max                               | V <sub>REF</sub> = +5.12V                                             |

| FORM (pin 7), HSEL/\overline{LSEL} (pin 8),<br>CE (pin 22), \overline{CS} (pin 24),<br>RD (pin 25)                      |                                                |                                       | •            |                                         |                                         |                 |                                      |                                                                       |

| VII. Input Low Voltage                                                                                                  | + 0.8                                          | *                                     | •            | *                                       | *                                       | *               | V max                                | $V_{OC} = +5V$                                                        |

| 37                                                                                                                      | +1.5                                           | *                                     | *            | *                                       | •                                       | *               | V max                                | $V_{CC} = +15V$                                                       |

| V <sub>IH</sub> Input High Voltage                                                                                      | + 2.4                                          | •                                     | *            | *                                       | *                                       | *               | V min                                | $V_{OC} = +5V$                                                        |

| I I                                                                                                                     | + 13.5                                         | •                                     | *            | *                                       | *                                       | *               | V min                                | $V_{OC} = +15V$                                                       |

| I <sub>DN</sub> Input Current + 25°C                                                                                    | 1                                              | *                                     | *            | •                                       | *                                       | *               | μA max                               | V <sub>IN</sub> = 0V or V <sub>CC</sub>                               |

| T <sub>min</sub> to T <sub>max</sub> C <sub>in</sub> Input Capacitance <sup>4</sup>                                     | 10                                             | *                                     | •            | •                                       | *                                       | *               | μA max                               | V <sub>IN</sub> = 0V or V <sub>CC</sub>                               |

| C <sub>in</sub> Input Capacitance <sup>4</sup><br>CLK IN (Pin 26)                                                       | 8                                              | •                                     | *            | •                                       | *                                       | *               | pF max                               | THE STATE OF                                                          |

|                                                                                                                         |                                                |                                       |              |                                         |                                         |                 | •                                    |                                                                       |

| V <sub>II.</sub> Input Low Voltage                                                                                      | +1.5                                           | *                                     | *            | •                                       | * ,                                     | •               | V max                                |                                                                       |

| V <sub>IH</sub> Input High Voltage                                                                                      | +13.5                                          | *                                     | •            | *                                       | •                                       | *               | V min                                | •                                                                     |

| I <sub>IL</sub> Input Low Current<br>I <sub>IH</sub> Input High Current                                                 | 10                                             | *                                     | *            | *                                       | •                                       | *               | μA max                               |                                                                       |

|                                                                                                                         | 3                                              | *                                     | *            | *                                       | *                                       | *               | mA max                               |                                                                       |

| OGIC OUTPUTS                                                                                                            |                                                |                                       |              |                                         |                                         |                 |                                      |                                                                       |

| DB9 to DB0 (pins 10-19),<br>SIGN (pin 20), BUSY (pin 23),<br>CLK OUT (pin 27), CMPOUT (pin 28)                          |                                                |                                       |              |                                         |                                         |                 |                                      |                                                                       |

| V <sub>OH</sub> Output High Voltage                                                                                     |                                                | _                                     | _            |                                         |                                         |                 |                                      |                                                                       |

| VOH Output riigh voitage                                                                                                | + 4.0                                          | •                                     | •            | *                                       | *                                       | *               | V min                                | $V_{CC} = +5V, I_{SOURCE} = 40\mu A$                                  |

| Vo. Output Law Values                                                                                                   | + 13.5                                         | •                                     | *            | *                                       | •                                       | *               | V min                                | $V_{CC} = +15V, I_{SOURCE} = 100\mu A$                                |

| Vol. Output Low Voltage                                                                                                 | + 0.4                                          | *                                     | *            | *                                       | *                                       | *               | V max                                | $V_{\rm OC} = +5V, I_{\rm SINK} = 1.6 \text{mA}$                      |

| Floating State Leakage Current                                                                                          | +1.5                                           | •                                     | •            | *                                       | *                                       | *               | V max                                | $V_{CC} = +15V, I_{SINK} = 2mA$                                       |

| (DB9-DB0, BUSY, CLK OUT.                                                                                                | ± 10                                           | *                                     | *            | *                                       | *                                       | *               | μ.A max                              | , , , , , , , , , , , , , , , , , , , ,                               |

| CMPOUT)                                                                                                                 |                                                |                                       |              |                                         |                                         |                 |                                      |                                                                       |

| Floating State Output Capacitance                                                                                       | -                                              |                                       |              |                                         |                                         |                 |                                      |                                                                       |

|                                                                                                                         | 7                                              | •                                     |              | •                                       | *                                       | *               | pF max                               |                                                                       |

| OWER REQUIREMENTS                                                                                                       |                                                |                                       |              |                                         |                                         |                 |                                      |                                                                       |

|                                                                                                                         | + 11.4 to + 16.5                               | *                                     | *            | •                                       |                                         |                 | v                                    |                                                                       |

| $V_{DD}$                                                                                                                | 11 41- 16 6                                    | •                                     | *            | *                                       | *                                       |                 | v.                                   | •                                                                     |

| V <sub>DD</sub><br>V <sub>SS</sub>                                                                                      | – 11.4 to – 16.5                               |                                       |              | •                                       | *                                       |                 | V                                    |                                                                       |

| V <sub>DD</sub><br>V <sub>SS</sub><br>V <sub>CC</sub>                                                                   |                                                | *                                     |              |                                         |                                         |                 | ٧                                    |                                                                       |

| V <sub>DD</sub><br>V <sub>SS</sub><br>V <sub>CC</sub>                                                                   | +4.5 to V <sub>DD</sub>                        | •                                     | •            | *                                       | *                                       |                 |                                      |                                                                       |

| V <sub>DD</sub><br>V <sub>SS</sub><br>V <sub>CC</sub><br>I <sub>DD</sub> + 25°C                                         | + 4.5 to V <sub>DD</sub><br>7.5                | *<br>•                                | •            | •                                       | •                                       | :               | mA max                               |                                                                       |

| V <sub>DD</sub><br>V <sub>SS</sub><br>V <sub>CC</sub><br>I <sub>DD</sub> + 25°C<br>T <sub>min</sub> to T <sub>max</sub> | +4.5 to V <sub>DD</sub><br>7.5<br>9.75         | * * *                                 | •            | *                                       | •                                       | :               | mA max                               |                                                                       |

| V <sub>DD</sub><br>V <sub>SS</sub><br>V <sub>CC</sub><br>I <sub>DD</sub> + 25°C<br>T <sub>min</sub> to T <sub>max</sub> | +4.5 to V <sub>DD</sub> 7.5 9.75 5.0           | * * * *                               | *            | :                                       | :                                       | *               | mA max<br>mA typ                     |                                                                       |

| VDD Vss VCC IDD +25°C T min to T max T min to T max                                                                     | +4.5 to V <sub>DD</sub><br>7.5<br>9.75         | * * * * *                             | * * *        | *                                       | * * *                                   | :               | mA max<br>mA typ<br>μΑ typ           |                                                                       |

| VDD Vss Vcc IDD + 25°C Tmin to Tman Tmin to Town Iss Loc                                                                | +4.5 to V <sub>DD</sub> 7.5 9.75 5.0 10 50     | #<br>#<br>#<br>#                      | *            | * * * * * * * * * * * * * * * * * * * * | *                                       | * * *           | mA max<br>mA typ<br>μA typ<br>μΑ typ | V -0V-v                                                               |

| VDD<br>Vss<br>VCC<br>IDD + 25°C<br>Tunin to Tunan<br>Tmin to Town                                                       | +4.5 to V <sub>DD</sub> 7.5 9.75 5.0 10 50 200 | # # # # # # # # # # # # # # # # # # # | *            | * * * * * * * * * * * * * * * * * * * * | *                                       | * * * * *       | mA max<br>mA typ<br>μΑ typ           | V <sub>IN</sub> = 0V or V <sub>CC</sub>                               |

| VDD<br>Vss<br>VCC<br>IDD + 25°C<br>T <sub>min</sub> to T <sub>max</sub><br>T <sub>min</sub> to T <sub>oux</sub>         | +4.5 to V <sub>DD</sub> 7.5 9.75 5.0 10 50     | # # # # # # # # # # # # # # # # # # # | *            | * * * * * *                             | * * * * * * * * * * * * * * * * * * * * | * * * * * * * * | mA max<br>mA typ<br>μA typ<br>μΑ typ | $V_{DN} = 0V \text{ or } V_{CC}$ $V_{DN} = V_{IL} \text{ or } V_{IH}$ |

<sup>3</sup>Typical value, not guaranteed or subject to test Guaranteed but not tested. \*Specifications same as AD7571 JN. \*Specifications same as AD7571 KN. Specifications subject to change without notion.

VOL. I, 10-140 ANALOG-TO-DIGITAL CONVERTERS

NOTES

Temperature Range as follows: AD7571JN, KN; 0 to + 70°C

AD7571AQ, BQ; - 22°C to + 85°C

AD7571AD, TD; - 55°C to + 125°C

The analog input voltage at either AIN + or AIN - must not saccood the V<sub>DD</sub> or V<sub>B</sub> supply voltages. However, with saccood the V<sub>DD</sub> or V<sub>B</sub> supply voltages. However, with only positive analog input signels, the AD7571 any be operated with V<sub>BB</sub> = 0°V. All relevant specifications in the above table will apply in this unipolar configuration.

# **SPECIFICATIONS** ( $V_{00} = +15V$ , $V_{ss} = -15V$ , $V_{cc} = +5V$ , $f_{cl.x} = 550$ kHz. External unless otherwise noted)

| arameter                                 |                                                                                                                                                   | Limit at + 25°C<br>(All Grades)                                                                                             | Limit at<br>T <sub>min</sub> , T <sub>max</sub><br>(J, K, A & B Grades) | Limit at<br>T <sub>min</sub> , T <sub>max</sub><br>(S & T Grades) | Units                      | Conditions/<br>Comments                      |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------------|----------------------------------------------|

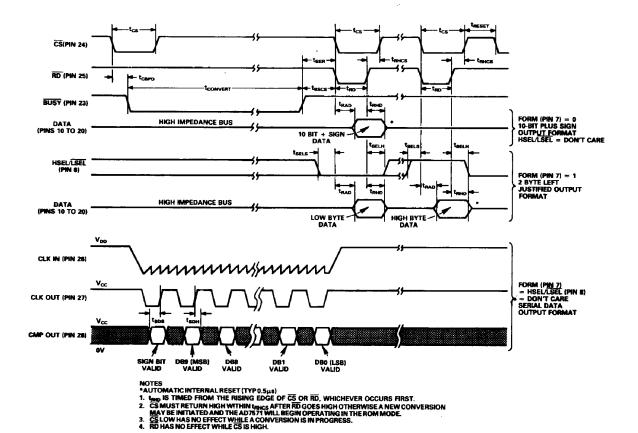

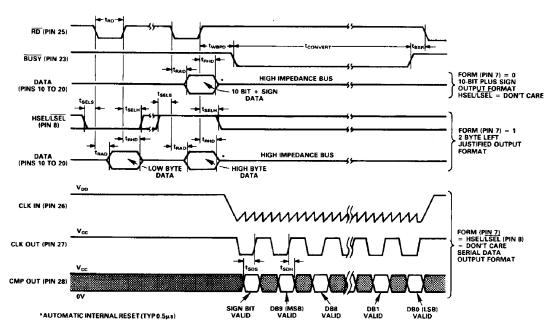

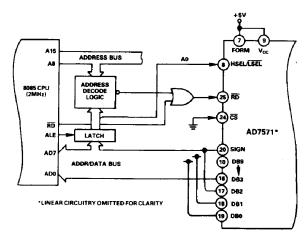

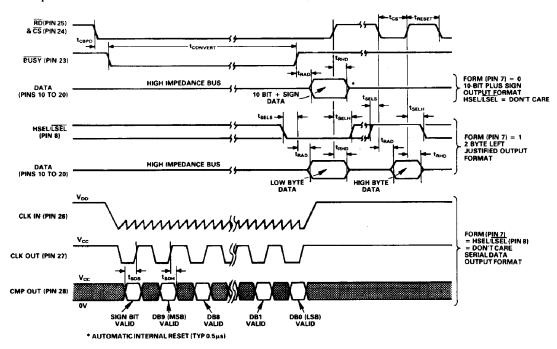

|                                          | MINTERFACE MODE                                                                                                                                   | (See Figure 5)                                                                                                              |                                                                         |                                                                   |                            |                                              |

| CS<br>BSR                                | CS Pulse Width Requirement BUSY to RD Setup Time BUSY to CS Setup Time                                                                            | 100<br>0<br>0                                                                                                               | 130<br>0<br>0                                                           | 150<br>U<br>O                                                     | ns min<br>ns min<br>ns min | Start Conversion Only                        |

| SSCS<br>SELS<br>RD                       | HSEL/LSEL to RD Setup Time RD Pulse Width                                                                                                         | 0<br>ERAD                                                                                                                   | 0<br>trad                                                               | 0<br><sup>t</sup> RAD                                             | ns mín<br>ns min           | <sup>t</sup> RD <sup>≥t</sup> RAD            |

| BPD                                      | CS to BUSY Propagation Delay                                                                                                                      | 150<br>210                                                                                                                  | 190<br>250                                                              | 220<br>300                                                        | ns typ<br>ns max           | BUSY Load = 20pF                             |

|                                          |                                                                                                                                                   | 175<br>240                                                                                                                  | 220<br>300                                                              | 250<br>340                                                        | ns typ<br>ns max           | BUSY Load = 100pF                            |

| IAD                                      | Data Access Time                                                                                                                                  | 300<br>430                                                                                                                  | 360<br>510                                                              | 390<br>550                                                        | ns typ<br>ns max           | Bus Load = 20pF                              |

|                                          |                                                                                                                                                   | 460<br>680                                                                                                                  | 540<br>800<br>330                                                       | 600<br>900<br>360                                                 | ns typ<br>ns max<br>ns typ | Bus Load = 100pF                             |

| RHD                                      | Data Hold Time                                                                                                                                    | 300<br>200<br>400                                                                                                           | 220<br>450                                                              | 260<br>480                                                        | ns min<br>ns max           |                                              |

| RHCS<br>SELH<br>RESET                    | CS to RD Hold Time HSEL/LSEL to RD Hold Time Reset Time Requirement                                                                               | 200<br>0<br>0.5                                                                                                             | 350<br>0<br>0.6                                                         | 500<br>0<br>· 0.8                                                 | ns max<br>ns min<br>µs min |                                              |

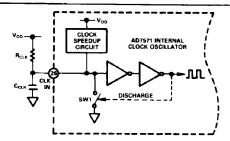

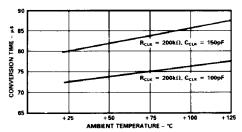

| CONVERT                                  | Conversion Time Using Internal Clock Oscillator Conversion Time Using External Clock                                                              | See Typical Data of Fig<br>80                                                                                               | ure 14.<br>80                                                           | 80                                                                | he wax                     | f <sub>CLK</sub> = 550kHz<br>See Figure 15.  |

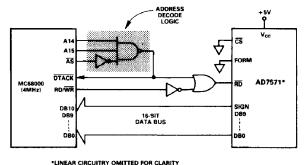

|                                          | RFACE MODE                                                                                                                                        | (See Figure 8.)                                                                                                             | <u> </u>                                                                |                                                                   |                            |                                              |

| RD<br>SELS<br>SELH<br>RAD<br>RHD<br>WBPD | RD Pulse Width Requirement HSEL/LSEL to RD Setup Time HSEL/LSEL to RD Hold Time Data Access Time Data Hold Time RD High to BUSY Propagation Delay | Same as t <sub>RD</sub> in RAM m<br>Same as RAM mode.<br>Same as RAM mode.<br>Same as RAM mode.<br>Same as RAM mode.<br>0.5 | 0.7<br>1.0                                                              | 0.8<br>1.4                                                        | μs typ<br>μs max           | BUSY Load = 20pF                             |

| CONVERT                                  | Conversion Time Using Internal<br>Clock Oscillator                                                                                                |                                                                                                                             | Data Shown in Figure 14.                                                |                                                                   |                            |                                              |

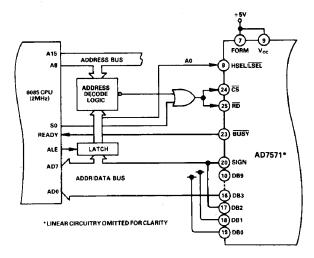

| LOW-ME.                                  | MORY INTERFACE MODE                                                                                                                               | (See Figure 11).                                                                                                            |                                                                         |                                                                   |                            |                                              |

| CBPD<br>RAD                              | CS to BUSY Propagation Delay<br>Data Access Time                                                                                                  | Same as RAM mode.<br>40<br>70                                                                                               | 60<br>100                                                               | 70<br>120                                                         | ns typ<br>ns max           | Bus Load = 20pF                              |

|                                          | D HALLTime                                                                                                                                        | 180<br>300<br>Same as RAM mode.                                                                                             | 230<br>370                                                              | 280<br>420                                                        | ns typ<br>ns max           | Bus Load = 100pF                             |

| RHD<br>SELS<br>SELH<br>RESET             | Data Hold Time  HSEL/LSEL to RD Setup Time  HSEL/LSEL to RD Hold Time  Reset Time Requirement                                                     | Same as RAM mode.<br>Same as RAM mode.<br>Same as RAM mode.                                                                 |                                                                         |                                                                   |                            |                                              |

| ONVERT                                   |                                                                                                                                                   | Same as RAM mode.                                                                                                           | L. L. Firmer Cond l                                                     | 1)                                                                |                            | ·                                            |

| SERIAL DA                                | ATA OUTPUT  CE to Low Impedance Outputs                                                                                                           | (Applies to all 1 hree M                                                                                                    | lodes, see Figures 5, 8 and 1<br>100                                    | 120                                                               | ns max                     | Low Impedance<br>to DGND or V <sub>CC</sub>  |

| СЕН                                      | (BUSY, CLK OUT, CMP OUT) CE to High Impedance Outputs (BUSY, CLK OUT, CMP OUT)                                                                    | 60                                                                                                                          | 100                                                                     | 120                                                               | ns max                     | High Impedance<br>to DGND or V <sub>CC</sub> |

| CBPD                                     | CS to BUSY Propagation Delay RD HIGH to BUSY Propagation Delay                                                                                    | Same as RAM mode.<br>Same as ROM mode.                                                                                      |                                                                         |                                                                   |                            |                                              |

| t SDS                                    | Serial Data to CLK OUT Setup Time<br>Serial Data to CLK OUT Hold Time                                                                             | 20<br>500                                                                                                                   | 20<br>500                                                               | 20<br>500                                                         | ns min<br>ns min           |                                              |

NOTE All specified control signals are measured with  $t_{\rm t}=t_{\rm f}=20$ ns (10% to 90%) for  $\sim$  5V logic and timed from a voltage level of + 1.6V. Data is timed from  $V_{\rm DH}, V_{\rm IL}$  or  $V_{\rm OH}, V_{\rm OL}$ . Sample tested at + 25°C to ensure conformance.

Specifications subject to change without notice.

#### ABSOLUTE MAXIMUM RATINGS\*

| $(T_A = +25^{\circ}C \text{ unless otherwise noted})$      |

|------------------------------------------------------------|

| $V_{DD}$ to AGND                                           |

| $V_{DD}$ to DGND                                           |

| $V_{CC}$ to DGND 0V, $V_{DD}$ +0.4                         |

| $V_{SS}$ to AGND                                           |

| $V_{SS}$ to DGND                                           |

| AGND to DGND $-0.3V$ , $V_{DD}$                            |

| Digital Input Voltage to DGND                              |

| (pins 7, 8, 22, 24, 25) $-0.3V$ , $V_{CC}$                 |

| CLK IN Input Voltage (pin 26) to DGND0.3V, V <sub>DD</sub> |

| Digital Output Voltage to DGND                             |

| (pins 10-20, 23, 27, 28) $-0.3V$ , $V_{CC}$                |

| $V_{REF}$ to AGND0.3V, $V_{DD}$                            |

| AIN (+), AIN (-) to AGND $V_{SS}$ , $V_{DD}$               |

| Opera | ting Te | mperature | Range |

|-------|---------|-----------|-------|

| T . T | *** * * |           |       |

| JN, NN                                       |

|----------------------------------------------|

| AQ, BQ $\dots$ -25°C to +85°C                |

| SD, TD55°C to +125°C                         |

| Storage Temperature +65°C to +150°C          |

| Lead Temperature (Soldering, 10secs) + 300°C |

| Power Dissipation (Any Package)              |

| To +75°C                                     |

| Derates above +75°C 10mW/°C                  |

\*Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note:  $V_{CC}$  should never exceed  $V_{\rm DD}$  by more than 0.4V, especially during power ON or OFF sequencing. See diode protection in Figure 16.

#### **CAUTION**

ESD (Electro-Static-Discharge) sensitive device. The digital control inputs are zener protected; however, permanent damage may occur on unconnected devices subject to high energy electrostatic fields. Unused devices must be stored in conductive foam or shunts. The protective foam should be discharged to the destination socket before devices are removed.

#### PIN CONFIGURATION

## TERMINOLOGY AND DEFINITIONS LEAST SIGNIFICANT BIT (LSB)

An ADC with 10-bits plus sign resolution can resolve 1 part in  $2^{10}$  of either positive or negative full scale. For the AD7571 with  $\pm 10.24V$  full scale one LSB is 10.0 mV.

#### **RELATIVE ACCURACY**

Relative accuracy is the deviation of the ADC's actual code transition points from a straight line drawn between the device's measured first LSB transition point and the measured full scale transition point. For the purpose of specifying the relative accuracy of a 10-bit plus sign ADC, the AD7571 is treated as two separate unipolar ADCs with the transfer characteristics for both positive and negative differential inputs measured independently.

## DIFFERENTIAL NONLINEARITY (NO MISSING CODES)

A specification which guarantees no missing codes requires that every code combination appear in a monotonic increasing sequence as the analog input level is increased. Thus every code must have a non-zero width. Since all grades of the AD7571 guarantee no missing codes to 10-bits plus sign resolution, all 1024 codes plus sign bit (i.e., total of 2048 codes) must be present over the entire operating temperature ranges.

#### **OFFSET ERRORS**

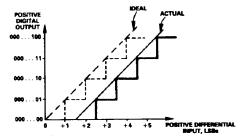

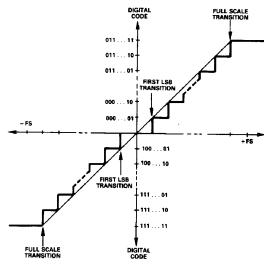

Positive Differential Inputs: A measure of the difference between the ideal (+1LSB) and the actual differential analog input level required to produce the first positive LSB code transition (000 . . . 00 to 000 . . . 01), see Figure 1.

Negative Differential Inputs: A measure of the difference between the ideal (-1LSB) and the actual differential input level required to produce the first negative LSB code transition (100 . . . 00 to 100 . . . 01).

#### ORDERING INFORMATION

|                                                           | Temperature Range and Package |                                              |                                               |  |  |  |  |  |

|-----------------------------------------------------------|-------------------------------|----------------------------------------------|-----------------------------------------------|--|--|--|--|--|

| Relative Accuracy (T <sub>min</sub> to T <sub>max</sub> ) | Plastic (N28A)<br>0 to +70°C  | Cerdip <sup>1</sup> (Q28A)<br>-25°C to +85°C | Side-Brazed Ceramic (D28B)<br>-55°C to +125°C |  |  |  |  |  |

| ± 1LSB                                                    | AD7571JN                      | AD7571AQ                                     | AD7571SD                                      |  |  |  |  |  |

| ± 1/2LSB                                                  | AD7571KN                      | AD7571BQ                                     | AD7571TD                                      |  |  |  |  |  |

NOTES

<sup>1</sup>Analog Devices reserves the right to ship ceramic packages in lieu of cerdip packages. See Section 19 for package outline information.

VOL. I, 10-142 ANALOG-TO-DIGITAL CONVERTERS

Figure 1. ADC Transfer Characteristics for Positive Differential Input with Offset Error of  $\pm 1$  1/2 LSBs

#### SIGN BIT OFFSET ERROR

Ideally occurring at 0V input, the sign bit transition may shift by up to  $\pm 1/2$ LSB for the AD7571 K/B/T grades and by  $\pm 1$ LSB for J/A/S grades. However, since all grades of the AD7571 are guaranteed to have no missed codes over their entire temperature ranges, the sign bit transition will always occur before the first LSB transitions occur.

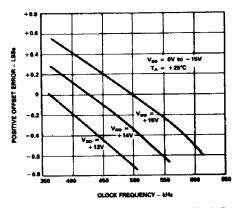

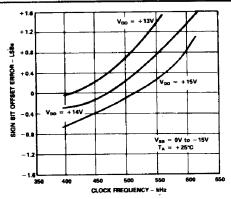

The magnitude and polarity of offset errors depends on the clock frequency and  $V_{\rm DD}$  power supply used to operate the AD7571. See Figure 2 and Figure 3.

Figure 2. Typical Positive Offset Error vs. Clock Frequency for Different Supply Voltages

#### **FULL SCALE ERROR (GAIN ERROR)**

The gain of a unipolar ADC is defined as the difference between the analog input levels required to produce the first and the last

Figure 3. Typical Sign Bit Offset Error vs. Clock Frequency for Different Supply Voltages

digital output code transitions. Gain error is a measure of the deviation of the actual span from the ideal span of FS-2LSBs. In the AD7571 both positive and negative differential input ADC transfer characteristics exhibit the same magnitude and direction of gain error. This correspondence also extends to the gain error drift performance over temperature.

#### ZERO INPUT READING

Digital output which results when AIN (+) = AIN (-).

#### **ROLL-OVER ERROR**

This is the difference in digital output, i.e., reading, for equal positive and negative inputs near full scale.

#### **POWER SUPPLY REJECTION**

A measure of the maximum change in the full scale range of the AD7571 resulting from a change in supply voltage.

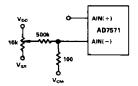

#### INPUT COMMON MODE VOLTAGE

For the AD7571, the voltage at both inputs can be raised above (or lowered below) analog ground potential. The common mode voltage represents the voltage range over which this is allowed. However, the maximum possible differential input signal range will be directly affected by this common mode voltage signal. Table I shows the analog input signal range with a common mode voltage of +6V.

Note that the supply voltage  $V_{SS}$  must be at least as negative as the most negative analog input applied to the AD7571.

| AIN (+),                                      | AIN (-),                         | Differential                                    | Output Code           |                       |                  |                  |                  |                       |                       |                       |                  |                       |                       |

|-----------------------------------------------|----------------------------------|-------------------------------------------------|-----------------------|-----------------------|------------------|------------------|------------------|-----------------------|-----------------------|-----------------------|------------------|-----------------------|-----------------------|

| Volts                                         | Volts "                          | Input, Volts                                    | Sign                  | DB9                   | DB8              | DB7              | DB6              | DB5                   | DB4                   | DB3                   | DB2              | DB1                   | DB0                   |

| +6<br>+6.01<br>+10.24<br>+5.99<br>-4.24<br>+6 | +6<br>+6<br>+6<br>+6<br>+6<br>+6 | 0<br>+0.01<br>+4.24<br>-0.01<br>-10.24<br>-0.01 | 0<br>0<br>0<br>1<br>1 | 0<br>0<br>0<br>0<br>1 | 0<br>0<br>1<br>0 | 0<br>0<br>1<br>0 | 0<br>0<br>0<br>0 | 0<br>0<br>1<br>0<br>1 | 0<br>0<br>0<br>0<br>1 | 0<br>0<br>1<br>0<br>1 | 0<br>0<br>0<br>1 | 0<br>0<br>0<br>1<br>0 | 0<br>1<br>0<br>1<br>1 |

| +6<br>+6<br>+6                                | +10.24<br>+5.99<br>-4.24         | -4.24<br>+0.01<br>+10.24                        | 1<br>0<br>0           | 0<br>0<br>1           | 1<br>0<br>1      | 1<br>0<br>1      | 0<br>0<br>1      | 1<br>0<br>1           | 0<br>0<br>1           | 1<br>0<br>1           | 0<br>0<br>1      | 0<br>0<br>1           | 0<br>1<br>1           |

Table I. Realizable Output Codes vs. Analog Inputs with a Common Mode Voltage of + 6V. Note that All Error Sources are Assumed to be Zero and  $V_{REF} = +5.12V$ .

#### ANALOG INPUT RANGE

With  $V_{REF} = \pm 5.12V$  the maximum analog input voltage range is  $\pm 10.24V$ . The digital output data is related to the reference and differential input voltages by the following expression:

$$DATA = \frac{AIN(+) - AIN(-)}{2V_{REF}} \times 1024$$

The sign of this data is determined by the sign of AIN (+) – AIN (-).

The negative supply  $(V_{SS})$  must be equal to or more negative than the most negative analog input signal applied to AIN+ or AIN- (pins 3 and 4).

#### **BIPOLAR TRANSFER CHARACTERSTIC**

The ideal composite transfer characteristic for the AD7571 is shown in Figure 4. The sign bit transition which ideally occurs at 0V analog input is not shown for ease of illustration.

The first LSB transition points are mirror images of each other. The effect of non-zero offset errors is to either broaden or narrow the zero code widths. The effect of non-zero Gain Error is to pivot the composite transfer characteristic around the 0V origin.

Figure 4. Composite AD7571 Transfer Characteristic

| PIN   | MNEMONIC           | DESCR                                                                                                                                                                                                                                                                                                                             | IPTION                                                                                                                                                           | · · · ·                                                                                                      |                                                                                                                                     |  |  |  |  |  |

|-------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1     | V <sub>ss</sub>    | Negative supply 0V to $-15$ V. V <sub>SS</sub> must be equal to or more negative than the most negative analog input voltage. With positive only input signals AD7571 may be operated with V <sub>SS</sub> = 0V.                                                                                                                  |                                                                                                                                                                  |                                                                                                              |                                                                                                                                     |  |  |  |  |  |

| 2     | Vpp                | 1                                                                                                                                                                                                                                                                                                                                 | Positive supply, +15V.                                                                                                                                           |                                                                                                              |                                                                                                                                     |  |  |  |  |  |

| 3     | AIN+               |                                                                                                                                                                                                                                                                                                                                   | Positive differential input.                                                                                                                                     |                                                                                                              |                                                                                                                                     |  |  |  |  |  |

| 5     | AIN -              |                                                                                                                                                                                                                                                                                                                                   | e differential inpu                                                                                                                                              |                                                                                                              |                                                                                                                                     |  |  |  |  |  |

| ,     | V <sub>REF</sub>   | Voltage                                                                                                                                                                                                                                                                                                                           | reference input.                                                                                                                                                 | The AD7571 is specified v                                                                                    | with $V_{REF} = +5.12V$ .                                                                                                           |  |  |  |  |  |

| 6     | AGND               | Analog                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                  |                                                                                                              |                                                                                                                                     |  |  |  |  |  |

| 7 8   | FORM<br>HSEL/LSET. | 1                                                                                                                                                                                                                                                                                                                                 | Data format select. See pin 8 description.                                                                                                                       |                                                                                                              |                                                                                                                                     |  |  |  |  |  |

| 1 *   | HSEL/LSEL          | data out                                                                                                                                                                                                                                                                                                                          | put format.                                                                                                                                                      | E select. Used in conjunc                                                                                    | tion with FORM (pin 7) to select the                                                                                                |  |  |  |  |  |

|       |                    | FORM                                                                                                                                                                                                                                                                                                                              | HSEL/LSEL                                                                                                                                                        | DATA OUTPUT<br>FORMAT                                                                                        | ACTIVE OUTPUT<br>PINS                                                                                                               |  |  |  |  |  |

|       |                    | 0                                                                                                                                                                                                                                                                                                                                 | Х                                                                                                                                                                | SIGN + 10-BIT<br>PARALLEL                                                                                    | PIN 20 (SIGN) &<br>PINS 10–19<br>(DB9–DB0)                                                                                          |  |  |  |  |  |

|       |                    | 1                                                                                                                                                                                                                                                                                                                                 | 0                                                                                                                                                                | LOW BYTE<br>(3LSBs)                                                                                          | PINS 17, 18 & 19<br>DB2, DB1 & DB0)                                                                                                 |  |  |  |  |  |

|       |                    | 1                                                                                                                                                                                                                                                                                                                                 | 1                                                                                                                                                                | HIGH BYTE<br>(SIGN + 7MSBs)                                                                                  | PIN 20 (SIGN) &<br>PINS 10-16<br>(DB9-DB3)                                                                                          |  |  |  |  |  |

|       |                    | X = "D                                                                                                                                                                                                                                                                                                                            | on't care" state.                                                                                                                                                |                                                                                                              |                                                                                                                                     |  |  |  |  |  |

| 9     | Vcc                | Logic Su                                                                                                                                                                                                                                                                                                                          | pply. For V <sub>CC</sub> =                                                                                                                                      | + 5V digital inputs and o                                                                                    | utputs are TTL compatible. For                                                                                                      |  |  |  |  |  |

| 10-19 | DB9-DB0            | V <sub>CC</sub> = V <sub>DD</sub> digital inputs and outputs are CMOS compatible.  DATA OUTPUT. Three state output. DB9 = MSB.                                                                                                                                                                                                    |                                                                                                                                                                  |                                                                                                              |                                                                                                                                     |  |  |  |  |  |

| 20    | SIGN               | SIGN BI                                                                                                                                                                                                                                                                                                                           | SIGN BIT OUTPUT. Three state output. Sign = AIN(+) - AIN(-) and is a logic zero for positive differential inputs and logic one for negative differential inputs. |                                                                                                              |                                                                                                                                     |  |  |  |  |  |

| 21    | DGND               | Digital G                                                                                                                                                                                                                                                                                                                         | Digital Ground.                                                                                                                                                  |                                                                                                              |                                                                                                                                     |  |  |  |  |  |

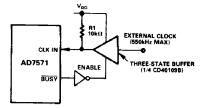

| 22    | CE                 | CHIP ENABLE. This is an enabling signal for the AD7571.  CE = 1: Normal device operation.  CE = 0: All outputs are placed in high impedance state, CS and RD input activity is ignored. Conversion results, if they have not previously been read, are stored internally and can be read when device returns to normal operation. |                                                                                                                                                                  |                                                                                                              |                                                                                                                                     |  |  |  |  |  |

| 23    | BUSY               | BUSY in<br>BUSY is                                                                                                                                                                                                                                                                                                                | dicates conversio<br>placed into a high                                                                                                                          | n status. Three-state outp<br>impedance state when Cl                                                        | out. $\overline{BUSY}$ is low during conversion.<br>E = 0.                                                                          |  |  |  |  |  |

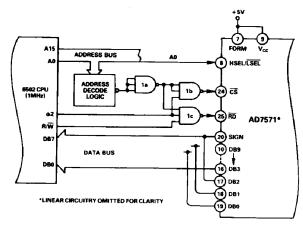

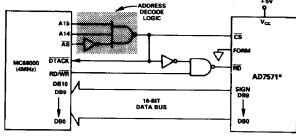

| 24    | <u>CS</u>          |                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                  | device address, used with operating modes).                                                                  | RD(pin 25) to control                                                                                                               |  |  |  |  |  |