OBSOLETE PRODUCT

NO RECOMMENDED REPLACEMENT

NO RECOMMENDED REPLACEMENT

1-800-442-7747

Call Central Applications 1-800-442-000

Central Centra

# IH6201

Dual CMOS Driver/Voltage Translator

April 1999

#### **Features**

- Driven Direct from TTL or CMOS Logic

- Translates Logic Levels Up to 30V Levels

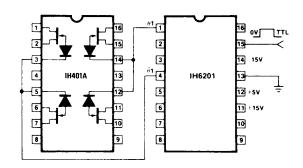

- Switches 20V<sub>ACPP</sub> Signals When Used in Conjunction with the IH401A Varafet (As An Analog Gate)

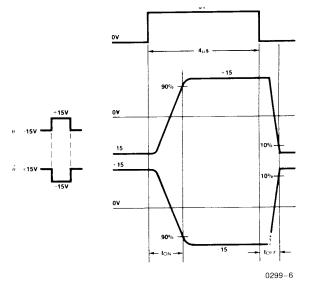

- t<sub>ON</sub> ≤ 300ns & t<sub>OFF</sub> ≤ 200ns for 30V Level Shifts

- Quiescent Supply Current ≤ 100µA for Any State (DC)

- · Provides Both Normal & Inverted Outputs

#### Part Number Information

| PART NUMBER | TEMP. RANGE<br>(°C) | PACKAGE      |

|-------------|---------------------|--------------|

| IH6201CJE   | 0 to 70             | 16 Ld CerDIP |

| IH6201MJE   | -55 to 125          | 16 Ld CerDIP |

| IH6201CPE   | 0 to 70             | 16 Ld PDIP   |

# Description

The IH6201 is a CMOS, Monolithic, Dual Voltage Translator; it takes low level TTL or CMOS logic signals and converts them to higher levels (i.e. to  $\pm 15$ V swings). This translator is typically used in making solid state switches, or analog gates.

When used in conjunction with the IH401A Varafets, the combination makes a complete solid state switch capable of switching signals up to 22V<sub>P-P</sub> and up to 20MHz in frequency. This switch is a "break-before-make" type (i.e.  $t_{OFF}$  time <  $t_{ON}$  time). The combination has typical  $t_{OFF} \approx 80 \text{ns}$  and typical  $t_{ON} \approx 200 \text{ns}$  for signals up to  $20 \text{V}_{\text{P-P}}$  in amplitude.

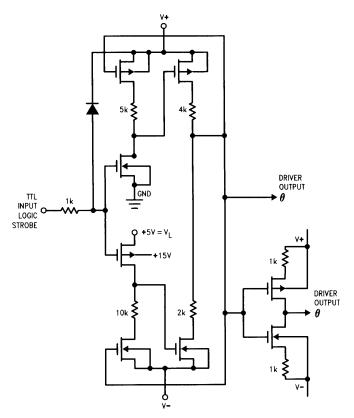

A TTL "1" input strobe will force the  $\theta$  driver output up to V+level; the  $\overline{\theta}$  output will be driven down to the V-level. When the TTL input goes to "0", the  $\theta$  output goes to V- and  $\overline{\theta}$  goes to V+; thus  $\theta$  and  $\overline{\theta}$  are  $180^{\rm O}$  out of phase with each other. These complementary outputs can be used to create a wide variety of functions such as SPDT and DPDT switches, etc.; alternatively the complementary outputs can be used to drive N and P channel MOSFETs, to make a complete CMOS analog gate.

The driver typically uses +5V and  $\pm 15V$  power supplies, however a wide range of V+ and V- is also possible. It is necessary that V+ > 5V for the driver to work properly, however.

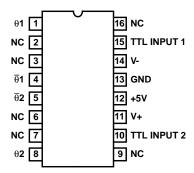

#### **Pinout**

#### IH6201 (OUTLINE DWGS, JE, PE) TOP VIEW

# Functional Diagram

#### IH6201

#

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

# **Electrical Specifications** V+ = +15V, V- = -15V, $V_L = +5V$

|                                                                    |                                                                                     | IH6201CJE, CPE |      | IH6201MJE |                    |      |       |                  |

|--------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------|------|-----------|--------------------|------|-------|------------------|

| PARAMETER                                                          | TEST CONDITIONS                                                                     | 0°C            | 25°C | 70°C      | -55 <sup>0</sup> C | 25°C | 125°C | UNITS            |

| $\theta$ or $\overline{\theta}$ Driver Output Swing                | V <sub>IN</sub> = 0V <b>_</b> + 3V, Figure 3B                                       | -              | 28   | -         | -                  | 28   | -     | V <sub>P-P</sub> |

| V <sub>IN</sub> Strobe Level ("1") for<br>Proper Translation       | $\theta \ge 14V, \ \overline{\theta} \ge -14V$                                      | 3.0            | 3.0  | 3.0       | -                  | 2.4  | -     | V <sub>DC</sub>  |

| V <sub>IN</sub> Strobe Level ("0") for<br>Proper Translation       | $\theta \ge -14V, \ \overline{\theta} \ge 14V$                                      | 0.4            | 0.4  | 0.4       | -                  | 0.8  | -     | V <sub>DC</sub>  |

| I <sub>IN</sub> Input Strobe Current<br>Draw (for 0V - 5V Range)   | V <sub>IN</sub> = 0V or +5V                                                         | ±1             | ±1   | 10        | ±1                 | ±1   | 10    | μА               |

| t <sub>ON</sub> Time                                               | V <sub>IN</sub> = 0V _L C <sub>L</sub> = 30pF Switching<br>Turn-on Time, Figure 3B  | -              | 500  | -         | -                  | 500  | -     | ns               |

| t <sub>OFF</sub> Time                                              | V <sub>IN</sub> = 0V _L C <sub>L</sub> = 30pF Switching<br>Turn-off Time, Figure 3B | -              | 500  | -         | -                  | 500  | -     | ns               |

| I+ (V+) Power Supply<br>Quiescent Current                          | V <sub>IN</sub> = 0V or +5V                                                         | 100            | 100  | 100       | 100                | 100  | 100   | μА               |

| I- (V-) Power Supply<br>Quiescent Current                          | V <sub>IN</sub> = 0V or +5V                                                         | 100            | 100  | 100       | 100                | 100  | 100   | μА               |

| I <sub>L</sub> (V <sub>L</sub> ) Power Supply<br>Quiescent Current | V <sub>IN</sub> = 0V or +5V                                                         | 100            | 100  | 100       | 100                | 100  | 100   | μА               |

### Schematic Diagram

FIGURE 1. SCHEMATIC DIAGRAM (ONE CHANNEL)

# **Applications**

#### Input Drive Capability

The strobe input lines are designed to be driven from TTL logic levels; this means 0.8V to 2.4V levels max. and min. respectively. For those users who require 0.8V to 2.0V operation, a pull-up resistor is recommended from the TTL output to +5V line. This resister is not critical and can be in the  $1k\Omega$  to  $10k\Omega$  range.

When using 4000 series CMOS logic, the input strobe is connected direct to the 4000 series gate output and no pull up resistors, or any other interface is necessary.

When the input strobe voltage level goes below GND (i.e. to -15V) the circuit is unaffected as long as V+ to  $V_{\mbox{IN}}$  does not exceed absolute maximum rating.

#### **Output Drive Capability**

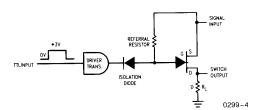

The translator output is designed to drive the IH401A Varafets; these are N-channel JFETS with built-in driver diodes. Driver diodes are necessary to isolate the signal source from the driver/translator output; this prevents a forward bias condition between the signal input and the +V<sub>CC</sub> supply. The IH6201 will drive any JFET provided some sort of isolation is added.

You will notice in Figure 2 that a "referral" resistor has been added from 2N4391 gate to its source. This resistor is needed to compensate for the inadequate charge area curve for isolation diode i.e. if C vs. V plot for diode  $\leq 2$  [C vs. V plot

for output JFET] switch won't function; then adding this resistor overcomes this condition. The "referral" resistor is normally in the  $100k\Omega$  to  $1M\Omega$  range and is not tool critical.

FIGURE 2.

# Making a Complete Solid State Switch that Can Handle 20V<sub>P-P</sub> Signals

The limitation on signal handling capability comes from the output gating device. When a JFET is used, the pinch-off of the JFET acting with the V- supply does the limiting. In fact max. signal handling capability = 2 (Vp + (V-)) Vp\_p where Vp = pinch-off voltage of JFET chosen. i.e. Vp = 7V, V- = -15V: max. signal handling = 2(7V + (-15V)) Vp\_p = 2 (7V - 15) Vp\_p = 2(-8Vp\_p) = 16Vp\_p. Obviously to get  $\geq 20Vp_p$ , Vp  $\geq 5V$  with V- = -15V. Another simple way to get  $20Vp_p$  with Vp = 7V, is to increase V- to -17V. In fact using V+ = +12V or +15V and setting V- = -18V allows one to switch  $20Vp_p$  with the IH401A. The advantage of using the Vp = 7V pinch-off (along with unsymmetrical supplies), over the Vp = 5V pinch-off (and

$\pm$ 15V supplies), is that you will have a much lower R<sub>DS(ON)</sub> for the V<sub>P</sub> = 7 JFET (i.e. for the 2N4391).

$$r_{DS(ON)}\approx 22\Omega, ~~R_{DS(ON)}\approx 35\Omega$$

$$V_P = 7V$$

$V_P = 5V$

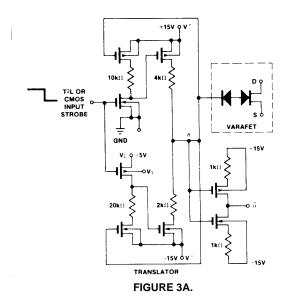

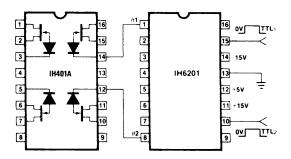

The IH6201 is a dual translator, each containing 4 CMOS FET pairs. The schematic of one-half of an IH6201, driving one-quarter of an IH401A, is shown in Figure 3A.

FIGURE 3B.

NOTE: Each translator output has a  $\theta$  and  $\overline{\theta}$  output,  $\theta$  is just the inverse of  $\overline{\theta}.$

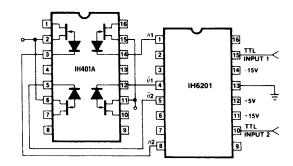

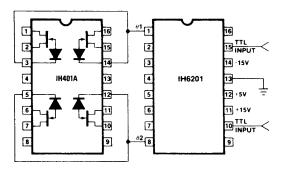

A very useful feature of this system is that one-half of an IH6201 and one-half of an IH401A can combine to make a SPDT switch, or an IH6201 plus an IH401A can make a dual SPDT analog switch (See Figure 6).

## **Switches**

FIGURE 4. DUAL SPST ANALOG SWITCH

FIGURE 5. DPDT ANALOG SWITCH

FIGURE 6. DUAL SPDT

FIGURE 7. DUAL DPST