# **LH5168**

CMOS 64K (8K × 8) Static Ram

## **FEATURES**

- 8,192 × 8 bit organization

- Access times: 80/100 ns (MAX.)

- Low-power consumption:

Operating:

303 mW (MAX.) LH5168/D/N

@ 80 ns

248 mW (MAX.) LH5168/D/N/T/TR

@ 100 ns

275 mW (MAX.) LH5168H/HD/HN

@ 100 ns

Standby:

5.5 μW (MAX.) LH5168/D/N/T/TR 16.5 μW (MAX.) LH5168H/HD/HN

- Fully-static operation

- Three-state outputs

- Single +5 V power supply

- TTL compatible I/O

- Pin compatible to 64K bit EPROM

- Wide temp. range available

LH5168: -10 to +70°C

LH5168H: -40 to +85°C

Packages:

28-pin, 600-mil DIP

28-pin, 300-mil SK-DIP

28-pin, 450-mil SOP

28-pin,  $8 \times 13 \text{ mm}^2 \text{ TSOP (Type I)}$

## DESCRIPTION

The LH5168 is a static RAM organized as  $8,192 \times 8$  bits. It is fabricated using silicon-gate CMOS process technology.

The LH5168H is designed for wide temperature range from -40 to +85°C.

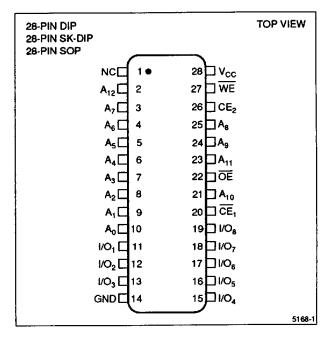

## PIN CONNECTIONS

Figure 1. Pin Connections for DIP, SK-DIP, and SOP Packages

CMOS 64K (8K × 8) Static RAM

LH5168

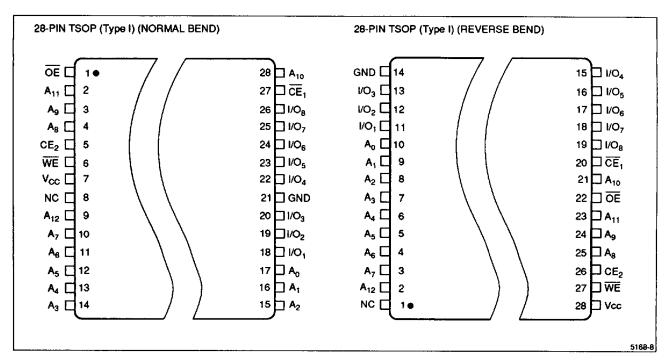

Figure 2. Pin Connections for TSOP Packages

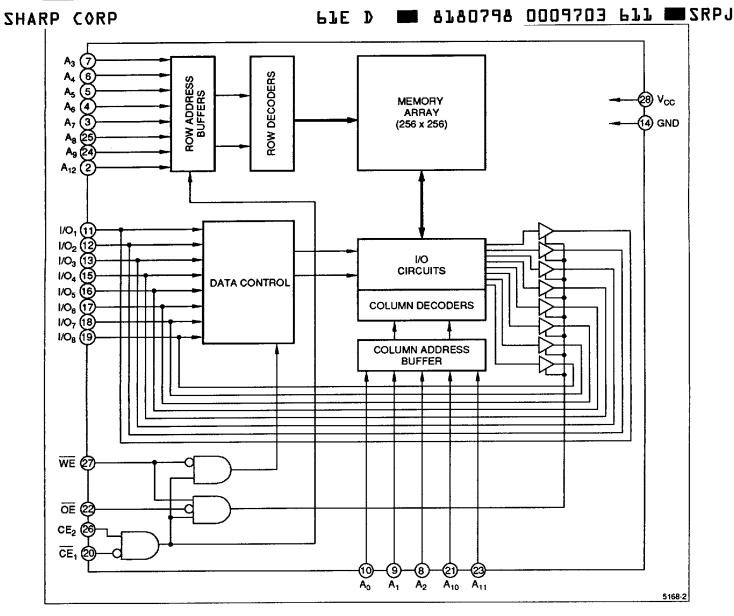

Figure 3. LH5168 Block Diagram

## PIN DESCRIPTION

| SIGNAL                            | PIN NAME            |

|-----------------------------------|---------------------|

| A <sub>0</sub> - A <sub>12</sub>  | Address inputs      |

| CE <sub>1</sub> - CE <sub>2</sub> | Chip Enable input   |

| WE                                | Write Enable input  |

| ŌĒ                                | Output Enable input |

| SIGNAL                              | PIN NAME                |

|-------------------------------------|-------------------------|

| I/O <sub>1</sub> - I/O <sub>8</sub> | Data inputs and outputs |

| Vcc                                 | Power supply            |

| GND                                 | Ground                  |

| NC                                  | Non-connection          |

## **TRUTH TABLE**

| CE <sub>1</sub> | CE <sub>2</sub> | WE | ŌĒ | MODE           | I/O <sub>1</sub> - I/O <sub>8</sub> | SUPPLY CURRENT             | NOTE |

|-----------------|-----------------|----|----|----------------|-------------------------------------|----------------------------|------|

| Н               | Х               | Х  | Х  | Deselect       | High-Z                              | Standby (I <sub>SB</sub> ) | 1    |

| Х               | L               | Х  | Х  | Deselect       | High-Z                              | Standby (I <sub>SB</sub> ) | 1    |

| L               | Н               | L  | X  | Write          | DiN                                 | Operating (Icc)            |      |

| L               | Н               | Н  | L  | Read           | Dout                                | Operating (Icc)            |      |

| L               | Н               | Н  | Н  | Output disable | High-Z                              | Operating (Icc)            |      |

#### NOTE:

1. X = H or L

## **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER             | CVMDOL | SYMBOL 80 ns 100 n           |                              | UNIT | NOTE |

|-----------------------|--------|------------------------------|------------------------------|------|------|

| PANAMETER             | STMBOL | RATING                       | RATING                       | UNII | NOTE |

| Supply voltage        | Vcc    | -0.3 to +7.0                 | -0.3 to +7.0                 | ٧    | 1    |

| Input voltage         | VIN    | -0.5 to V <sub>CC</sub> +0.5 | -0.3 to V <sub>CC</sub> +0.3 | ٧    | 1    |

| Operating temperature | Tonr   | -10 to +70                   | -10 to +70                   | °C   | 2    |

| Operating temperature | Topr   |                              | -40 to +85                   | °C   | 3    |

| Storage temperature   | Tstg   | -55 to +150                  | -55 to +150                  | °C   |      |

#### NOTES:

- 1. The maximum applicable voltage on any pin with respect to GND.

- 2. LH516B/D/N

- 3. LH5168H/HD/HN

## **RECOMMENDED OPERATING CONDITIONS (Note 1)**

| PARAMETER      | SYMBOL          | 80 ns |      |           |      | LINUT |                       |      |

|----------------|-----------------|-------|------|-----------|------|-------|-----------------------|------|

|                | STMBOL          | MIN.  | TYP. | MAX.      | MIN. | TYP.  | MAX.                  | UNIT |

| Supply voltage | Vcc             | 4.5   | 5.0  | 5.5       | 4.5  | 5.0   | 5.5                   | ٧    |

| Input voltage  | V <sub>IH</sub> | 2.2   |      | Vcc + 0.5 | 2.2  |       | V <sub>CC</sub> + 0.3 | V    |

| input voitage  | V <sub>IL</sub> | -0.5  |      | 0.8       | -0.3 |       | 0.8                   | V    |

### NOTE:

## DC CHARACTERISTICS $^1$ (V<sub>CC</sub> = 5 V $\pm$ 10%)

| PARAMETER              | SYMBOL           | CONDITIONS                                                                                                                                           |                       |  | MAX.  | UNIT | NOTE |

|------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|-------|------|------|

| Input leakage current  | ارر              | $V_{IN} = 0$ to $V_{CC}$                                                                                                                             |                       |  | 1.0   | μА   |      |

| Output leakage current | lιο              | $\overline{CE}_1 = V_{IH} \text{ or } CE_2 = V_{IL}$ or $\overline{OE} = V_{IH} \text{ or } \overline{WE} = V_{IL}$ $V_{I/O} = 0 \text{ to } V_{CC}$ |                       |  | 1.0   | μΑ   |      |

|                        |                  | CE <sub>1</sub> = V <sub>IL</sub> , V <sub>IN</sub> = V <sub>IL</sub> to V <sub>IH</sub><br>CE <sub>2</sub> = V <sub>IH</sub> , Outputs open         | tcycle =<br>80 ns     |  | 55    | mA   |      |

| 0                      | lcc              | CE <sub>1</sub> = V <sub>IL</sub> , V <sub>IN</sub> = V <sub>IL</sub> to V <sub>IH</sub><br>CE <sub>2</sub> = V <sub>IH</sub> , Outputs open         | tcycle =              |  | 45    |      | 2    |

| Operating current      |                  |                                                                                                                                                      | 100 ns                |  | 50    |      | 3    |

|                        |                  | $\overline{CE}_1 = V_{IL}, V_{IN} = 0.2 \text{ V to}$ $V_{CC} - 0.2 \text{ V}$ $CE_2 = V_{IH}, \text{ Outputs open}$                                 | tcycLE =<br>1.0 μs    |  | 10 mA |      |      |

|                        | I <sub>SB1</sub> | $\overline{CE}_1 = V_{IH} \text{ or } CE_2 =$                                                                                                        | V <sub>IL</sub>       |  | 10    | mA   |      |

| Standby current        | Isa              | CE <sub>2</sub> ≤ 0.2 V or                                                                                                                           | T <sub>A</sub> ≤ 70°C |  | 1.0   | μА   | 2    |

|                        | isa              | CE <sub>1</sub> , CE <sub>2</sub> ≥ V <sub>CC</sub> - 0.2 V                                                                                          | T <sub>A</sub> ≤ 85°C |  | 3.0   | μА   | 3    |

| Output voltage         | Vol              | l <sub>OL</sub> = 2.1 mA                                                                                                                             |                       |  | 0.4   | ٧    |      |

| Output Voltage         | VoH              | I <sub>OH</sub> = -1 mA                                                                                                                              |                       |  |       | >    |      |

## NOTES:

- 1.  $T_A = -10$  to  $70^{\circ}$ C (LH5168/D/N/T/TR),  $T_A = -40$  to  $+85^{\circ}$ C (LH5168H/HD/HN)

- 2. LH5168/D/N/T/TR

- 3. LH5168H/HD/HN

<sup>1.</sup>  $T_A = -10$  to +70°C (LH5168/D/N),  $T_A = -40$  to +85°C (LH5168H/HD/HN).

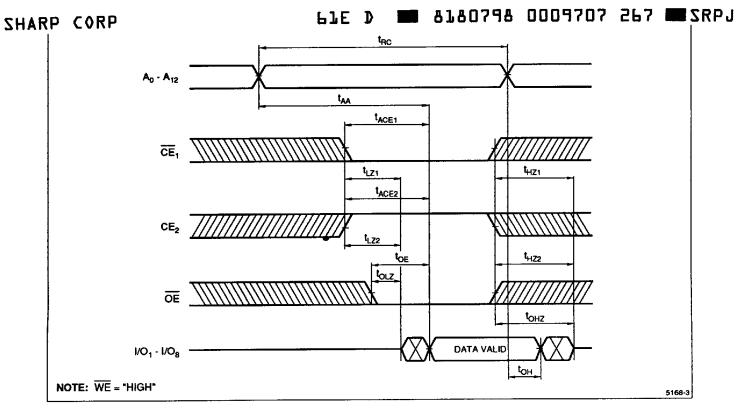

## AC CHARACTERISTICS 1

## (1) READ CYCLE (VCC = $5 V \pm 10\%$ )

| PARAMETER                          |                    | SYMBOL | 80   | กร   | 100 ns |      | UNIT    | NOTE |

|------------------------------------|--------------------|--------|------|------|--------|------|---------|------|

|                                    |                    | STMBOL | MIN. | MAX. | MIN.   | MAX. | 1 0,4,, |      |

| Read cycle                         |                    | trc    | 80   |      | 100    |      | ns      |      |

| Address access time                | )                  | taa    |      | 80   |        | 100  | ns      |      |

| Chip enable                        | (CE <sub>1</sub> ) | tace1  |      | 80   |        | 100  | ns      |      |

| access time                        | (CE <sub>2</sub> ) | tace2  |      | 80   |        | 100  | ns      |      |

| Output enable access time          |                    | toe    |      | 40   |        | 40   | ns      |      |

| Output hold time                   |                    | tон    | 10   |      | 10     |      | ns      |      |

| Chip enable to                     | (CE <sub>1</sub> ) | tLZ1   | 10   |      | 10     |      | ns      | 2    |

| output in Low-Z                    | (CE <sub>2</sub> ) | tLZ2   | 10   |      | 10     |      | กร      | 2    |

| Output enable to out<br>Low-Z      | tput in            | toLz   | 5    |      | 5      |      | กร      | 2    |

| Chip enable to                     | (CE <sub>1</sub> ) | tHZ1   | 0    | 30   | 0      | 30   | ns      | 2    |

| output in High-Z                   | (CE <sub>2</sub> ) | tHZ2   | 0    | 30   | 0      | 30   | ns      | 2    |

| Output disable to output in High-Z |                    | tonz   | 0    | 20   | 0      | 20   | ns      | 2    |

## NOTES:

- 1.  $T_A = -10 \text{ to } +70 ^{\circ}\text{C} \text{ (LH5168/D/N/T/TR)}, T_A = -40 \text{ to } +85 ^{\circ}\text{C} \text{ (LH5168H/HD/HN)}$

- 2. Active output to high-impedance and high-impedance to output active tests specified for a ±500 mV transition from steady state levels into the test load. CLOAD = 5 pF.

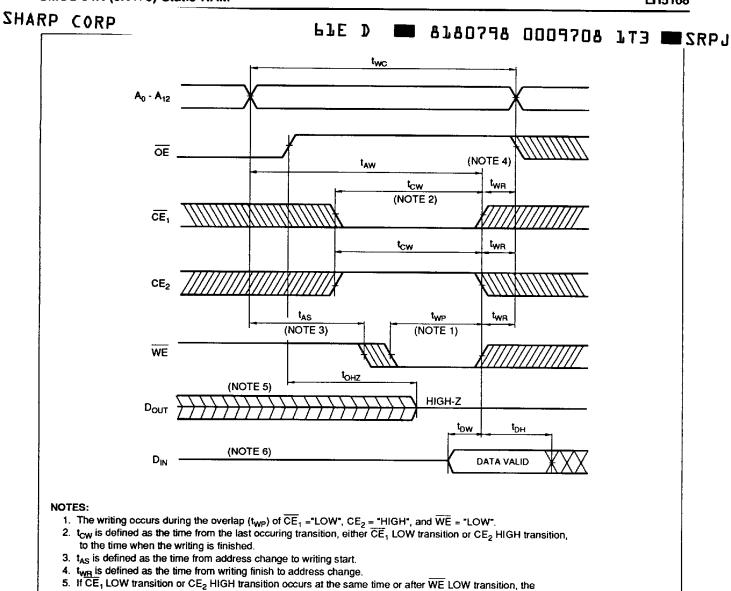

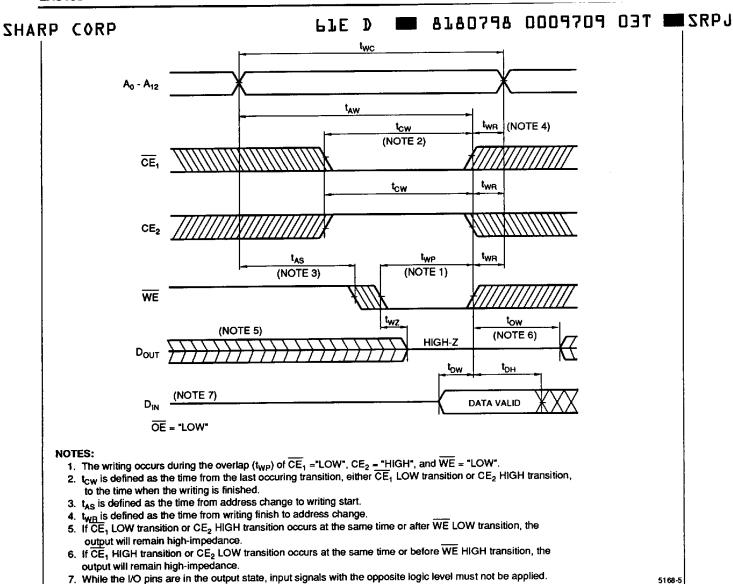

## (2) WRITE CYCLE (V<sub>CC</sub> = $5 V \pm 10\%$ )

| PARAMETER                       | SYMBOL | 80 ns |      | 100 ns |      | UNIT | NOTE |

|---------------------------------|--------|-------|------|--------|------|------|------|

|                                 | SIMBUL | MIN.  | MAX. | MIN.   | MAX. | ONII | HOIL |

| Write cycle time                | twc    | 80    |      | 100    |      | ns   |      |

| Chip enable to end of write     | tcw    | 70    |      | 80     |      | ns   |      |

| Address valid to end of write   | taw    | 70    |      | 80     |      | ns   |      |

| Address setup time              | tas    | 0     |      | 0      |      | ns   |      |

| Write pulse width               | twp    | 60    |      | 60     |      | ns   |      |

| Write recovery time             | twn    | 0     |      | 0      |      | ns   |      |

| Data valid to end of write      | tow    | 40    |      | 40     |      | ns   |      |

| Data hold time                  | tон    | 0     |      | 0      |      | ns   |      |

| Output active from end of write | tow    | 10    |      | 10     |      | ns   | 1    |

| WE to output in High-Z          | twz    | 0     | 30   | 0      | 30   | ns   | 1    |

| OE to output in High-Z          | tonz   | 0     | 20   | 0      | 20   | ns   | 1    |

## NOTE:

## **AC TEST CONDITIONS**

| PARAMETER               | MODE                             |

|-------------------------|----------------------------------|

| Input voltage amplitude | 0.6 to 2.4 V                     |

| Input rise/fall time    | 10 ns                            |

| Timing reference level  | 1.5 V                            |

| Output load conditions  | (1TTL + C <sub>L</sub> = 100 pF) |

<sup>1.</sup> Active output to high-impedance and high-impedance to output active tests specified for a ±500 mV transition from steady state levels into the test load. CLOAD = 5 pF.

## SHARP CORP

# 6]E D ■ 8]80798 0009706 320 ■ SRPJ

## CAPACITANCE 1 (TA = 25°C, f = 1MHz)

| PARAMETER                | SYMBOL          | CONDITIONS            | MIN. | TYP. | MAX. | UNIT |

|--------------------------|-----------------|-----------------------|------|------|------|------|

| Input capacitance        | CIN             | V <sub>IN</sub> = 0 V |      |      | 7    | рF   |

| Input/output capacitance | C <sub>VO</sub> | V <sub>VO</sub> = 0 V |      |      | 10   | pF   |

#### NOTE:

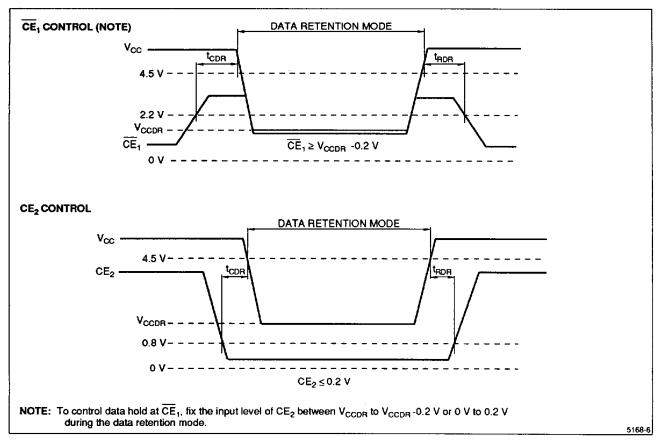

## DATA RETENTION CHARACTERISTICS 1

| PARAMETER                      | SYMBOL CONDITIONS |                                                                                       | MIN. | MAX. | UNIT | NOTE |

|--------------------------------|-------------------|---------------------------------------------------------------------------------------|------|------|------|------|

| Data retention voltage         | VCCDR             | $CE_2 \le 0.2 \text{ V or}$<br>$CE_1$ , $CE_2 \ge V_{CC} - 0.2 \text{ V}$             | 2.0  |      | ٧    |      |

| Data retention current         | ICCDR             | VCCDR = 3 V,                                                                          |      | 0.6  | μΑ   | 2    |

|                                |                   | $CE_2 \le 0.2 \text{ V or } \overline{CE}_1$ ,<br>$CE_2 \ge V_{CCDR} - 0.2 \text{ V}$ |      | 1.5  | μА   | 3    |

| Chip disable to data retention | tcor              |                                                                                       | 0    |      | ns   |      |

| Recovery time                  | t <sub>RDR</sub>  |                                                                                       | tRC  |      | ns   | 4    |

#### NOTES:

- 1.  $T_A = -10$  to +70°C (LH5168/D/N/T/TR),  $T_A = -40$  to +85°C (LH5168H/HD/HN)

- 2. LH5168/D/N/T/TR at T<sub>A</sub> ≤ 70°C

- 3. LH5168H/HD/HN at T<sub>A</sub> ≤ 85°C

- 4. t<sub>RC</sub> = Read cycle time

Figure 4. Low Voltage Data Retention

<sup>1.</sup> This parameter is sampled and not production tested.

Figure 5. Read Cycle

output will remain high-impedance.

Figure 6. Write Cycle 1

6. While the I/O pins are in the output state, input signals with the opposite logic level must not be applied.

5168-4

Figure 7. Write Cycle 2

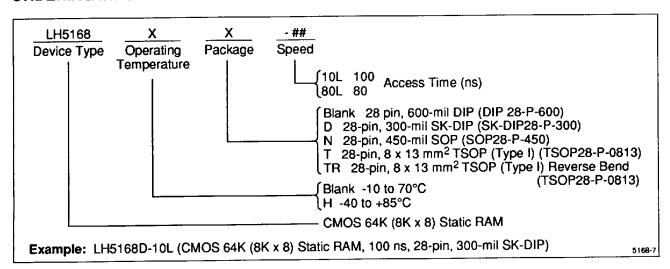

### ORDERING INFORMATION