June 1990

### Description

The  $\mu$ PD42270 is a field buffer designed for NTSC TV applications and for other applications where serial data is needed. Equipped with four planes of 263-line by 910-bit storage, the  $\mu$ PD42270 can execute serial write and read cycles on any of the 263 lines. Within a line, four planes of 910 bits each may be written or read at the NTSC sampling rate of  $4f_{SC}$ .

Each of the four planes in the  $\mu$ PD42270 is equipped with two ports, one each for the write and read data registers. Each of the registers is split into two 455-bit segments but functions as if it were organized as one scan line of 910 bits. Independent control of write and read operation makes it possible for the device to operate synchronously or asynchronously at a clock frequency of 14.3 MHz or higher.

The synchronous option simplifies interframe luminance (Y) and chrominance (C) separation and interfield noise reduction and makes it easy to obtain a one-field delay line for digital TV and VCR applications requiring NTSC 4f<sub>SC</sub> sampling. To obtain a very long delay, field length can be configured from 260 to 263 lines and line length of the last line from 896 to 910 bits.

The asynchronous option is useful in applications such as frame synchronization and time base correction, where line jump, line hold, line reset and pointer clear functions are required to support special effects in TV field processing.

Regular refreshing of the device's dynamic storage cells is performed automatically by an internal circuit. All inputs and outputs, including clocks, are TTL-compatible. The  $\mu$ PD42270 is packaged in a 400-mil, 28-pin plastic DIP and is guaranteed for operation at -20 to  $+70^{\circ}$ C.

#### Ordering Information

|              | Access Time | Cycle Time |                    |

|--------------|-------------|------------|--------------------|

| Part Number  | (max)       | (min)      | Package            |

| μPD42270C-60 | 40 ns       | 60 ns      | 28-pin plastic DIP |

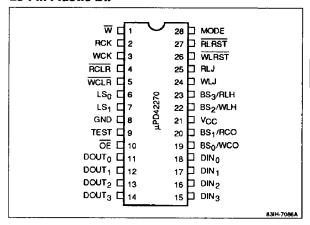

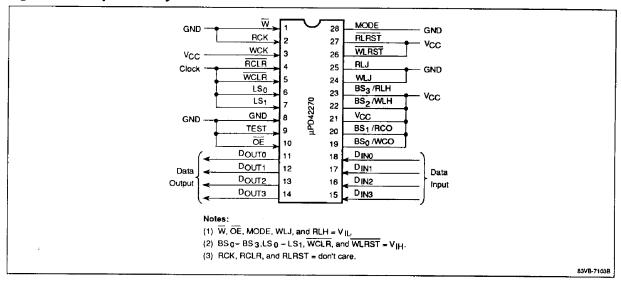

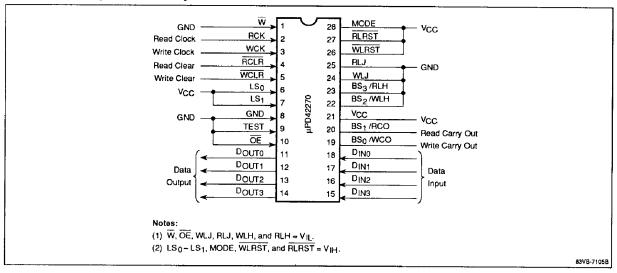

# **Pin Configuration**

#### 28-Pin Plastic DIP

### **Features**

- Three functional blocks

- Four 263-line x 910-bit storage planes

- --- Four 910-bit write registers, one for each plane

- Four 910-bit read registers, one for each plane

- Two data ports: serial write and serial read

- □ Asynchronous operation

- --- Dual-port accessibility

- Carry-out feature to indicate position of scan line

- Line jump, line hold, line reset, and pointer clear functions

- Synchronous operation

- Variable field length: from 260 to 263 lines

- Variable last line length: from 896 to 910 bits

- Automatic refreshing

- CMOS technology

- Fully TTL-compatible inputs, outputs, and clocks

- Three-state outputs

- Single + 5-volt power supply

- On-chip substrate bias generator

- Standard 400-mil, 28-pin plastic DIP packaging

18c

| Din | Identifica | tion | ì |

|-----|------------|------|---|

|     |            |      |   |

| Symbol                                | Function                            |

|---------------------------------------|-------------------------------------|

| D <sub>INO</sub> - D <sub>IN3</sub>   | Write data inputs                   |

| D <sub>OUT0</sub> - D <sub>OUT3</sub> | Read data outputs                   |

| W                                     | Write enable                        |

| ŌĒ                                    | Output enable                       |

| WCK                                   | Write clock input                   |

| RCK                                   | Read clock input                    |

| WCLA                                  | Write pointer clear                 |

| RCLR                                  | Read pointer clear                  |

| WLRST                                 | Write line reset                    |

| RLRST                                 | Read line reset                     |

| WLJ                                   | Write line jump                     |

| RLJ                                   | Read line jump                      |

| WLH                                   | Write line hold                     |

| RLH                                   | Read line hold                      |

| wco                                   | Write data register carry output    |

| RCO                                   | Read data register carry output     |

| LS <sub>0</sub> - LS <sub>1</sub>     | Line select inputs                  |

| BS <sub>0</sub> - BS <sub>3</sub>     | Bit select inputs                   |

| MODE                                  | Synchronous/asynchronous control    |

| GND                                   | Ground                              |

| Vcc                                   | +5-volt power supply                |

| TEST                                  | Test pin (connect to GND in system) |

### Pin Functions

$D_{INO}$  -  $D_{IN3}$ . These pins function as write data inputs, e.g., for  $4f_{SC}$  composite color or brightness signals.

$\textbf{D}_{\mbox{OUT0}}$  -  $\mbox{D}_{\mbox{OUT3}}.$  These pins are three-state read data outputs.

$\overline{W}$ . A low level on  $\overline{W}$  enables write operation.  $\overline{W}$  must be kept low throughout the entire scan line to ensure that data is stored serially; if  $\overline{W}$  goes high any time during the WCK clock sequencing for a line, write operation will be disabled for the half of the line (455 bits) being written. The write address pointer increments in synchronization with WCK, regardless of  $\overline{W}$ .

$\overline{\text{OE}}$ . This signal controls read data output. When  $\overline{\text{OE}}$  is low, read data is output on  $D_{\text{OUT0}}\text{-}D_{\text{OUT3}}$ . When  $\overline{\text{OE}}$  is high,  $D_{\text{OUT0}}$  -  $D_{\text{OUT3}}$  are in a state of high impedance. The read address pointer is incremented by RCK, regardless of the signal level of  $\overline{\text{OE}}$ .

WCK The rising edge of WCK latches write data from  $D_{\text{INO}}$  -  $D_{\text{IN3}}$ . Each time this signal is activated, the write bit pointer increments sequentially and 4 bits of data

are sampled and loaded into the write register. Although the register functions as one scan line of 910 bits, data is moved into and out of it in blocks of 455 x 4 bits. While 455 serial write cycles are being executed in one-half of the register, the 455 addresses previously written to the other half are simultaneously transferred to storage. Writing continues in this manner, alternating between the two halves of the register. Automatic refreshing and data transfer timing decisions are made by the internal arbitration circuit after each block of 455 addresses has been written.

RCK. The rising edge of RCK initiates read operation. Each time this signal is activated, the bit pointer increments by 1 and serial read cycles are executed in the read register. Although the register functions as one scan line of 910 bits, data is moved into and out of it in blocks of 455 x 4 bits. While 455 serial read cycles are being executed in one-half of the register, the 455 addresses previously read out of the other half are replaced by data from the storage array. Reading continues in this manner, alternating between the two halves of the register. Automatic refreshing and data transfer timing decisions are made by the arbitration circuit after each block of 455 addresses has been read. In synchronous operation, WCK controls read cycles and RCK is not used.

WCLR. When WLRST is high, WCLR can be brought low to clear the write pointers to address 0 of the data register and scan line 0 of the storage array. At least one rising edge of WCK must occur while WCLR is held low for a minimum of 3 μs to ensure clearing of both pointers. The clear function ends when WCLR goes high. If WLRST is still high, the next rising edge of WCK writes the data on D<sub>INO</sub> - D<sub>IN3</sub> into address 0 of the write register.

RCLR. When RLRST is high, RCLR can be brought low to clear the read pointers to address 0 of the data register and scan line 0 of the storage array (asynchronous operation only). At least one rising edge of RCK must occur while RCLR is held low for a minimum of 3  $\mu$ s to ensure clearing of both pointers. The clear function ends when RCLR goes high. If RLRST is still high, the data from address 0 is read out on D<sub>OUT0</sub> - D<sub>OUT3</sub> and the next rising edge of RCK initiates data access from address 1.

WLRST. This pin is used in synchronous or asynchronous operation to reset the bit pointer to address 0 of the line following the one to which the signal is applied. In standard write operation, the scan line pointer increments by 1 whenever the bit pointer reaches the last address of a line. If WCLR is high, WLRST can be brought low for a minimum of 3 µs to force an end-of-

18c

line condition, whereby write cycles begin executing from address 0 of the next sequential scan line. When used in conjunction with WLH, WLRST resets the current scan line; when combined with WLJ, WLRST begins writing from address 0 of the line to which the scan line pointer is jumped.

RLRST. This pin is valid in asynchronous operation and can be used to reset the bit pointer to address 0 of the read line following the one to which the signal is applied. In standard read operation, the scan line pointer increments by 1 whenever the bit pointer reaches the last address of a line. If RCLR is high, RLRST can be brought low for a minimum of 3  $\mu$ s to force an end-of-line condition, whereby read cycles begin executing from address 0 of the next sequential scan line. When used in conjunction with RLH, RLRST resets the current scan line; when combined with RLJ, RLRST begins reading from address 0 of the line to which the scan line pointer is jumped.

WLJ. Each positive pulse of this signal increments the write scan line pointer by one line (asynchronous operation only). WLJ is sampled at the rising edge of WCK. If WLJ is high, a single jump is executed. If WLJ remains high, no further jumps occur. To jump again, WLJ must go low for at least one rising edge of WCK before going high again. It takes a minimum of two WCK cycles to complete a line jump. The first cycle senses the high level of WLJ and increments the scan line pointer. An additional WCK cycle with WLJ low is required to complete the function. If more than one line jump is needed, then the sequence must be repeated. A line jump occurs either when the current line has been completely filled or after WLRST has reset the write address. The new scan line can be calculated by n+11+1x (where "n" is the current line and "x" equals the number of positive WLJ pulses). Changes in the level of WLJ must be made when the bit pointer is between locations 229 and 909 of the current line and when WCLR and WLRST are high and WLH is low.

RLJ. Each positive pulse of this signal increments the read scan line pointer by one line (asynchronous operation only). RLJ is sampled at the rising edge of RCK. If RLJ remains high, a single line jump is executed. To jump again, RLJ must go low for at least one rising edge of RCK before going high again. It takes a minimum of two RCK cycles to complete a line jump. The first cycle senses the high level of RLJ and increments the scan line pointer. An additional RCK cycle with RLJ low is required to complete the function. If more than one line jump is needed, then this sequence must be repeated.

A line jump occurs either when the current line has been completely read or after RLRST has reset the read

address. The new scan line can be calculated by n+1+x (where "n" is the current line and "x" equals the number of positive RLJ pulses).

Changes in the level of RLJ must be made when the bit pointer is between locations 682 and 909 of the previous line, or between 0 and 452 of the current line, and when RCLR and RLRST are high and RLH is low.

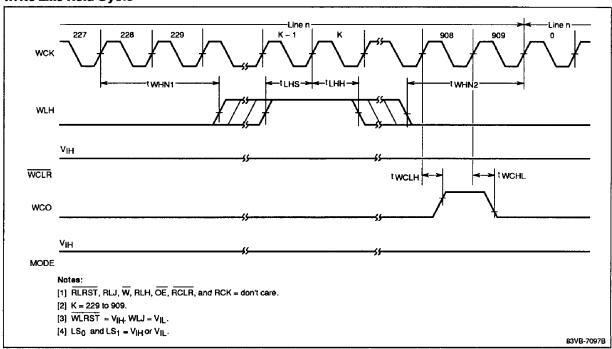

WLH. Once this input is applied, the write scan line pointer will hold its position even if successive write clocks are applied. The level of WLH is sampled at the rising edge of WCK and must be applied between locations 229 and 909 of the line to be held. The held line is released after 910 addresses have been rewritten or after WLRST resets the write line address. WLH is multiplexed with BS<sub>2</sub> and is valid in asynchronous operation only. WLH (high) must be input only when WCLR and WLRST are high and WLJ is low.

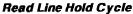

RLH. Once this input is applied, the read scan line pointer will hold its position even if successive read clocks are applied. The level of RLH is sampled at the rising edge of RCK and must be clocked between locations 682 and 909 of the line preceding the line to hold, or between locations 0 and 452 of the line to hold. The held line is released after 910 addresses have been read or after RLRST resets the read line address. RLH (high) must be input only when RCLR and RLRST are high and RLJ is low. RLH is multiplexed with BS<sub>3</sub> and is valid in asynchronous operation only.

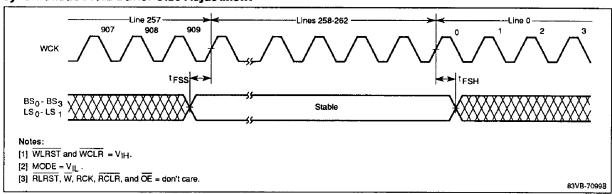

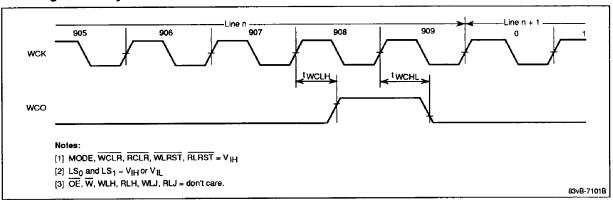

**WCO.** When the bit pointer reaches address 909 of the write data register, this signal goes high for one WCK cycle. WCO is multiplexed with BS<sub>0</sub> and is valid in asynchronous operation only.

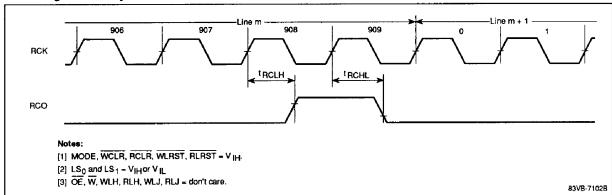

**RCO.** When the bit pointer reaches address 909 of the read data register, this signal goes high for one RCK cycle. RCO is multiplexed with BS<sub>1</sub> and is valid in asynchronous operation only.

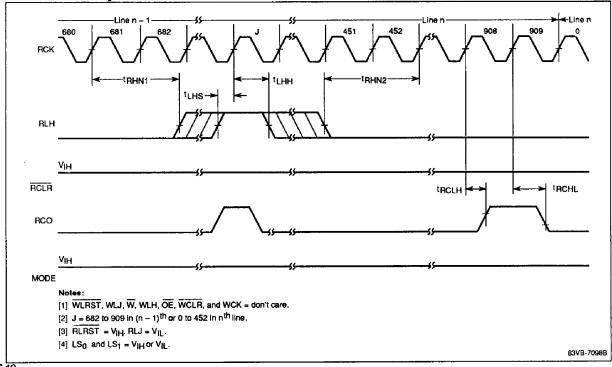

$BS_0$  -  $BS_3$ . These pins control the number of bits in the last line of the field. The combined signals of  $BS_0$ - $BS_3$  set the line length from 896 to 910 bits in one-bit steps (table 1). The length of the last line can change for each field, but all four pins should not be set low.  $BS_0$ ,  $BS_1$ ,  $BS_2$  and  $BS_3$  are multiplexed with WCO, RCO, WLH and RLH, respectively, and are valid in synchronous operation only. In asynchronous operation, the line length is fixed at 910 bits.

$LS_0$  -  $LS_1$ . These pins control the number of lines for one field in either synchronous or asynchronous operation. The combined signals of  $LS_0$  and  $LS_1$  set the number of lines to 260, 261, 262, or 263 (table 2). The number of lines can be changed for each field.

18С-з

MODE. This pin selects the operating mode. A low signal selects synchronous operation and a high signal selects asynchronous operation. If MODE is changed after power has been applied to the μPD42270, it is necessary to clear the address pointers by bringing WCLR and RCLR low. MODE can be changed at any time; however, data input in one mode may be unreliable in the other (see table 3 for valid pin functions).

Table 1. Line Length Adjustment

| BS <sub>3</sub> | BS <sub>2</sub> | BS <sub>1</sub> | BS <sub>0</sub> | Number of Bits in the Last Line |

|-----------------|-----------------|-----------------|-----------------|---------------------------------|

| L               | L               | L               | L               | Prohibited                      |

| L               | L               | L               | Н               | 896                             |

| L               | L               | Н               | L               | 897                             |

| L               | L               | Н               | Н               | 898                             |

| L               | Н               | L               | L               | 899                             |

| L               | Н               | L               | н               | 900                             |

| L               | Н               | Н               | L               | 901                             |

| L               | Н               | Н               | Н               | 902                             |

| Н               | L               | L               | L               | 903                             |

| Н               | L               | L               | н               | 904                             |

| Н               | L               | Н               | L               | 905                             |

| Н               | L               | Н               | Н               | 906                             |

| Н               | Н               | L               | L               | 907                             |

| Н               | Н               | L               | • Н             | 908                             |

| H               | Н               | Н               | L               | 909                             |

| H               | Н               | Н               | Н               | 910                             |

#### Notes:

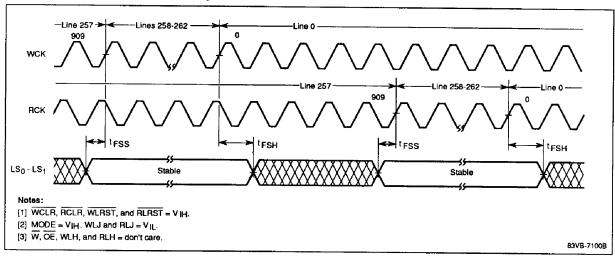

(1) LS<sub>0</sub>- LS<sub>1</sub> and BS<sub>0</sub>- BS<sub>3</sub> must be held at a stable high or low level to maintain the number of bits per scan line and the number of scan lines per field while the line pointer indicates the position between lines 258 and 262.

Table 2. Line Number Adjustment

| LS <sub>0</sub> | Number of Lines |

|-----------------|-----------------|

| L               | 260             |

| Н               | 261             |

| L               | 262             |

| Н               | 263             |

|                 | L<br>H<br>L     |

#### Notes:

(1) LS<sub>0</sub> - LS<sub>1</sub> and BS<sub>0</sub> - BS<sub>3</sub> must be held at a stable high or low level to maintain the number of bits per scan line and the number of scan lines per field while the line pointer indicates a position between lines 258 and 262.

Table 3. Valid Pin Functions According to Mode

| Pin Name             | Synchronous Mode<br>(Note 1) | Asynchronous Mode<br>(Note 2) |

|----------------------|------------------------------|-------------------------------|

| MODE                 | 0                            | 1                             |

| BS <sub>0</sub> /WCO | BS <sub>0</sub>              | wco                           |

| BS <sub>1</sub> /RCO | BS <sub>1</sub>              | RCO                           |

| BS <sub>2</sub> /WLH | BS <sub>2</sub>              | WLH                           |

| BS <sub>3</sub> /RLH | BS <sub>3</sub>              | RLH                           |

| RCLR                 | Invalid                      | Valid                         |

| RCK                  | Invalid                      | Valid                         |

| RLRST                | Invalid                      | Valid                         |

| WCLR                 | Valid                        | Valid                         |

| WCK                  | Valid                        | Valid                         |

| WLRST                | Valid                        | Valid                         |

| WLJ                  | Invalid                      | Valid                         |

| RW                   | Invalid                      | Valid                         |

#### Notes:

- (1) Write and read cycles are controlled by WCLR, WCK, and WLRST in synchronous operation.

- (2) In asynchronous operation, write and read cycles are controlled independently.

### Capacitance

$T_A = 25^{\circ}C$ ;  $V_{CC} = +5.0 \text{ V} \pm 10\%$ ; GND = 0 V; f = 1 MHz

| Parameter          | Symbol | Min | Тур | Max | Unit | Pins Under Test                                                                                                                                                                           |

|--------------------|--------|-----|-----|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input capacitance  | CI     |     |     | 5   | рF   | $D_{IN0}$ - $D_{IN3}$ , $\overline{W}$ , $\overline{OE}$ , WCK, RCK, $\overline{WCLR}$ , RCLR, $\overline{WLRST}$ , RLRST, WLJ, RLJ, LS $_0$ - LS $_1$ , BS $_2$ /WLH, BS $_3$ /RLH, MODE |

| I/O capacitance    | CVO    |     |     | 8   | рF   | BS <sub>0</sub> /WCO, BS <sub>1</sub> /RCO                                                                                                                                                |

| Output capacitance | Co     |     |     | 7   | рF   | D <sub>OUT</sub> - D <sub>OUT</sub>                                                                                                                                                       |

#### **DEVICE OPERATION**

The  $\mu$ PD42270 supports two operating modes to accommodate various NTSC TV applications. Depending on the logic level of the MODE pin, the device will execute either synchronous or asynchronous write and read cycles on the addresses specified by the internal address pointers. When selecting the mode after poweron, it is necessary to reset these pointers to starting address 0 using WCLR and RCLR. The level of MODE may be changed at any time.

### Synchronous Mode

In synchronous mode, write and read cycles are executed simultaneously by WCLR, WLRST, WCK, W and OE to create a delay line, which means that write and read addresses always coincide. After all lines within a field have been written, they then are read out as the device begins overwriting new data to the same addresses again. Field length may be configured from 260 to 263 lines and last line length from 896 to 910 bits by means of the LS and BS pins, respectively. Synchronous operation is useful in applications where a very long delay line is required and may be selected by setting MODE low.

### Asynchronous Mode

In asynchronous mode,  $\overline{WCLR}$ ,  $\overline{WLRST}$ , WCK and  $\overline{W}$  control write cycles, while read cycles are controlled independently by  $\overline{RCLR}$ ,  $\overline{RLRST}$ , RCK and  $\overline{OE}$ . Field length may be configured from 260 to 263 lines using LS<sub>0</sub> - LS<sub>1</sub>. Line length remains fixed at 910 bits and BS<sub>0</sub>-BS<sub>3</sub> are disabled to provide for the register carry out, line hold, and line jump functions. Asynchronous operation is useful for frame synchronization or time base correction and may be selected by setting MODE high.

**Address Clear.** Setting WCLR and RCLR low for a minimum of  $3\,\mu s$  during successive WCK and RCK cycles initializes the internal pointers to starting address 0 of the first scan line (RCLR is disabled in synchronous mode). Although address clear signals must meet the specifications for setup and hold times as measured from the rising edges of WCK and RCK, they are not dependent on the status of  $\overline{W}$  or  $\overline{OE}$ . An address clear cycle cannot occur in conjunction with WLRST or RLRST line reset cycles.

**Write Operation.** Write cycles are executed in synchronization with WCK as  $\overline{W}$  is held low. Bits are input sequentially into one of the two halves of the data

register before being transferred to the storage array. Since data is transferred into the array in blocks of 455 x 4 bits, no data transfer occurs if W goes high to disable write operation before all 455 bits are written. Despite write operation being disabled, the internal bit pointer continues to increment with each successive write clock.

Read Operation. Read cycles are executed in synchronization with RCK (asynchronous operation only) or WCK (synchronous operation only) as  $\overline{OE}$  is held low. If  $\overline{OE}$  goes high any time during a cycle, the outputs are in a state of high impedance until OE returns low. Since the internal bit pointer increments by 1 in spite of read operation being disabled, it is always important to reset the write and read pointers using WCLR and RCLR prior to beginning or resuming operation at the first address location in the array.

### **Special Functions**

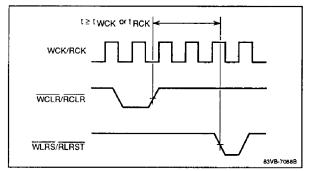

Line Reset. A line reset is similar to an address clear cycle, except that it only affects the bit pointers within a line. While WCLR and RCLR are held high, WLRST or RLRST can be brought low for a minimum of 3  $\mu$ s during successive WCK or RCK cycles to reset the bit pointer to address 0 of the scan line. At the completion of the reset cycle, the next sequential scan line will be selected unless line hold (WLH or RLH) or line jump (WLJ or RLJ) are also used. See WLRST and RLRST for more detail.

A combination of line reset and an address clear cycle must be separated by at least one serial clock cycle. The timing relationship of WCLR, WLRST and WCK (or RCLR, RLRST and RCK) is shown in figure 1.

In asynchronous operation, WLRST and RLRST independently reset the write and read bit pointers. During synchronous operation, WLRST resets both pointers.

Line Jump. With the line jump function, it is possible to advance the current write or read line position according to the number of positive WLJ or RLJ pulses applied (see descriptions for the WLJ and RLJ pins). In this cycle, which is valid in asynchronous mode only, the scan line pointer resets to address 0 if the number of positive pulses causes the resulting line number (n+11+1x, where "n" is the current line number and "x" is the number of positive WLJ or RLJ pulses) to exceed the maximum line number (number of lines minus 1) specified by the LS<sub>0</sub> and LS<sub>1</sub> pins (table 2).

18c

Line Hold. The line hold feature is available in asynchronous mode only and can be used to prevent the internal scan line pointers from incrementing to the next sequential address. The read and write line pointers

may be held independently; however, restrictions pertaining to when this function can be initiated, detailed in the descriptions for the WLH and RLH pins, should be carefully followed.

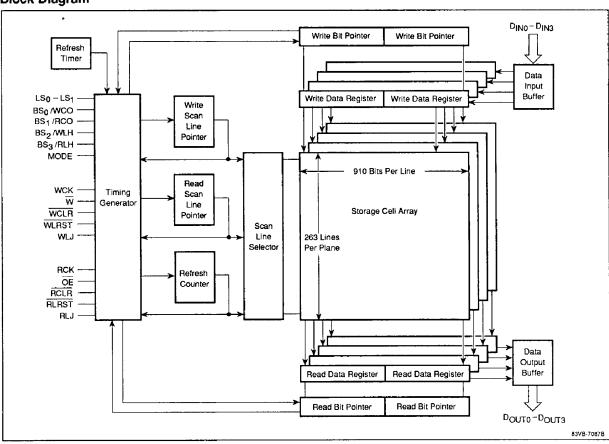

### **Block Diagram**

Figure 1. Separation of Clear and Reset Signals

# **Absolute Maximum Ratings**

| Supply voltage on any pin except V <sub>CC</sub> relative to GND, V <sub>R1</sub> | -1.5 to +7.0 V |

|-----------------------------------------------------------------------------------|----------------|

| Supply voltage on V <sub>CC</sub> relative to GND, V <sub>R2</sub>                | -1.5 to +7.0 V |

| Operating temperature, T <sub>OPR</sub>                                           | -20 to +70°C   |

| Storage temperature, T <sub>STG</sub>                                             | -55 to +125°C  |

| Short-circuit output current, I <sub>OS</sub>                                     | 50 mA          |

| Power dissipation, P <sub>D</sub>                                                 | 1.5 W          |

Exposure to Absolute Maximum Ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage. The device should be operated within the limits specified under DC and AC Characteristics.

18c

# **Recommended Operating Conditions**

| Parameter           | Symbol          | Min  | Тур | Max | Unit |

|---------------------|-----------------|------|-----|-----|------|

| Supply voltage      | Vcc             | 4.5  | 5.0 | 5.5 | ٧    |

| Input voltage, high | V <sub>IH</sub> | 2.4  |     | Vcc | ٧    |

| Input voltage, low  | V <sub>IL</sub> | -1.5 | ·   | 0.8 | ٧    |

| Ambient temperature | T <sub>A</sub>  | -20  |     | 70  | °C   |

### **DC Characteristics**

$T_A = -20 \text{ to } +70^{\circ}\text{C}; V_{CC} = +5.0 \text{ V } \pm 10\%; \text{ GND} = 0 \text{ V}$

| Parameter              | Symbol          | Min | Тур | Max | Unit | Test Conditions                                                         |

|------------------------|-----------------|-----|-----|-----|------|-------------------------------------------------------------------------|

| Input leakage current  | I <sub>IL</sub> | -10 |     | 10  | μΑ   | $V_{IN} = 0 \text{ V to } V_{CC}$ ; all other pins not under test = 0 V |

| Output leakage current | l <sub>OL</sub> | -10 |     | 10  | μΑ   | D <sub>OUT</sub> disabled; V <sub>OUT</sub> = 0 V to V <sub>CC</sub>    |

| Output voltage, high   | V <sub>OH</sub> | 2.4 |     |     | ٧    | I <sub>OH</sub> = -1 mA                                                 |

| Output voltage, low    | V <sub>OL</sub> |     |     | 0.4 | ٧    | I <sub>OL</sub> = 2 mA                                                  |

| Standby current        | lcc1            |     | 6   | 20  | mA   | WCK, RCK = V <sub>IL</sub>                                              |

| Operating current      | lcc2            |     | 40  | 80  | mA   | twck = twck (min); tack = tack (min)                                    |

### **AC Characteristics**

$T_A = -20 \text{ to } +70^{\circ}\text{C}; V_{CC} = +5.0 \text{ V } \pm 10\%; \text{ GND } = 0 \text{ V}$

| Parameter                               | Symbol           | Min | Max | Unit | Test Conditions |

|-----------------------------------------|------------------|-----|-----|------|-----------------|

| Access time from RCK                    | t <sub>AC</sub>  |     | 40  | ns   | ·               |

| Write clock cycle time                  | twck             | 60  |     | ns   | (Note 5)        |

| Write clock active pulse width          | twow             | 20  |     | ns   | -               |

| Write clock precharge time              | twcp             | 20  |     | ns   |                 |

| Read clock cycle time                   | t <sub>RCK</sub> | 60  |     | ns   | (Note 5)        |

| Read clock active pulse width           | t <sub>RCW</sub> | 20  |     | ns   |                 |

| Read clock precharge time               | t <sub>RCP</sub> | 20  |     | ns   |                 |

| Output hold time                        | tон              | 5   |     | ns   |                 |

| Output low impedance delay              | t <sub>LZ</sub>  | 5   | 40  | ns   | (Note 6)        |

| Data output buffer high impedance delay | t <sub>HZ</sub>  | 5   | 40  | ns   | (Note 7)        |

| Input data setup time                   | t <sub>DS</sub>  | 15  |     | ns   |                 |

|                                         |                  |     |     |      |                 |

# µPD42270

# AC Characteristics (cont)

| Parameter                                                            | Symbol            | Min | Max | Unit | Test Conditions                         |

|----------------------------------------------------------------------|-------------------|-----|-----|------|-----------------------------------------|

| input data hold time                                                 | toH               | 3   |     | ns   | =                                       |

| WCLR (RCLR) setup time before the rising edge of WCK (RCK)           | tcs               | 20  |     | ns   | (Note 8)                                |

| WCLR (RCLR) hold time after the rising edge of WCK (RCK)             | tcH               | 3   |     | ns   | (Note 8)                                |

| WCLR (RCLR) invalid hold time after the rising edge of WCK (RCK)     | t <sub>CN1</sub>  | 5   |     | ns   | (Note 8)                                |

| WCLR (RCLR) invalid setup time before the rising edge of WCK (RCK)   | t <sub>CN2</sub>  | 20  |     | ns   | (Note 8)                                |

| WCLR (RCLR) low level valid time                                     | tolr              | 3   |     | μs   |                                         |

| WLRST (RLRST) setup time before the rising edge of WCK (RCK)         | t <sub>LRS</sub>  | 20  |     | ns   | (Note 8)                                |

| WLRST (RLRST) hold time after the rising edge of WCK (RCK)           | <sup>t</sup> LRH  | 3   |     | пѕ   | (Note 8)                                |

| WLRST (RLRST) invalid hold time after the rising edge of WCK (RCK)   | tLRN              | 5   |     | ns   | (Note 8)                                |

| WLRST (RLRST) invalid setup time before the rising edge of WCK (RCK) | tLRN              | 20  |     | ns   | (Note 8)                                |

| WLRST (RLRST) low level valid time                                   | <sup>‡</sup> LRST | 3   |     | μs   |                                         |

| W setup time before the rising edge of WCK                           | tws               | 20  |     | ns   | (Note 9)                                |

| W hold time after the rising edge of WCK                             | twH               | 3   |     | ns   | (Note 9)                                |

| W valid hold time after subline (1/2) switch                         | t <sub>WN1</sub>  | 5   |     | ns   | (Note 9)                                |

| W valid setup time before subline (1/2) switch                       | t <sub>WN2</sub>  | 20  |     | пş   | (Note 9)                                |

| WLH (RLH) setup time before the rising edge of WCK (RCK)             | tLHS              | 20  |     | ns   |                                         |

| WLH (RLH) hold time after the rising edge of WCK (RCK)               | †LHH              | 3   |     | ns   |                                         |

| WLH invalid hold time measured from the end of write cycle 227       | twHN1             | 5   |     | ns   |                                         |

| WLH invalid setup time measured before write cycle 0                 | twHN2             | 20  | •   | ns   |                                         |

| RLH invalid hold time measured from the end of read cycle 681        | t <sub>RHN1</sub> | 5   |     | ns   |                                         |

| RLH invalid setup time measured before read cycle 453                | t <sub>RHN2</sub> | 20  |     | ns   |                                         |

| WLJ (RLJ) setup time before the rising edge of WCK (RCK)             | t <sub>LJS</sub>  | 20  |     | ns   |                                         |

| WLJ (RLJ) hold time after the rising edge of WCK (RCK)               | t <sub>LJH</sub>  | 3   |     | ns   |                                         |

| WLJ hold time measured from the end of write cycle 227               | twun1             | 5   |     | ns   |                                         |

| WLJ setup time measured before write cycle 0                         | twJN2             | 20  |     | ns   |                                         |

| RLJ hold time measured from the end of read cycle 681                | t <sub>RJN1</sub> | 5   |     | ns   |                                         |

| RLJ setup time measured before read cycle 453                        | t <sub>RJN2</sub> | 20  |     | ns   |                                         |

| OE setup time before the rising edge of RCK (WCK)                    | toes              | 20  |     | ns   | (Note 9)                                |

| OE hold time after the rising edge of RCK (WCK)                      | toEH              | 3   |     | ns   | (Note 9)                                |

| OE valid hold time after the rising edge of RCK (WCK)                | toen1             | 5   |     | ns   | (Note 9)                                |

| OE valid setup time before the rising edge of RCK (WCK)              | <sup>t</sup> OEN2 | 20  |     | ns   | (Note 9)                                |

| LS, BS setup time before WCK (RCK), line 258                         | trss              | 0   |     | ns   |                                         |

| LS, BS hold time after WCK (RCK), line 0                             | trsh              | 3   |     | μs   | , ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

| Write carry output high level delay                                  | twcl H            |     | 40  | ns   |                                         |

### AC Characteristics (cont)

| Parameter                          | Symbol            | Min | Max | Unit | Test Conditions |

|------------------------------------|-------------------|-----|-----|------|-----------------|

| Write carry output low level delay | ₩cнг              |     | 40  | ns   |                 |

| Read carry output high level delay | <sup>t</sup> RCLH |     | 40  | ns   |                 |

| Read carry output low level delay  | t <sub>RCHL</sub> |     | 40  | ns   |                 |

| Transition time                    | tŢ                | 3   | 35  | ns   | (Note 4)        |

#### Notes:

- (1) All voltages are referenced to GND

- (2) Ac measurements assume  $t_T = 5$  ns.

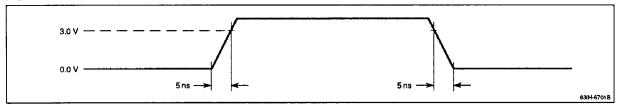

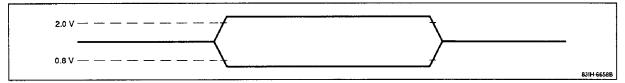

- (3) Input timing reference levels = 1.5 V; input levels are measured between GND and 3.0 V; output levels are measured between 0.8 and 2.0 V. See figures 2 and 3.

- (4) V<sub>IH</sub> (min) and V<sub>IL</sub> (max) are reference levels for measuring the timing of input signals. Transition times are measured between V<sub>IH</sub> and V<sub>IL</sub>.

- (5) The minimum specifications are used only to indicate the cycle time at which proper operation over the full temperature range (T<sub>A</sub> = -20 to 70°C) is assured.

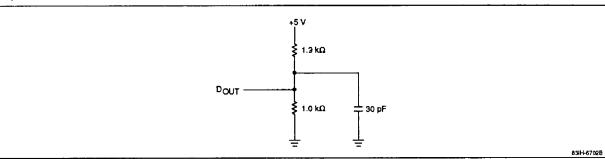

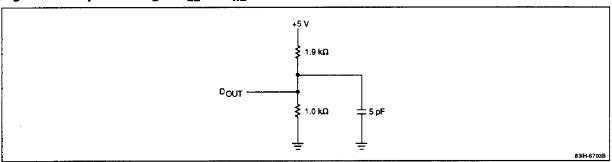

- (6) This delay is measured at -200 mV from the steady-state voltage with the load specified in figure 5.

- (7) This delay is measured at the maximum steady-state output high voltage -200 mV or the minimum steady-state output low voltage +200 mV with the load specified in figure 5.

- (8) For proper execution of the pointer clear and line reset functions, specifications for t<sub>CS</sub>, t<sub>CH</sub>, t<sub>CN1</sub>, t<sub>CN2</sub>, t<sub>LRS</sub>, t<sub>LRH</sub>, t<sub>LRN1</sub> and t<sub>LRN2</sub> must be met; otherwise, these functions may not affect the desired cycles or may affect adjacent cycles erroneously.

- (9) If a W (or OE) pulse does not satisfy the specifications for tws, twh, twh1 and twn2 (or toes, toeh, toen1 and toen2), the write disable function (output high impedance) being executed may not affect the desired cycles or may affect adjacent cycles erroneously.

- (10) For the μPD42270 to read new data, read operation must be delayed from write operation by at least 920 cycles. In those cases where the delay is less than 920 cycles, read data will vary as shown below:

| Source of Read Data                    | Delay Between Write<br>and Read Operation |  |  |

|----------------------------------------|-------------------------------------------|--|--|

| Old data                               | 0 to 450 cycles                           |  |  |

| Indeterminate (either old or new data) | 451 to 919 cycles                         |  |  |

| New data                               | 920 or more cycles                        |  |  |

18c

Figure 2. Input Timing

Figure 3. Output Timing

Figure 4. Output Loading for tAC, tOH, tWCLH, tWCHL, tRCLH, tRCHL

Figure 5. Output Loading for  $t_{LZ}$  and  $t_{HZ}$

# **Timing Waveforms**

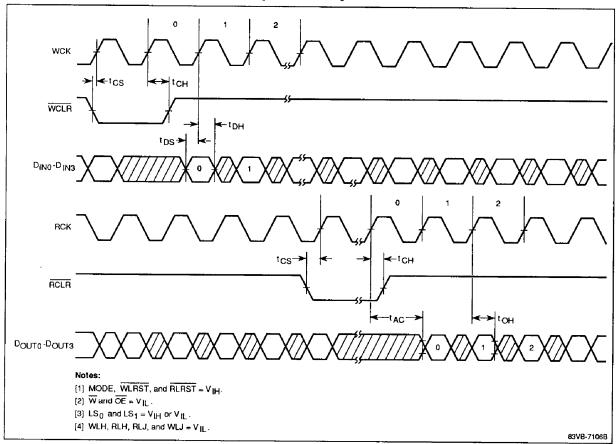

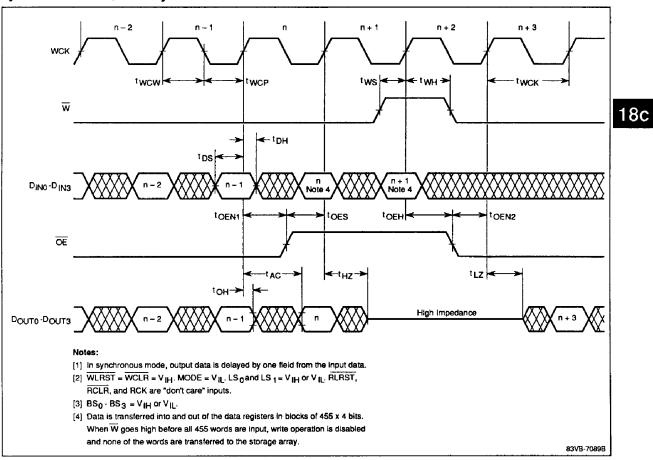

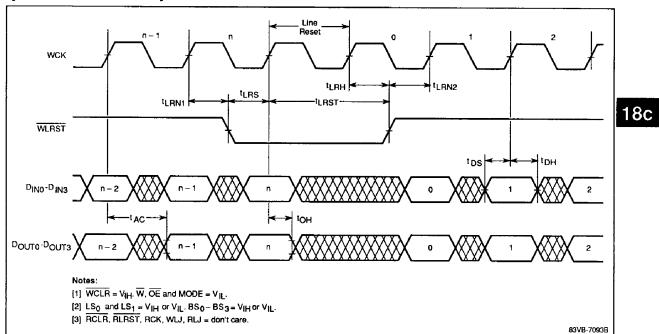

### Synchronous Write/Read Cycle

# Asynchronous Write and Read Cycles

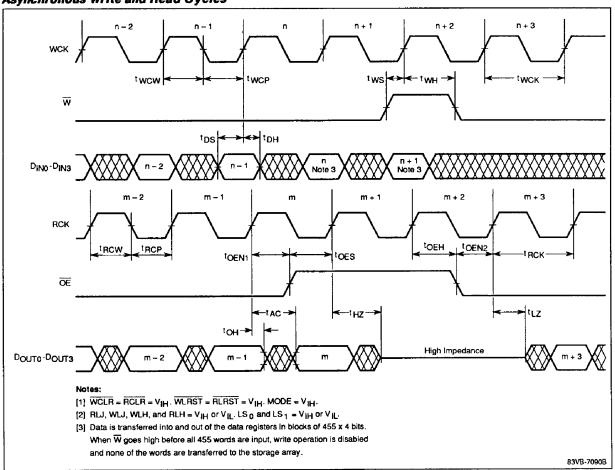

# Synchronous Pointer Clear Cycle

# Asynchronous Pointer Clear Cycle

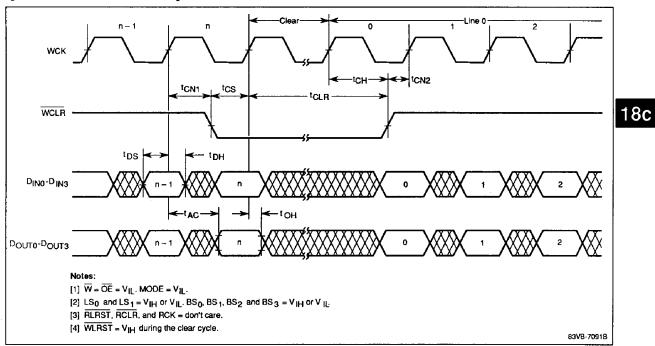

# Synchronous Line Reset Cycle

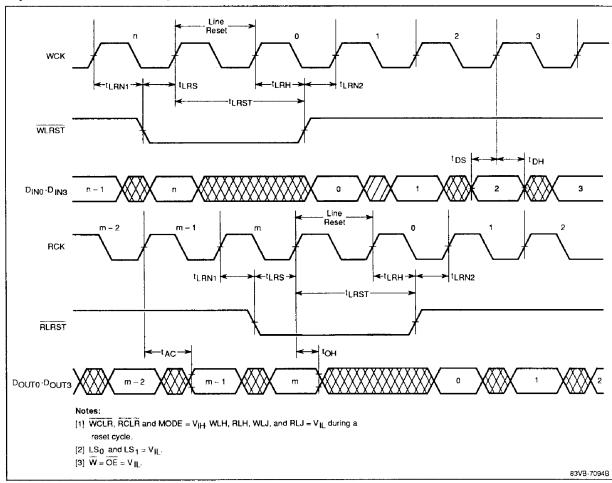

# Asynchronous Line Reset Cycle

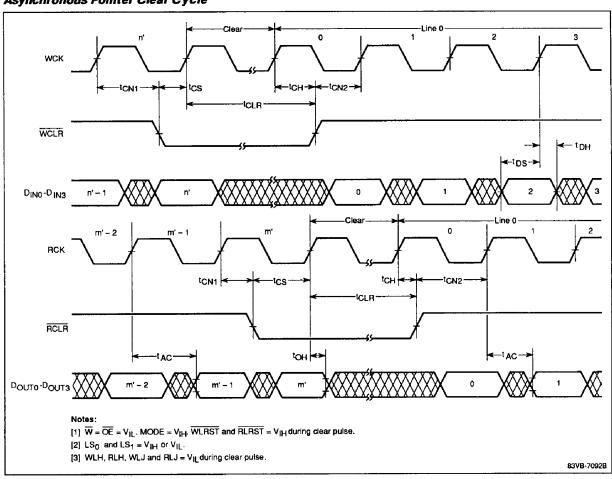

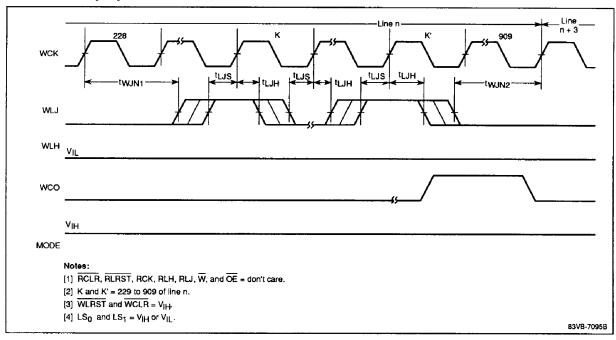

# Write Line Jump Cycle

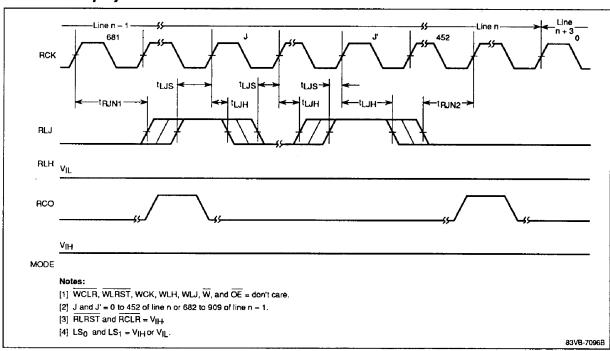

### Read Line Jump Cycle

18C-17 ·

# Write Line Hold Cycle

18c

# Timing Waveforms (cont)

# Synchronous Field Buffer Size Adjustment

# Asynchronous Field Buffer Size Adjustment

# Write Register Carry Out

# Read Register Carry Out

### **APPLICATION EXAMPLES**

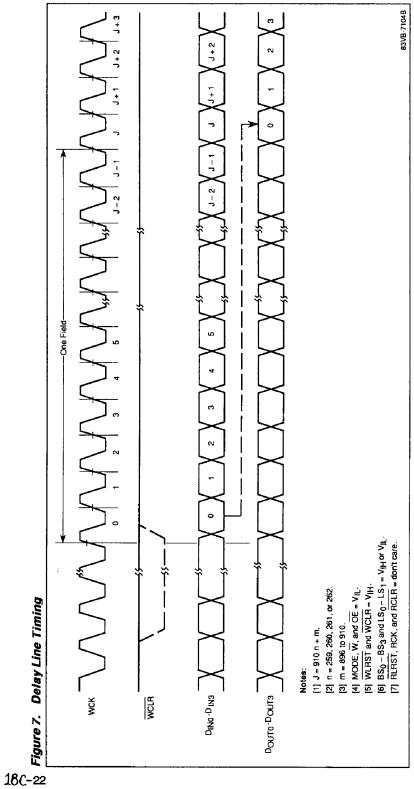

### **Delay Line**

The synchronous mode may be used to create a full-field delay line with a fixed length (figures 6 and 7). Useful video applications include field interpolation, interframe noise reduction, and separation of luminance (Y) and chrominance (C) signals. In these applications, field buffer size is determined by the logic levels applied to pins LS $_{\rm 0}$  - LS $_{\rm 1}$  and BS $_{\rm 0}$  - BS $_{\rm 3}$ . The former allows variation of the number of lines from 260 to 263, while the latter controls the actual line length at 896 to 910 bits for the last line. The actual delay between data being written into D $_{\rm IN}$  and read on D $_{\rm OUT}$  is controlled by the WCK clock period and the con figured size of the buffer.

### Frame Synchronization or Time Base Correction

The  $\mu$ PD42270 has the capability of executing asyn chronous write and read cycles by independently clocking WCK and RCK, respectively. The feature is

useful in applications requiring frame synchronization, time base correction or buffering, where WCK, RCK, WCLR and RCLR may all have variable time periods. In addition, the write carry out (WCO) and read carry out (RCO) options give a positive indication when the bit pointer reaches the end of the line.

# Vertical or Horizontal Image Compression and Expansion

Vertical compression and expansion of the video image may be accomplished by means of the line jump or line hold functions. Compression occurs when WLJ or RLJ are used to jump over lines that are not to be displayed. Expansion occurs when the WLH or RLH line hold signals are used to display a line multiple times.

Horizontal compression and expansion can be achieved by modifying the cycle time of the WCK and RCK clocks, and by using the WLRST and RLRST line reset signals.

Figure 6. Example of Delay Line

Figure 8. Example of Frame Synchronization/Time Base Correction

Figure 9. Asynchronous Read/Write Timing for Frame Synchronization or Time Base Correction