# TONE/PULSE DIALER WITH TWO-STAGE REDIAL FUNCTION

#### **GENERAL DESCRIPTION**

The W91610 series are Si-gate CMOS ICs that provide the signals needed for either pulse or tone dialing.

#### **FEATURES**

- DTMF/Pulse switchable dialer

- 32-digit redial memory

- Two-stage redial function

- Pulse-to-tone ( $P\rightarrow T$ ) keypad for long distance call operation

- $\bullet$  Easy operation with redial, flash, pause and P $\rightarrow$ T keypads

- Pause, pulse-to-tone (P→T) can be stored as a digit in memory

- Tone output duration: as long as key is depressed or 90 mS minimum

- Minimum intertone pause: 90 mS

- Flash time: 100 mSUses 4 × 5 keyboard

- On-chip power-on reset

- Uses 3.579545 MHz crystal or ceramic resonator

- Packaged in 18-pin DIP

- The different dialers in the W91610 series are shown in the following table:

| TYPE NO. | DIALING RATE | PAUSE | B:M | FLASH  |

|----------|--------------|-------|-----|--------|

| W91610   | 10 ppS       | 4 sec | 2:1 | 100 mS |

| W91611   |              |       | 3:2 |        |

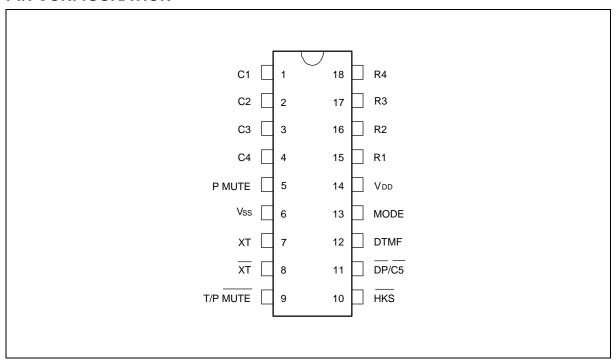

#### **PIN CONFIGURATION**

#### **PIN DESCRIPTION**

| SYMBOL     | PIN NO. | I/O  | FUNCTION                                                                                                                                                |

|------------|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Column-    | 1–4     | 1    | Keyboard inputs are designed for use with either a standard $4 \times 5$                                                                                |

| Row Inputs | &       |      | keyboard or an inexpensive single contact (Form A) keyboard.                                                                                            |

|            | 15–18   |      | Electronic input from a μC can also be used.                                                                                                            |

|            |         |      | Valid key entry is defined by a connection between a single row and a single column.                                                                    |

| XT, XT     | 7, 8    | I, O | A built-in inverter provides oscillation with an inexpensive 3.579545 MHz crystal or ceramic resonator.                                                 |

| T/P MUTE   | 9       | 0    | The T/P MUTE is a conventional CMOS inverter output. It is low during pulse and tone mode dialing sequence and flash break; otherwise, it remains high. |

| MODE       | 13      | I    | Pulling the mode pin to Vss place the dialer in tone mode.                                                                                              |

|            |         |      | Pull to VDD or leave floating: Pulse mode (10 ppS, M/B = 2:3 or 1:2)                                                                                    |

Pin Description, continued

| SYMBOL   | PIN NO. | I/O |            |                                                                                                               | F          | UNCTION     |                                                       |  |  |  |

|----------|---------|-----|------------|---------------------------------------------------------------------------------------------------------------|------------|-------------|-------------------------------------------------------|--|--|--|

| HKS      | 10      | I   |            | Hook switch input. Conventional CMOS input with an internal protection diode and a pull-high resistor to VDD. |            |             |                                                       |  |  |  |

|          |         |     | HKS = V    | D: On-hoo                                                                                                     | k state. C | Chip in sle | ep mode, no operation.                                |  |  |  |

|          |         |     | HKS = Vs   | ss: Off-hoo                                                                                                   | k state. C | Chip enabl  | led for normal operation.                             |  |  |  |

|          |         |     |            | aling, this i<br>mS (i.e., d                                                                                  |            |             | = VDD for durations of less ated).                    |  |  |  |

| DP/C5    | 11      | 0   | •          | in dialing p<br>causes D                                                                                      |            | , •         | e 1).<br>n both tone mode and pulse                   |  |  |  |

| DTMF     | 12      | 0   |            | ılse dialing<br>ode, outpu                                                                                    |            |             | te at all times.<br>tone.                             |  |  |  |

|          |         |     | Detailed t | iming diag                                                                                                    | ram for to | one mode    | is shown in Figure 2(a, b).                           |  |  |  |

|          |         |     |            | OUTPUT                                                                                                        | FREQUEN    | CY          |                                                       |  |  |  |

|          |         |     |            | Specified                                                                                                     | Actual     | Error %     |                                                       |  |  |  |

|          |         |     | R1         | 697                                                                                                           | 699        | +0.28       |                                                       |  |  |  |

|          |         |     | R2         | 770                                                                                                           | 766        | -0.52       |                                                       |  |  |  |

|          |         |     | R3         | 852                                                                                                           | 848        | -0.47       |                                                       |  |  |  |

|          |         |     | R4         | 941                                                                                                           | 948        | +0.74       |                                                       |  |  |  |

|          |         |     | C1         | 1209                                                                                                          | 1216       | +0.57       |                                                       |  |  |  |

|          |         |     | C2         | 1336                                                                                                          | 1332       | -0.30       |                                                       |  |  |  |

|          |         |     | C3         | 1477                                                                                                          | 1472       | -0.34       |                                                       |  |  |  |

| VDD, VSS | 14, 6   | I   | Power inp  | out pins.                                                                                                     |            |             |                                                       |  |  |  |

| P MUTE   | 5       | 0   |            | lse dialing                                                                                                   |            |             | inverter output. It is high<br>h break. Otherwise, it |  |  |  |

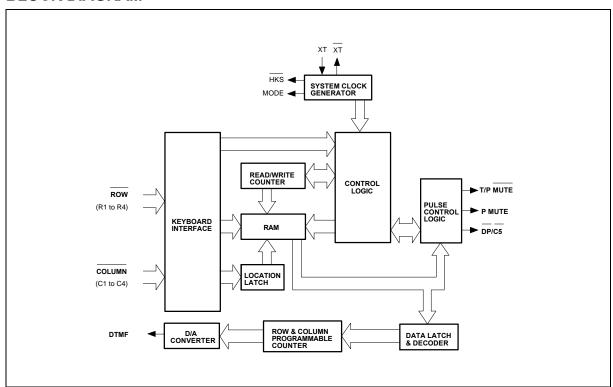

#### **BLOCK DIAGRAM**

#### **FUNCTIONAL DESCRIPTION**

### **Keyboard Operation**

| C1 | C2 | C3 | C4 | DP/C5 |    |

|----|----|----|----|-------|----|

| 1  | 2  | 3  |    | P→T   | R1 |

| 4  | 5  | 6  | F  | Р     | R2 |

| 7  | 8  | 9  |    |       | R3 |

| *  | 0  | #  | R  |       | R4 |

- F: Flash key

- P→T: In pulse mode, this key works as Pulse→Tone key

P→T key can be stored as a digit in pulse or tone mode

- R: Redial function key

- P: Pause key

#### **Normal Dialing**

1. D1, D2, ..., Dn will be dialed out.

- 2. Dialing length is unlimited, but redial is inhibited if length oversteps 32 digits in normal dialing.

- 3. Dialing mode is determined at the on/off hook transition.

#### Redialing

2. Redial content = D1, D2, ..., Dn

- a. D1, D2, ..., Dn, D1', D2', P→T, D3', D4' will be dialed out.

- b. Redial register is changed to D1, D2, ..., Dn, D1', D2', P→T, D3', D4'.

D1, D2, ..., Dn, D1', D2', will be dialed out.

#### **Access Pause**

- 1. The pause function can be stored in memory.

- 2. The pause function may be executed in normal dialing, redialing, or memory dialing (4.0 sec/pause).

- 3. The pause function can be stored as the first digit in memory.

- 4. The pause time depends on the number of times the P key is depressed. For example, if the sequence 1, 2, P, P, 4, 5, 6 is keyed in, then the pause time is 8 seconds.

- 5. The pause function timing diagram is shown in Figure 3.

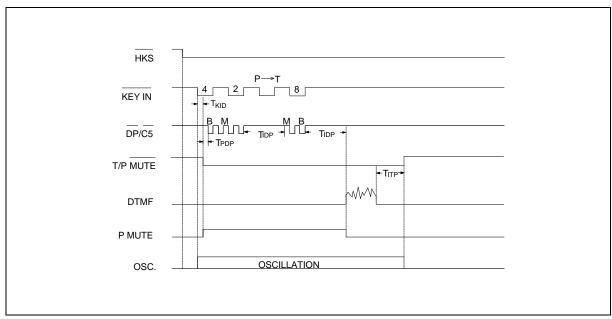

#### Pulse-to-tone (P→T)

1. OFF HOOK , D1 , D2 , ..., Dn ,

$$P \rightarrow T$$

,  $D1'$  ,  $D2'$  , ...,  $Dn'$

a. If the mode switch is set to pulse mode, then the output signal will be as follows:

In this case, the device can be reset to pulse mode only by going on-hook, because tone mode remains enabled after the digits have been dialed out.

|  | b. | If the | mode | switch i | s set to | tone | mode. | then the | output | signal | will be | as fo | llows |

|--|----|--------|------|----------|----------|------|-------|----------|--------|--------|---------|-------|-------|

|--|----|--------|------|----------|----------|------|-------|----------|--------|--------|---------|-------|-------|

D1, D2, ..., Dn, no pause, D1', D2', ..., Dn' (Tone) (Tone)

c. The P→T key may be pressed before the first sequence is dialed out completely.

2. OFF HOOK , R

a. If the mode switch is set to pulse mode, then the output signal will be as follows:

D1, D2, ..., Dn (Pulse)

b. In the first redial operation, only the digits before the tone key are dialed out.

R (2nd)

D1', D2', ..., Dn' are dialed out.

(Tone)

c. In the second redial operation, the digits after the tone key are dialed out.

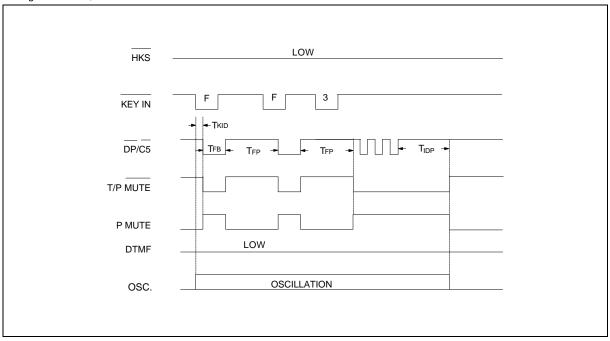

#### Flash

OFF HOOK , D1 , D2 , D3 , F , D4 , D5 , D6

1. The F key may be pressed before digits D1, D2, D3 are sent completely. Digits D4, D5, D6 may

be pressed during the 100 mS. flash period.

- 2. The flash key cannot be stored as a digit in memory or in the redial register.

- 3. The content of the redial register is D1, D2, D3, D4, D5, D6.

The register.

F key is not stored in the redial

- 4. The flash does not have first priority among the keyboard functions.

- 5. The flash pause time is 800 mS, so there is a pause of 800 mS between the flash and the next digit dialed (see Figure 5).

- 6. The dialer will not return to the initial state after the flash break time has elapsed.

- 7. The flash function timing diagram is shown in Figure 5.

#### ABSOLUTE MAXIMUM RATINGS

| PARAMETER            | SYMBOL  | RATING       | UNIT |

|----------------------|---------|--------------|------|

| DC Supply Voltage    | VDD-VSS | -0.3 to +7.0 | V    |

|                      | VIL     | Vss -0.3     | V    |

| Input/Output Voltage | ViH     | VDD +0.3     | V    |

|                      | Vol     | Vss -0.3     | V    |

|                      | Voн     | VDD +0.3     | V    |

| Power Dissipation     | PD   | 120         | mW |

|-----------------------|------|-------------|----|

| Operating Temperature | Topr | -20 to +70  | °C |

| Storage Temperature   | Тѕтс | -55 to +150 | °C |

Note: Exposure to conditions beyond those listed under Absolute Maximum Ratings may adversely affect the life and reliability of the device.

#### **DC CHARACTERISTICS**

(Fosc. = 3.58 MHz, Ta = 25° C, all outputs unloaded)

| PARAMETER                              | SYM. | CONDITIONS                             | MIN. | TYP. | MAX. | UNIT  |

|----------------------------------------|------|----------------------------------------|------|------|------|-------|

| Operating Voltage                      | Vdd  | -                                      | 2.0  | -    | 5.5  | V     |

| Operating Current                      | ЮР   | Tone, VDD = 2.5V                       | -    | 0.30 | 0.50 | mA    |

|                                        |      | Pulse, VDD = 2.5V                      | -    | 0.15 | 0.30 |       |

| Standby Current                        | ISB  | HKS = 0, No load & No key entry        | -    | -    | 15   | μΑ    |

| Memory Retention<br>Current            | IMR  | HKS = 1, VDD = 1.0V                    | -    | -    | 0.2  | μΑ    |

| DTMF Output Voltage                    | Vто  | Row group, $RL = 5 \text{ K}\Omega$    | 130  | 150  | 170  | mVrms |

| Pre-emphasis                           |      | Col/Row,<br>VDD = 2.0 to 5.5V          | 1    | 2    | 3    | dB    |

| DTMF Distortion                        | THD  | RL = 5 K $\Omega$<br>VDD = 2.0 to 5.5V | -    | -30  | -23  | dB    |

| DTMF Output DC Level                   | VTDC | RL = 5 K $\Omega$<br>VDD = 2.0 to 5.5V | 1.0  | -    | 3.0  | V     |

| DTMF Output Sink<br>Current            | lτι  | VTO = 0.5V<br>VDD = 2.5V               | 0.2  | -    | -    | mA    |

| DP/C5 Output Sink<br>Current           | lpL  | VPO = 0.5V<br>VDD = 2.5V               | 0.5  | -    | -    | mA    |

| P MUTE & T/P MUTE Output Drive Current | Імн  | VMO = 2.0V<br>VDD = 2.5V               | 0.2  | -    | -    | mA    |

| P MUTE & T/P MUTE Output Sink Current  | IML  | VMO = 0.5V, VDD = 2.5V                 | 0.5  | -    | -    | mA    |

| Keypad Input Drive<br>Current          | lkd  | VI = 0V, VDD = 2.5V                    | 4    | -    | -    | μΑ    |

| Keypad Input Sink<br>Current           | lks  | VI = 2.5V, VDD = 2.5V                  | 200  | 400  | -    | μΑ    |

| Keypad Resistance                      | Rĸ   | -                                      | -    | -    | 5.0  | ΚΩ    |

| HKS Input Pull High<br>Resistance      | Rнк  | -                                      | -    | 300  | -    | ΚΩ    |

| Input Voltage Low Level  | VIL | Pins 1, 2, 3, 4, 10, 13, | 0          | - | 0.2<br>Vdd | V |

|--------------------------|-----|--------------------------|------------|---|------------|---|

| Input Voltage High Level | VIH | 15, 16, 17, 18           | 0.8<br>Vdd | 1 | Vdd        | V |

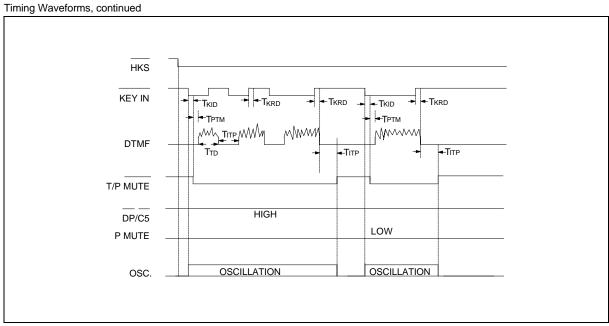

### **AC CHARACTERISTICS**

| PARAMETER                       | SYMBOL | CONDITIONS          | MIN. | TYP.  | MAX. | UNIT |

|---------------------------------|--------|---------------------|------|-------|------|------|

| Keypad Active in Debounce       | TKID   | -                   | -    | 20    | -    | mS   |

| Key Release Debounce            | TKRD   | -                   | -    | 20    | -    | mS   |

| Pre-digit Pause                 | TPDP1  | Mode Pin = Floating | -    | 33.3  | -    | mS   |

|                                 | 10 ppS | Mode Pin = VDD      | -    | 40    | -    |      |

| Interdigit Pause (Auto Dialing) | TIDP   | 10 ppS              | -    | 800   | -    | mS   |

| Make/Break Ratio                | M/B    | M/B = 1:2           | -    | 33:67 | -    | %    |

|                                 |        | M/B = 2:3           | -    | 40:60 | -    |      |

| DTMF Output Duration            | TTD    | Auto Dialing        | -    | 90    | -    | mS   |

| Intertone Pause                 | TITP   |                     | -    | 90    | -    | mS   |

| Flash Break Time                | Тғв    | -                   | -    | 100   | -    | mS   |

| Flash Pause                     | TFP    | -                   | -    | 800   | -    | mS   |

| Pause Time                      | ТР     | -                   | -    | 4.0   | -    | S    |

| Pre-tone Mute                   | Тртм   | -                   | -    | 70    | -    | mS   |

#### Notes:

<sup>1.</sup> Crystal parameters suggested for proper operation are Rs < 100  $\Omega$ , Lm = 96 mH, Cm = 0.02 pF, Cn = 5 pF, Cl = 18 pF, Fosc. = 3.579545 MHz  $\pm$ 0.02%.

<sup>2.</sup> Crystal oscillator accuracy directly affects these times.

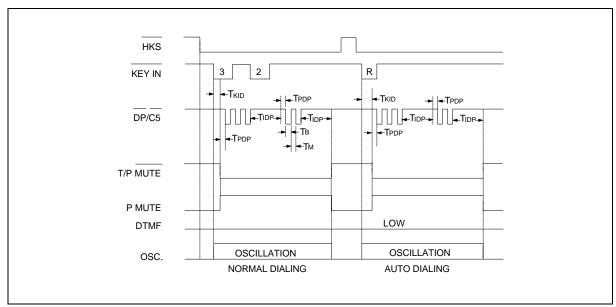

#### **TIMING WAVEFORMS**

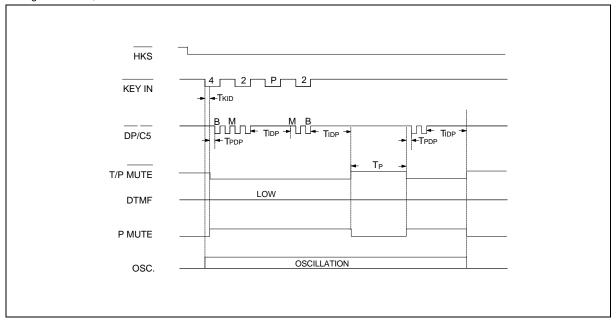

Figure 1. Pulse Mode Timing Diagram

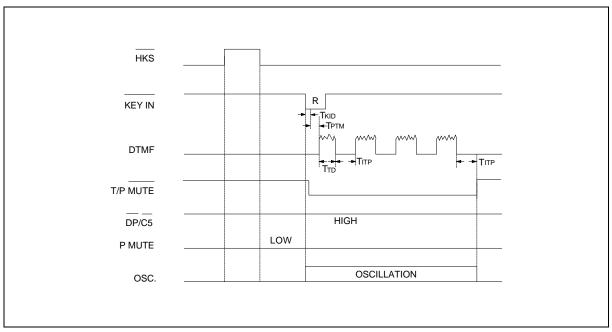

Figure 2(a). Tone Mode Normal Dialing Timing Diagram

Figure 2(b). Tone Mode Auto Dialing Timing Diagram

#### Timing Waveforms, continued

Figure 3. Pause Function Timing Diagram

Figure 4. P→T Operation Timing Diagram in Normal Dialing

#### Timing Waveforms, continued

Figure 5. Flash Operation Timing Diagram

#### **Headquarters**

No. 4, Creation Rd. III, Science-Based Industrial Park, Hsinchu, Taiwan TEL: 886-3-5770066 FAX: 886-3-5792697 http://www.winbond.com.tw/ Voice & Fax-on-demand: 886-2-7197006

**Taipei Office**

11F, No. 115, Sec. 3, Min-Sheng East Rd., Taipei, Taiwan TEL: 886-2-7190505 FAX: 886-2-7197502

Winbond Electronics (H.K.) Ltd. Rm. 803, World Trade Square, Tower II, 123 Hoi Bun Rd., Kwun Tong, Kowloon, Hong Kong TEL: 882-27516023 FAX: 852-27552064 Winbond Electronics North America Corp. Winbond Memory Lab.

Winbond Microelectronics Corp.

Winbond Systems Lab.

2730 Orchard Parkway, San Jose,

CA 95134, U.S.A.

TEI · 1.408.9436666

TEL: 1-408-9436666 FAX: 1-408-9436668

Note: All data and specifications are subject to change without notice.