TOSHIBA TC9256,57P/F

TOSHIBA CMOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# TC9256P, TC9256F, TC9257P, TC9257F

#### PLL FOR DTS

TC9256P, TC9256F, TC9257P and TC9257F are phase-locked loop (PLL) LSIs for digital tuning systems (DTS) with built-in 2 modulus prescalers.

All functions are controlled through 3 serial bus lines. These LSIs are used to configure high-performance digital tuning systems.

#### **FEATURES**

- Optimal for configuring digital tuning systems in high-fituners and car stereos.

- Built-in prescalers. Operate at input frequency ranging from 30~150MHz during FM<sub>IN</sub> input (with 2 modulus prescaler) and at 0.5~40MHz during AM<sub>IN</sub> input (with 2 modulus prescaler or direct dividing).

- 16bit programmable counter, dual parallel output phase comparator, crystal oscillator and reference counter.

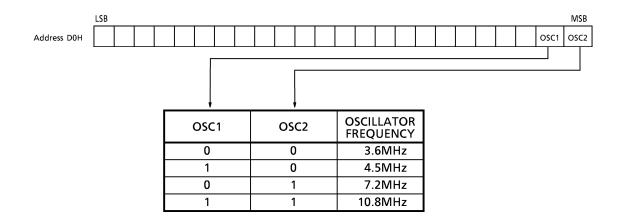

- 3.6MHz, 4.5MHz, 7.2MHz or 10.8MHz crystal oscillators can be used.

- 15 possible reference frequencies. (When using 4.5MHz crystal) (Ref. = 0.5k, 1k, 2.5k, 3k, 3.125k, 3.90625k, 5k, 6.25k, 7.8125k, 9k, 10k, 12.5k, 25k, 50k and 100kHz).

- Built-in 20bit general-purpose counter for such uses as measuring intermediate frequencies (IF<sub>IN1</sub> and IF<sub>IN2</sub>) and low-frequency pilot signal cycles (SC<sub>IN</sub>). (Cycle measurement function is not available on TC9256P and TC9256F.)

- High-precision ( $\pm 0.55 \sim \pm 7.15 \mu s$ ) PLL phase error detection.

- Numerous general-purpose I/O pins for such uses as peripheral circuit control.

- 4 N-channel open-drain output ports (OFF withstanding voltage: 12V) for such uses as control signal output. (TC9256P and TC9256F have only 3 ports.)

- Standby mode function (turns off FM, AM and IF amps) to save current consumption.

- All functions controlled through 3 serial bus lines.

- CMOS structure with operating power supply range of VDD = 5.0 ± 0.5V.

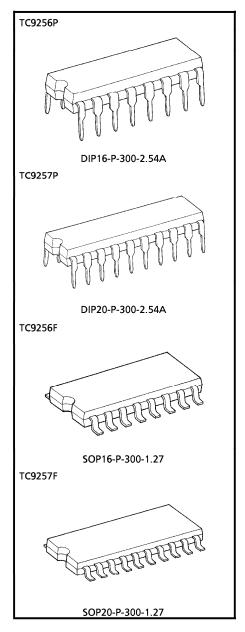

● 16pin DIP (TC9256P), 20pin DIP (TC9257P), 16pin SOP (TC9256F) 20pin SOP (TC9257F) SOP16-P-3001.27 : 0.16g (Typ.) 5OP20-P-3001.27 : 0.48g (Typ.)

packages.

980508EBA2

TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

TOSHIBA TC9256,57P/F

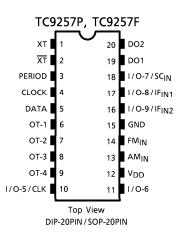

#### **PIN CONNECTION**

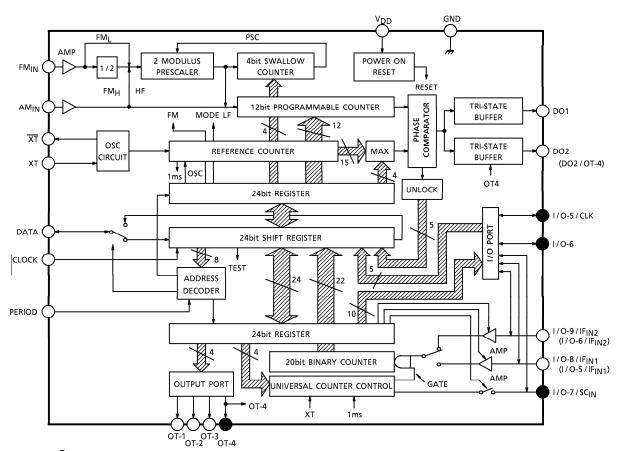

#### **BLOCK DIAGRAM**

(Note)

Mark terminals are not existence in TC9256P, TC9256F.

Terminal name of TC9256P, TC9256F is shown in parentheses.

Others are common terminals.

980508EBA2'

The products described in this document are subject to foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

1998-05-15 2/33

## PIN FUNCTION

| PIN<br>No. | SYMBOL           | PIN NAME                     | FUNCTION                                                                                                                                    | CIRCUIT DIAGRAM       |

|------------|------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 1          | XT               | Crystal oscillator pins      | Connects 3.6MHz, 4.5MHz, 7.2MHz or 10.8MHz crystal                                                                                          | r Ev <sub>DD</sub>    |

| 2          | XT               |                              | oscillator to supply reference frequency and internal clock.                                                                                | XT JE J               |

| 3          | PERIOD           | Period signal input          | Serial I/O ports. These pins transfer data to and from the                                                                                  | T OOO O               |

| 4          | CLOCK            | Clock signal input           | controller to set divisors and dividing modes, and to control                                                                               | Schmitt Schmitt input |

| 5          | DATA             | Serial data input/<br>output | the general-purpose counter and general-purpose I/O ports.                                                                                  | DATA CLOCK, PERIOD    |

| 6          | OT-1             |                              | N channel open drain port pins, for such uses as control signal                                                                             |                       |

| 7          | OT-2             | General-purpose              | output. These pins are set to the OFF                                                                                                       | <b>○</b>              |

| 8          | OT-3             | output ports                 | state when power is turned on.<br>(On TC9256P and TC9256F, OT-4                                                                             | N-channel open drain  |

| 9 (-)      | OT-4             |                              | can be used as a CMOS output pin by switching it with DO2.)                                                                                 |                       |

| 10<br>(-)  | 1 / O-5 /<br>CLK | General-purpose 1/O          | CMOS structure allows free use of<br>these ports for input or output.<br>Ports are set for input when the<br>power is turned on. On TC9257P | V <sub>DD</sub>       |

| 11 (-)     | I / O-6          | ports                        | and TC9257F, I/O-5 can be switched for use as a system clock output pin.                                                                    |                       |

| 13<br>(10) | AMIN             | Programmable                 | These pins input FM and AM band local oscillator signals by                                                                                 | VDD                   |

| 14<br>(11) | FM <sub>IN</sub> | counter input                | capacitor coupling. $FM_{IN}$ and $AM_{IN}$ operate at low amplitude.                                                                       |                       |

| PIN<br>No. | SYMBOL                     | PIN NAME                                                                    | FUNCTION                                                                                                                                                                                                                                             | CIRCUIT DIAGRAM                           |

|------------|----------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| 16<br>(13) | I / O-9 (-6)<br>/ IFIN2    | General-purpose I/O ports / General-purpose                                 | General-purpose I/O port input/<br>output pins. Can be switched for<br>use as input pins to measure<br>general-purpose counter<br>frequencies. The frequency<br>measurement function has such<br>uses as measuring intermediate<br>frequencies (IF). | VDD - I I I I I I I I I I I I I I I I I I |

| 17<br>(14) | I / O-8 (-5)<br>/ IFIN1    | counter frequency<br>measurement<br>input                                   | These pins feature built-in amps.  Data are input by capacitor coupling. FMIN and AMIN operate at low amplitude.  (Note) Pins are set for input when power is turned on.                                                                             |                                           |

| 18 (-)     | 1/O-7<br>/SC <sub>IN</sub> | General-purpose I/O ports / General-purpose counter cycle measurement input | General-purpose I/O port input/output pin. Can be switched for use as signal input pin to measure low-frequency signal cycles. (Not available on TC9256P and TC9256F.)  (Note) This pin is set for input when power is turned on.                    |                                           |

| 19<br>(15) | DO1                        | Phase comparator output                                                     | These pins are for phase comparator tristate output. DO1 and DO2 are output in parallel.                                                                                                                                                             | V <sub>DD</sub> +                         |

| 20<br>(16) | DO2<br>(DO2<br>/ OT-4)     | (General-purpose output ports)                                              | (On TC9256P and TC9256F, DO2 can be switched for use as a general-purpose output port.)                                                                                                                                                              | <i>m</i>                                  |

| 15<br>(12) | GND                        | Power supply pins                                                           | Applies 5.0V ± 10%.                                                                                                                                                                                                                                  | _                                         |

| 12<br>(9)  | $V_{DD}$                   |                                                                             | ,,                                                                                                                                                                                                                                                   |                                           |

- (\*) Pin numbers 1~8 are common to TC9256P, TC9256F, TC9257P and TC9257F.

- (\*) Pin names and numbers in parentheses apply to TC9256P and TC9256F.

#### **FUNCTIONS AND OPERATION**

#### O Serial I/O ports

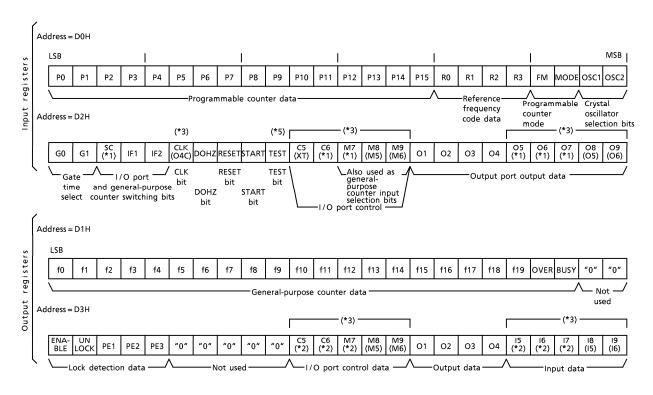

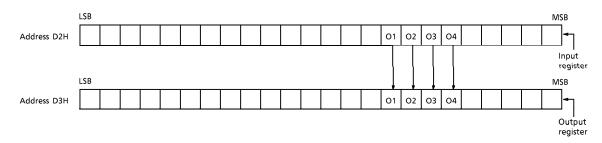

As the block diagram shows, the functions of TC9256P, TC9256F, TC9257P and TC9257F are controlled by setting data in the 48 bits contained in each of the 2 sets of 24bit registers. Each bit of data in these registers is transferred through the serial ports between the controller and the DATA, CLOCK and PERIOD pins. Each serial transfer consists of a total of 32 bits, with 8 address bits and 24 data bits.

Since all functions are controlled in units of registers, the explanation in this manual focuses on the 8bit addresses and functions of each register.

These registers consist of 24 bits and are selected by an 8bit address.

A list of the address assignment for each register is given below under Register assignments.

| REGISTER            | ADDRESS | CONTENTS OF 24 BITS                                         | No. OF BITS |

|---------------------|---------|-------------------------------------------------------------|-------------|

|                     |         | PLL divisor setting                                         | 16          |

| lanut               |         | Reference frequency setting                                 | 4           |

| Input<br>Register 1 | D0H     | PLL input and mode setting                                  | 2           |

| Register            |         | Crystal oscillator selection                                | 2           |

|                     |         |                                                             | Total 24    |

|                     |         | General-purpose counter control                             | 4           |

|                     |         | (including lock detection bit control)                      |             |

|                     |         | I/O port and general-purpose counter switching bits         | 3           |

|                     |         | I/O-5/CLK pin switching bit                                 | 1 1         |

| Input               |         | (DO2/OT-4 pin switching bit for TC9256P and TC9256F)        |             |

| Register 2          | D2H     | DO pin control                                              | 1           |

| inegister 2         |         | Test bit                                                    | 1           |

|                     |         | I/O port control                                            | 5           |

|                     |         | (also used as general-purpose counter input selection bits) |             |

|                     |         | Output data                                                 | 9           |

|                     |         |                                                             | Total 24    |

| Output              |         | General-purpose counter numeric data                        | 22          |

| Register 1          | D1H     | Not used                                                    | 2           |

| Register            |         |                                                             | Total 24    |

|                     |         | Lock detection data                                         | 5           |

|                     |         | I/O port control data                                       | 5           |

| Output              | D3H     | Output data                                                 | 4           |

| Register 2          | 5511    | Input data (undefined during output port selection)         | 5           |

|                     |         | Not used                                                    | 5           |

|                     |         |                                                             | Total 24    |

When the PERIOD signal falls, the input data are latched in register 1 or register 2 and the function is performed.

When the CLOCK signal falls for the 9 time, the output data are latched in parallel in the output registers. The data are subsequently output serially from the data pin.

#### **REGISTER ASSIGNMENTS**

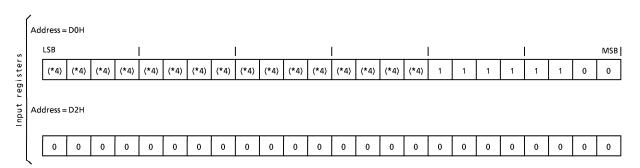

When power is turned on, the input registers are set as shown below.

(Notes) (\*1) Cannot be set on TC9256P and TC9256F.

- (\*2) These data are "0" on TC9256P and TC9256F.

- (\*3) Bit names in parentheses "( )" refer to TC9256P and TC9256F.

- (\*4) Data are undefined.

- (\*5) Set data to "0" for TEST bit.

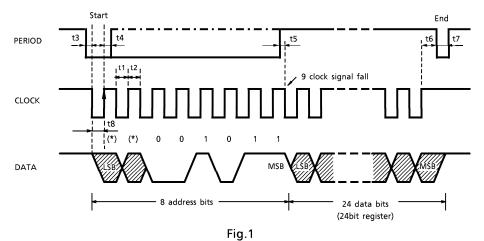

#### O Serial transfer format

The serial transfer format consists of 8 address bits and 24 data bits (Fig.1). Addresses D0H~D3H are used.

#### Serial data transfer

Serial data are transferred in sync with the clock signal. In the idlestate, the PERIOD, CLOCK and DATA pin lines are all set to "H" level. When the period signal is at "L" level, the falling of the clock signal initiates serial data transfer. Data transfer ceases when the period signal is set to "L" level when the clock signal is at "H" level. Once serial data transfer has begun, however, no more than 8 falls of the clock signal can occur during the time the period signal is at "L" level.

Since the receiving side receives the serial data as valid data when the clock signal rises, it is effective for the sending side to produce output in sync with the clock signal fall. To receive serial data from the output registers (D1H, D3H), set the serial data output to high impedance after the 8bit address is output but before the next clock signal falls. Data reception subsequently continues until the period signal becomes "L" level; data transfer ends just before the period signal rises. Therefore, the data pin must have an open-drain or tristate interface.

- (Note 1) When power is turned on, some internal circuits have undefined states. To set internal circuit states, execute a dummy data transfer before performing regular data transfer.

- (Note 2) Times t1~t8 have the following values.

t1≧ 1.0 *μ*s

$t2 \ge 1.0 \mu s$

$t3 \ge 0.3 \mu s$

t4≧ 0.3 *μ*s

$t5 \ge 0.3 \mu s$

t6≧ 1.0 *μ*s

$t7 \ge 1.0 \mu s$

t8≧ 0.3 *u*s

(Note 3) Asterisks represent numbers taken from addresses, as in D\*H.

## ○ Crystal oscillator pins (XT, XT)

As Fig.2 shows, the clock necessary for internal operation is produced by connecting a crystal oscillator between capacitors. Use the crystal oscillator selection bit to select an oscillating frequency of 3.6MHz, 4.5MHz, 7.2MHz or 10.8MHz which matches that of the crystal oscillator used.

Fig.2

(Note) Set to 3.6MHz (OSC1 = "0" and OSC2 = "0") when power is turned on.

The crystal is not oscillating at this time because the system is in standby mode.

O Reference counter (Reference frequency divider)

The reference counter section consists of a crystal oscillator and a counter.

A crystal oscillator frequency of 3.6MHz, 4.5MHz, 7.2MHz or 10.8MHz can be selected. A maximum of 15 reference frequencies can be generated.

1. Setting reference frequency

The reference frequency is set using bits R0~R3.

| Address D0H |    |          |    |    |                |     |              |    |          | R0      | R1  | R2  | R3   |             |            |          |  |

|-------------|----|----------|----|----|----------------|-----|--------------|----|----------|---------|-----|-----|------|-------------|------------|----------|--|

| -           |    | •        |    | •  |                |     | 1            |    | •        |         |     |     |      |             |            |          |  |

|             |    |          |    |    |                |     |              |    | •        |         |     |     |      |             |            |          |  |

|             |    | <b>,</b> | ļ  | Ţ  |                |     | $\downarrow$ | •  | <b>\</b> | <b></b> |     |     |      |             |            |          |  |

|             | R0 | R1       | R2 | R3 | REFER<br>FREQU |     | R0           | R1 | R2       | R3      |     |     |      | EREI<br>QUE | NCE<br>NCY |          |  |

|             | 0  | 0        | 0  | 0  | 0.5            | kHz | 0            | 0  | 0        | 1       |     | *   | 7.8  | 125         | kHz        | <u> </u> |  |

|             | 1  | 0        | 0  | 0  | 1              | kHz | 1            | 0  | 0        | 1       |     |     |      | 9           | kHz        | <u>'</u> |  |

|             | 0  | 1        | 0  | 0  | 2.5            | kHz | 0            | 1  | 0        | 1       |     |     |      | 10          | kHz        | !        |  |

|             | 1  | 1        | 0  | 0  | 3              | kHz | 1            | 1  | 0        | 1       |     |     | 1    | 2.5         | kHz        | :        |  |

|             | 0  | 0        | 1  | 0  | 3.125          | kHz | 0            | 0  | 1        | 1       |     |     |      | 25          | kHz        | :        |  |

|             | 1  | 0        | 1  | 0  | *3.90625       | kHz | 1            | 0  | 1        | 1       |     |     |      | 50          | kHz        | :        |  |

|             | 0  | 1        | 1  | 0  | 5              | kHz | 0            | 1  | 1        | 1       |     |     |      | 100         | kHz        | :        |  |

|             | 1  | 1        | 1  | 0  | 6.25           | kHz | 1            | 1  | 1        | 1       | Sta | ndl | оу г | nod         | e (*       | 1)       |  |

- (Note 1) Reference frequencies marked with an asterisk "\*" can only be generated with a 4.5MHz crystal oscillator.

- (Note 2) (\*1) Standby mode

Standby mode occurs when bits R0, R1, R2 and R3 are all set to "1". In standby mode, the programmable counter stops, and FM, AM and IF<sub>IN</sub> (when selected IF<sub>IN</sub>) are set to "amp off" state (pins at "L" level). This saves current consumption when the radio is turned off. The DO pins become high impedance during standby mode.

During standby mode, the I/O ports (I/O-5~I/O-9) and output ports (OT1~OT4) can be controlled and the crystal oscillator can be turned on and off.

- (Note 3) The system is set to standby mode when power is turned on. At this time, the crystal oscillator is not oscillating and the I/O ports are set to input mode.

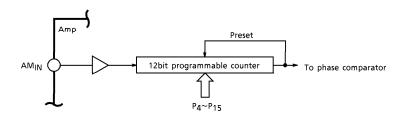

## O Programmable counter

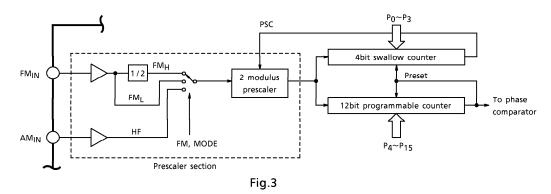

The programmable counter section consists of a 1/2 prescaler, a 2 modulus prescaler and a 4bit + 12bit programmable binary counter.

- 1. Setting programmable counter

- 16 bits of divisor data and 2 bits which indicate the dividing mode are set in the programmable counter.

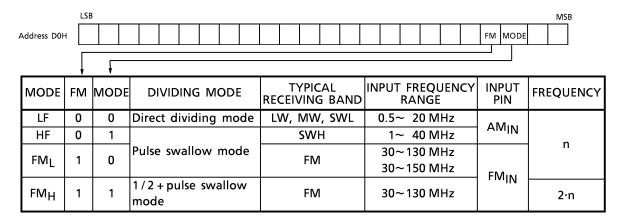

- (1) Setting dividing mode

The FM and MODE bits are used to select the input pin and the dividing mode (pulse swallow mode or direct dividing mode). There are 4 possible choices, shown in the table below. Select one based on the frequency band used.

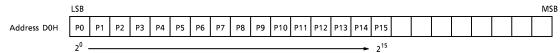

## (2) Setting divisor

The divisor for the programmable counter is set as binary data in bits P0~P15.

Pulse swallow mode (16 bits)

Divisor setting range (pulse swallow mode) :  $n = 210 \text{H} \sim \text{FFFFH}$  (528~65535)

(Note) With the 1/2+pulse swallow mode, the actual divisor is twice the programmed value.

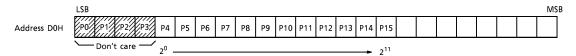

Direct dividing mode (12 bits)

Divisor setting range (direct dividing mode):  $n = 10H \sim FFFH$  (16~4095) With the direct dividing mode, data P0 $\sim$ P3 are don't-care and bit P4 is the LSB.

1998-05-15 10/33

- 2. Prescaler and programmable counter circuit configuration

- (1) Pulse swallow mode circuit configuration

This circuit consists of a 2 modulus prescaler, a 4bit swallow counter and a 12bit programmable counter. During  $FM_{IN}$  ( $FM_H$  mode), a 1/2 prescaler is added to the preceding step.

(2) Direct dividing method circuit configuration

Fig.4

With the direct dividing mode, the prescaler section is bypassed and the 12bit programmable counter is used.

(3) Both  $FM_{IN}$  and  $AM_{IN}$  have built-in amps. Data are input by capacitor coupling.  $FM_{IN}$  and  $AM_{IN}$  operate at low amplitude.

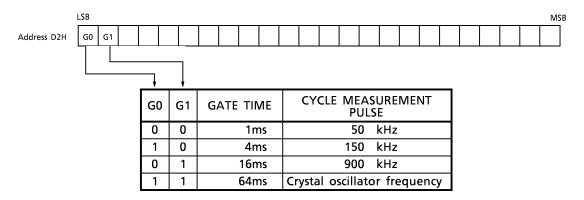

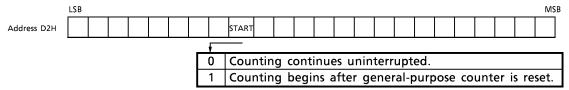

### O General-purpose counter

The general-purpose counter is a 20bit counter. It has such uses as counting AM/FM band intermediate frequencies (IF) and detecting auto-stop signals during auto-search tuning. It also features a cycle measurement function for such uses as measuring low-frequency pilot signal cycles. TC9256P and TC9256F do not have the cycle measurement function (SC<sub>IN</sub> mode). General-purpose counter pins can also be used as I/O ports.

- 1. General-purpose counter control bits

- (1) Bits G0 and G1····· Used for selecting the general-purpose counter gate time.

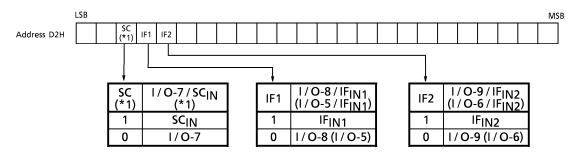

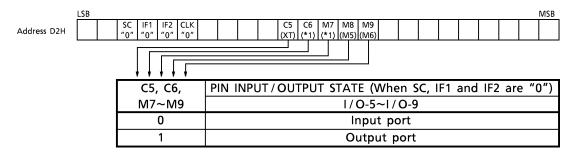

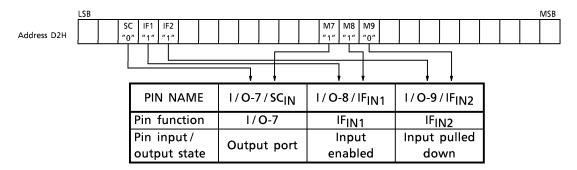

(2) Bits SC, IF1 and IF2·····I/O port and general-purpose counter switching bits.

(\*) The functions of the following pins are switched by data.

- (Note 1) Pin names in parentheses "( )" apply to TC9256P and TC9256F.

- (Note 2) Bits marked with (\*1) cannot be set on TC9256P and TC9256F.

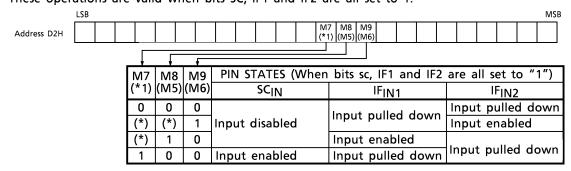

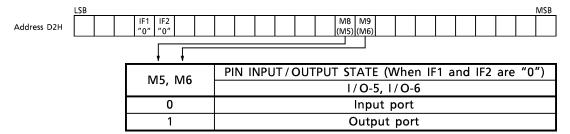

(3) Bits M7, M8 and M9··· M7 (\*1) sets the state for pin I/O-7/SC<sub>IN</sub>, M8 (M5) sets the state for pin I/O-8/IF<sub>IN1</sub>; M9 (M6), for pin I/O-9/IF<sub>IN2</sub>.

These operations are valid when bits SC, IF1 and IF2 are all set to 1.

- (Note 1) Bits marked with an asterisk "(\*)" are don't-care.

- (Note 2) Bit names in parentheses "( )" apply to TC9256P and TC9256F.

- (Note 3) Bits marked with (\*1) cannot be set on TC9256P and TC9256F.

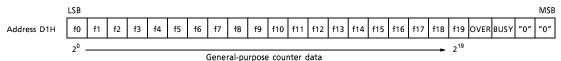

- (4) Bits f0~f19··· The general-purpose counter results can be read in binary from bits f0~f19 of the output register (D1H).

(5) OVER and BUSY bits · · · Detect the operating state of the general-purpose counter.

- (Note) When using the general-purpose counter, before referring to the contents of the general-purpose counter result bits (f0~f19), confirm that the BUSY bit is "0" (counting is ended) and the OVER bit is "0" (general-purpose counter data are normal).

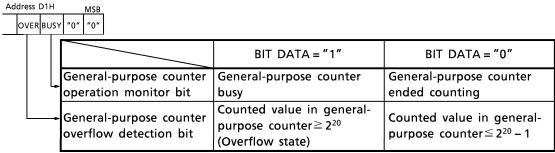

- (6) START bit ··· When the data are set to "1", the general-purpose counter is reset then counting begins.

1998-05-15 13/33

## 2. General-purpose counter circuit configuration

The general-purpose counter section consists of input amps, a gate time control circuit and a 20bit binary counter.

## 3. General-purpose counter measurement timing

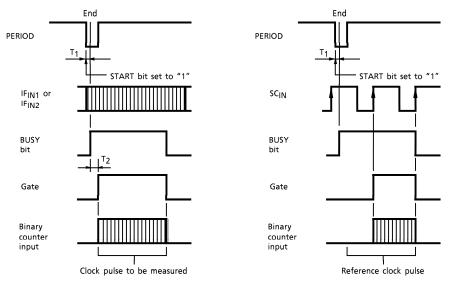

Frequency measurement timing chart

Cycle measurement timing chart

$$0 < T_1 \le 0.25$$

( $\mu$ s),  $0 < T_2 \le 1$  (ms)

Fig.6

- (Note 1)  $IF_{IN1}$  and  $IF_{IN2}$  input have built-in amps. Data are input by capacitor coupling.  $FM_{IN}$  and  $AM_{IN}$  operate at low amplitude.

- (Note 2) SCIN is configured for CMOS input, so input signals should be logic level.

### ○ General-purpose I/O ports

These LSIs feature general-purpose output and I/O ports which are controlled through the serial ports.

| INPUT /<br>OUTPUT FORM | TC9256P, TC9256F                                              | TC9257P, TC9257F                       | INPUT / OUTPUT<br>CONFIGURATION |

|------------------------|---------------------------------------------------------------|----------------------------------------|---------------------------------|

| Output ports           | Dedicated: 3 ports  Maximum: 4 ports (1 port for CMOS output) | Dedicated : 4 ports                    | N channel open-drain output     |

| I/O ports              | Maximum: 2 ports                                              | Dedicated: 1 port,<br>Maximum: 5 ports | CMOS input/output               |

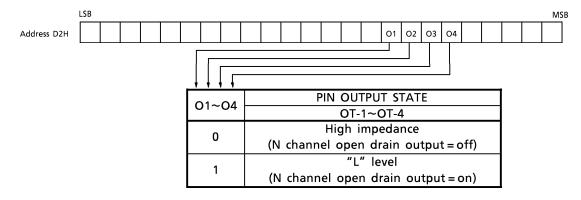

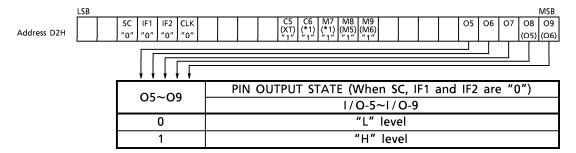

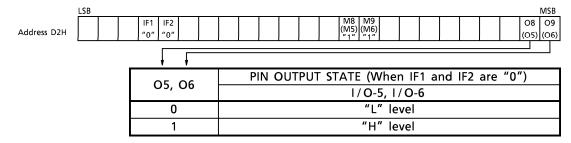

#### 1. General-purpose output ports (OT-1~OT-4)

Pins OT-1~OT-4 are general-purpose dedicated output ports. They have such uses as control signal output. They are configured for N channel open-drain output and have an off withstanding voltage of 12V.

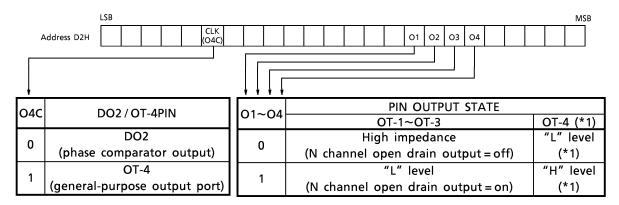

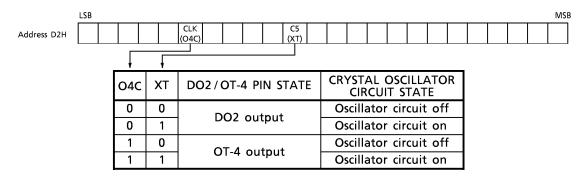

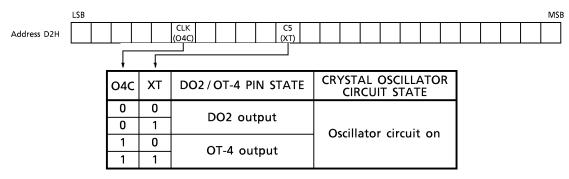

The data set in bits O1~O4 of the input register (D2H) are output in parallel from their corresponding dedicated output port pins OT-1~OT-4. TC9256P and TC9256F do not have dedicated output port OT-4, but setting the input register (D2H) CLK (O4C) bit to "1" converts pin DO2 into output port OT-4 (configured for CMOS output).

The data set in bits O1~O4 of the input register (D2H) can also be read from the DATA pins as output register (D3H) serial data O1~O4.

## (1) TC9257P and TC9257F

(Note 1) Bit names in parentheses "( )" apply to TC9256P and TC9256F.

(Note 2) (\*1) indicates the output state when DO2/OT-4 pin is switched for use as OT-4 output pin (configured for CMOS output).

(3) Output register...The data set in bits O1~O4 of the input register can be read as serial data O1~O4 from the output register (D3H).

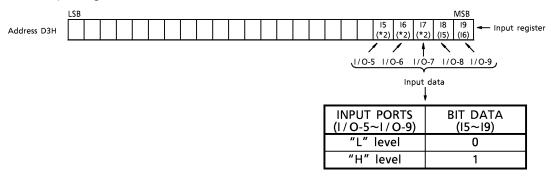

#### 2. General-purpose I/O ports (I/O-5~I/O-9)

Pins I/O-5~I/O-9 are general-purpose I/O ports used for control signal input and output. They are configured for CMOS input and output.

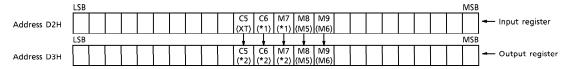

These I/O ports are set for input or output using bits C5, C6 and M7~M9 of the input register (D2H).

Setting bits C5, C6 and M7~M9 to "0" sets these ports for input. Data which are input in parallel from I/O-5~I/O-9 are latched in the internal register on the ninth fall of the serial clock signal. These data can then be read as serial data I5~I9 from the DATA pins. Setting bits C5, C6 and M7~M9 to "1" sets these ports for output.

Data which are set in bits O5~O9 of the input register (D2H) are output in parallel from their corresponding general-purpose I/O port pins I/O-5~I/O-9.

These operations are valid when bits SC, IF1, IF2 and CLK are all set to "0".

#### (1) TC9257P and TC9257F

## • Setting data for output ports

- (Note 1) On TC9257P and TC9257F, pins I/O-7~I/O-9 also serve as general-purpose counter input pins. Therefore, bits SC, IF1 and IF2 of the input register (D2H) must be set to "0" when pins I/O-7~I/O-9 are used for I/O ports. Since pin I/O-5 also serves as the CLK pin, the CLK bit of the input register (D2H) must be set to "0" when pin I/O-5 is used as an I/O port.

- (Note 2) Bit names in parentheses "( )" apply to TC9256P and TC9256F.

- (Note 3) Bits marked with (\*1) cannot be set on TC9256P and TC9256F.

## (2) TC9256P and TC9256F

Setting data for output ports

(3) Output register... Data which are set in bits C5, C6 and M7~M9 of the input register (D2H) can be read as serial data C5, C6 and M7~M9 from the output register (D3H).

Data which are input in parallel from pins  $1/O-5\sim1/O-9$  can be read as serial data  $15\sim19$  from the output register (D3H).

- (Note 1) Bit names in parentheses "( )" apply to TC9256P and TC9256F.

- (Note 2) Bits marked with (\*1) cannot be set on TC9256P and TC9256F.

Data are "0" for bits marked with (\*2) on TC9256P and TC9256F.

- (Note 3) When pins I/O-5~I/O-9 are used for output, the data in I5~I9 of the output register (D3H) are undefined.

- (Note 4) When power is turned on, input register (D2H) I/O port control bits C5, C6 and M7~M9 and output data bits O5~O9 are set to "0".

(General-purpose I/O ports are set as input ports. Pins which are used both as general-purpose I/O ports and for general-purpose counter input are set for I/O port input. The output state of general-purpose output ports is set to high impedance (N channel open drain output = off).

- (Note 5) On TC9256P and TC9256F, pins I/O-5 and I/O-6 also serve as general-purpose counter input pins. Therefore, bits IF1 and IF2 of input register 2 must be set to "0" when these pins are used as I/O ports.

A typical example of data setting for general-purpose counter and I/O port use is shown below.

## • TC9257P and TC9257F

As shown above, the pins can be switched as necessary to enable use as an I/O port or general-purpose counter.

#### O Phase comparator

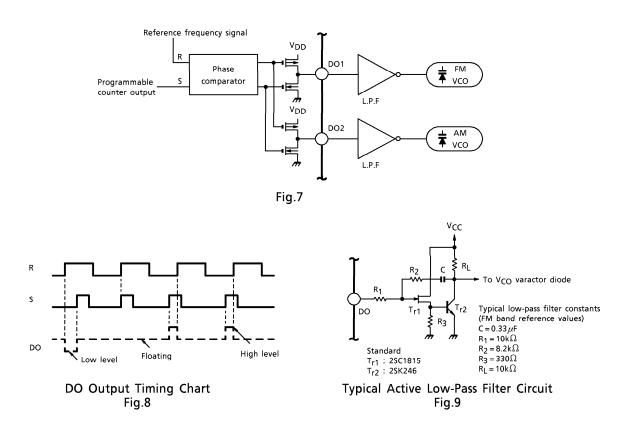

The phase comparator outputs the phase error after comparing the phase difference of the reference frequency signal supplied by the reference counter and the divided output from the programmable counter. The frequencies and phase differences of these two signals are then equalized by passing them through low-pass filters. These signals then control the VCOs. The filter constants can be customized for FM and AM bands since the signals are output in parallel from the phase comparator then pass through the two tristate buffer pins, DO1 and DO2.

The figures above show the DO output timing chart and a typical active low-pass filter circuit featuring a Darlington connection between the FET and transistor.

The filter circuit shown above is just one example. Actual circuits should be designed based on the band composition and the properties desired from the system.

(Note) On TC9256P and TC9256F, pin DO2 can be switched for use as pin OT-4.

#### O Lock detection bits

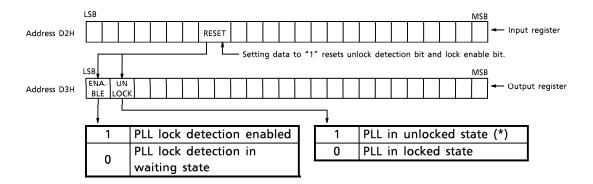

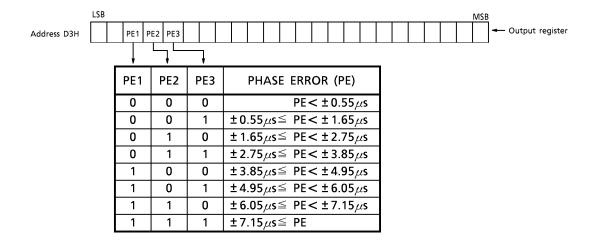

The lock detection bits detect locked states in the PLL system. These systems have an unlock detection bit (unlock bit) which is used to detect, using the reference frequency cycle, the phase difference between the reference frequency and the divided output of the programmable counter. These systems also have phase error detection bits (bits PE1~PE3), which are capable of more precise detection ( $\pm 0.55 \mu s \sim \pm 7.15 \mu s$ ).

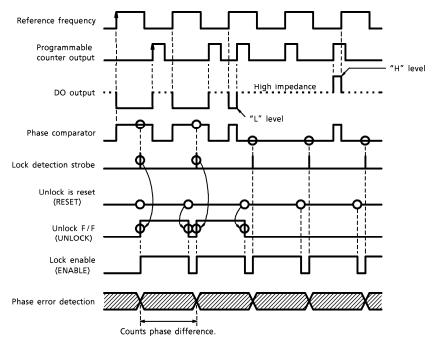

#### 1. Unlock detection bit (UNLOCK)

This bit detects, using the reference frequency cycle, the phase difference between the reference frequency and the divided output of the programmable counter. When there is no lock, that is, when the reference frequency and the divided output of the programmable counter are not the same, unlock F/F is set.

Unlock F/F is reset every time the input register (D2H) unlock reset bit (RESET) is set to "1". After unlock F/F has been reset in this way, locked state can be detected by checking the unlock detection bit (UNLOCK) of the output register (D3H). After unlock F/F has been reset, the unlock detection bit must be checked after a time interval exceeding that of the reference frequency cycle has elapsed. This is because the reference frequency cycle inputs the lock detection strobe to unlock F/F. If the time interval is short, the correct locked state cannot be detected. Therefore, the output register (D3H) has a lock enable bit (ENABLE). This bit is reset every time the input register (D2H) reset bit is set to "1", and set to "1" through the lock detection timing. That is, the locked state is correctly detected when the lock enable bit (ENABLE) is "1".

Fig.10

(Note) The asterisk "(\*)" indicates an error state of over 180° phase difference relative to the reference frequency.

## 2. Phase error detection bits (PE1~PE3)

The unlock bit detects, using the reference frequency cycle, the phase difference between the reference frequency and the divided output of the programmable counter. The phase error detection bits (bits PE1~PE3) are capable of precise phase error detection of  $\pm 0.55 \sim \pm 7.15 \,\mu s$  using the reference frequency cycle. (If the UNLOCK bit is set to "1" and the phase difference relative to the reference frequency is over 180°, bits PE1~PE3 cannot correctly detect the phase error. Therefore, bits PE1~PE3 are normally used when the UNLOCK bit is set to "0".) Bits PE1~PE3 detect phase error normally when the phase difference is  $-180^{\circ} \sim 180^{\circ}$  relative to the reference frequency cycle.

The phase error data can be read from the output register (D3H) as serial data PE1~PE3.

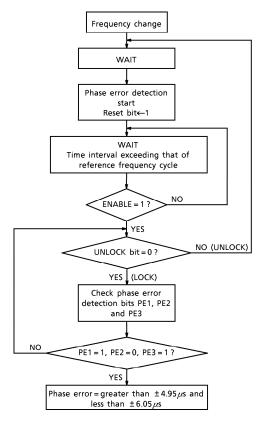

Following is a typical lock detection operation. It shows the operation flow from locked state to frequency change with a phase error greater than  $\pm 4.95 \mu s$  and less than  $\pm 6.05 \mu s$ .

Fig.11

- Other control bits

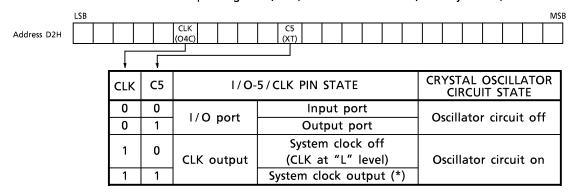

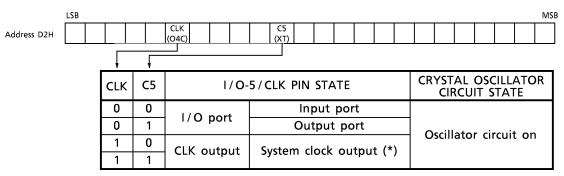

- 1. CLK (O4C) and C5 (XT) bits... Control bits which switch the function for the I/O-5/CLK pin on TC9257P and TC9257F and the OT-4/DO2 pin on TC9256P and TC9256F.

- (1) On TC9257P and TC9257F, the CLK bit controls switching of the I/O-5 pin and CLK pin.

- When bits R0~R3 of the input register (D0H) are all set to "1" (standby mode)

● When one of bits R0~R3 of the input register (D0H) is set to "0" (not standby mode)

(Note 1) The system clock output marked with an asterisk "(\*)" refers to output of the crystal oscillator frequencies listed below.

| CRYSTAL OSCILLATOR (MHz) | SYSTEM CLOCK<br>(kHz) | DUTY<br>(%) |

|--------------------------|-----------------------|-------------|

| 10.8                     |                       |             |

| 7.2                      | 600                   | 50          |

| 3.6                      |                       | 50          |

| 4.5                      | 750                   |             |

(Note 2) Bit names in parentheses "( )" apply to TC9256P and TC9256F.

(2) On TC9256P and TC9256F, the O4C bit controls switching of the DO2 pin and OT-4 pin.

• When bits R0~R3 of the input register (D0H) are all set to "1" (standby mode)

• When one of bits R0~R3 of the input register (D0H) is set to "0" (not standby mode)

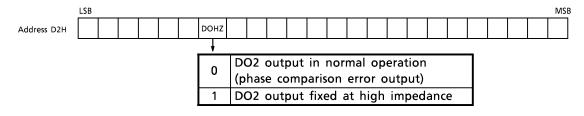

2. DOHZ bit...Controls the DO2 pin output state.

3. TEST bit... Data should normally be set to "0".

|             | LSB |  |  |  |  |             |  |  |  |  |  |  | MSE | 3 |

|-------------|-----|--|--|--|--|-------------|--|--|--|--|--|--|-----|---|

| Address D2H |     |  |  |  |  | TEST<br>"0" |  |  |  |  |  |  |     |   |

(Note) Bit names in parentheses "( )" apply to TC9256P and TC9256F.

## **MAXIMUM RATINGS** (Ta = $25^{\circ}$ C)

| CHARACTERISTIC                              | SYMBOL           | RATING                    | UNIT |

|---------------------------------------------|------------------|---------------------------|------|

| Supply Voltage                              | $V_{DD}$         | -0.3~6.0                  | V    |

| Input Voltage                               | VIN              | -0.3~V <sub>DD</sub> +0.3 | V    |

| N-ch Open-Drain OFF<br>Withstanding Voltage | V <sub>OFF</sub> | 13                        | V    |

| Power Dissipation                           | PD               | 300 (200)                 | mW   |

| Operating Temperature                       | T <sub>opr</sub> | - 40~85                   | °C   |

| Storage Temperature                         | $T_{stg}$        | <b>-65∼150</b>            | °C   |

( ): Flat Package

## **ELECTRICAL CHARACTERISTICS** (Unless otherwise specified, Ta = $-40 \sim 85$ °C, V<sub>DD</sub> = $4.5 \sim 5.5$ V)

| CHARACTERISTIC                    | SYMBOL           | TEST<br>CUR-<br>CUIT |                                                      | MIN. | TYP. | MAX. | UNIT |

|-----------------------------------|------------------|----------------------|------------------------------------------------------|------|------|------|------|

| Operating Power<br>Supply Voltage | V <sub>DD1</sub> | _                    | PLL operation<br>(Normal operating)                  | 4.5  | 5.0  | 5.5  | ٧    |

| Operating Power<br>Supply Current | I <sub>DD1</sub> | _                    | $V_{DD} = 5.0V, XT = 10.8MHz,$<br>$FM_{IN} = 150MHz$ |      | 7    | 15   | mA   |

## (Stand-by mode)

| Crystal Oscillation<br>Frequency Supply<br>Voltage | V <sub>DD2</sub> | _ | PLL OFF<br>(Operating crystal oscillation)       | 4.0 | 5.0 | 5.5 | ٧  |

|----------------------------------------------------|------------------|---|--------------------------------------------------|-----|-----|-----|----|

| Operating Power Supply Current                     | l <sub>DD2</sub> | _ | V <sub>DD</sub> = 5.0V, XT = 10.8MHz,<br>PLL OFF | -   | 0.8 | 1.5 | mA |

| Operating Power<br>Supply Current                  | l <sub>DD3</sub> | _ | V <sub>DD</sub> = 5.0V, XT stop, PLL OFF         |     | 120 | 240 | μΑ |

## (Operating frequency range)

|                                                       |                 |     | ı                                                                  |     |   |      |        |

|-------------------------------------------------------|-----------------|-----|--------------------------------------------------------------------|-----|---|------|--------|

| Crystal Oscillation                                   | f <sub>XT</sub> | l   | Connect crystal resonator to                                       | 3.6 | ~ | 10.8 | MHz    |

| Frequency                                             | 'X1             |     | XT-XT terminal                                                     | 3.  |   | 10.0 | 141112 |

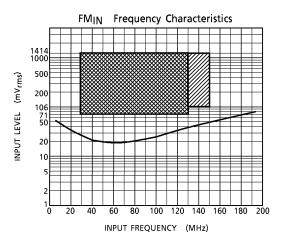

| FM <sub>IN</sub> (FM <sub>H</sub> , FM <sub>L</sub> ) | fFM             | —   | $FM_H$ , $FM_L$ mode, $V_{IN} = 0.2V_{p-p}$                        | 30  | ~ | 130  | MHz    |

| FM <sub>IN</sub> (FM <sub>L</sub> )                   | fFML            | —   | $FM_L$ mode, $V_{IN} = 0.3V_{p-p}$                                 | 30  | ~ | 150  | MHz    |

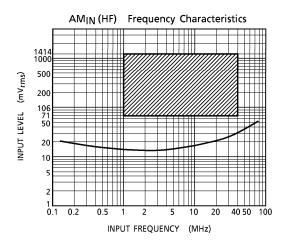

| AM <sub>IN</sub> (HF)                                 | fHF             | —   | HF mode, $V_{IN} = 0.2V_{p-p}$                                     | 1   | ~ | 40   | MHz    |

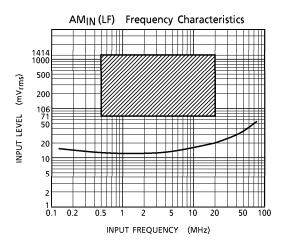

| AM <sub>IN</sub> (LF)                                 | f <sub>LF</sub> | —   | LF mode, $V_{IN} = 0.2V_{p-p}$                                     | 0.5 | ~ | 20   | MHz    |

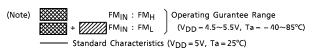

| IF <sub>IN1</sub> , IF <sub>IN2</sub>                 | f <sub>IF</sub> | T — | $V_{IN} = 0.2V_{p-p}$                                              | 0.1 | ~ | 15   | MHz    |

| sc <sub>IN</sub>                                      | fsc             | _   | $V_{IH} = 0.7V_{DD}$ , $V_{IL} = 0.3V_{DD}$ ,<br>Square wave input | _   | ~ | 100  | kHz    |

| CHARA                                 | CTERISTIC               | SYMBOL           | TEST<br>CUR-<br>CUIT | TEST CONDITION                                      | MIN.               | TYP.  | MAX.                     | UNIT             |

|---------------------------------------|-------------------------|------------------|----------------------|-----------------------------------------------------|--------------------|-------|--------------------------|------------------|

| (Operating                            | input amplitu           | de range)        |                      |                                                     |                    |       |                          |                  |

| FM <sub>IN</sub> (FM <sub>H</sub>     | , FM <sub>L</sub> )     | V <sub>FM</sub>  | _                    | $FM_H$ , $FM_L$ mode,<br>$f_{IN} = 30 \sim 130 MHz$ | 0.2                | ~     | V <sub>DD</sub><br>- 0.5 | V <sub>p-p</sub> |

| FM <sub>IN</sub> (FM <sub>L</sub> )   | )                       | V <sub>FML</sub> | -                    | FM <sub>L</sub> mode, $f_{IN} = 30 \sim 150 MHz$    | 0.3                | ~     | V <sub>DD</sub><br>- 0.5 | V <sub>p-p</sub> |

| AM <sub>IN</sub> (HF)                 |                         | V <sub>HF</sub>  | -                    | HF mode, f <sub>IN</sub> = 1~40MHz                  | 0.2                | ~     | V <sub>DD</sub><br>- 0.5 | V <sub>p-p</sub> |

| AM <sub>IN</sub> (LF)                 |                         | V <sub>LF</sub>  | -                    | LF mode, f <sub>IN</sub> = 0.5~20MHz                | 0.2                | ~     | V <sub>DD</sub><br>- 0.5 | V <sub>p-p</sub> |

| IF <sub>IN1</sub> , IF <sub>IN2</sub> | 2                       | V <sub>IF</sub>  | -                    | f <sub>IN</sub> = 0.1~15MHz                         | 0.2                | ~     | V <sub>DD</sub><br>- 0.5 | V <sub>p-p</sub> |

| (OT1~OT4                              | N-ch open dra           | ain)             |                      |                                                     |                    |       |                          |                  |

| Output<br>Current                     | "L" Level               | l <sub>OL1</sub> | -                    | V <sub>OL</sub> = 1.0V                              | 5.0                | 10.0  | _                        | mA               |

| OFF-Leak C                            | Current                 | lOFF             | _                    | V <sub>OFF</sub> = 12V                              | _                  | _     | 2.0                      | $\mu$ A          |

| (I / O-5~I / C                        | )-9, SC <sub>IN</sub> ) |                  |                      |                                                     |                    |       |                          |                  |

| Input                                 | "H" Level               | V <sub>IH1</sub> |                      |                                                     | 0.7V <sub>DD</sub> | ~     | $V_{DD}$                 | V                |

| Voltage                               | "L" Level               | V <sub>IL1</sub> |                      |                                                     | 0                  | ~     | 0.3V <sub>DD</sub>       | <b>v</b>         |

| Input                                 | "H" Level               | ΊΗ               | <u> </u>             | V <sub>IH</sub> = 5V                                | <u> </u>           | _     | 2.0                      | $\mu$ A          |

| Current                               | "L" Level               | IIL              |                      | V <sub>IL</sub> = 0V                                |                    | _     | - 2.0                    | μΑ               |

| Output                                | "H" Level               | IOH4             | <b>↓</b>             | V <sub>OH</sub> = 4.0V (Expect SC <sub>IN</sub> )   | - 2.0              | - 4.0 | _                        | mA               |

| Current                               | "L" Level               | lOL4             |                      | V <sub>OL</sub> = 1.0V (Expect SC <sub>IN</sub> )   | 2.0                | 4.0   | _                        |                  |

|                                       | LOCK, DATA)             |                  |                      |                                                     |                    |       |                          |                  |

| Input                                 | "H" Level               | V <sub>IH2</sub> |                      |                                                     | 0.8V <sub>DD</sub> | ~     | $V_{DD}$                 | V                |

| Voltage                               | "L" Level               | V <sub>IL2</sub> |                      |                                                     | 0                  | ~     | 0.2V <sub>DD</sub>       |                  |

| Input                                 | "H" Level               | ΊΗ               | l _                  | V <sub>IH</sub> = 5V                                |                    |       | 2.0                      | $\mu$ A          |

| Current                               | "L" Level               | ΙΙL              |                      | V <sub>IL</sub> = 0V                                | <u> </u>           |       | - 2.0                    | <i></i>          |

| Output                                | "H" Level               | I <sub>OH5</sub> | <b> </b>             | V <sub>OH</sub> = 4.0V (DATA)                       | - 1.0              | - 3.0 | _                        | mΑ               |

| Current                               | "L" Level               | I <sub>OL5</sub> |                      | V <sub>OL</sub> = 1.0V (DATA)                       | 1.0                | 3.0   | _                        |                  |

| (DO1, DO2)                            |                         | <u> </u>         |                      |                                                     |                    |       |                          |                  |

| Input                                 | "H" Level               | l <sub>ОН3</sub> | <del> </del> _       | V <sub>OH</sub> = 4.0V                              | - 2.0              | - 4.0 | —                        | mΑ               |

| Current                               | "L" Level               | lOL3             |                      | V <sub>OL</sub> = 1.0V                              | 2.0                | 4.0   | <u> </u>                 |                  |

|                                       | ead Current             | ITL              | _                    | V <sub>TLH</sub> = 5V, V <sub>TLL</sub> = 0V        |                    |       | ± 1.0                    | $\mu$ A          |

| (XT)                                  |                         |                  |                      |                                                     |                    |       |                          |                  |

| Output                                | "H" Level               | I <sub>OH2</sub> |                      | V <sub>OH</sub> = 4.0V                              | - 0.1              | - 0.3 |                          | mA               |

| Current                               | "L" Level               | l <sub>OL2</sub> |                      | V <sub>OL</sub> = 1.0V                              | 0.1                | 0.3   |                          | ША               |

| (Input feed                           | back resistanc          | e)               |                      |                                                     |                    |       |                          |                  |

| Input Feed                            | back                    | Rf1              |                      | $FM_{IN}$ , $AM_{IN}$ , $IF_{IN}$ ( $Ta = 25$ °C)   | 350                | 700   | 1400                     | kΩ               |

| Resistance                            |                         | Rf2              | -                    | XT-XT (Ta = 25°C)                                   | 500                | 1000  | 4000                     | K77              |

TOSHIBA TC9256,57P/F

(Note) Operating Gurantee Range  $(V_{DD} = 4.5 \sim 5.5 \text{V}, Ta = -40 \sim 85 ^{\circ}\text{C})$  Standard Characteristics  $(V_{DD} = 5 \text{V}, Ta = 25 ^{\circ}\text{C})$

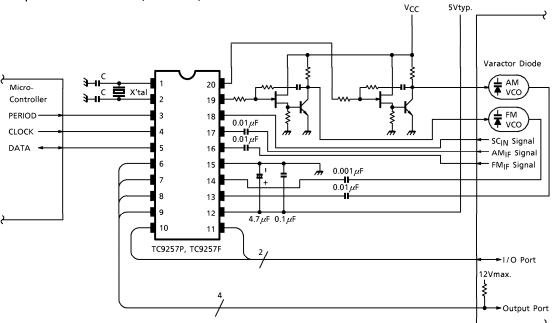

## **APPLICATION CIRCUIT**

(Example for use TC9257P, TC9257F)

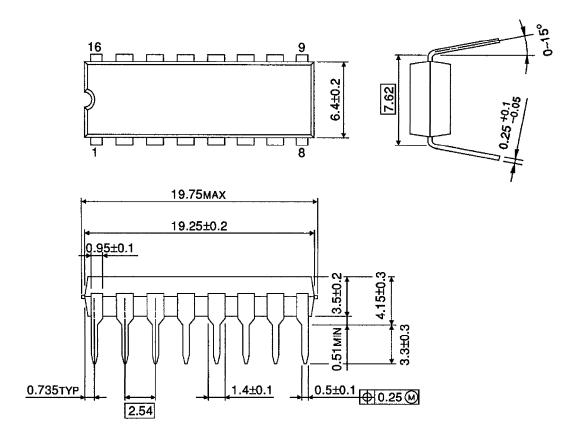

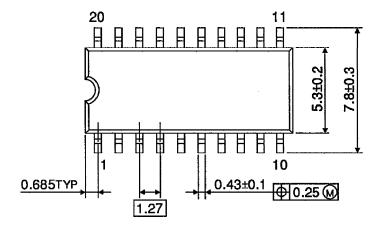

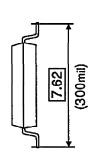

## OUTLINE DRAWING DIP16-P-300-2.54A

Unit: mm

Weight: 1.0g (Typ.)

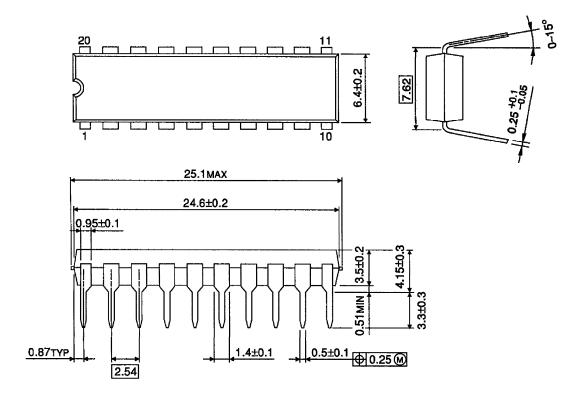

## OUTLINE DRAWING DIP20-P-300-2.54A

Unit: mm

Weight: 1.24g (Typ.)

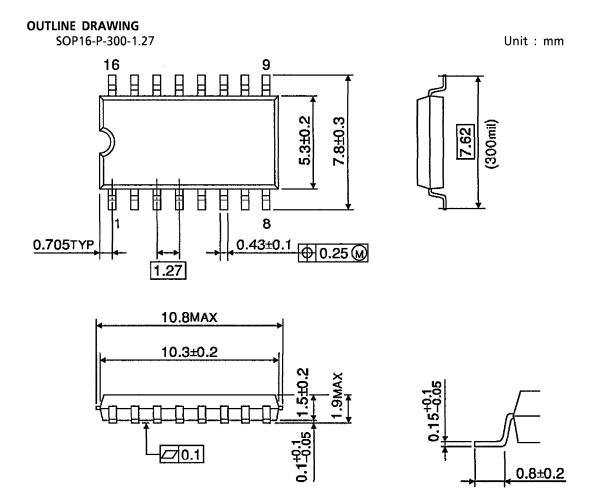

Weight: 0.16g (Typ.)

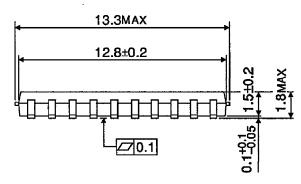

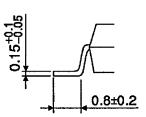

## OUTLINE DRAWING SOP20-P-300-1.27

Unit: mm

Weight: 0.48g (Typ.)