No.1374E

**CMOSIC**

## 3V Electronic Volume Control

### Use

· Attenuation of signal

### **Features**

- · CMOS process 3V typ. operation

- · Up/down operation is performed with SW input.

- · 4-bit, 16-step counter. Step 6\* is set with initial input (INIT).

- · Center tap provided.

- · Maximum attenuation: 60dB or less

- · Attenuation curve: Pseudo curve A. Left/right simultaneous setting.

- \*: Step 6 means mode 6.

| Absolute Maximum Ratings at                 | $Ta = 25^{\circ}$ | C                                          |                               |     | unit |      |

|---------------------------------------------|-------------------|--------------------------------------------|-------------------------------|-----|------|------|

| Maximum Supply Voltage                      | V <sub>DD</sub> m | V <sub>DD</sub> max                        |                               | 6   | V    |      |

| Supply Voltage                              | $V_{\rm I}$       |                                            | $V_{SS}$ to $V_{I}$           |     | V    |      |

| Allowable Power Dissipation                 | Pd max            | <b>C</b>                                   | 10                            | 00  | mW   |      |

| Operating Temperature                       | Topr              |                                            | -30  to  +7                   | 75  | . °C |      |

| Storage Temperature                         | Tstg              |                                            | -40  to  +12                  | 25  | °C   |      |

| Allowable Operating Conditions at Ta = 25°C |                   |                                            |                               |     | unit |      |

| Supply Voltage                              | $ m V_{DD}$       |                                            | 2.1 to 5                      | .0  | V    |      |

| Input 'H'-Level Voltage                     | $V_{IH1}$         | ĪNĪT,CE pin                                | $0.7 V_{DD}$ to $V_{D}$       | DD  | V    |      |

|                                             | $V_{IH2}$         | <del>UP,DN</del> ,CR pin                   | $0.9  m V_{DD}$ to $ m V_{D}$ | DD  | V    |      |

| Input 'L'-Level Voltage                     | $V_{IL1}$         | ĪNIT,CE                                    | 0 to 0.3V                     | ac  | V    |      |

|                                             | $V_{IL2}$         | ŪP,DN,CR                                   | $V_{SS}$ to $0.1V_{E}$        | DD  | V    |      |

| Electrical Characteristics at T             | a=25°C            |                                            | min                           | typ | max  | unit |

| Signal Distortion                           | $\mathrm{THD}_1$  | $V_{DD} = 3V, R_L = 50k\Omega, f = 1kHz$   |                               |     | 0.5  | %    |

|                                             | $\mathrm{THD}_2$  | $V_{DD} = 2.1V, R_L = 50k\Omega, f = 1kHz$ |                               | 1   |      | %    |

| Output at Attenuation Mode                  | $X_{OUT}$         | 0dBm input,1kHz,51k $\Omega$ load          |                               |     | -60  | dB   |

Continued on next page.

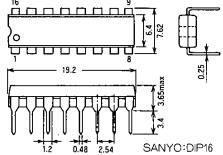

Package Dimensions (unit: mm)

3006B-D16IC

Electric Co., Ltd. Semiconductor Business Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

| Continued from preceding page. |                            |                                                                               |     |                    |     |               |

|--------------------------------|----------------------------|-------------------------------------------------------------------------------|-----|--------------------|-----|---------------|

|                                |                            |                                                                               | min | typ                | max | unit          |

| Signal Transmit Delay Time     | $\mathbf{t_{d}}$           | Between IN and OUT, no load                                                   |     | 1                  |     | μs            |

| Input Impedance                | $\mathbf{r_{i}}$           | $\overline{\text{UP}},\overline{\text{DN}},\text{CE}$ only                    | 100 | •                  | 400 | ${f k}\Omega$ |

| Output Noise Voltage           | $V_{NO}$                   | $V_{DD} = 3V_{,R_L} = 50k\Omega_{,STEP}$ "0"                                  |     |                    | 8   | $\mu V$       |

| Input 'H'-Level Current        | $I_{IH}$                   | $CE pin, V_{DD} = 3V, V_{I} = 3V$                                             |     |                    | 40  | μΑ            |

| Input 'L'-Level Current        | $I_{IL}$                   | $\overline{UP}$ , $\overline{DN}$ pin, $V_{DD} = 3V$ , $V_{I} = 0V$           | -55 |                    |     | μA            |

| Attenuation Balance            | $\Delta V$                 | Pins OUT1,2,other than STEP "0"                                               | -2  | 0                  | 2   | dB            |

|                                |                            | (Note 1)                                                                      |     |                    |     |               |

| Channel Balance                | $\Delta V_{O}$             | Between pins OUT1,2,other than                                                | -2  |                    | 2   | dB            |

|                                |                            | STEP "0" (Note 2)                                                             |     |                    |     |               |

| Current Dissipation            | $I_{\mathbf{D}\mathbf{D}}$ | $V_{DD} = 3V, CE = V_{DD}, \overline{INIT} = V_{DD},$                         |     |                    | 1   | mA            |

|                                |                            | other pins : OPEN                                                             |     |                    |     |               |

|                                | $\Pi_{\mathbf{DD}}$        | $V_{DD} = 3V, CE = V_{SS}, \overline{INIT} = V_{DD},$                         |     |                    | 1   | μA            |

|                                | BACK UP                    | other pins : OPEN                                                             |     |                    |     | -             |

| Crosstalk between Channels     | CT                         | $V_{DD} = 1.5 V, V_{SS} = -1.5 V, V_{M} = 0 V,$                               |     | 85                 |     | dB            |

|                                |                            | $f=1k\Omega,1Vrms$ input,                                                     |     |                    |     |               |

|                                |                            | test side input : 1kΩ short                                                   |     |                    |     |               |

| Minimum Pulse Width            | $T_{UP/DN}$                | $T = (CR \text{ oscillation cycle}) \overline{UP}, \overline{DN} \text{ pin}$ |     | $1.5_{\mathrm{T}}$ |     | ms            |

|                                | $T_{INIT}$                 | INIT pin                                                                      | 2   | •                  |     | μs            |

|                                |                            |                                                                               |     |                    |     | •             |

Note 1 (1)  $\Delta V = 20 \log 10 V_{OUT} / V_{TYP}$

$V_{OUT}$ : OUT1 (OUT2) output level

V<sub>TYP</sub>: Standard output level

(2) Satisfy  $V_{OUT}$  (STEP N)  $< V_{OUT}$  (STEP N + 1)

Note 2 (1)  $\Delta V_O = 20 \log 10 V_{OUT1} / V_{OUT2}$

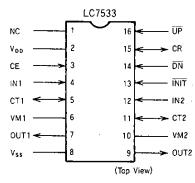

#### Pin Assignment

Note 1: No bonding exists on the inside of NC pin. It is recommended that the outside should be shorted to  $V_{DD}$ ,  $V_{SS}$ , etc. on the printed circuit board.

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

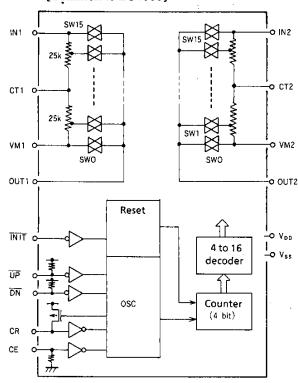

# Equivalent Circuit Block Diagram

## [Common to LC7533]

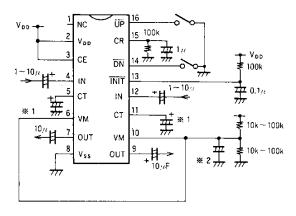

## Sample Application Circuit [LC7533 DIP16]

$\begin{array}{ll} For \ V_M, 1/2 V_{DD} \ bias \ is \ recommended. \\ \hline \times 1 \quad For \ low-band \ boost \ (appro. 1 \mu F) \end{array}$

- The larger the capacity is (appro. 100µF), the better the characteristics of attenuation and closstalk.

Unit (resistance: Ω, capacitance: F)

Note 1: The TEST pin is bonded only when the MFP20 is used.

## Pin Description

| Pin Name                          | Pin Number | Description                                                                                                                                                                                                                             |  |

|-----------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IN1, IN2                          | 4, 12      | Input pin for volume control                                                                                                                                                                                                            |  |

| OUT1, OUT2                        | 7, 9       | Output pin for volume control                                                                                                                                                                                                           |  |

| V <sub>M1</sub> , V <sub>M2</sub> | 6, 10      | Bias pin. When operated form single supply, $1/2V_{DD}$ is applied to this pin.                                                                                                                                                         |  |

| $C_{T1}, C_{T2}$                  | 5,11       | Tap pin provided at the center of volume control. By connecting C and R to this pin, the loudness can be controlled.                                                                                                                    |  |

| CE                                | 3          | When this pin is set to "L", the current dissipation i reduced. This pin must be "L" at backup mode.                                                                                                                                    |  |

| ĪNIT                              | 13         | Initial pin. When set to "L", the 6th step is reached.                                                                                                                                                                                  |  |

| ŪΡ                                | 16         | When the level on this pin is made to fall, the step rises and the volume goes up. When held at "L", the volume goes up; if set to "H", the volume stops going up at a step reached at that moment. The step stops at the MSB position. |  |

| DN                                | 14         | The $\overline{DN}$ operation is the reverse of $\overline{UP}$ . When the $\overline{UP}$ , $\overline{L}$ are set to "L" at the same time, the $\overline{UP}$ is given priori. The step stops at the LSB position.                   |  |

| CR                                | 15         | Pin for connecting R, C on which the rate of step depends.                                                                                                                                                                              |  |

| $V_{DD}$                          | 2          | Power supply pin (+)                                                                                                                                                                                                                    |  |

| $V_{SS}$                          | 8          | Ground                                                                                                                                                                                                                                  |  |

| NC                                | 1          | No bonding exists on the inside of NC pin. Connected to $V_{DD}$ or $V_{SS}$ is recommended.                                                                                                                                            |  |