SANYO SEMICONDUCTOR CORP

CMOS LSI

## Electronic Volume Control for Graphic Equalizer

€1590F

#### **Functions**

- · On-chip electronic volume control for graphic equalizer with 7 bands each of right/left

- · 2dB/step variable in each band

- · Maximum boost of + 12dB, maximum cut of 12dB, and 13 positions in each band

- · Simultaneous drive of right/left band

- · Band setting by serial data input, 2 control lines

- · CMOS LSI of 16V breakdown voltage

#### **Features**

By using 3 chips of the LC7522, a controller (LC7060 or general-purpose microcomputer LC6502C), and a display LSI (LC7560→LCD, LC7565→FLT, LED), an electronic graphic equalizer system with the following features can be formed.

- · The gain in each band can be increased/decreased with one touch.

- · Since the preset memory contents can be called with one touch, your desired frequency characteristic to the music can be selected.

(Example) User option 2 modes + maker option 3 modes + last channel memory

- · ' 0dB in each band (flat function)', 'The frequency characteristic in each band is reversed with respect to 0dB (reverse function)'. - These functions can be software-controlled with one touch.

- · Spectrum analyzing display can be used to provide recording equalization easily.

- · Since 2 control lines can be also used for a display LSI, wiring between microcomputer and LSI is facilitated.

# Absolute Maximum Ratings at Ta = 25°C, V<sub>SS</sub> = 0V

|                             |                     | Pin Name                           | Conditions                 |                    |                                     | unit     |

|-----------------------------|---------------------|------------------------------------|----------------------------|--------------------|-------------------------------------|----------|

| Maximum Supply Voltage      | V <sub>DD</sub> max | $V_{\mathrm{DD}}, V_{\mathrm{EE}}$ | $-8V \le V_{EE} \le V_{S}$ | $_{S} \leq V_{DD}$ | 16                                  | V        |

|                             | $V_{EE}$ max        | $V_{\mathrm{DD}}, V_{\mathrm{EE}}$ | $-8V \le V_{EE} \le V_{S}$ | $_{S} \leq V_{DD}$ | 16                                  | V        |

|                             | $V_{CC}$ max        | $v_{cc}$                           |                            | V                  | $_{\rm SS}$ to $\rm V_{\rm SS}$ + 7 | V        |

| Maximum Input Voltage       | $v_{I1}$            | CLK,DI                             |                            | 0                  | to $V_{CC} + 0.3$                   | V        |

|                             | $v_{I2}$            | f1 to f7,IN1,                      | IN2                        | $V_{\rm EE} = 0.3$ | to $V_{DD} + 0.3$                   | V        |

|                             | $V_{I3}$            | S                                  |                            | $V_{\rm EE}-0.3$   | to V <sub>DD</sub> + 0.3            | v        |

| Allowable Power Dissipation | Pd max              |                                    | $Ta = 75^{\circ}C$         |                    | 200                                 | mW       |

| Operating Temperature       | Topg                |                                    |                            |                    | -30  to  +75                        | <b>℃</b> |

| Storage Temperature         | Tstg                |                                    |                            | _                  | -40 to +125                         | °C       |

|                             |                     |                                    |                            |                    |                                     |          |

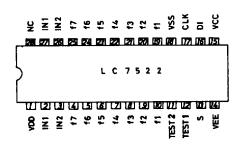

### Pin Assignment

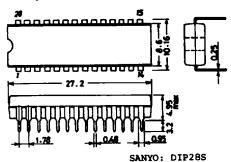

## Case Outline 3029A

(unit: mm)

7100TA/7088YT/6096KI/2225KI,TS No.1590-1/5

| Recommended Operating Co        | ndition           | at Ta = 25°C Vos                   | = 0V                                                                                                                                                          |                                     |      |

|---------------------------------|-------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|------|

| Recommended Operating Co        | namons            | Pin Name                           | Conditions                                                                                                                                                    | •                                   | unit |

| Supply Voltage                  | $V_{DD}$          | $V_{\mathrm{DD}}, V_{\mathrm{EE}}$ | $-7.0V \le V_{EE} \le V_{SS} \le V_{DD}$                                                                                                                      | 14                                  | V    |

| Supply votange                  | $V_{EE}$          | $V_{DD}, V_{EE}$                   | $-7.0V \le V_{EE} \le V_{SS} \le V_{DD}$                                                                                                                      | 14                                  | V    |

|                                 | V <sub>CC</sub>   | $v_{cc}$                           | <b>35 44</b>                                                                                                                                                  | 5.0                                 | V    |

|                                 | _                 |                                    | > **                                                                                                                                                          |                                     |      |

| Allowable Operating Conditi     | ons at T          | $a = 25^{\circ}C, V_{SS} = 0V$     |                                                                                                                                                               |                                     | unit |

|                                 |                   | Pin Name                           | Conditions                                                                                                                                                    | 7 5 40 15 0                         | V    |

| Supply Voltage                  | $V_{DD}$          | $V_{DD}, V_{EE}$                   | $\begin{bmatrix} -7.5 \text{V} \leq \text{V}_{\text{EE}} \leq \text{V}_{\text{SS}} \leq \text{V}_{\text{DD}} \\ 1 & \text{V} & \text{Constant} \end{bmatrix}$ | 7.5 to 15.0<br>7.5 to 15.0          | v    |

|                                 | $V_{EE}$          | $V_{\mathrm{DD}}, V_{\mathrm{EE}}$ | externally connect a capacitor of 1000pF or                                                                                                                   | 7.5 to 15.0                         | v    |

|                                 |                   |                                    | greater across V <sub>DD</sub> - V <sub>SS</sub> ,                                                                                                            |                                     |      |

|                                 |                   |                                    | V <sub>CC</sub> - V <sub>SS</sub> and V <sub>EE</sub> - V <sub>SS</sub> .                                                                                     |                                     |      |

|                                 | $v_{cc}$          | $v_{cc}$                           | $V_{CC} \leq V_{DD}$                                                                                                                                          | 4.5 to 5.5                          | V    |

| Input 'H'-Level Voltage         | V <sub>IH 1</sub> | CLK,DI                             |                                                                                                                                                               | 8V <sub>CC</sub> to V <sub>CC</sub> | V    |

| Input II -Devel Voltage         | V <sub>IH 2</sub> | S                                  | $0.9(V_{DD} - V_{EE}) +$                                                                                                                                      |                                     | V    |

| Input 'L'-Level Voltage         | V <sub>IL 1</sub> | CLK,DI                             | COCCO DD CED                                                                                                                                                  | 0.2V <sub>CC</sub>                  | V    |

| Input L-Level voltage           | $V_{\rm IL2}$     | S S                                | $V_{EE}$ to $0.1(V_{DD}$ -                                                                                                                                    |                                     | V    |

| Inner Deller Width              | tøW               | CLK                                | FE of cirt ( DD                                                                                                                                               | 1 min.                              | μS   |

| Input Pulse Width               | tsetup            | DI                                 |                                                                                                                                                               | 1 min.                              | μS   |

| Setup Time                      | -                 | DI                                 |                                                                                                                                                               | 1 min.                              | μS   |

| Hold Time                       | t hold            | CLK                                |                                                                                                                                                               | up to 330                           | kHz  |

| Operating Frequency             | fopg              | CLK                                |                                                                                                                                                               | ар 60 000                           | MIL  |

| Electrical Characteristics at ' | Γa = 25°C         |                                    |                                                                                                                                                               |                                     | ٠,   |

|                                 |                   | Pin Name                           | Conditions min                                                                                                                                                | typ max                             | unit |

| Total Harmonic Distortion       | THD 1             |                                    | V <sub>OUT</sub> =1V,flat mode,<br>f=20kHz,Test Circuit 1                                                                                                     | 0.005 0.01                          | .%   |

|                                 | THD 2             |                                    |                                                                                                                                                               | 0.0015 0.003                        | %    |

|                                 |                   |                                    | f=1kHz,Test Circuit 1                                                                                                                                         |                                     |      |

|                                 | THD 3             |                                    | V <sub>OUT</sub> = 1V, boost mode,                                                                                                                            | 0.04 0.1                            | %    |

|                                 |                   |                                    | f=20kHz,Test Circuit 1                                                                                                                                        |                                     |      |

|                                 | THD 4             |                                    | V <sub>OUT</sub> =1V,boost mode,                                                                                                                              | 0.015 0.03                          | %    |

|                                 |                   |                                    | f=1kHz,Test Circuit 1                                                                                                                                         |                                     |      |

| Crosstalk between Channels      | Xtalk             |                                    | $V_{OUT} = 1V, f = 20kHz,$                                                                                                                                    | 55                                  | dB   |

| Crosstaik between Chaimers      | 2100111           |                                    | Test Circuit 2                                                                                                                                                |                                     |      |

| Setting Error                   | ΔΒ                |                                    | Other band flat, $-1$                                                                                                                                         | +1                                  | dB   |

| Setting Error                   | 20                |                                    | $V_{DD} - V_{EE} = 14V$ ,                                                                                                                                     |                                     |      |

|                                 |                   |                                    | Test Circuit 1                                                                                                                                                |                                     |      |

| Current Dissipation             | I                 |                                    | $V_{DD} - V_{EE} = 15V$                                                                                                                                       | 1                                   | mA   |

| Current Dissipation             | $I_{DD}$ $I_{CC}$ |                                    | $V_{CC} = 5V$                                                                                                                                                 | 1                                   | mA   |

| Analog CW OPP I as boss         |                   |                                    | f1 to f7                                                                                                                                                      | 10                                  | μA   |

| Analog SW OFF Leakage           | $I_{OFF}$         |                                    |                                                                                                                                                               | 10                                  | μ.1  |

| Current                         |                   | ZANYO ZEM                          | ICONDUCTOR CORP                                                                                                                                               |                                     |      |

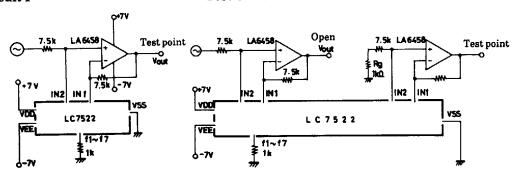

## Test Circuit 1

## Test Circuit 2

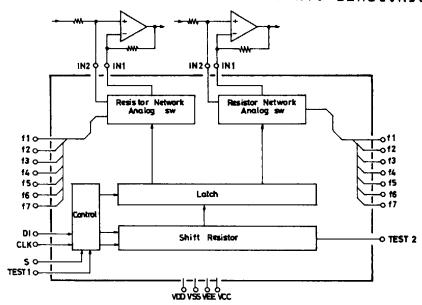

## **Equivalent Circuit Block Diagram**

## SANYO SEMICONDUCTOR CORP

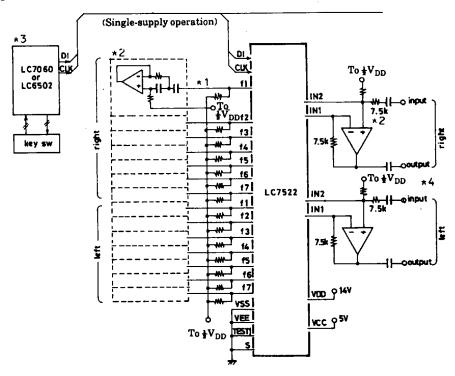

## Sample Application Circuit

- \*1 It is recommended that  $1/2V_{DD}$  is applied to pins f1 to f7 through resistors of  $1M\Omega$  so that noise is minimized at the select mode.

- \*2 The optimum conditions for 2dB/step are as follows:

$V_{DD}$  = 14V,feedback resistance of OP amp : 7.5k $\Omega$ , equivalent LC resonance impedance : 1k $\Omega$  (For  $V_{DD}$  = 8V, the LC7523 is recommended.)

- \*3 The LC7060 is available as a standard controller.

- \*4 The LC7560 (LCD driver), LC7565 (FLT, LED driver) are available as spectrum analyzing display drivers for graphic equalizer output signal.

Note 1. When power is applied, data "0" must be first transferred for 60 clocks (initial clock) or more. If data transfer is stopped halfway, the transfer of the remaining data must be completed or data transfer must be started after the initial clocks have been transferred.

Note 2. When the DI, CLK pins are shared with the LC7560, etc., the maximum initial clocks for such device must be transferred.

### Pin Description

| Pin Name                                              | Pin Configuration | Description                                                                                                                                                                                                                                                                                                                     |  |  |  |

|-------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| V <sub>DD</sub><br>V <sub>SS</sub><br>V <sub>EE</sub> |                   | $\begin{array}{lll} \mbox{Power supply pin} & +7V \mbox{ typ. power supply for audio signal} \\ \mbox{Power supply pin} & 0V \\ \mbox{Power supply pin} & -7V \mbox{ typ. power supply for audio signal,} \\ \mbox{connected to $V_{SS}$ at single-supply operation} \\ \mbox{Power supply pin} & +5V \mbox{ typ.} \end{array}$ |  |  |  |

| DI                                                    | - 2               | Used to input data from CPU<br>Schmitt inverter type                                                                                                                                                                                                                                                                            |  |  |  |

| CLK                                                   |                   | Used to input clock from CPU<br>Schmitt inverter type                                                                                                                                                                                                                                                                           |  |  |  |

| IN1<br>IN2                                            |                   | Audio signal input pin Normally, IN1 is connected to inverting input of OP amp. Normally, IN2 is connected to noninverting input of OP amp. Provided in Lch/Rch                                                                                                                                                                 |  |  |  |

| f1 to f7                                              | □                 | Band-pass filter connecting pin<br>f1 to f7×2 (right/left) = 14(total) pins                                                                                                                                                                                                                                                     |  |  |  |

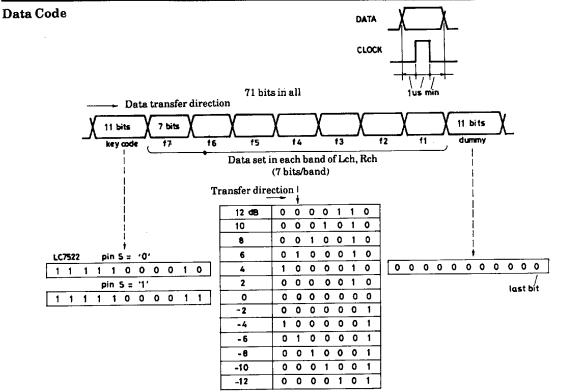

| S                                                     | <b>□</b> →>       | Select pin at 2-chip used mode To accept data under key code 7C3, S must be set to '1'.  →Connected to V <sub>DD</sub> To accept data under key code 7C2, S must be set to '0'.  →Connected to V <sub>EE</sub>                                                                                                                  |  |  |  |

| TEST1<br>TEST2                                        |                   | IC test pin<br>Open during operation                                                                                                                                                                                                                                                                                            |  |  |  |

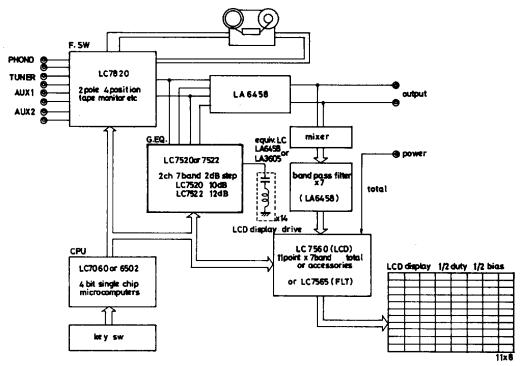

## [Reference 1] ECS System/Graphic Equalizer Application Circuit Block Diagram

SANYO SEMICONDUCTOR CORP

# [Reference 2] Main Specifications for LC7060 (CMOS LSI/Graphic Equalizer Controller) Use

Controller LSI for graphic equalizer electronic volume control LSI: LC7520,7522, LCD driver: LC7560, FLT driver: LC7565.

#### **Functions**

- $\cdot$  7 bands, 2dB/step,  $\pm$  10dB ( $\pm$  12dB) variable, ( ): LC7522/7565-combined use.

- · Max. 8 memories (user option 5 modes, maker option 3 modes) + last channel memory.

- · Possible to control function switch (5 positions) and electronic volume control.

- · 2 control lines for graphic equalizer electronic volume control and display IC

- · Buzzer sound is generated when a key is operated.

- · On-chip remote control reception program.

#### **Features**

- Any combination of graphic equalizer electronic volume control LSI LC7520,7522, and display driver LSI LC7560,7565 may be used. (Port-selectable)

- $\cdot$  FLAT function to permit the FLAT mode to be entered with one touch.

- · REVERSE function to permit the frequency characteristic to be reversed with respect to 0dB with one touch.

- · Tuner band select and SCAN output.

- MUTE and MUTE output.

- · Backup operation available.